## Automated Target Recognition on SPLASH 2 †

Michael Rencher and Brad L. Hutchings

Department of Electrical and Computer Engineering

Brigham Young University

Provo, UT 84602

#### Abstract

Automated target recognition is an application area that requires special-purpose hardware to achieve reasonable performance. FPGA-based platforms can provide a high level of performance for ATR systems if the implementation can be adapted to the limited FPGA and routing resources of these architectures. This paper discusses a mapping experiment where a linear-systolic implementation of an ATR algorithm is mapped to the SPLASH 2 platform. Simple columnoriented processors were used throughout the design to achieve high performance with limited nearestneighbor communication. The distributed Splash 2 memories are also exploited to achieve a high degree of parallelism. The resulting design is scalable and can be spread across multiple SPLASH 2 boards with a linear increase in performance.

#### 1 Introduction

Automated target recognition (ATR) is a computationally demanding application area that typically requires special-purpose hardware to achieve desirable performance. ASICs are not an option for these systems due to high non-recurring engineering (NRE) costs and because the algorithms are constantly evolving. Existing FPGA-based computing platforms can potentially provide the necessary performance and flexibility for evolving ATR systems; however, mapping applications to these existing platforms can be very challenging because they lack abundant interconnect and FPGA resources. The key to achieving a high-performance implementation of ATR algorithms with existing platforms is to carefully organize the design of the ATR implementation so that it can communicate via the limited interconnect and can be easily partitioned among the FPGA devices.

This paper presents a linear systolic implementation of an existing ATR algorithm on SPLASH 2 that is well-suited to the SPLASH 2 architecture. Inter-FPGA communication is limited and easily accommodated by the SPLASH 2 interconnect. Moreover, the implementation can be scaled across any number of SPLASH 2 boards and achieves high performance with limited resources.

This paper briefly discusses the entire ATR algorithm as developed by Sandia National Labs, and then overviews the design and implementation of the most computationally demanding part of the algorithm: Chunky SLD. The SPLASH 2 implementation is presented in some detail with future directions and possible improvements.

#### 2 Automatic Target Recognition

The goal of a typical ATR system is to analyze a digital representation of a scene and locate/identify objects that are of interest. Although this goal is conceptually simple, ATR systems have extremely demanding I/O and computational requirements: image data are large, can be generated in real-time, and must be processed quickly so that results remain relevant in a dynamic environment. The common use of special-purpose hardware in nearly all high-performance ATR systems is a clear indication of the computational complexity of these systems.

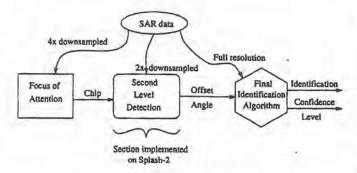

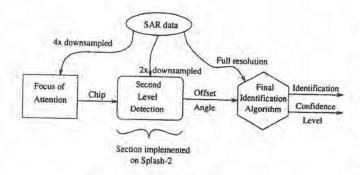

This paper details the implementation of an existing ATR algorithm on SPLASH 2. The algorithm in question was developed at Sandia National Laboratories and was designed to detect partially obscured targets in Synthetic Aperture Radar (SAR) images. It is commonly referred to as Chunky SLD, so named for the second step of the algorithm that differentiates this algorithm from others developed at Sandia. This algorithm consists of the following three steps: (1) Focus of Attention (FOA), (2) Second-Level Detection (SLD), and (3) Final Identification (FI). Each of these steps will now be introduced so that the algorithm implementation can be understood in its operating context.

<sup>&</sup>lt;sup>†</sup>This work was supported by DARPA/CSTO under contract number DABT63-94-C-0085 under a subcontract to National Semiconductor

Figure 1: ATR Block Diagram.

#### 2.1 Focus of Attention (FOA)

Focus of attention is the first step of the ATR process and uses image morphology techniques to detect potential targets in SAR data. FOA operates on "down-sampled" SAR images that are approximately 600-1000 pixels on a side. Once FOA detects a potential target, it determines the approximate center of the potential target and creates 2× down-sampled subimages of the original SAR data where each subimage contains a single target centered within the subimage. These subimages are referred to as chips and are 128 × 128 pixels.

#### 2.2 Second Level Detection (SLD)

The SLD step processes the chips generated by the FOA step. SLD further restricts the areas of interest by giving the potential targets coordinates and angular orientation. SLD does this by correlating predefined binary templates to the areas of interest. The templates represent different object orientation angles. Templates are oriented between 5 and 10 degrees apart. SLD also uses adaptive threshold levels determined by the overall image intensity.

The algorithm studied in the paper is a variation of SLD called Chunky SLD. Chunky SLD adds a level of complexity to SLD by using more templates to represent objects that have been partially obscured (partially hidden by camouflage or objects overhead). This allows better target recognition at a cost of higher computational requirements. Chunky SLD is discussed in more detail later in this section.

#### 2.3 Final Identification (FI)

The FI algorithm correlates full resolution image data and templates with finer angular resolution (3 to 5 degrees). FI also uses adaptive threshold levels. The output of FI is a location of the target, and confidence level corresponding to the level of correlation between the object and the FI templates.

#### 2.4 The Chunky SLD Algorithm

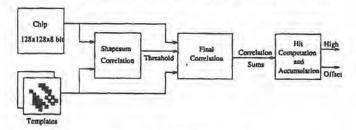

The general goal of the Chunky-SLD algorithm is to recognize targets that are partially concealed or obscured in some way. To achieve this goal, the designers of this algorithm treat the target as a set of 40 template pairs where each pair of templates is a digital representation of some salient feature of the specific target. If the majority of the template pairs strongly correlate with the image data, then a match of the overall target is assumed. Each pair of templates con-

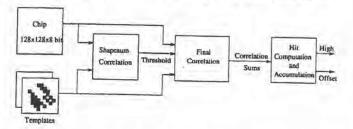

Figure 2: Chunky SLD

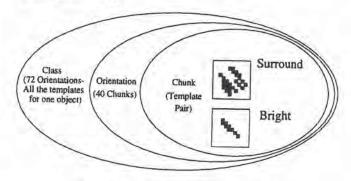

sists of a Bright template and a Surround template. The Bright template is a representation of expected reflections directly from surfaces of a salient target feature while the Surround template represents expected absorption in the immediate area surrounding the target feature. Each pair of a Bright and Surround template is referred to as a chunk, so called because each pair of templates represents a "chunk" of the overall target. Each set of 40 chunks represents a single target at a specific rotation. There are 72 orientations, each representing a different target orientation and radar incidence angle. Each set of 72 orientations is referred to as a class and is the complete set of templates that must be correlated with a chip to detect the presence of a specific target.

Figure 3: Template Organization

The first step of the Chunky SLD algorithm is to correlate the chip and the Bright template. This correlation value is used to compute a value that will be used to threshold the incoming chip data, converting the 8-bit chip image into a binary image. The equations describing this process are shown below.

$$Shapesum(x,y) = \sum_{a,b=0}^{15} B_{temp}(a,b) * Chip(x+a,y+b)$$

$$Threshold(x,y) = \frac{Shapesum(x,y)}{Bright\_template\_pixel\_count}$$

The values obtained by correlating the Bright and Surround templates with the binarized chip (B<sub>sum</sub> and S<sub>sum</sub>) are checked against minimum values to generate a "hit value" for each offset in the chip. The threshold value is also checked to see if it falls in an acceptable range when generating the hit values.

$$if([T_{max} \ge T \ge T_{min}] \ AND$$

$[B_{sum} \ge B_{min}] \ AND$

$[S_{sum} \ge S_{min}])$

then

$Hit = 1;$

$else$

$Hit = 0;$

The hit values are accumulated for each offset for a specific orientation (40 chunks). The highest values are used to identify the areas of interest for the final identification step.

#### 2.4.1 Template Characteristics

Template pairs exhibit useful properties: sparseness and mutual exclusivity. The Bright template consists mostly of zeros; only 3 to 10 percent of the template values are '1's and this limits the magnitude of the Shapesum and  $B_{sum}$  values. The Bright and Surround templates are also mutually exclusive; that is, if the two templates are overlaid no "on" pixels will overlap. When carefully exploited, both of these properties lead to more compact and higher performance hardware.

#### 3 Other Implementations of Chunky-SLD

As explained the ATR application is computationally demanding. There are  $(128-15) \times (128-15)$  offsets per chunk  $\times$  40 chunks  $\times$  72 orientations  $\cong$  36  $\times$  10<sup>6</sup> hit values to compute per targeted object (or per class, see Figure 3). The computational rate and I/O requirements of this algorithm make it impossible to use current microprocessors. Thus any high-performance implementation of this algorithm will require special-purpose hardware to meet performance goals.

However, custom ASICs are also not an option because the algorithm is constantly evolving and also because commercial-off-the-shelf components (COTS) are often dictated by the ultimate customers of ATR systems. The only remaining options are to construct the system with commercially available fixed-function devices such as correlaters, multipliers, etc., or to use programmable logic, e.g., FPGAs [1, 2]. Thus all known implementations of Chunky-SLD use either fixed-function devices or programmable logic.

#### 3.1 Sandia

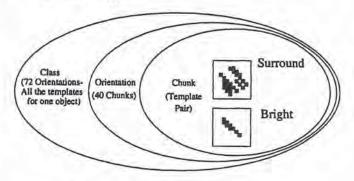

Current Sandia implementations of ATR are based on commercially available one-bit correlater chips. Sandia designers adapted the basic Chunky-SLD algorithm so they could exploit the capabilities of these components to achieve high performance. Rather than process the Shapesum and then process the final correlation, the two steps were done in parallel. The correlation was done at 8 discrete threshold levels and the Shapesum determined which threshold to use for each offset.

Figure 4: Sandia's Implementation.

#### 3.2 UCLA

A group at UCLA (Headed by John Villasenor) [3] is working on a FPGA based SLD implementation. By doing bit level correlations they are able to do very compact adder trees that take advantage of template sparseness and FPGA on board lookup-table memory capability. Their approach compiles template information directly into the hardware and relies on fast reconfiguration to switch template information. They

also try and take advantage of template overlap by computing the results of multiple correlations simultaneously.

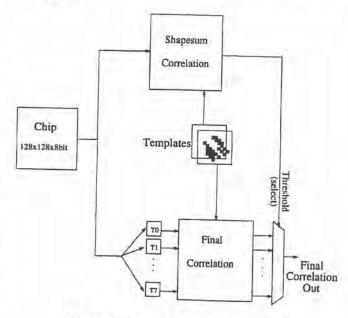

#### 4 Chunky-SLD on Splash 2

On SPLASH 2 a static implementation was done to avoid the overhead of reconfiguring the hardware during execution. In order to reduce the hardware requirements without reducing throughput a deeply pipelined design (~400 cycle latency) was implemented. The Shapesum unit generates the threshold value which is then used to generate the final correlation values. (Note: There is a unique threshold for each offset). By doing this only two final correlations have to be computed per offset (one B<sub>sum</sub> and one S<sub>sum</sub>).

The Sandia implementation computes the Shapesum and final correlation in parallel which forces them to compute multiple final correlations. While our implementation does them serially. This allows us to use an exact threshold value. Also only one final correlation needs to be computed because the threshold value is computed before the final correlation begins. The technique used was to look at the correlations by column, compute the partial correlation for that column, and sum up the partial sums for all 16 columns. In this method 16 different column correlations are going on in parallel but only one column of data needs to be available for processing.

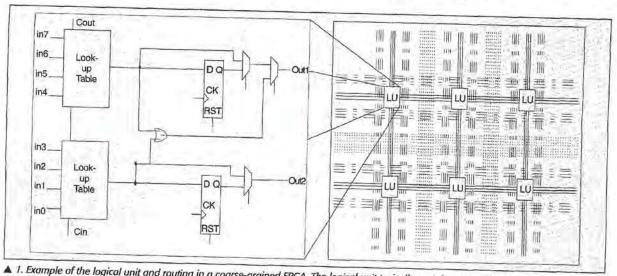

#### 4.1 Implementing the Correlation as Column Sums

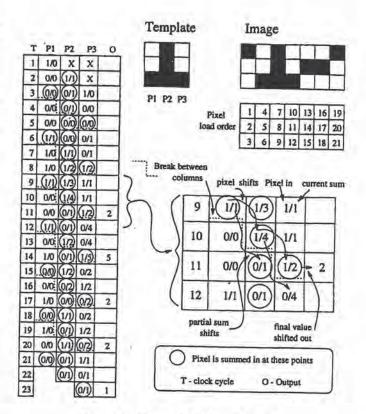

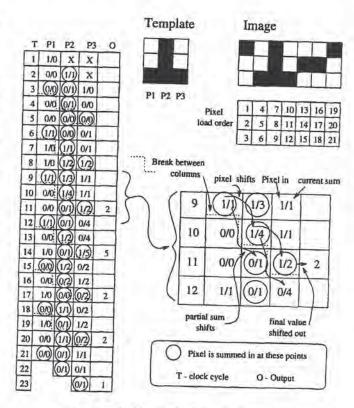

Figure 5 depicts a simple example that demonstrates a correlation of a 3×3 template with a binary image. Each row in the table represents one clock cycle. The first column is the clock cycle number. Corresponding numbers are found in the Pixel load order box at the right. A new pixel is brought in on each clock cycle. The P1, P2, and P3 columns represent the three column processing units needed for a three column template. The last column represents the actual output. Clock cycles 9 through 12 have been expanded to show how data (pixels and partial sums) are passed from column to column and illustrate the data format. Once the pipeline is full, a new correlation value is computed as each column arrives (three pixels/cycles).

Note that valid output comes every three cycles because the template is three rows tall. All processing elements are actively processing 3 pixel values at all times. The Splash 2 implementation works just like the example except for the size of the columns (16 pixels instead of three) and the data format (eight-bit instead of one-bit).

Figure 5: Example Column Sum.

#### 4.2 Platforms/Implementations

Chunky SLD was implemented on the SPLASH 2 board. SPLASH 2 has shown itself to be a useful platform and has had numerous applications mapped to it [4, 5, 6, 7, 8, 9, 10, 11]. The implementation was done in VHDL and simulated/synthesized using Synopsis. All place and route was done automatically using Xilinx place and route tools.

One of the goals of the implementation was to run the system so that it consumed a pixel per cycle. This means that each cycle all processing elements (PE) need to be able to process a new pixel. This implementation follows Sandia National Labs algorithms (not implementation) as closely as possible (see Section 2.4).

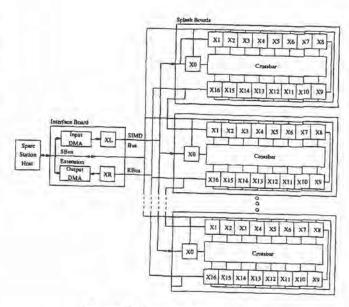

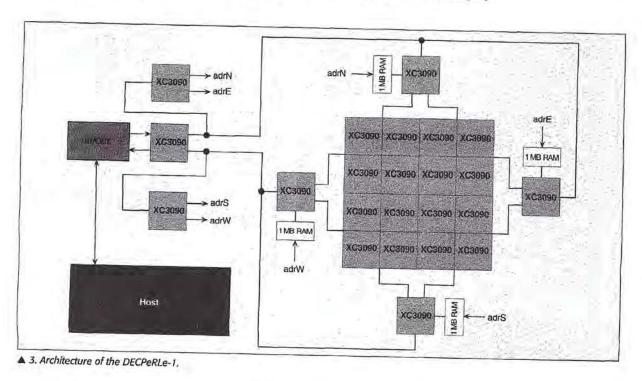

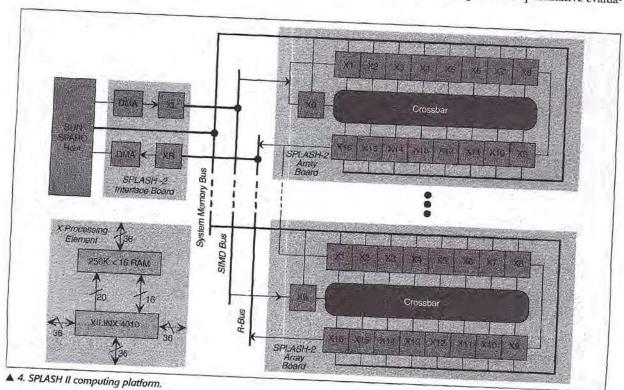

The SPLASH 2 board was developed by SRC (Supercomputing Research Center Institute for Defense Analyses) [12]. The SPLASH 2 board is a linear systolic array of processing elements (FPGAs), each with their own memory.

#### 4.2.1 Splash 2 Hardware

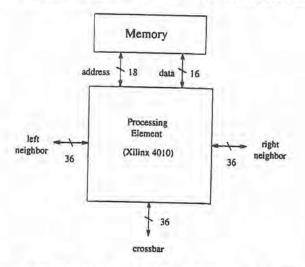

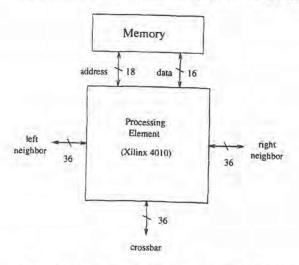

From a conceptual point of view, the SPLASH 2 system consists of a linear array of processing elements. This

makes SPLASH 2 a good candidate for linear-systolic applications with limited neighbor-to-neighbor interconnect. Because of limited routing resources SPLASH 2 has difficulty implementing multi-chip systems that are not linear systolic, though they are possible [8].

The actual SPLASH 2 platform consists of a board with 16 Xilinx 4010 chips (plus one for control) arranged in a linear systolic array. Each chip has a limited 36-bit connection to its two nearest neighbors. Each Xilinx 4010 is connected to a 512 kbyte memory

Figure 6: Single Processing Element of SPLASH 2.

(16-bit word size). The memory can handle back-to-back reads, or back-to-back writes, but requires one 'dead' (or turn around) cycle when changing from write to read. There is also a crossbar connected to all of the chips that allows some level of random connection between chips. Up to 16 boards can be daisy-chained together to provide a large linear-systolic array of 256 elements.

#### 4.3 ATR Implementation on Splash 2

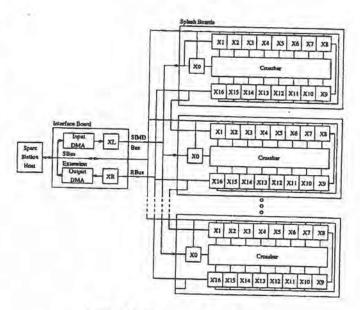

Similar to the example, the SPLASH 2 implementation processes one pixel at a time and loads them in column order so that the partial sums can be generated and passed from column to column. All template data are stored in the memories adjacent to the FPGAs on the SPLASH 2 boards. Each memory can hold several thousand templates thus making it possible to store all of the templates for a single class (5760) on a single SPLASH 2 board. There is sufficient room in the FPGA design to store a single template. The templates are switched by reading the new template data out of the memory and storing it within the FPGA. However, because this implementation is deeply pipelined, it is necessary to flush all current

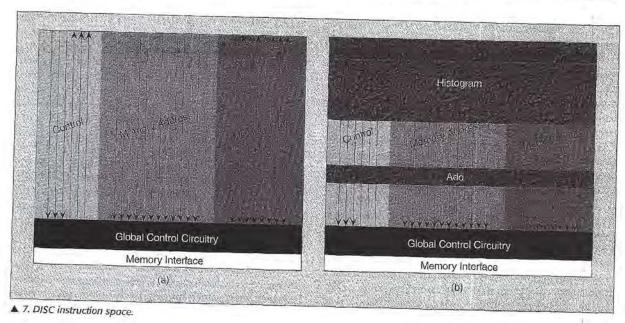

Figure 7: SPLASH 2 platform.

data from the system when switching to a new template. The overhead from the flushing operation is minimal ( $\frac{318 \ flush \ cycles}{231424 \ compute \ cycles}$  =) 0.14%.

During each clock cycle, a new pixel arrives at the FPGA. If the template bit corresponding to this pixel is on then the incoming pixel is added to the current partial sum. Each 16 clock cycles, this partial sum is then passed on to the next column and a new partial sum is received from the previous column. The last column computes a complete Shapesum every 16 cycles (one column). The final correlation of the Bright and Surround templates with the thresholded chip data works similarly except there are two correlations (one for each template).

Intermediate hit values are stored in a table, referred to as the hit-table, in one of the local memories. Each location in the table corresponds to an x-y offset of a chip, the origin of a single correlation. For each offset, if a chunk "hits", then the corresponding location in this table is incremented. Thus the table contains the accumulated hit values for all chunks and all offsets that have been computed to that point.

Hits are computed according to Equation 1. First, each B<sub>sum</sub> and S<sub>sum</sub> value is compared to its corresponding minimum value. Second, the threshold value corresponding to each B<sub>sum</sub> and S<sub>sum</sub> is checked to see if it is between a certain minimum and maximum value. For reasons of efficiency, the threshold value is actually examined earlier in the process and a zero for the threshold is stored in lookup-table memory if it is out of bounds. This works correctly because if the

threshold is zero, it will cause the B<sub>sum</sub> to be zero, which will in turn cause the B<sub>sum</sub> comparison to fail. Otherwise, if all three of these tests come back true then a hit has been found for the corresponding offset (see Equation 1) and the corresponding location in the hit-table is incremented. After the 40 templates are tested against the same chip the two offsets with the highest accumulated hit values are written into memory where the host computer can read them. This is accomplished by examining the hit values during this process and retaining the top two values in special memory locations. These final two hit values (which represent the top two orientations for a specific class) are used in the FI step.

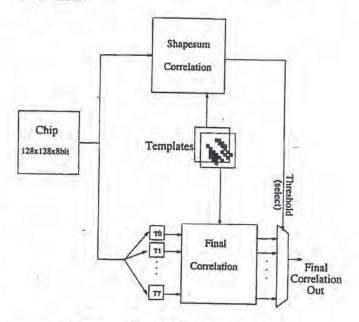

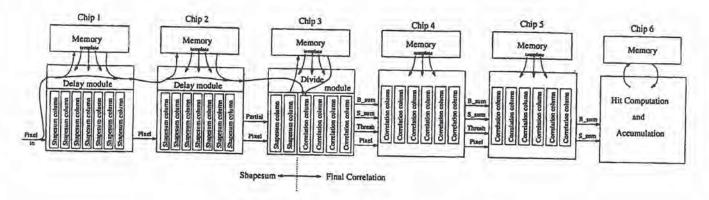

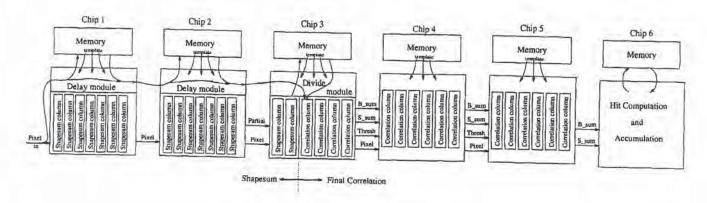

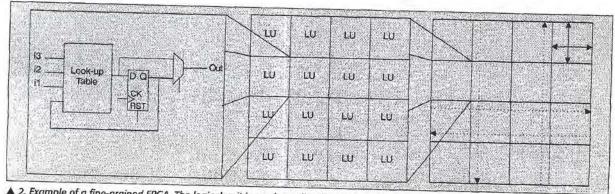

For the SPLASH 2 board, as with most FPGA systems, partitioning is a major issue. The design needed to be modular so that different design modules could be reassigned to different FPGAs as necessary. This is where the column modules were so valuable (see Figure 8).

#### 4.4 Special Features

This implementation has several notable characteristics. They include control distribution, modular design for partitioning and memory utilization.

#### 4.4.1 Distributed Control

The control in this system is distributed throughout the array. Each column module has it's own state machine based control. Module synchronization is achieved by distributing a control token through the pipeline along with the data. When a module receives this signal, it resets its internal state machines and retrieves template data from its local memory. A memory controller resides in each processing element (FPGA) to retrieve template data and give memory access to all other modules.

#### 4.4.2 Modular Design (Design for Partitioning)

Each column in both the Shapesum and final correlation use totally self contained modules that can be easily migrated from processing element to processing element. This was done to simplify the partitioning onto Splash 2 [13]. Memory data had to be carefully partitioned as well so that the data could follow the module to which it applied. The regularity of the design was an important concern; it allowed the placement of specific circuit modules to be dictated by the requirements of the algorithm and not by the limited interconnect of the platform. There are 16 identical

modules in the Shapesum and 16 more identical modules in the final correlation. Along with these there is a divide, a hit accumulator and 2 delay modules (see Figure 8).

#### 4.4.3 Memory Usage

The memories in Splash 2 serve several purposes. The template information is stored in them. They are used to implement video shift registers that correct for the latency incurred during threshold computation. These shift registers require that two memories be used in tandem because every clock cycle a new pixel (8 bits) had to be written to memory and a delayed pixel had to be read from memory. The bandwidth of one memory was such that it can handle two pixels (load and store) every three cycles. Thus one memory would delay two pixels and skip two pixels, while the other memory would delay the two pixels that the first memory skipped and skip the two pixels that the first memory delayed. The divide unit and the final result including the accumulated hit values are also stored in memory.

#### 4.5 Performance Metrics

There are many metrics that could be used to measure the value of this implementation. This section is devoted to discussing some of these metrics.

#### 4.5.1 Performance

This implementation runs at a frequency of 19 MHz using a test template that tests all column modules. Xdelay (a Xilinx timing tool) reports a guaranteed frequency of 13.2 MHz. Designs that will run in the 10 to 20 MHz range are typical [8, 10].

Using the above frequency a single system could process one orientation every .487 seconds (.701 seconds using a 13.2 MHz clock).

$$\frac{128 \ col \times (128-15) \ row \times 16 \frac{pix}{col}}{19 \ MHz} \times 40 \frac{Chunks}{Orient} = \\ (12 \ ms/Chunk) \times 40 \frac{Chunks}{Orientation} = \\ 487 \ ms @ 19 \ MHz$$

10

$$\frac{128 \ col \times (128-15) \ row \times 16 \frac{pis}{col}}{13.2 \ MHz} \times 40 \frac{Chunks}{Orient} =$$

$$(17.5 \ ms/Chunk) \times 40 \frac{Chunks}{Orientation} =$$

$$701 \ ms @ 13.2 \ MHz$$

Figure 8: SPLASH 2 Implementation.

Using a brute force approach it takes 59 seconds to compute the same data on an HP 770 (110 MHz). That is two orders of magnitude slower. On one SPLASH 2 board two processing units can be installed yielding the ability to process 1 orientation (40 chunks) every .244 seconds (.350 seconds at 13.2 MHz).

#### 4.5.2 Multi-board Splash 2

If a 16-board system were used then 256 processing elements would be available, this would make 42 processing units (256 PEs ÷ 6 PE per PU) and 42× the throughput. Thus one orientation can be processed every 11.6 ms (16.7 ms at 13.2 MHz). This is equal to covering 86 orientation per second (60 orientations per second at 13.2 MHz).

#### 4.5.3 Memory Bandwidth

The distributed memory and aggregate memory bandwidth is what makes this implementation possible. Because the memory is distributed to each chip this implementation can be extended to a multi-board system quite easily. Consider that a processing unit consists of 6 FPGAs and their corresponding memories. Each processing unit performs 10 reads and 13 writes each 16 clock cycles. The SPLASH 2 memories require 3 clock cycles to perform a read and a write for a total available bandwidth of 2 reads and 2 writes every cycle (6 memories / 3 cycles / 3

#### 4.5.4 Memory stored templates

The decision to use statically configured hardware and memory-stored templates was made early in the design process. Another approach would be to use hard-coded templates, e.g., hardware with the template data compiled in as constants. A hard-coded template implementation could possibly use less hardware by removing unused accumulators and template reading logic, however it would require the hardware to be reconfigured during run-time in order to switch templates. This would take significantly longer than the memory read done in the memory-stored template version. The SPLASH 2 system requires approximately 17 ms per chip to configure. The system would have to be reconfigured each time a new template was used. In order to process one orientation the system would have to be configured 40 different times. This would adversely impact system throughput. In fact even if the system could be reconfigured in one cycle the performance wouldn't improve because the time spent reading templates from memory is hidden while the pipeline is initially filling (during the flush cycles). There are other advantages as well. Design time is simplified because new hardware bit streams don't have to be generated and tested to use new templates. Re-compilation may improve hardware utilization, however that would come at a cost of repartitioning difficulty.

#### 5 Future work

In the future, additional related research will be conducted on possible improvements to the implementation described in this paper. In addition, alternative implementations that are not currently possible with the SPLASH 2 platform are under examination. Finally, work is underway on a bit-serial version of this implementation.

#### 5.1 Splash 2 Improvements

Although Splash 2 was suitable for this project, there are many possible architectural improvements that could be made that would increase performance significantly. A faster memory interface that supports a two-cycle read-write operation or perhaps a dual-ported memory interface would provide improved memory bandwidth. A larger processing element would give more resources and make implementations more flexible. Updated VHDL libraries that conform to standard data types would help design portability and simplicity.

If chip-to-chip I/O were increased on SPLASH 2 a full column could be processed each clock cycle. This would require at least 339 I/O pins ([128 pixel bits + 13 bit partial sum + 8 bit threshold + 2 bits of control] × 2 (in and out) + 16-bit memory data + 21-bit memory address = 339 pins). The current chips (Xilinx 4010) has enough logic and routing to process an entire column at one time. If this kind of I/O bandwidth were available [14] the system would consume 2 SPLASH 2 boards but would have 16 times the throughput because 16 times as much data would be processed each clock cycle.

Another option would be to distribute the *chip* image to each FPGA memory and have a wide memory data path. This would require at least 195 I/O pins ([13 bit partial sum + 8 bit threshold + 2 bit control]  $\times$  2 (in and out) + 128 bit memory data path + 21 bit memory address = 195) but would have the same throughput.

#### 5.1.1 Interface Improvements

The current implementation assumes that all data are loaded on the Splash 2 board before processing commences. A more realistic implementation would stream data to the system as it is produced. Thus, DMA channels or other high-performance I/O hardware, if added to the system, would make performance more sustainable across multiple images.

#### 5.2 Other implementations

There are several ways this algorithm could be implemented. The most obvious way is to to a full parallel version that looks at a full 16×16 pixels at a time. Another is a linear systolic version that looks at one pixel at a time. A linear systolic implementation was designed because Splash 2 is organized that way.

This implementation takes a relatively brute-force approach and feeds the entire chip into the system for processing. Whether or not a given pixel actually contributes to the calculation is determined after

the image data are already in the pipeline. Other approaches may take a more selective approach and only access image pixels that actually contribute to the calculation. This may reduce overall memory bandwidth requirements and suggest other implementation strategies. An implementation that only examined pixels that will be used could potentially give a performance increase when correlating the Bright template because the majority of pixels in the template represent chip locations that do not contribute to the computation. However, such an approach would require a complicated control scheme and may not map well onto SPLASH 2.

Here at BYU there is ongoing work targeting 3 different FPGA architectures, each looking to better understand the hardware and ATR algorithms. These include a bit-serial version targeted at National Semiconductors Clay FPGA and a Xilinx 6200. Another project is looking at a full parallel implementation targeting an Altera Flex-10K part.

#### 6 Conclusion

SPLASH 2 is organized as a linear array of FPGA chips each connected to a separate memory. Because of this, applications can only make effective use of SPLASH 2 resources if (1) individual circuit modules are small enough to easily fit into the limited resources available within a single FPGA (Xilinx 4010) and (2) circuit modules can be grouped together in such a way that the interconnect requirements between modules on separate chips will fit in the limited chip-to-chip interconnect available on SPLASH 2.

Both of these requirements were met in this application by carefully organizing all correlations (both Shapesum and final correlation) as independent column-oriented processing elements (PEs). Each PE occupied only a small amount of FPGA resources thereby making it possible to place several PEs into a single FPGA. PEs that are integrated on a single FPGA communicate via the available on-chip FPGA routing; PEs that are located on different FPGAs can easily communicate via the limited inter-chip routing on SPLASH 2.

This repetitive, column-oriented organization also eases the programming of SPLASH 2 considerably. Much of the VHDL code was reused and because the fourth and fifth chips are identical (because of the linear column layout, see Figure 8) it was possible to down-load the same bit-stream into both chips.

This column organization presents a good tradeoff between a fully parallel design and a design that fits within the restrictions of the SPLASH 2 architecture. Each column operates in parallel computing a column sum that when complete is passed onto its neighboring column. While it is possible to achieve higher levels of parallelism, it is likely that such designs will require denser interconnect than SPLASH 2 is capable of providing (see Section 5.1). By limiting communication to only adjacent columns, significant parallelism is still achieved with only moderate amounts of interconnect.

This implementation can also take advantage of SPLASH 2's extensibility giving it even higher performance capability. Simply by passing the pixel data from chip 6 (see Figure 8) to the next chip on the SPLASH 2 board and configuring the next 6 chips in the array with the same bit stream as the first 6 chips the throughput on the system would be doubled. This extensibility can also be expanded to multiple boards giving a linear increase in system throughput.

#### References

- S. Trimberger. A reprogrammable gate array and applications. Proceedings of the IEEE, pages 1030-1041, July 1993.

- [2] National Semiconductor. Configurable Logic Array (CLAy). National Semicondutor, 1993.

- [3] J. Villasenor, B. Schoner, K. Chia, and C. Zapata. Configurable computing solutions for automatic target recognition. In J. Arnold and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 70-79, Napa, CA, April 1996.

- [4] A. L. Abbott, P. M. Athanas, L. Chen, and R. L. Elliott. Finding lines and building pyramids with Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 155-161, Napa, CA, April 1994.

- [5] J. M. Arnold. The Splash 2 software environment. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 88-93, Napa, CA, April 1993.

- [6] P. Athanas and A. Abbott. Image processing on a custom computing platform. In R. Hartenstein and M. Z. Servit, editors, Field-Programmable Logic: Architectures, Synthesis and Applications. 4th International Workshop on Field-Programmable Logic and Applications, pages 156-167, Prague, Czech Republic, September 1994. Springer-Verlag.

- [7] M. Gokhale and B. Schott. Data parallel C on a reconfigurable logic array. Journal of Supercomputing, 9(3):291-313, 1994.

- [8] P. Graham and B. Nelson. A hardware genetic algorithm for the travelling salesman problem on SPLASH 2. In W. Moore and W. Luk, editors, Field-Programmable Logic and Applications, pages 352-361, Oxford, England, August 1995. Springer.

- [9] D. T. Hoang. Searching genetic databases on Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 185-191, Napa, CA, April 1993.

- [10] D. V. Pryor, M. R. Thistle, and N. Shirazi. Text searching on Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 172-177, Napa, CA, April 1993.

- [11] N. Ratha, A. Jain, and D. Rover. Convolution on Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 204-213, Napa, CA, April 1995.

- [12] J. M. Arnold, D. A. Buell, and E. G. Davis. Splash 2. In Proceedings of the 4th Annual ACM Symposium on Parallel Algorithms and Architectures, pages 316-324, June 1992.

- [13] Benjamin W. Wah. Systolic arrays-from concept to implementation. *IEEE Journal Com*puter, 20(7):12-17, July 1987.

- [14] Altera. Altera-Embedded Programmable Logic Family-Flex 10K Data Sheet. Altera, 1995.

## Attachment 2B

| IEEE.org | IEEE Xplore Digital Library | IEEE-SA | IEEE Spectrum | More Sites

Cart (0) | Create Account | Personal Sign In

Access provided by: Purdue University Sign Out

Browse

My Settings

Get Help

Browse Conferences > Proceedings. The 5th Annual I...

Back to Results

#### Automated target recognition on SPLASH 2

Wissy Document

15 Paper Citations 73 Full Text Views **Related Articles**

NMF and FLD based feature extraction with application to Synthetic Aperture Rada...

A Real-Time NetFlow-based Intrusion Detection System with Improved BBNN and High...

View All

2 Author(s)

M. Rencher; B.L. Hutchings

View All Authors

Abstract

Authors

Figures

References

Citations

Keywords

Metrics

Media

IEEE websites place cookies on your device to give you the best user experience. By using our websites, you agree to the placement of these cookies. To learn more, read our Privacy Policy.

Accept & Close

Alerts

#### Abstract:

Automated target recognition is an application area that requires special-purpose hardware to achieve reasonable performance. FPGA-based platforms can provide a high level of performance for ATR systems if the implementation can be adapted to the limited FPGA and routing resources of these architectures. The paper discusses a mapping experiment where a linear-systolic implementation of an ATR algorithm is mapped to the SPLASH 2 platform. Simple column oriented processors were used throughout the design to achieve high performance with limited nearest neighbor communication. The distributed SPLASH 2 memories are also exploited to achieve a high degree of parallelism. The resulting design is scalable and can be spread across multiple SPLASH 2 boards with a linear increase in performance.

Published in: Proceedings. The 5th Annual IEEE Symposium on Field-Programmable Custom Computing Machines Cat. No.97TB100186)

Date of Conference: 16-18 April 1997

Date Added to IEEE Xplore: 06 August 2002

Print ISBN: 0-8186-8159-4

INSPEC Accession Number: 5731389

DOI: 10.1109/FPGA.1997.624619

Publisher: IEEE

Conference Location: Napa Valley, CA, USA, USA

Download PDF continue-Download Citation Authors View References References Email Citations 75.63/ WHITEST III. Print Keywords released review-Related Articles Request Permissions Back to Top

**IEEE Account** Purchase Details Profile Information Need Help? » Change Username/Password

Payment Options Communications Preferences US & Canada: +1 800 678 4333 Update Address Order History Profession and Education Worldwide: +1 732 981 0060 N View Purchased Documents

Technical Interests » Contact & Support

About IEEE Xplore | Contact Us | Help | Accessibility | Terms of Use | Nondiscrimination Policy | Sitemap | Privacy & Opting Out of Cookies

A mot-forcinal organization, IEEE is the world's larguest technical professional inpartization understand to annually lazarionical for the persons of humanity. - Copyright 2018 IEEE - All agaits reserved. Usin of this web site algorifies your engreence of to the (cross and populations

IEEE websites place cookies on your device to give you the best user experience. By using our websites, you agree to the placement of these cookies. To learn more, read our Privacy Policy.

Accept & Close

### Automated Target Recognition on Splash 2 †

Michael Rencher and Brad L. Hutchings Department of Electrical and Computer Engineering Brigham Young University Provo, UT 84602

#### Abstract

Automated target recognition is an application area that requires special-purpose hardware to achieve reasonable performance. FPGA-based platforms can provide a high level of performance for ATR systems if the implementation can be adapted to the limited FPGA and routing resources of these architectures. This paper discusses a mapping experiment where a linear-systolic implementation of an ATR algorithm is mapped to the Splash 2 platform. Simple columnoriented processors were used throughout the design to achieve high performance with limited nearestneighbor communication. The distributed SPLASH 2 memories are also exploited to achieve a high degree of parallelism. The resulting design is scalable and can be spread across multiple SPLASH 2 boards with a linear increase in performance.

#### 1 Introduction

Automated target recognition (ATR) is a computationally demanding application area that typically requires special-purpose hardware to achieve desirable performance. ASICs are not an option for these systems due to high non-recurring engineering (NRE) costs and because the algorithms are constantly evolving. Existing FPGA-based computing platforms can potentially provide the necessary performance and flexibility for evolving ATR systems; however, mapping applications to these existing platforms can be very challenging because they lack abundant interconnect and FPGA resources. The key to achieving a high-performance implementation of ATR algorithms with existing platforms is to carefully organize the design of the ATR implementation so that it can communicate via the limited interconnect and can be easily partitioned among the FPGA devices.

This paper presents a linear systolic implementation of an existing ATR algorithm on SPLASH 2 that

<sup>†</sup>This work was supported by DARPA/CSTO under contract number DABT63-94-C-0085 under a subcontract to National Semiconductor is well-suited to the SPLASH 2 architecture. Inter-FPGA communication is limited and easily accommodated by the SPLASH 2 interconnect. Moreover, the implementation can be scaled across any number of SPLASH 2 boards and achieves high performance with limited resources.

This paper briefly discusses the entire ATR algorithm as developed by Sandia National Labs, and then overviews the design and implementation of the most computationally demanding part of the algorithm: Chunky SLD. The Splash 2 implementation is presented in some detail with future directions and possible improvements.

#### 2 Automatic Target Recognition

The goal of a typical ATR system is to analyze a digital representation of a scene and locate/identify objects that are of interest. Although this goal is conceptually simple, ATR systems have extremely demanding I/O and computational requirements: image data are large, can be generated in real-time, and must be processed quickly so that results remain relevant in a dynamic environment. The common use of special-purpose hardware in nearly all high-performance ATR systems is a clear indication of the computational complexity of these systems.

This paper details the implementation of an existing ATR algorithm on Splash 2. The algorithm in question was developed at Sandia National Laboratories and was designed to detect partially obscured targets in Synthetic Aperture Radar (SAR) images. It is commonly referred to as Chunky SLD, so named for the second step of the algorithm that differentiates this algorithm from others developed at Sandia. This algorithm consists of the following three steps: (1) Focus of Attention (FOA), (2) Second-Level Detection (SLD), and (3) Final Identification (FI). Each of these steps will now be introduced so that the algorithm implementation can be understood in its operating context.

Figure 1: ATR Block Diagram.

#### 2.1 Focus of Attention (FOA)

Focus of attention is the first step of the ATR process and uses image morphology techniques to detect potential targets in SAR data. FOA operates on "down-sampled" SAR images that are approximately 600-1000 pixels on a side. Once FOA detects a potential target, it determines the approximate center of the potential target and creates  $2\times$  down-sampled subimages of the original SAR data where each subimage contains a single target centered within the subimage. These subimages are referred to as *chips* and are  $128\times128$  pixels.

#### 2.2 Second Level Detection (SLD)

The SLD step processes the chips generated by the FOA step. SLD further restricts the areas of interest by giving the potential targets coordinates and angular orientation. SLD does this by correlating predefined binary templates to the areas of interest. The templates represent different object orientation angles. Templates are oriented between 5 and 10 degrees apart. SLD also uses adaptive threshold levels determined by the overall image intensity.

The algorithm studied in the paper is a variation of SLD called Chunky SLD. Chunky SLD adds a level of complexity to SLD by using more templates to represent objects that have been partially obscured (partially hidden by camouflage or objects overhead). This allows better target recognition at a cost of higher computational requirements. Chunky SLD is discussed in more detail later in this section.

#### 2.3 Final Identification (FI)

The FI algorithm correlates full resolution image data and templates with finer angular resolution (3 to 5 degrees). FI also uses adaptive threshold levels. The output of FI is a location of the target, and confidence level corresponding to the level of correlation between the object and the FI templates.

#### 2.4 The Chunky SLD Algorithm

The general goal of the Chunky-SLD algorithm is to recognize targets that are partially concealed or obscured in some way. To achieve this goal, the designers of this algorithm treat the target as a set of 40 template pairs where each pair of templates is a digital representation of some salient feature of the specific target. If the majority of the template pairs strongly correlate with the image data, then a match of the overall target is assumed. Each pair of templates con-

Figure 2: Chunky SLD

sists of a Bright template and a Surround template. The Bright template is a representation of expected reflections directly from surfaces of a salient target feature while the Surround template represents expected absorption in the immediate area surrounding the target feature. Each pair of a Bright and Surround template is referred to as a chunk, so called because each pair of templates represents a "chunk" of the overall target. Each set of 40 chunks represents a single target at a specific rotation. There are 72 orientations, each representing a different target orientation and radar incidence angle. Each set of 72 orientations is referred to as a class and is the complete set of templates that must be correlated with a chip to detect the presence of a specific target.

Figure 3: Template Organization

The first step of the Chunky SLD algorithm is to correlate the chip and the Bright template. This correlation value is used to compute a value that will be used to threshold the incoming chip data, converting the 8-bit chip image into a binary image. The equations describing this process are shown below.

$$Shapesum(x,y) = \sum_{a,b=0}^{15} B_{temp}(a,b) * Chip(x+a,y+b)$$

$$Threshold(x, y) = \frac{Shapesum(x, y)}{Bright\_template\_pixel\_count}$$

The values obtained by correlating the Bright and Surround templates with the binarized chip (B<sub>sum</sub> and S<sub>sum</sub>) are checked against minimum values to generate a "hit value" for each offset in the chip. The threshold value is also checked to see if it falls in an acceptable range when generating the hit values.

$$if([T_{max} \ge T \ge T_{min}] \ AND$$

$[B_{sum} \ge B_{min}] \ AND$

$[S_{sum} \ge S_{min}])$

then

$Hit = 1;$

else

$Hit = 0;$

The hit values are accumulated for each offset for a specific orientation (40 chunks). The highest values are used to identify the areas of interest for the final identification step.

#### 2.4.1 Template Characteristics

Template pairs exhibit useful properties: sparseness and mutual exclusivity. The Bright template consists mostly of zeros; only 3 to 10 percent of the template values are '1's and this limits the magnitude of the Shapesum and  $B_{sum}$  values. The Bright and Surround templates are also mutually exclusive; that is, if the two templates are overlaid no "on" pixels will overlap. When carefully exploited, both of these properties lead to more compact and higher performance hardware.

#### 3 Other Implementations of Chunky-SLD

As explained the ATR application is computationally demanding. There are  $(128-15) \times (128-15)$  offsets per chunk  $\times$  40 chunks  $\times$  72 orientations  $\cong$  36  $\times$  10<sup>6</sup> hit values to compute per targeted object (or per class, see Figure 3). The computational rate and I/O requirements of this algorithm make it impossible to use current microprocessors. Thus any high-performance implementation of this algorithm will require special-purpose hardware to meet performance goals.

However, custom ASICs are also not an option because the algorithm is constantly evolving and also because commercial-off-the-shelf components (COTS) are often dictated by the ultimate customers of ATR systems. The only remaining options are to construct the system with commercially available fixed-function devices such as correlaters, multipliers, etc., or to use programmable logic, e.g., FPGAs [1, 2]. Thus all known implementations of Chunky-SLD use either fixed-function devices or programmable logic.

#### 3.1 Sandia

Current Sandia implementations of ATR are based on commercially available one-bit correlater chips. Sandia designers adapted the basic Chunky-SLD algorithm so they could exploit the capabilities of these components to achieve high performance. Rather than process the Shapesum and then process the final correlation, the two steps were done in parallel. The correlation was done at 8 discrete threshold levels and the Shapesum determined which threshold to use for each offset.

Figure 4: Sandia's Implementation.

#### 3.2 UCLA

A group at UCLA (Headed by John Villasenor) [3] is working on a FPGA based SLD implementation. By doing bit level correlations they are able to do very compact adder trees that take advantage of template sparseness and FPGA on board lookup-table memory capability. Their approach compiles template information directly into the hardware and relies on fast reconfiguration to switch template information. They

also try and take advantage of template overlap by computing the results of multiple correlations simultaneously.

#### 4 Chunky-SLD on Splash 2

On SPLASH 2 a static implementation was done to avoid the overhead of reconfiguring the hardware during execution. In order to reduce the hardware requirements without reducing throughput a deeply pipelined design (~400 cycle latency) was implemented. The Shapesum unit generates the threshold value which is then used to generate the final correlation values. (Note: There is a unique threshold for each offset). By doing this only two final correlations have to be computed per offset (one B<sub>sum</sub> and one S<sub>sum</sub>).

The Sandia implementation computes the Shapesum and final correlation in parallel which forces them

to compute multiple final correlations. While our implementation does them serially. This allows us to use

an exact threshold value. Also only one final correlation needs to be computed because the threshold value

is computed before the final correlation begins. The

technique used was to look at the correlations by column, compute the partial correlation for that column,

and sum up the partial sums for all 16 columns. In

this method 16 different column correlations are going

on in parallel but only one column of data needs to be

available for processing.

#### 4.1 Implementing the Correlation as Column Sums

Figure 5 depicts a simple example that demonstrates a correlation of a 3×3 template with a binary image. Each row in the table represents one clock cycle. The first column is the clock cycle number. Corresponding numbers are found in the Pixel load order box at the right. A new pixel is brought in on each clock cycle. The P1, P2, and P3 columns represent the three column processing units needed for a three column template. The last column represents the actual output. Clock cycles 9 through 12 have been expanded to show how data (pixels and partial sums) are passed from column to column and illustrate the data format. Once the pipeline is full, a new correlation value is computed as each column arrives (three pixels/cycles).

Note that valid output comes every three cycles because the template is three rows tall. All processing elements are actively processing 3 pixel values at all times. The SPLASH 2 implementation works just like the example except for the size of the columns (16 pixels instead of three) and the data format (eight-bit instead of one-bit).

Figure 5: Example Column Sum.

#### 4.2 Platforms/Implementations

Chunky SLD was implemented on the SPLASH 2 board. SPLASH 2 has shown itself to be a useful platform and has had numerous applications mapped to it [4, 5, 6, 7, 8, 9, 10, 11]. The implementation was done in VHDL and simulated/synthesized using Synopsis. All place and route was done automatically using Xilinx place and route tools.

One of the goals of the implementation was to run the system so that it consumed a pixel per cycle. This means that each cycle all processing elements (PE) need to be able to process a new pixel. This implementation follows Sandia National Labs algorithms (not implementation) as closely as possible (see Section 2.4).

The SPLASH 2 board was developed by SRC (Supercomputing Research Center Institute for Defense Analyses) [12]. The SPLASH 2 board is a linear systolic array of processing elements (FPGAs), each with their own memory.

#### 4.2.1 Splash 2 Hardware

From a conceptual point of view, the SPLASH 2 system consists of a linear array of processing elements. This

makes SPLASH 2 a good candidate for linear-systolic applications with limited neighbor-to-neighbor interconnect. Because of limited routing resources SPLASH 2 has difficulty implementing multi-chip systems that are not linear systolic, though they are possible [8].

The actual SPLASH 2 platform consists of a board with 16 Xilinx 4010 chips (plus one for control) arranged in a linear systolic array. Each chip has a limited 36-bit connection to its two nearest neighbors. Each Xilinx 4010 is connected to a 512 kbyte memory

Figure 6: Single Processing Element of Splash 2.

(16-bit word size). The memory can handle back-to-back reads, or back-to-back writes, but requires one 'dead' (or turn around) cycle when changing from write to read. There is also a crossbar connected to all of the chips that allows some level of random connection between chips. Up to 16 boards can be daisy-chained together to provide a large linear-systolic array of 256 elements.

#### 4.3 ATR Implementation on Splash 2

Similar to the example, the SPLASH 2 implementation processes one pixel at a time and loads them in column order so that the partial sums can be generated and passed from column to column. All template data are stored in the memories adjacent to the FPGAs on the SPLASH 2 boards. Each memory can hold several thousand templates thus making it possible to store all of the templates for a single class (5760) on a single SPLASH 2 board. There is sufficient room in the FPGA design to store a single template. The templates are switched by reading the new template data out of the memory and storing it within the FPGA. However, because this implementation is deeply pipelined, it is necessary to flush all current

Figure 7: SPLASH 2 platform.

data from the system when switching to a new template. The overhead from the flushing operation is minimal ( $\frac{318 \ flush \ cycles}{231424 \ compute \ cycles}$  =) 0.14%.

During each clock cycle, a new pixel arrives at the FPGA. If the template bit corresponding to this pixel is on then the incoming pixel is added to the current partial sum. Each 16 clock cycles, this partial sum is then passed on to the next column and a new partial sum is received from the previous column. The last column computes a complete Shapesum every 16 cycles (one column). The final correlation of the Bright and Surround templates with the thresholded chip data works similarly except there are two correlations (one for each template).

Intermediate hit values are stored in a table, referred to as the hit-table, in one of the local memories. Each location in the table corresponds to an x-y offset of a chip, the origin of a single correlation. For each offset, if a chunk "hits", then the corresponding location in this table is incremented. Thus the table contains the accumulated hit values for all chunks and all offsets that have been computed to that point.

Hits are computed according to Equation 1. First, each B<sub>sum</sub> and S<sub>sum</sub> value is compared to its corresponding minimum value. Second, the threshold value corresponding to each B<sub>sum</sub> and S<sub>sum</sub> is checked to see if it is between a certain minimum and maximum value. For reasons of efficiency, the threshold value is actually examined earlier in the process and a zero for the threshold is stored in lookup-table memory if it is out of bounds. This works correctly because if the

threshold is zero, it will cause the B<sub>sum</sub> to be zero, which will in turn cause the B<sub>sum</sub> comparison to fail. Otherwise, if all three of these tests come back true then a hit has been found for the corresponding offset (see Equation 1) and the corresponding location in the hit-table is incremented. After the 40 templates are tested against the same chip the two offsets with the highest accumulated hit values are written into memory where the host computer can read them. This is accomplished by examining the hit values during this process and retaining the top two values in special memory locations. These final two hit values (which represent the top two orientations for a specific class) are used in the FI step.

For the SPLASH 2 board, as with most FPGA systems, partitioning is a major issue. The design needed to be modular so that different design modules could be reassigned to different FPGAs as necessary. This is where the column modules were so valuable (see Figure 8).

#### 4.4 Special Features

This implementation has several notable characteristics. They include control distribution, modular design for partitioning and memory utilization.

#### 4.4.1 Distributed Control

The control in this system is distributed throughout the array. Each column module has it's own state machine based control. Module synchronization is achieved by distributing a control token through the pipeline along with the data. When a module receives this signal, it resets its internal state machines and retrieves template data from its local memory. A memory controller resides in each processing element (FPGA) to retrieve template data and give memory access to all other modules.

## 4.4.2 Modular Design (Design for Partitioning)

Each column in both the Shapesum and final correlation use totally self contained modules that can be easily migrated from processing element to processing element. This was done to simplify the partitioning onto Splash 2 [13]. Memory data had to be carefully partitioned as well so that the data could follow the module to which it applied. The regularity of the design was an important concern; it allowed the placement of specific circuit modules to be dictated by the requirements of the algorithm and not by the limited interconnect of the platform. There are 16 identical

modules in the Shapesum and 16 more identical modules in the final correlation. Along with these there is a divide, a hit accumulator and 2 delay modules (see Figure 8).

#### 4.4.3 Memory Usage

The memories in SPLASH 2 serve several purposes. The template information is stored in them. They are used to implement video shift registers that correct for the latency incurred during threshold computation. These shift registers require that two memories be used in tandem because every clock cycle a new pixel (8 bits) had to be written to memory and a delayed pixel had to be read from memory. The bandwidth of one memory was such that it can handle two pixels (load and store) every three cycles. Thus one memory would delay two pixels and skip two pixels, while the other memory would delay the two pixels that the first memory skipped and skip the two pixels that the first memory delayed. The divide unit and the final result including the accumulated hit values are also stored in memory.

#### 4.5 Performance Metrics

There are many metrics that could be used to measure the value of this implementation. This section is devoted to discussing some of these metrics.

#### 4.5.1 Performance

This implementation runs at a frequency of 19 MHz using a test template that tests all column modules. Xdelay (a Xilinx timing tool) reports a guaranteed frequency of 13.2 MHz. Designs that will run in the 10 to 20 MHz range are typical [8, 10].

Using the above frequency a single system could process one orientation every .487 seconds (.701 seconds using a 13.2 MHz clock).

$$\frac{128 \ col \times (128 - 15) \ row \times 16 \frac{pix}{col}}{19 \ MHz} \times 40 \frac{Chunks}{Orient} = \\ (12 \ ms/Chunk) \times 40 \frac{Chunks}{Orientation} = \\ 487 \ ms @ 19 \ MHz$$

or

$$\frac{128 \ col \times (128-15) \ row \times 16 \frac{pix}{col}}{13.2 \ MHz} \times 40 \frac{Chunks}{Orient} = \\ (17.5 \ ms/Chunk) \times 40 \frac{Chunks}{Orientation} = \\ \hline (701 \ ms @ 13.2 \ MHz)$$

Figure 8: SPLASH 2 Implementation.

Using a brute force approach it takes 59 seconds to compute the same data on an HP 770 (110 MHz). That is two orders of magnitude slower. On one SPLASH 2 board two processing units can be installed yielding the ability to process 1 orientation (40 chunks) every .244 seconds (.350 seconds at 13.2 MHz).

#### 4.5.2 Multi-board Splash 2

If a 16-board system were used then 256 processing elements would be available, this would make 42 processing units (256 PEs ÷ 6 PE per PU) and 42× the throughput. Thus one orientation can be processed every 11.6 ms (16.7 ms at 13.2 MHz). This is equal to covering 86 orientation per second (60 orientations per second at 13.2 MHz).

#### 4.5.3 Memory Bandwidth

The distributed memory and aggregate memory bandwidth is what makes this implementation possible. Because the memory is distributed to each chip this implementation can be extended to a multi-board system quite easily. Consider that a processing unit consists of 6 FPGAs and their corresponding memories. Each processing unit performs 10 reads and 13 writes each 16 clock cycles. The SPLASH 2 memories require 3 clock cycles to perform a read and a write for a total available bandwidth of 2 reads and 2 writes every cycle (\frac{6 memories}{3 cycles}). Thus a processing unit consumes approximately 1/2 of the available memory bandwidth. If there were only two or three memories available for the six-chip system this implementation would not be possible.

#### 4.5.4 Memory stored templates

The decision to use statically configured hardware and memory-stored templates was made early in the design process. Another approach would be to use hard-coded templates, e.g., hardware with the template data compiled in as constants. A hard-coded template implementation could possibly use less hardware by removing unused accumulators and template reading logic, however it would require the hardware to be reconfigured during run-time in order to switch templates. This would take significantly longer than the memory read done in the memory-stored template version. The SPLASH 2 system requires approximately 17 ms per chip to configure. The system would have to be reconfigured each time a new template was used. In order to process one orientation the system would have to be configured 40 different times. This would adversely impact system throughput. In fact even if the system could be reconfigured in one cycle the performance wouldn't improve because the time spent reading templates from memory is hidden while the pipeline is initially filling (during the flush cycles). There are other advantages as well. Design time is simplified because new hardware bit streams don't have to be generated and tested to use new templates. Re-compilation may improve hardware utilization, however that would come at a cost of repartitioning difficulty.

#### 5 Future work

In the future, additional related research will be conducted on possible improvements to the implementation described in this paper. In addition, alternative implementations that are not currently possible with the SPLASH 2 platform are under examination. Finally, work is underway on a bit-serial version of this implementation.

#### 5.1 Splash 2 Improvements

Although SPLASH 2 was suitable for this project, there are many possible architectural improvements that could be made that would increase performance significantly. A faster memory interface that supports a two-cycle read-write operation or perhaps a dual-ported memory interface would provide improved memory bandwidth. A larger processing element would give more resources and make implementations more flexible. Updated VHDL libraries that conform to standard data types would help design portability and simplicity.

If chip-to-chip I/O were increased on SPLASH 2 a full column could be processed each clock cycle. This would require at least 339 I/O pins ([128 pixel bits + 13 bit partial sum + 8 bit threshold + 2 bits of control] × 2 (in and out) + 16-bit memory data + 21-bit memory address = 339 pins). The current chips (Xilinx 4010) has enough logic and routing to process an entire column at one time. If this kind of I/O bandwidth were available [14] the system would consume 2 SPLASH 2 boards but would have 16 times the throughput because 16 times as much data would be processed each clock cycle.

Another option would be to distribute the *chip* image to each FPGA memory and have a wide memory data path. This would require at least 195 I/O pins ([13 bit partial sum + 8 bit threshold + 2 bit control]  $\times$  2 (in and out) + 128 bit memory data path + 21 bit memory address = 195) but would have the same throughput.

#### 5.1.1 Interface Improvements

The current implementation assumes that all data are loaded on the SPLASH 2 board before processing commences. A more realistic implementation would stream data to the system as it is produced. Thus, DMA channels or other high-performance I/O hardware, if added to the system, would make performance more sustainable across multiple images.

#### 5.2 Other implementations

There are several ways this algorithm could be implemented. The most obvious way is to to a full parallel version that looks at a full 16×16 pixels at a time. Another is a linear systolic version that looks at one pixel at a time. A linear systolic implementation was designed because SPLASH 2 is organized that way.

This implementation takes a relatively brute-force approach and feeds the entire chip into the system for processing. Whether or not a given pixel actually contributes to the calculation is determined after

the image data are already in the pipeline. Other approaches may take a more selective approach and only access image pixels that actually contribute to the calculation. This may reduce overall memory bandwidth requirements and suggest other implementation strategies. An implementation that only examined pixels that will be used could potentially give a performance increase when correlating the Bright template because the majority of pixels in the template represent chip locations that do not contribute to the computation. However, such an approach would require a complicated control scheme and may not map well onto SPLASH 2.

Here at BYU there is ongoing work targeting 3 different FPGA architectures, each looking to better understand the hardware and ATR algorithms. These include a bit-serial version targeted at National Semiconductors Clay FPGA and a Xilinx 6200. Another project is looking at a full parallel implementation targeting an Altera Flex-10K part.

#### 6 Conclusion

SPLASH 2 is organized as a linear array of FPGA chips each connected to a separate memory. Because of this, applications can only make effective use of SPLASH 2 resources if (1) individual circuit modules are small enough to easily fit into the limited resources available within a single FPGA (Xilinx 4010) and (2) circuit modules can be grouped together in such a way that the interconnect requirements between modules on separate chips will fit in the limited chip-to-chip interconnect available on SPLASH 2.

Both of these requirements were met in this application by carefully organizing all correlations (both Shapesum and final correlation) as independent column-oriented processing elements (PEs). Each PE occupied only a small amount of FPGA resources thereby making it possible to place several PEs into a single FPGA. PEs that are integrated on a single FPGA communicate via the available on-chip FPGA routing; PEs that are located on different FPGAs can easily communicate via the limited inter-chip routing on SPLASH 2.

This repetitive, column-oriented organization also eases the programming of SPLASH 2 considerably. Much of the VHDL code was reused and because the fourth and fifth chips are identical (because of the linear column layout, see Figure 8) it was possible to down-load the same bit-stream into both chips.

This column organization presents a good tradeoff between a fully parallel design and a design that fits within the restrictions of the SPLASH 2 architecture. Each column operates in parallel computing a column sum that when complete is passed onto its neighboring column. While it is possible to achieve higher levels of parallelism, it is likely that such designs will require denser interconnect than SPLASH 2 is capable of providing (see Section 5.1). By limiting communication to only adjacent columns, significant parallelism is still achieved with only moderate amounts of interconnect.

This implementation can also take advantage of SPLASH 2's extensibility giving it even higher performance capability. Simply by passing the pixel data from chip 6 (see Figure 8) to the next chip on the SPLASH 2 board and configuring the next 6 chips in the array with the same bit stream as the first 6 chips the throughput on the system would be doubled. This extensibility can also be expanded to multiple boards giving a linear increase in system throughput.

#### References

- S. Trimberger. A reprogrammable gate array and applications. Proceedings of the IEEE, pages 1030-1041, July 1993.

- [2] National Semiconductor. Configurable Logic Array (CLAy). National Semicondutor, 1993.

- [3] J. Villasenor, B. Schoner, K. Chia, and C. Zapata. Configurable computing solutions for automatic target recognition. In J. Arnold and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 70-79, Napa, CA, April 1996.

- [4] A. L. Abbott, P. M. Athanas, L. Chen, and R. L. Elliott. Finding lines and building pyramids with Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 155-161, Napa, CA, April 1994.

- [5] J. M. Arnold. The Splash 2 software environment. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 88-93, Napa, CA, April 1993.

- [6] P. Athanas and A. Abbott. Image processing on a custom computing platform. In R. Hartenstein and M. Z. Servit, editors, Field-Programmable Logic: Architectures, Synthesis and Applications. 4th International Workshop on Field-Programmable Logic and Applications, pages 156-167, Prague, Czech Republic, September 1994. Springer-Verlag.

- [7] M. Gokhale and B. Schott. Data parallel C on a reconfigurable logic array. Journal of Supercomputing, 9(3):291-313, 1994.

- [8] P. Graham and B. Nelson. A hardware genetic algorithm for the travelling salesman problem on SPLASH 2. In W. Moore and W. Luk, editors, Field-Programmable Logic and Applications, pages 352-361, Oxford, England, August 1995. Springer.

- [9] D. T. Hoang. Searching genetic databases on Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 185-191, Napa, CA, April 1993.

- [10] D. V. Pryor, M. R. Thistle, and N. Shirazi. Text searching on Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 172-177, Napa, CA, April 1993.

- [11] N. Ratha, A. Jain, and D. Rover. Convolution on Splash 2. In D. A. Buell and K. L. Pocek, editors, Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, pages 204-213, Napa, CA, April 1995.

- [12] J. M. Arnold, D. A. Buell, and E. G. Davis. Splash 2. In Proceedings of the 4th Annual ACM Symposium on Parallel Algorithms and Architectures, pages 316-324, June 1992.

- [13] Benjamin W. Wah. Systolic arrays-from concept to implementation. IEEE Journal Computer, 20(7):12-17, July 1987.

- [14] Altera. Altera-Embedded Programmable Logic Family-Flex 10K Data Sheet. Altera, 1995.

## Attachment 2C

Enter your location: boston spa Find libraries

Submit a complete postal address for best results.

Displaying libraries 1-6 out of 207 for all 8 editions (Boston Spa, Wetherby LS23, UK)

\*\*First < Prev 1 2 3 Next > Last >>

Library

Held formats

Distance

1. The British Library, On Demand The British Library, Document Supply, Boston Spa

Book

2 miles

Library info

Wetherby, West Yorkshire, LS23 7BQ United

Add to favorites

MAP IT

#### Kingdom

| 2.   | University of Sheffield                     |      |                     |                                     |

|------|---------------------------------------------|------|---------------------|-------------------------------------|

|      | Sheffield University                        | Book | 37 miles            | Library info                        |

|      | Sheffield, S10 2TN United Kingdom           | Soon | MAP IT              | Ask a librarian Add to favorites    |

| 3.   | University of Liverpool, Sydney Jones       |      |                     |                                     |

| 1.50 | Library                                     |      | 75 miles            | Library info                        |

|      | Liverpool, L69 3DA United Kingdom           | Book | MAP IT              | Ask a librarian                     |

|      | Liverpoon, 200 SBA Officed Kingdom          |      |                     | Add to favorites                    |

| 4.   | University of Gloucestershire               |      |                     |                                     |

|      | Francis Close Hall Campus Library, Oxstalls |      | 440                 | Library info                        |

|      | Campus Library, Park Campus Library         | Book | 143 miles           | Ask a librarian                     |

|      | Cheltenham, GL50 2RH United Kingdom         |      |                     | Add to favorites                    |

| 5.   | University of Essex                         |      |                     |                                     |

|      | The Albert Sloman Library                   | Book | 170 miles<br>MAP IT | Library info                        |

|      | Colchester, CO4 3SQ United Kingdom          | BOOK |                     | Add to favorites                    |

| 6.   | London Metropolitan University              |      | 171 miles           | 116                                 |

|      | London, N7 8DB United Kingdom               | Book |                     | Library info Search at this library |

|      | SSS Officed Kingdom                         |      | MAP IT              | Add to favorites                    |

|      |                                             |      |                     |                                     |

« First « Prev 1 2 3 Next » Last »

#### - Details

Genre/Form:

Conference papers and proceedings

Congresses

Material Type:

Conference publication, Internet resource

**Document Type:**

Book, Internet Resource

All Authors /

Kenneth L Pocek; Jeffrey M Arnold; IEEE Computer Society. Technical Committee on Computer

Contributors:

Architecture.

Find more information about: Kenneth L Pocek Go

ISBN:

0818681594 9780818681592 0818681608 9780818681608 0818681616 9780818681615

**OCLC Number:**

37949175

Notes:

"IEEE Computer Society order number PR08159"--Title page verso. "IEEE order plan catalog number 97TB100186"--Title page verso.

Description:

x, 250 pages : illustrations ; 28 cm

Other Titles:

FPGAs for Custom Computing Machines, 1997, proceedings, The 5th Annual IEEE Symposium on.

FCCM'97

5th Annual IEEE Symposium on Field-Programmable Custom Computing Machines Fifth Annual IEEE Symposium on Field-Programmable Custom Computing Machines IEEE Symposium on FPGAs for Custom Computing Machines

FPGAs for Custom Computing Machines

Responsibility:

sponsored by the IEEE Computer Society, IEEE Computer Society Technical Committee on Computer

Architecture ; [edited by Kenneth L. Pocek and Jeffrey Arnold].

#### = Reviews

#### User-contributed reviews

Add a review and share your thoughts with other readers.

- Tags

Add tags for "Proceedings, the 5th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, April 16-18, 1997, Napa Valley, California". Be the first.

Be the first.

- Similar Items

Related Subjects: (4)

Field programmable gate arrays -- Congresses.

Computer engineering -- Congresses.

Computer engineering.

Field programmable gate arrays.

+ Linked Data

## Attachment 2D

Close this window to return to the catalogue

## **EXPLORE THE BRITISH LIBRARY**

#### Item Details

**FMT** BK LDR caa a22003133u 4500 001 006410603 971111s1997 xxu || 800 100 ||eng 020 |a 0818681594 (pbk) |a 0818681608 (casebound) 020 |a 0818681616 (microfiche) 020 040 la Uk Ic Uk Ja Field-programmable custom computing machines (Annual symposium) In (5th : Jd 1997 CNF Apr : [c Napa Valley, CA] 24514 |a The 5th Annual IEEE symposium on field-programmable custom computing machines. |b IEEE Computer Society Press, |c 1997. la text |2 rdacontent 337 la unmediated |2 rdamedia 338 |a volume |2 rdacarrier 653 la FPGAs 653 la custom computing machines 653 la IEEE |a computer architecture 653 653 la FCCM 653 |a field-programmable custom computing machines 7001 |a Pocek, Kenneth L., |e Ed. 7001 |a Arnold, Jeffrey, |e Ed. 7102 |a IEEE Computer Society. |b Technical Committee on Computer Architecture. 945 |a IEEE symposium on FPGAs for custom computing machines, ISSN 1082-3409; 5th 85241 |a British Library |b DSC |j 4363.086450 |i 5th 1997 SYS 006410603

Accessibility Terms of use @ The British Library Board

HSILIN

Guest My workspace Personal settin

Catalogues

Collections

Discover

Services

Visiting

About

Information for...

### Explore the British Library

Explore Home

Feedback

Tags

Request Other Items

My Reading Room Requests

Help

Main catalogue

Our website

Explore Further

Basket

5th annual ieee symposium on fpgas for custom computir

Everything in this catalogue

Advanced search

Back to results list

## The 5th Annual IEEE symposium on field-programmable custom computing machines.

IEEE Computer Society Press, 1997.

Details

I want this

Notes & Tags

Actions \*

Title: The 5th Annual IEEE symposium on field-programmable custom computing

machines.

Contributor: Kenneth L. Pocek Ed.;

Jeffrey Arnold Ed.;

IEEE Computer Society. Technical Committee on Computer Architecture.

Subjects: FPGAs; custom computing machines; IEEE; computer architecture;

FCCM; field-programmable custom computing machines

Rights: Terms governing use: Current copyright fee: GBP23.57

Publication Details: IEEE Computer Society Press, 1997.

Language: English

Identifier: ISBN 0818681594 (pbk); System number: 006410603; ISBN 0818681608 (casebound); System number: 006410603; ISBN 0818681616 (microfiche); System

number: 006410603

Shelfmark(s): Document Supply 4363.086450 5th 1997

UIN: BLL01006410603

Back to results list

#### Links