|          | E DATENT | TDIAL AND | ADDEAL DO |

|----------|----------|-----------|-----------|

| OKE I HI | t PAIENI | IKIAL AND | APPEAL BO |

|          |          |           |           |

|          |          |           |           |

# **TABLE OF CONTENTS**

|      |                                        | Page |

|------|----------------------------------------|------|

| I.   | INTRODUCTION                           | 1    |

| II.  | BACKGROUND AND QUALIFICATIONS          | 1    |

| III. | PRELIMINARIES                          | 3    |

| IV.  | OPINION REGARDING INDIVIDUAL DOCUMENTS | 19   |

| CON  | NCLUSION                               | 39   |

I, James L. Mullins, hereby declare under penalty of perjury:

#### I. INTRODUCTION

- 1. I have knowledge of the facts and opinions set forth in this declaration, I believe them to be true, and if called upon to do so, I would testify competently to them. I have been warned that willful false statements and the like are punishable by fine or imprisonment, or both.

- 2. I am a retired academic librarian working as the Founder and Owner of the firm Prior Art Documentation Librarian Services, LLC at 106 Berrow, Williamsburg, VA 23188. Attached as Appendix A is a true and correct copy of my Curriculum Vitae describing my background and experience. Further information about my firm, Prior Art Documentation Librarian Services, LLC (PADLS), is available at <a href="https://www.priorartdoclib.com">www.priorartdoclib.com</a>.

- 3. I have been retained by Sidley Austin LLP to authenticate and establish the dates of public accessibility of certain documents for use in one or more *inter partes* review proceedings. For this service, I am being paid my usual hourly fee of \$185/hour. My compensation in no way depends on the substance of my testimony or the outcome of the proceeding.

## II. BACKGROUND AND QUALIFICATIONS

4. Presently, I am the Dean of Libraries Emeritus and Esther Ellis Norton Professor Emeritus, Purdue University.

- 5. I was previously employed as follows:

- Dean of Libraries and Professor & Esther Ellis Norton Professor, Purdue University, West Lafayette, IN, 2004-2017.

- Assistant/Associate Director for Administration, Massachusetts Institute of Technology Libraries, Cambridge, MA, 2000-2004.

- University Librarian and Director, Falvey Memorial Library, Villanova University, Villanova, PA, 1996-2000.

- Director of Library Services, Indiana University South Bend, South Bend, IN, 1978-1996. Part-time instructor, School of Library and Information Science, Indiana University, Bloomington, IN, 1979-1996.

- Associate Law Librarian, and associated titles, Indiana University School of Law, Bloomington, IN, 1974-1978.

- Catalog Librarian, Assistant Professor, Georgia Southern College (now University), Statesboro, GA, 1973-1974.

- 6. Over the course of my career as a librarian, instructor of library science, author of scholarly publications, and presenter at national and international conferences, I have had experience with catalog records and online library management systems built around Machine-Readable Cataloging (MARC) standards.

- 7. In the course of more than forty-four years as an academic librarian and scholar, I have been an active researcher. In my years as a librarian I have facilitated the research of faculty colleagues either directly or through the provision of and access to the requisite print and/or digital materials and services at the universities I worked. I have kept current on the professional library science literature and served

on the editorial board of the most prominent library journal, *College and Research Libraries*. This followed service as the chair of the Research Committee of the Association of College and Research Libraries (ACRL), a division of the American Library Association (ALA). As an academic library administrator I have had responsibility to insure that students were educated to identify, locate, assess and integrate information garnered from library resources.

#### III. PRELIMINARIES

- 8. Scope of this declaration. I am not a lawyer and I am not rendering an opinion on the legal question of whether any particular document is, or is not, a "printed publication" under the law.

- 9. I am, however, rendering my expert opinion on the authenticity of the documents referenced herein and on when and how each of these documents was disseminated or otherwise made available to the extent that persons interested and ordinarily skilled in the subject matter or art, exercising reasonable diligence, could have located the documents no later than September 11, 2007.

- 10. *Materials considered*. In forming the opinions expressed in this declaration, I have reviewed the documents and attachments referenced herein. These materials are records created in the ordinary course of business by publishers, libraries, indexing services, and others. From my years of experience, I am familiar with the process for creating many of these records, and I know these records are

created by people with knowledge of the information in the record. Further, these records are created with the expectation that researchers and other members of the public will use them. All materials cited in this declaration and its attachments are of a type that experts in my field would reasonably rely upon and refer to in forming their opinions.

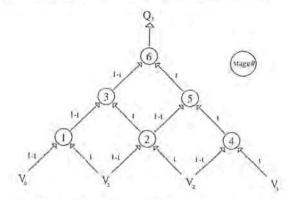

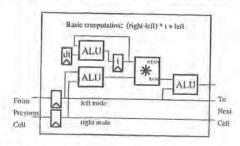

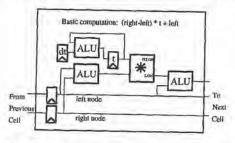

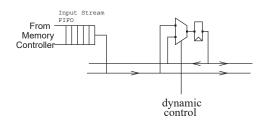

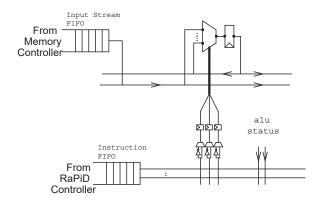

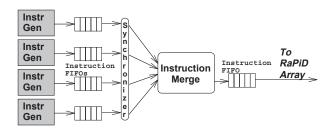

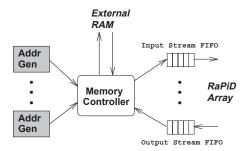

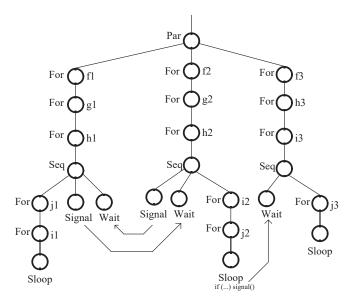

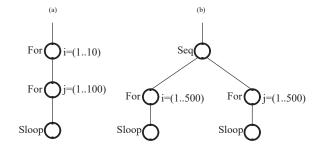

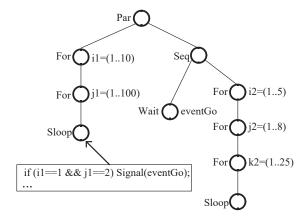

Persons of ordinary skill in the art. I have been informed by counsel 11. that a person of ordinary skill in the art in the field of U.S. Patent Nos. 7,225,324 ("324 Patent") and 7,620,800 ("800 Patent") in the 2002 time frame would have had an advanced degree in electrical or computer engineering, or computer science with substantial study in computer architecture, hardware design, and computer algorithms, and at least three years' experience working in the field. Alternatively, that person would have had a bachelor's degree covering those disciplines and at least four years working the field. Such a person would have been knowledgeable about the programming, design and operation of computer systems based on reconfigurable components such as FPGAs (field programmable gate arrays) and CPLDs (complex programmable logic devices), including computer systems for performing systolic and data driven calculations. That person would also have been familiar with hardware description languages such as VHDL that could be used to configure FPGAs and CPLDs that serve as components of reconfigurable computer systems. Finally, such a person would also have been familiar with various other

areas of technology that by 2002 had relied on high performance and parallel computing systems.

12. I am told that Patent Owner claims a priority date of October 31, 2002. By that date, a person of ordinary skill would have had access to a vast array of longestablished print resources in the field of field programmable gate array based systems and to a rich and fast changing set of online resources providing indexing information, abstracts, and full text services for persons interested in field programmable gate array based systems.

# **Library Catalog Records**

13. Some background on MARC (Machine-Readable Cataloging) formatted records, OCLC, and WorldCat is helpful to understand the library catalog records discussed in this declaration. I am fully familiar with the library cataloging standard known as the MARC standard, which is an industry-wide standard method of storing and organizing library catalog information. MARC practices have been consistent since the MARC format was developed by the Library of Congress in the 1960s, and by the early 1970s became the U.S. national standard for disseminating bibliographic data. By the mid-1970s, MARC format became the international

<sup>&</sup>lt;sup>1</sup> The full text of the standard is available from the Library of Congress at <a href="http://www.loc.gov/marc/bibliographic/">http://www.loc.gov/marc/bibliographic/</a>.

standard, and persists through the present. A MARC-compatible library is one that has a catalog consisting of individual MARC records for each of its items. Today, MARC is the primary communications protocol for the transfer and storage of bibliographic metadata in libraries.<sup>2</sup> The MARC practices discussed below were in place during the mid to late 1990s timeframe relevant to the documents referenced herein.

14. Similarly, OCLC practices have been consistent since the 1970s through the present, and the OCLC practices discussed below were in place during the mid to late 1990s timeframe relevant to the documents referenced herein. The OCLC was created "to establish, maintain and operate a computerized library

<sup>&</sup>lt;sup>2</sup> Almost every major library in the world is MARC-compatible. *See, e.g., MARC Frequently Asked Questions (FAQ)*, LIBRARY OF CONGRESS, <a href="https://www.loc.gov/marc/faq.html">https://www.loc.gov/marc/faq.html</a> (last visited January 24, 2018) ("MARC is the acronym for MAchine-Readable Cataloging. It defines a data format that emerged from a Library of Congress-led initiative that began nearly forty years ago. It provides the mechanism by which computers exchange, use, and interpret bibliographic information, and its data elements make up the foundation of most library catalogs used today."). MARC is the ANSI/NISO Z39.2-1994 (reaffirmed 2009) standard for Information Interchange Format.

network and to promote the evolution of library use, of libraries themselves, and of librarianship, and to provide processes and products for the benefit of library users and libraries, including such objectives as increasing availability of library resources to individual library patrons and reducing the rate of rise of library per-unit costs, all for the fundamental public purpose of furthering ease of access to and use of the ever-expanding body of worldwide scientific, literary and educational knowledge and information." Among other services, OCLC and its members are responsible for maintaining the WorldCat database (<a href="http://www.worldcat.org/">http://www.worldcat.org/</a>), used by independent and institutional libraries throughout the world.

15. A complementary library organization, Research Library Group (RLG) was formed in 1974 by several major research universities including Yale, New York Public, Columbia, and Harvard as an alternative to OCLC. RLG created a database of bibliographic records and holdings identified as RLIN that used the MARC format in creating its OPAC and holding records at member institutions. RLG merged with OCLC in 2006 to form one unified library bibliographic, member driven utility.

<sup>3</sup> Third Article, Amended Articles of Incorporation of OCLC Online Computer Library Center, Incorporated (available at <a href="http://www.oclc.org/en-us/councils/documents/amended\_articles.html">http://www.oclc.org/en-us/councils/documents/amended\_articles.html</a>).

- Libraries world-wide have used the machine-readable MARC format 16. for catalog records. MARC formatted records have provided a variety of subject access points based on the content of the document being cataloged. A MARC record comprises several fields, each of which contains specific data about the work. Each field is identified by a standardized, unique, three-digit code corresponding to the type of data that follows. For example, a work's title is recorded in field 245, the primary author of the work is recorded in field 100, an item's International Standard Book Number ("ISBN") is recorded in field 020, an item's Library of Congress call number is recorded in field 050, and the publication date is recorded in field 260 under the subfield "c." If a work is a periodical, then its publication frequency is recorded in field 310, and the publication dates (e.g., the first and last publication) are recorded in field 362, which is also referred to as the enumeration/chronology field.

- 17. The MARC Field 040, subfield a, identifies the library or other entity that created the original catalog record for a given document and transcribed it into machine readable form. The MARC Field 008 identifies the date when this first catalog record was entered on the file. This date persists in all subsequent uses of the first catalog record, although newly-created records for the same document, separate from the original record will show a new date. It is not unusual to find multiple

catalog records for the same document, typically this is the result of the merger of RLG and OCLC.

- 18. MARC records also include several fields that include subject matter classification information. An overview of MARC record fields is available through the Library of Congress at <a href="http://www.loc.gov/marc/bibliographic/">http://www.loc.gov/marc/bibliographic/</a>. For example, 6XX fields are termed "Subject Access Fields." Among these, for example, is the 650 field; this is the "Subject Added Entry Topical Term" field. See <a href="http://www.loc.gov/marc/bibliographic/bd650.html">http://www.loc.gov/marc/bibliographic/bd650.html</a>. The 650 field is a "[s]ubject added entry in which the entry element is a topical term." Id. These entries "are assigned to a bibliographic record to provide access according to generally accepted thesaurus-building rules (e.g., Library of Congress Subject Headings (LCSH), Medical Subject Headings (MeSH))." Id. Thus, a researcher might discover material relevant to his or her topic by a search using the terms employed in the MARC Fields 6XX.

- 19. The 9XX fields are not part of the standard MARC 21 format.<sup>5</sup> OCLC has defined these 9XX fields for use by the Library of Congress and for internal OCLC use: 936, 938, 956, 987, 989, and 994. 955 is used by the Library of Congress

<sup>&</sup>lt;sup>4</sup> See <a href="http://www.loc.gov/marc/bibliographic/bd6xx.html">http://www.loc.gov/marc/bibliographic/bd6xx.html</a>.

<sup>&</sup>lt;sup>5</sup> See <a href="https://www.oclc.org/bibformats/en/9xx.html">https://www.oclc.org/bibformats/en/9xx.html</a>.

to track the progress of a new acquisition from the time it is submitted for Cataloging in Publication (CIP) review until it is published and fully cataloged and available for use within the Library of Congress. Fields 901-907, 910, and 945-949 have been defined by OCLC for local use and will pass OCLC validation. Fields 905 or 910 are often used by an individual library for internal processing purposes, for example the date of cataloging and the initials of the cataloger.

20. Further, MARC records include call numbers, which themselves include a classification number. For example, the 050 field is the "Library of Congress Call Number." A defined portion of the Library of Congress Call Number is the classification number, and "source of the classification number is *Library of Congress Classification* and the *LC Classification-Additions and Changes.*" *Id.* Thus, included in the 050 field is a subject matter classification. Each item in a library has a single classification number. A library selects a classification scheme (*e.g.*, the Library of Congress Classification scheme just described or a similar scheme such as the Dewey Decimal Classification scheme) and uses it consistently. When the Library of Congress assigns the classification number, it appears as part of the 050 field. If a local library assigns the classification number, it appears in a

<sup>6</sup> See <a href="http://www.loc.gov/marc/bibliographic/bd050.html">http://www.loc.gov/marc/bibliographic/bd050.html</a>.

090 field. In either scenario, the MARC record includes a classification number that represents a subject matter classification.

- 21. WorldCat is the world's largest public online catalog, maintained by the Online Computer Library Center, Inc., or OCLC, and built with the records created by the thousands of libraries that are members of OCLC. OCLC has provided bibliographic and abstract information to the public based on MARC records through its OCLC WorldCat database. WorldCat requires no knowledge of MARC tags and code and does not require a log-in or password. WorldCat is easily accessible through the World Wide Web to all who wish to search it; there are no restrictions to be a member of a particular community, etc. The date a given catalog record was created (corresponding to the MARC Field 008) appears in some detailed WorldCat records as the Date of Entry but not necessarily all. Whereas WorldCat records are widely available, the availability of MARC formatted records varies from library to library and when made available will be identified as MARC record or librarian/staff view.

- 22. When an OCLC member institution acquires a work, it creates a MARC record for this work in its computer catalog system in the ordinary course of its business. MARC records created at the Library of Congress were historically tapeloaded into the OCLC database through a subscription to MARC Distribution Services daily or weekly. Once the MARC record is created by a cataloger at an

OCLC member institution or is tape-loaded from the Library of Congress, the MARC record is then made available to any other OCLC members online, and therefore made available to the public. Accordingly, once the MARC record is created by a cataloger at an OCLC member institution or is tape-loaded from the Library of Congress or another library anywhere in the world, any publication corresponding to the MARC record has been cataloged and indexed according to its subject matter such that a person interested in that subject matter could, with reasonable diligence, locate and access the publication through any library with access to the OCLC WorldCat database or through the Library of Congress.

23. When an OCLC member institution creates a new MARC record, OCLC automatically supplies the date of creation for that record. The date of creation for the MARC record appears in the fixed field (008), characters 00 through 05. The MARC record creation date reflects the date on which the item was first acquired or cataloged. Initially, field 005 of the MARC record is automatically populated with the date the MARC record was created in year, month, day format (YYYYMMDD) (some of the newer library catalog systems also include hour, minute, second (HHMMSS)). Thereafter, the library's computer system may automatically update the date in field 005 every time the library updates the MARC record (e.g., to reflect that an item has been moved to a different shelving location within the library).

- 24. Once one library has cataloged and indexed a publication by creating a MARC record for that publication, other libraries that receive the publication do not create additional MARC records—the other libraries instead rely on the original MARC record. They may update or revise the MARC record to ensure accuracy, but they do not replace or duplicate it. This practice does more than save libraries from duplicating labor. It also enhances the accuracy of MARC records. Further, it allows librarians around the world to know that a particular MARC record is authoritative (in contrast, a hypothetical system wherein duplicative records were created would result in confusion as to which record is authoritative).

- 25. The date of creation of the MARC record by a cataloger at an OCLC member institution reflects when the underlying item is accessible to the public. Upwards of two-thirds to three-quarters of book sales to libraries come from a jobber or wholesaler for online and print resources. These resellers make it their business to provide books to their customers as fast as possible, often providing turnaround times of only a single day after publication. Libraries purchase a significant portion of the balance of their books directly from publishers themselves, which provide delivery on a similarly expedited schedule. In general, libraries make these purchases throughout the year as the books are published and shelve the books as soon thereafter as possible in order to make the books available to their patrons.

Thus, books are generally available at libraries across the country within just a few weeks of publication.

## **Monograph Publications**

26. Monograph publications are written on a single topic, presented at length and distinguished from an article and include books, dissertations, and technical reports. A library typically creates a catalog record when the monograph is acquired by the library. First, it will search OCLC to determine if a record has already been created by the Library of Congress or a contributing member library. If the record is found in OCLC, the record is downloaded into the library's LMS (Library Management System) that includes typically the acquisitions, cataloging, and circulation integrated functions. Once the item is downloaded into the library's LMS, the library adds its identifier to the OCLC database so when a search is completed on WorldCat, the library will be indicated as an owner of the title. With the creation of the record in the LMS it is searchable and viewable through the library Online Public Access Catalog (OPAC), by author, title, and subject heading, at the library and from anywhere in the world through the internet. The OPAC also connects with the circulation function of the library which typically indicates whether the book, dissertation, tech report is available, in circulation, etc., with its call number and location in a specific departmental/disciplinary library. The OPAC not only provides immediate bibliographic access on site, it also facilitates

interlibrary loan of items, that is, the loan of an item from one library to another to meet a research need.

## Ownership and Date Stamp

27. Every library sets its own practice or policy on whether-or-not to date stamp, but all will have an ownership stamp somewhere in the publication — typically on the cover page, verso of the cover page, or a designated page within the publication, but sometimes even on the top, side, or bottom edge of the monograph. The ownership and date stamp can also vary from one library to another when the date stamp is entered on the monograph. It could occur when received in acquisitions after shipment to the library, or it could be at time of cataloging. Therefore, there could be instances when the date of receipt precedes the cataloging date or vice versa.

#### **Periodicals, Indexes, and Citation Sources**

- a. Publications in Series: Conference Proceedings/Technical Report publications

- 28. A library typically creates a MARC catalog record for a series of closely related publications, such as the proceedings of an annual conference or a technical report when the library receives its first issue and assumes there will be annual or succeeding issues/volumes/reports. When the institution receives subsequent issues/volumes/reports of the series, the issues/volumes/reports are checked in (sometimes using a date stamp), added to the institution's holdings

records, and made available very soon thereafter—normally within a few days of receipt or (at most) within a few weeks of receipt. The initial series record may not reflect all subsequent changes in publication details (including minor variations in title, etc.).

#### b. Indexing

- 29. A researcher may discover material relevant to his or her topic in a variety of ways. One common means of discovery is to search for relevant information in an index of periodical and other publications. Having found relevant material, the researcher will then normally obtain it online, look for it in libraries, or purchase it from the publisher, a bookstore, a document delivery service, or other provider. Sometimes, the date of a document's public accessibility will involve both indexing and library date information. Date information for indexing entries is, however, often unavailable. This is especially true for online indices. Indexing services use a wide variety of controlled vocabularies to provide subject access and other means of discovering the content of documents. The formats in which these access terms are presented vary from service to service.

- 30. Online indexing services commonly provide bibliographic information, abstracts, and full-text copies of the indexed publications, along with a list of the documents cited in the indexed publication. These services also often provide lists of publications that cite a given document. A citation of a document is evidence that

the document was publicly available and in use by researchers no later than the publication date of the citing document.

- 31. <u>IEEE Xplore Digital Library</u>. The Institute of Electrical and Electronics Engineers is the world's largest organization for the advancement of technology, with some 430,000 members in 160 countries. Known by its acronym IEEE, it has created IEEE Xplore Digital Library, which provides access to the contents of over 170 journals, more than 1,400 conference proceedings, some 5,100 technical standards, 2,000 eBooks, and 400 educational courses. More than 3 million documents, dating from 1872, are searchable and available either through subscription or individual purchase.

- 32. <u>Wiley Online Library</u>. Produced by John Wiley & Sons, Wiley Online Library is a collection of online resources covering life, health and physical sciences, the social sciences, and the humanities. It provides access to over 6 million articles from over 1,500 journals and over 19,000 online books.

#### c. Citation Sources

33. <u>Web of Science</u>. Like its print predecessors Science Citation Index, Social Science Citation Index, and Arts and Humanities Citation Index, Web of Science provides thorough coverage of a broad set of disciplines. A Thomson Reuters product, Web of Science indexes 1,700 arts and humanities journals from

1975 to the present, 8,500 scientific journals from 1900 to the present, and some 300 social science journals from 1900 to the present.

- 34. <u>Science Direct</u>. Science Direct, provided by the major publisher Elsevier, is a database of abstracts and articles in the physical sciences and engineering, the life and health sciences, and the social sciences and humanities. It has over 12 million items from 3,500 journals and 34,000 books.

- 35. Scopus. Produced by Elsevier, a major publisher, Scopus is the largest database of abstracts and citations of peer-reviewed literature. Its scope includes the social sciences, science, technology, medicine, and the arts. It includes 60 million records from more than 21,500 titles from some 5,000 international publishers. Coverage includes 360 trade publications, over 530 book series, more than 7.2 million conference papers, and 116,000 books. Records date from 1823.

- 36. Google Scholar. Google Scholar indexes the texts and metadata of scholarly publications across a wide range of disciplines. It includes most peer-reviewed online academic journals, conference papers, theses, technical reports, and other material. Google does not publish the size of the Google Scholar database, but researchers have estimated that it contained approximately 160 million items in 2014 (Enrique Oduña-Malea, et al., "About the size of Google Scholar: playing the numbers," Granada: EC3 Working Papers, 1B: 23 July 2014, available at <a href="https://arxiv.org/ftp/arxiv/papers/1407/1407.6239.pdf">https://arxiv.org/ftp/arxiv/papers/1407/1407.6239.pdf</a>.

#### IV. OPINION REGARDING INDIVIDUAL DOCUMENTS

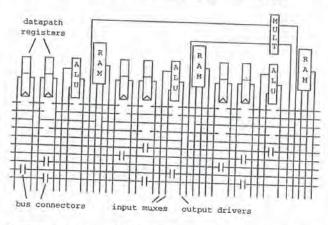

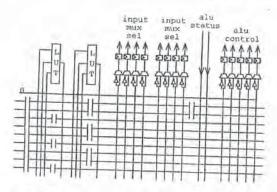

Document 1: Carl Ebeling, et al., "Mapping Applications to the RaPiD Configurable Architecture," IEEE Symposium on FPGAs for Custom Computing Machines. April 16-18, 1997 Napa Valley, California: 106-115.

#### Authentication

- 37. Document 1 is an article by Carl Ebeling, et al., titled "Mapping Applications to the RaPiD Configurable Architecture" presented at the IEEE Symposium on FPGAs for Custom Computing Machines, published in the Proceedings: IEEE Symposium on FPGAs for Custom Computer Machines, held on April 16-18, 1997 Napa Valley, California.

- 38. Attachment 1A was provided to me by Wisconsin TechSeach (WTS) from the Library of Congress. In includes the cover, title page, verso of the title page, table of contents and the article by Carl Ebeling, et al., "Mapping Applications to the RaPiD Configurable Architecture." On the title page is the ownership stamp of the Library of Congress with the check-in date of October 9, 1997. On the verso of the title page is the call number hand written of: TK7895.G36 I35 1997.

- 39. Attachment 1B, downloaded by me, includes Document 1 in PDF format from IEEE Xplore through Purdue University Libraries: <a href="https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/document/624610/">https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/document/624610/</a>.

- 40. Attachment 1A is in a condition that creates no suspicion about its authenticity. Specifically, Attachment 1A is not missing any intermediate pages, the text on each page appears to flow seamlessly from one page to the next, and there

are no visible alterations to the document. Attachment 1A was found within the custody of a library, the Library of Congress – a place where, if authentic, it would likely be found.

41. Based on finding Attachment 1A in a library and Document 1 (Attachment 1B) online at IEEE Xplore, I conclude that Document 1 is an authentic document and that Attachment 1A is an authentic copy of Document 1.

## **Public Accessibility**

- 42. Attachment 1C is the WorldCat record. This record shows that Document 1 is held by 207 libraries world-wide as of July, 2018. Subject access is possible through subject headings: Field Programmable Data Arrays Congresses; Computer Engineering Congresses; and Computer Engineering. Library of Congress is listed as one of the holding libraries among the 207 as of July, 2018.

- 43. Attachment 1D is the Library of Congress MARC record for Document

1. In MARC field 955 is the record of the processing of Document 1. MARC field

955 is used by the Library of Congress to track the progress of a new acquisition

from the time it is submitted for Cataloging in Publication (CIP) review until it is

published and fully cataloged and available for use within the Library of Congress.

In Attachment 1D, MARC field 955 contains the phrase "pb23 11-18-97 to cat,"

which indicates that a Library of Congress librarian noted that Document 1 was sent

to cataloging on November 18, 1997. In addition, MARC field 955 in Attachment

D contains the phrase "jg00 11-26-97." That field further indicates that a librarian noted that Document 1 was sent to the Library of Congress stacks November 26, 1997.

- Attachment 1E is the Library of Congress Online Catalog (OPAC) 44. record. On page 2, this OPAC record indicates that there are two copies of Document 2 available, locatable by call numbers TK7895.G36 I35 1997 or TK7895.G36 I35 1997 FT MEADE. That record states that copy 1, call number TK7895.G36 I35 1997 (the same call number written on Attachment 1A), is available upon request in the Jefferson or Adams Building Reading Rooms. From my familiarity with the Library of Congress' procedures, I would expect that based on this record, any person could request Document 1 be brought to one of the reading rooms for review. A request for photocopies or scans could be made from Document Items do not circulate outside the Reading Rooms except to Members of I conclude from the information in Attachments 1D and 1E that Document 1 would have been publicly accessible by interested persons at the Library of Congress no later than the date it was sent to the stacks, on November 26, 1997.

- 45. Attachment 1F is a paper by Darren C. Cronquist et al., "Specifying and Compiling Applications for RaPiD" from the Proceedings, IEEE Symposium on FPGAs for Custom Computing Machines, April 17, 1998 pp. 116-125. Number 2 of the References on page 116 is Document 1. Downloaded by me on July 5, 2018,

from IEEE Xplore through Purdue University Libraries: <a href="https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/stamp/stamp.jsp?tp=&arnumber=707889">https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/stamp/stamp.jsp?tp=&arnumber=707889</a>.

#### Conclusion

46. Based on the evidence presented here I conclude that Attachment 1A is an authentic copy of Document 1, which is an article published in the Proceedings: IEEE Symposium on FPGAs for Custom Computer Machines, held on April 16-18, 1997 Napa Valley, California. Based on the Library of Congress's records showing the receipt of this document on October 9, 1997, the cataloguing and availability of this document at the end of November of 1997, and the fact this this document was cited in a published article in 1998, it is my opinion that Document 1 was publicly accessible to and in actual use by ordinarily skilled researchers as early as the first part of December, 1997.

Document 2: Michael Rencher and Brad L. Hutchins, "Automated Target Recognition on Splash 2," IEEE Symposium on FPGAs for Custom Computing Machines. April 16-18, 1997 Napa Valley, California: 192-200

#### Authentication

- 47. Document 2 is an article by Michael Rencher and Brad L. Hutchins titled "Automated Target Recognition on Splash 2" presented as a paper at the IEEE Symposium on FPGAs for Custom Computing Machines held on April 16-18, 1997 Napa Valley, California.

- 48. Attachment 2A a true and accurate copy of Document 2 including the cover page, title page, verso of the title page, and table of contents for the 1997 IEEE

Symposium, and the article comprising Document 2. On the cover is the ownership and date stamp of the British Library's Boston Spa facility, November 10, 1997 indicating the date that the British Library received Document 2. Attachment 2A was supplied to me by the Wisconsin TechSearch (WTS) on July 2, 2018.

- 49. Attachment 2B of Document 2 was downloaded by me through Purdue University Libraries online through IEEE Xplore <a href="https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/stamp/stamp.jsp?tp=&arnumber=624619">https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/stamp/stamp.jsp?tp=&arnumber=624619</a>.

- 50. Attachment 2A is in a condition that creates no suspicion about its authenticity. Specifically, Attachment 2A is not missing any intermediate pages, the text on each page appears to flow seamlessly from one page to the next, and there are no visible alterations to the document. Attachment 2A was found within the custody of a library (the British Library) a place where, if authentic, it would likely be found.

- 51. Based on finding Attachment 2A in a library, the British Library, and locating Document 2 online at IEEE Xplore, I conclude that Document 2 is an authentic document and that Attachment 2A is an authentic copy of Document 2.

## **Public Accessibility**

52. Attachment 2C is the WorldCat record that shows British Library, Boston Spa as one of the libraries holding Document 2. The record shows that Document 2 is held by 207 libraries world-wide as of July 2018. Subject access is

possible through subject headings: Field Programmable Data Arrays – Congresses; Computer Engineering – Congresses; and Computer Engineering.

- 53. Attachment 2D is the British Library MARC and OPAC records for Document 2. Attachment 2D indicates through MARC field 260 that Document 2 has a copyright date of 1997, meaning that a librarian noted that the Document 2 claimed to have been copyrighted in the year 1997. Since there are no special notes in this record to indicate otherwise, I would expect that this document was catalogued and sent to the stacks for public access within a few weeks of receipt by the British Library. Thus, based on the date stamp of November 10, 1997 included on Attachment 2A and the records shown in Attachment 2D, I conclude that Attachment 2A would have been available in the stacks of the British Library no later than the end of November, 1997. As additional evidence, I further note that since Document 1 and Document 2 are from the same monograph, the processing identified by the Library of Congress MARC record in Attachment 1D should apply as well as Document 2. Since Document 1 was sent to cataloging on November 18, 1997 and went to the Library of Congress stacks November 26, 1997, I would expect the same of Document 2.

- 54. Attachment 2E is a true and accurate copy of a paper by John Villasenor and Brad Hutchings, "The Flexibility of Configurable Computing" IEEE Signal Processing Magazine, September 1998: 67-84. Number 35 of the References on page

94 is Document 2. Typically, due to the requirements of editing and processing, an article will have been completed approximately 1 year prior to its publication date. Thus, I would expect that Document 2 would have been available to the authors of Attachment 2E no later than the end of November, 1997, for it to appear as an article published in September of 1998.

#### Conclusion

is an authentic copy of Document 2, which is an article published in Proceedings: IEEE Symposium on FPGAs for Custom Computer Machines, held on April 16-18, 1997 Napa Valley, California. Based on the British Library's records showing the receipt of this document on November 10, 1997, the lack of special notes in the document's records, and the fact this this document was cited in a published article in September of 1998, it is my opinion that Document 2 was publicly accessible to and in actual use by ordinarily skilled researchers no later than the end of November 1997.

Document 3: Jean-Luc Gaudiot, "Data Driven Multicomputers in Digital Signal Processing." Proceedings of the IEEE, 1987, vol. 75, no. 9: 1220-1234.

#### Authentication

56. Document 3 is an article by Jean-Luc Gaudiot titled "Data Driven Multicomputers in Digital Signal Processing," 1987, IEEE, Proceedings, volume 75, number 9, pages 1220-1234.

- 57. Attachment 3A includes the cover of the September 1987 issue of IEEE Proceedings: table of contents and Document 3. On the cover of the issue is the stamp that identifies it as the property of Linda Hall Library, and the date October 23, 1987, indicating when it was checked-in by the Linda Hall Library. Attachment 3A was provided to me by the Wisconsin TechSearch (WTS).

- 58. Document 3 is available on-line through IEEE Xplore. Attachment 3B is a download I completed of Document 3 from IEEE Xplore on June 30, 2018 through the Purdue University Libraries: https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/stamp/stamp.jsp?tp=&arnumber=1458142.

- 59. Attachment 3A is in a condition that creates no suspicion about its authenticity. Specifically, Attachment 3A is not missing any intermediate pages, the text on each page appears to flow seamlessly from one page to the next, and there are no visible alterations to the document. Attachment 3A was found within the custody of a library, the Linda Hall Library a place where, if authentic, it would likely be found. The text of the article is also consistent in Attachment 3A and 3B. I see no reason to question the authenticity of the cover and its stamp or other preliminary pages in Attachment 3A.

- 60. Based on finding Attachment 3A in a library, on finding Document 3 online at IEEE Xplore, I conclude that Document 3 is an authentic document and that Attachment 3A is an authentic copy of Document 3.

#### **Public Accessibility**

- 61. Attachment 3C is the WorldCat record for Document 3 it shows that it is held by 789 libraries world-wide as of July 2018 and one of those 789 is the Linda Hall Library. Subject access is possible through subject headings: Elektronik; Elektrotechnik; and Institute of Electrical and Electronics Engineers.

- 62. Attachment 3D is the Linda Hall Library OPAC and MARC records for Document 3. The OPAC record documents that the Linda Hall Library holds Volume 75 (1987). This is indicated toward the bottom on the record under heading: Holdings Information Issues: v51(1963) 85(1997) indicates all volumes and issues are held from volume 51 1963 through volume 85 1997, thereby indicating that volume 75 1987 is held by the Linda Hall Library. Since there are no special notes in this record to indicate otherwise, I would expect that Document 3D was catalogued and sent to the stacks for public access within a week to ten days after receipt by the Linda Hall Library. Thus, based on the date stamp of October 23, 1987 included on Attachment 3A and the records shown in Attachment 3D, I conclude that Attachment 3A would have been available in the stacks of the Linda Hall Library, no later than early November 1987.

- 63. Attachment 3E is a true and accurate copy of a paper by Edward Ashford Lee and Jeffery C. Bier, "Architecture for Statically Scheduled Dataflow" published in the Journal of Parallel and Distributed Computing, Volume 10, issue 4,

December 1990: 333-348. On page 347, in References, citation number 21 is Document 3.

#### **Conclusion**

64. Based on the evidence presented here, I conclude that Attachment 3A is an authentic copy of Document 3, which is an article by Jean-Luc Gaudiot titled "Data Driven Multicomputers in Digital Signal Processing," 1987, IEEE, Proceedings, volume 75, number 9:1220-1234. Based on the Linda Hall Library's records showing the receipt of this document on October 23, 1987, the lack of special notes in the document's records, and the fact this this document was cited in a published article in December of 1990, it is my opinion that Document 3 was publicly accessible to and in actual use by ordinarily skilled researchers no later than early November 1987.

Document 4: D. Roccatano et al., "Development of a Parallel Molecular Dynamics Code on SIMD Computers: Algorithm for Use of Pair List Criterion" Journal of Computational Chemistry. Volume 19, number 7 (May 1998): 685 – 694

#### **Authentication**

65. Document 4 is an article by D. Roccatano, et al., titled "Development of a Parallel Molecular Dynamics Code on SIMD Computers Algorithm for Use of Pair List Criterion" published in the Journal of Computational Chemistry, volume 19, number 7 (May 1998): 685-694.

- 66. Attachment 4A includes the cover of the May 1998 issue of the Journal of Computational Chemistry, the title page, table of contents and Document 4. This information was provided to me by the Wisconsin TechSearch (WTS) from the Linda Hall Library. On the first page of Document 4 is the ownership and date stamp of the Linda Hall Library indicating that it processed this issue into its collection on April 28, 1998.

- 67. Document 4 is available on-line through Wiley Online Library <a href="https://onlinelibrary-wiley-">https://onlinelibrary-wiley-</a>

com.ezproxy.lib.purdue.edu/doi/10.1002/%28SICI%291096-

987X%28199805%2919%3A7%3C685%3A%3AAID-JCC1%3E3.0.CO%3B2-

MIEEE. Attachment 4B is a download I made from Wiley Online Library through Purdue University Libraries on June 30, 2018.

68. Attachment 4A is in a condition that creates no suspicion about its authenticity. Specifically, Attachment 4A is not missing any intermediate pages, the text on each page appears to flow seamlessly from one page to the next, and there are no visible alterations to the document. Attachment 4A was found within the custody of a library (the Linda Hall Library) – a place where, if authentic, it would likely be found. The text of the article is also consistent in Attachment 4A and 4B. I see no reason to question the authenticity of the cover and its stamp or other

preliminary pages in Attachment 4A. There are no missing pages and the text of the article flows seamlessly from one page to the next.

69. Based on finding Attachment 4A in a library, on finding Document 4 online at Wiley Online Library, I conclude that Document 4 is an authentic document and that Attachment 4A is an authentic copy of Document 4.

## **Public Accessibility**

- 70. Attachment 4C is the WorldCat record that shows Linda Hall Library as holding the Journal of Computational Chemistry. The record shows that the Journal of Computational Chemistry is held by 812 libraries world-wide as of July, 2018 among those libraries is the Linda Hall Library. Subject access is possible through subject headings: Chemistry Data Processing Periodicals; Chemistry Methods; and Computer Simulation.

- 71. Attachment 4D is the Linda Hall Library OPAC record for Journal of Computational Chemistry. The OPAC record documents that the Linda Hall Library holds the 1988 volume in the "Holdings Information": Issues: v.1:no. 1 (1980-Spring), v.4 (1983) v.34, issue 31/32 (2013) indicates that the Linda Hall Library has holdings that are inclusive from v.4 (1983) v.34 (2013) with no missing volumes or gaps, hence, volume 19, 1998 is held by the Linda Hall Library. Since there are no special notes in this record to indicate otherwise, I would expect that this document was catalogued and sent to the stacks for public access within a few

weeks of receipt by the Linda Hall Library. Thus, based on the date stamp of April 28, 1998 included with Attachment 4A and the records shown in Attachment 4D, I conclude that Attachment 4A would have been available in the stacks of the Linda Hall Library, no later than the middle of May 1998.

72. Attachment 4E is a paper by G. Chillemi et al., "The Role of Computer Technology in Applied Computational Chemical-Physics." Computer Physics Communication, Volume 139, Issue 1 (1 September 2001): 1-19. On page 18, References, citation number 9 is for Document 4.

#### **Conclusion**

73. Based on the evidence presented here, I conclude that Attachment 4A is an authentic copy of Document 4, which is an article by D. Roccatano et al., titled "Development of a Parallel Molecular Dynamics Code on SIMD Computers Algorithm for Use of Pair List Criterion" published in the Journal of Computational Chemistry, volume 19, number 7 (May 1998): 685-694. Based on the Linda Hall Library record showing the receipt of this document was on April 28, 1998, the lack of special notes in the document's records, and the fact this this document was cited in a published article in September of 2001, it is my opinion that Document 4 was publicly accessible to and in actual use by ordinarily skilled researchers no later than the middle of May 1998.

# Document 5. Buell, Duncan, et al., Splash 2: FPGAs in a Custom Computing Machine. Vol. 9. Wiley-IEEE Computer Society Press, 1996.

#### Authentication

- 74. Document 5 is a monograph edited by Duncan Buell and others with the title of "Splash 2: FPGAs in a Custom Computing Machine." Volume 9 published by Wiley-IEEE Computer Society Press in 1996. Attachment 2A is a scan of Document 2 provided to me by the Wisconsin TechSearch (WTS) of the book held by the Massachusetts Institute of Technology (MIT) Library.

- 75. Attachment 5A includes a scan of the cover; inside front cover (with ownership stamp of Massachusetts Institute of Technology Libraries & inventory label indicating MIT Libraries); two blank facing introductory pages; introductory title page; trademark statement page; full title page identifying the editors as Duncan A. Buell, Jeffrey M. Arnold, and Walter J. Kleinfelder; Published by IEEE Computer Society Press, Los Alamitos, California; verso of the title page which provides the Cataloging in Publication (CIP) information and copyright date of 1996. The verso of the title page also has the stamp of the MIT Libraries and the check-in date of August 8, 1996. Written in pencil by hand is the call number: QA76.8. S65 B84 1996. The Contents section follows and the last page is the back cover.

- 76. Attachment 5B is and true and accurate copy of Document 5 that was provided to me by Counsel. Attachment 5B is in a condition that creates no suspicion about its authenticity. Specifically, Attachment 5B is not missing any

intermediate pages, the text on each page appears to flow seamlessly from one page to the next, and there are no visible alterations to the document. I have been informed by counsel that Attachment 5B was found within the custody of a library (the Library of Congress) – a place where, if authentic, it would likely be found.

77. Based on the information that Attachments 5A and 5B were found in a library and on finding library catalog and online index records for Document 5, I conclude that Document 5 is an authentic document and that Attachment 5B is an authentic copy of Document 5. After a thorough review of the cover, title page, verso of title page, and table of contents of Attachment 5A and 5B, I conclude that Attachment 5B is the same publication that was identified in Attachment 5A.

## **Public Accessibility**

78. Attachment 5C is a download of the WorldCat record for Document 2. As discussed above WorldCat is the most comprehensive catalog that documents the bibliographic information about books, journals, tech reports, dissertations, etc., that are available in libraries world-wide. Attachment 2B indicates that Document 2 was accessible by title: Splash 2: FPGAs in a custom computing machine; by authors: Duncan A. Buell, Jeffrey M. Arnold, and Walter J. Kleinfelder. Document 2 was also accessible by subject headings: Splash 2 (Computer); Electronic digital computers – Design and construction; Field programmable gate arrays.

- 79. The WorldCat record indicates, as of August 4, 2018, that 83 libraries around the world hold this monograph among these is the MIT Libraries.

- 80. Attachment 5D is a download from the Online Public Access Catalog (OPAC) of the MIT Libraries. This OPAC records indicates the book was available at the MIT Libraries with the call number: QA76.8.S65.B84 1996 in the Barker Engineering Library Stacks.

- 81. Attachment 5E is a download from the Online Public Access Catalog (OPAC) of the MIT Libraries that provides the MARC record for Document 5. The fields indicate through the MARC format title, author, publisher, etc. In the 910 field MIT has a unique practice of inserting the initials of the cataloger and the date the book was cataloged (this practice was observed by me during my years at MIT Libraries). The 910 field in this record reads: "tn961003" indicating the cataloger with the initials of tn cataloged Document 1 on October 3, 1996, in sequence from the date it was checked into the MIT Libraries by acquisitions as evidenced above by the date: August 8, 1996. The catalog information would have been entered into the GEAC Library Management System (LMS) then in use at the MIT Libraries, and would have been immediately available in the OPAC (called Barton). Thus, based on the date stamp of August 8, 1996 included with Attachment 5A and the records shown in Attachment 5E (cataloging date of October 3, 1996), I conclude that

Document 5 would have been available in the stacks of the MIT Libraries no later than the middle of October 1996.

#### Conclusion

82. Based on the evidence presented here, I conclude that Attachments 5A and 5B are authentic copies of Document 5, which is a book by Duncan Buell and others with the title of "Splash 2: FPGAs in a Custom Computing Machine." Volume 9 published by Wiley-IEEE Computer Society Press in 1996. Based on the MIT Library's records showing the receipt of this document (through Attachment 5A) on August 8, 1996, the MARC records in Attachment 5E indicating that the book was catalogued on October 3, 1996, it is my opinion that Document 5 was publicly accessible to and in actual use by ordinarily skilled researchers no later than the middle of October 1996.

Document 6: Yong-Jin Jeong and Wayne P. Burlson, "VLSI Array Algorithms and Architectures for RSA Modular Multiplication," IEEE Transactions on Very Large Scale Integration (VLSI) Systems. Volume 5, Number 2 (June 1997): 211-217.

#### **Authentication**

- 83. Document 6 is an article by Yong-Jin Jeong and Wayne B. Burlson titled "VLSI Array Algorithms and Architectures for RSA Modular Multiplication," IEEE Transactions on Very Large Scale Integration (VLSI) Systems. Volume 5, Number 2 (June 1997): 211-217.

- 84. Attachment 6A includes the June 1997 issue of IEEE Transactions on Very Large Scale Integration (VLSI) Systems. Volume 5, Number 2: cover/title-

page/table of contents, publication details, page 161, and Document 6 (pages 211 – 217). On page 161 is the stamp of the Library of Congress, Copyright Office and the date of receipt, September 22, 1997. Attachment 6A was provided to me by the Wisconsin TechSearch (WTS) from the Library of Congress.

- 85. Document 6 is available on-line through IEEE Xplore. Attachment 6B is a download from IEEE Xplore through Purdue University Libraries on August 29,

2018 at <a href="https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/stamp/stamp.jsp?tp=&arnumber=585224">https://ieeexplore-ieee-org.ezproxy.lib.purdue.edu/stamp/stamp.jsp?tp=&arnumber=585224</a>.

- 86. Attachment 6A is in a condition that creates no suspicion about its authenticity. Specifically, Attachment 6A is not missing any intermediate pages, the text on each page appears to flow seamlessly from one page to the next, and there are no visible alterations to the document. Attachment 6A was found within the custody of a library, the Library of Congress a place where, if authentic, it would likely be found. The text of the article is also consistent in Attachment 6A and 6B. I see no reason to question the authenticity of the cover and its stamp or other preliminary pages in Attachment 6A. There are no missing pages and the text of the article flows seamlessly from one page to the next.

- 87. Based on finding Attachment 6A in a library, on finding Document 6 online at IEEE Xplore, I conclude that Document 6 is an authentic document and that Attachment 6A is an authentic copy of Document 6.

#### **Public Accessibility**

- 88. Attachment 6C is the WorldCat record for IEEE Transactions on Very Large Scale Integration (VLSI) Systems. The WorldCat record shows that the IEEE Transactions on Very Large Scale Integration (VLSI) Systems is held by 530 libraries world-wide as of August 2018 among these is the Library of Congress.

- 89. Attachment 6D is the Library of Congress OPAC (public catalog) record for IEEE Transactions on Very Large Scale Integration (VLSI) Systems. The OPAC record documents that the Library of Congress subscribed from volume 1, no. 1 (March 1993) to the present. Toward the end of the record, is a section titled "Older Receipts" in which it states holdings "v.1-v.14 (1993-2006:May). It also shows subject access through subject headings: Integrated circuits Very large scale integration-Design and construction Periodicals; Integrated circuits Very large scale integration-Design and construction; and VLSI.

- 90. Attachment 6E is the MARC record available for IEEE Transactions on Very Large Scale Integration (VLSI) Systems from the Library of Congress. The MARC record indicates the "Unbound" (current) issues are shelved in the Newspaper & Current Periodical Reading Room (Madison LM133), when this issue was current (unbound) it would have been available in Madison LM133. Since there are no special notes in this record to indicate otherwise, I would expect that this document was checked-in and sent to the Newspaper & Current Periodical Reading

Room for public access within a few days of receipt by the Library of Congress. Thus, based on the date stamp of September 22, 1997 included with Attachment 6A and the records shown in Attachment 6D & 6E, I conclude that Attachment 6A would have been available in the Newspaper & Current Periodical Reading Room of the Library of Congress no later than the end of September 1997.

91. Attachment 6F is a paper by William L. Freking and Keshab K. Parhi, "Ring-Planarized Cylindrical Arrays with Application to Modular Multiplication," Proceedings IEEE International Conference on Application-Specific Systems, Architectures, and Processors, Boston, MA, USA, (July 10-12, 2000): 497-506. On page 504, References, citation number 10 is for Document 6.

#### Conclusion

92. Based on the evidence presented here, I conclude that Attachment 6A is an authentic copy of Document 6, the article by Yong-Jin Jeong and Wayne B. Burlson titled "VLSI Array Algorithms and Architectures for RSA Modular Multiplication," IEEE Transactions on Very Large Scale Integration (VLSI) Systems. Volume 5, Number 2 (June 1997): 211-217. Based on the Library of Congress record showing the receipt of this document on September 22, 1997, the lack of special notes in the document's records, and the fact this this document was cited in a paper presented in July 2000, it is my opinion that Document 6 was

publicly accessible to and in actual use by ordinarily skilled researchers no later than the end of September 1997.

#### CONCLUSION

- 93. I reserve the right to supplement my opinions in the future to respond to any arguments that Patent Owner or its expert(s) may raise and to take into account new information as it becomes available to me.

- 94. I declare that all statements made herein of my knowledge are true, and that all statements made on information and belief are believed to be true, and that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Executed this 30<sup>th</sup> day of August, 2018 in Williamsburg, Virginia

James L. Mullins, Ph.D.

#### APPENDIX A

#### JAMES L. MULLINS

Prior Art Documentation Librarian Services, LLC

106 Berrow, Williamsburg, VA 23188

jlmullins@priorartdoclib.com

ph. 765 479 4956

#### **Experience:**

| 2018-present | Dean of Libraries Emeritus and Esther Ellis Norton Professor Emeritus.                                                |

|--------------|-----------------------------------------------------------------------------------------------------------------------|

| 2011-2017    | Dean of Libraries & Esther Ellis Norton Professor.                                                                    |

| 2004-2011    | Dean of Libraries & Professor Purdue University, West Lafayette, IN.                                                  |

| 2000-2004    | Assistant/Associate Director for Administration, MIT Libraries, Massachusetts Institute of Technology, Cambridge, MA. |

| 1996-2000    | University Librarian & Director, Falvey Memorial Library.<br>Villanova University, Villanova, PA.                     |

| 1978-1996    | Director of Library Services, Indiana University South Bend.                                                          |

| 1974-1978    | Associate Librarian, Indiana University Bloomington, School of Law.                                                   |

| 1974-1978    | Instructor/Catalog Librarian. Georgia Southern College (now University).                                              |

#### **Teaching Experience:**

| 1977-1996 | Associate Professor (part-time), School of Library and    |

|-----------|-----------------------------------------------------------|

|           | Information Science, Indiana University. Subjects taught: |

|           | Cataloging, Management, and Academic Librarianship.       |

#### **Education:**

The University of Iowa. Honors Bachelor of Arts in History, Religion and Political Science.

The University of Iowa. Master of Arts in Library Science.

Indiana University. Doctor of Philosophy. Concentration: Academic Library Administration. Emphasis: Legal Librarianship.

#### **Awards and Recognition:**

2017 Wilmeth Active Learning Center/Library of Engineering and Science, Grand Reading Room, was announced by President Mitch Daniels, Purdue University,

that it would be re-named the James L. Mullins Reading Room to honor his leadership and reputation in the academic library profession. September 2017. Portrait unveiled December 2017.

2017 Distinguished Alumnus Award by the School of Informatics and Computing, Indiana University, Bloomington. Given June 25, 2017.

2016 Hugh C. Atkinson Memorial Award, jointly sponsored by the four divisions of the American Library Association (ALA), June 27, 2016.

2015 ACRL Excellence in University Libraries Award, April 23, 2015.

Named Esther Ellis Norton Professor of Library Science by Purdue Trustees, December 11, 2011.

International Review Panel to evaluate the University of Pretoria Library, February 20 - 24, 2011. Pretoria, South Africa.

#### **Publications: (selected)**

A Purdue Icon: creation, life, and legacy, edited by James L. Mullins, Founder's Series, Purdue University Press, 138pp., August 2017.

"The policy and institutional framework." In *Research Data Management, Practical Strategies for Information Professionals*, edited by Ray, J M. Purdue University Press, pp.25-44, 2014.

"DataCite: linking research to data sets and content." In Benson, P and Silver, S. What Editors Want: An Author's Guide to Scientific Journal Publishing. University of Chicago Press, pp. 21-23, December 2012.

"Library Publishing Services: Strategies for Success," with R. Crow, O. Ivins, A. Mower, C. Murray-Rust, J. Ogburn, D Nesdill, M. Newton, J. Speer, C. Watkinson. *Scholarly Publishing and Academic Resources Coalition (SPARC)*, version 2.0, March 2012.

"The Changing Definition and Role of Collections and Services in the University Research Library." *Indiana Libraries*, Vol 31, Number 1 (2012), pp.18-24.

"Are MLS Graduates Being Prepared for the Changing and Emerging Roles that Librarians must now assume within Research Libraries?" *Journal of Library Administration*. Volume 52, Issue 1, 2012, p. 124-132

Baykoucheva, Svetla. What Do Libraries Have to Do with e-Science?: An Interview with James L. Mullins, Dean of Purdue University Libraries. Chem. Inf. Bull. [Online] 2011, 63 (1), 45-49. <a href="http://www.acscinf.org/publications/bulletin/63-1/mullins.php">http://www.acscinf.org/publications/bulletin/63-1/mullins.php</a> (accessed Mar 16, 2011).

"The Challenges of e-Science Data-set Management and Scholarly Communication for Domain Sciences and Technology: a Role for Academic Libraries and Librarians," chapter in, *The Digital Deluge: Can Libraries Cope with e-Science*?" Deanna B. Marcum and Gerald George, editors, Libraries Unlimited/Teacher Ideas Press, 2009. (a monograph publication of the combined proceedings of the KIT/CLIR proceedings).

"Bringing Librarianship to e-Science," *College and Research Libraries*. vol. 70, no. 3, May 2009, editorial.

"The Librarian's Role in e-Science" *Joho Kanri (Journal on Information Processing and Management)*, Japan Science and Technology Agency (formerly Japan Information Center of Science and Technology), Tokyo, Japan. Translated into Japanese by Taeko Kato. March 2008.

The Challenge of e-Science Data-set Management to Domain Sciences and Engineering: a Role for Academic Libraries and Librarians," KIT (Kanazawa Institute of Technology)/CLIR (Council of Library and Information Resources) International Roundtable for Library and Information Science, July 5-6, 2007. Developments in e-science status quo and the challenge, The Japan Foundation, 2007.

"An Administrative Perspective," Chapter 14, *Proven Strategies for Building an Information Literacy Program*, Susan Curzon and Lynn Lampert, editors, Neal-Schuman Publishers, Inc., New York, 2007. pp. 229-237.

Library Management and Marketing in a Multicultural World, proceedings of the IFLA Management and Marketing (M&M) Section, Shanghai, China, August 16-17, 2006, edited. K.G. Saur, Munchen, Germany, June 2007. 390 pp.

Top Ten Assumptions for the Future of Academic Libraries and Librarians: a report from the ACRL Research Committee, with Frank R. Allen and Jon R. Hufford. College & Research Libraries, April 2007, vol.68, no.4. pp.240-241, 246.

To Stand the Test of Time: Long-term Stewardship of Digital Data Sets in Science and Engineering. A report to the National Science Foundation from the ARL

Workshop on New Collaborative Relationships: the Role of Academic Libraries in the Digital Data Universe. September 26-27, 2006, Arlington, VA. p.141. http://www.arl.org/bm~doc/digdatarpt.pdf.

"Enabling Interaction and Quality in a Distributed Data DRIS," *Enabling Interaction and Quality: Beyond the Hanseatic League.* 8th International Conference on Current Research Information Systems, with D. Scott Brandt and Michael Witt. Promoted by euro CRIS. Leuven University Press, 2006. pp.55-62. Editors: Anne Garns Steine Asserson and Eduard J. Simons.

"Standards for College Libraries, the final version approved January 2000," prepared by the ACRL College Libraries Standards Committee (member), *C&RL News*, March 2000, p.175-182.

"Standards for College Libraries: a draft," prepared by the ACRL College Libraries Section, Standards Committee (member), *C&RL News*, May 1999, p. 375-381.

"Statistical Measures of Usage of Web-based Resources," *The Serials Librarian*, vol. 36, no. 1-2 (1999) p. 207-10.

"An Opportunity: Cooperation between the Library and Computer Services," in *Building Partnerships: Computing and Library Professionals*. Edited by Anne G. Lipow and Sheila D. Creth. Berkeley and San Carlos, CA, Library Solutions Press, 1995. p. 69-70.

"Faculty Status of Librarians: A Comparative Study of Two Universities in the United Kingdom and How They Compare to the Association of College and Research Libraries Standards," in *Academic Librarianship, Past, Present, and Future: a Festschrift in Honor of David Kaser*. Englewood, Colorado; Libraries Unlimited, 1989. p. 67-78. Review in: *College & Research Libraries*, vol. 51, no. 6. November 1990, p. 573-574.

#### **Presentations:** (representative)

"How Long the Odyssey? Transitioning the Library and Librarians to Meet the Needs and Expectations of the 21st Century University," David Kaser Lecture, School of Informatics & Computing, Indiana University, Bloomington, IN, November 16, 2015.

Presentation at University of Cape Town, Cape Town, South Africa, August 20, 2015.

"The Challenge of Discovering Science and Technology Information," Moderator, International Federation of Library Associations (IFLA) Science and Technological Libraries Section Program, Cape Town, South Africa, August 18, 2015.

"An Odyssey in Data Management: Purdue University," International Federation of Library Associations (IFLA) Research Data Management: Finding Our Role – A program of the Research Data Alliance, Cape Town, South Africa, August 17, 2015.

Presentation at University of Pretoria, Pretoria, South Africa, August 11, 2015.

Co-Convener with Sarah Thomas, Harvard University, at the Harvard Purdue Symposium on Data Management, Harvard University, Cambridge, MA, June 15-18, 2015.

"Strategic Communication," panel discussion on the Director's role and perspective on library communications at Committee on Institutional Cooperation (CIC) Center for Library Initiatives (CLI) Annual Conference, University of Illinois Urbana-Champaign, May 20, 2015.

"Issues in Data Management," panel discussion moderated by Catherine Woteki, United States Undersecretary for Research, Education & Economics at 20th Agriculture Network Information Collaborative (AgNIC) Annual Meeting in the National Agricultural Library, Beltsville, MD, May 6, 2015.

"Active learning/IMPACT & the Active Learning Center at Purdue University," Florida Institute of Technology, Melbourne, FL, February 11, 2015.

"Science+art=creativity: libraries and the new collaborative thinking," panel moderator, International Federation of Library Associations (IFLA) 80th General Conference and Assembly, Lyon, France, August 19, 2014.

"Purdue University The Active Learning Center—A new concept for a library," Association of University Architects 59th Annual National Conference, University of Notre Dame, South Bend, IN, June 23, 2014.

"Big Data & Implications for Academic Libraries," keynote speaker, Greater Western Library Alliance (GWLA) Cyber-infrastructure Conference, Kansas City, MO, May 28, 2014.

- "Research Infrastructure," panel moderator, Association of Research Libraries (ARL) 164th Membership Meeting, Ohio State University, Columbus, OH, May 7, 2014.

- "An Eight Year Odyssey in Data Management: Purdue University," International Association of Scientific and Technological University Libraries (IATUL) 2013 Workshop Research Data Management: Finding Our Role, University of Oxford, UK, December 2013.

- "Purdue University Libraries & Press: from collaboration to integration," Ithaka Sustainable Scholarship, The Evolving Digital Landscape: New Roles and Responsibilities in Higher Education, libraries as publishers, New York, New York, October 2013.

- "Tsinghua and Purdue: Research Libraries for the 21st Century," Tsinghua University, Tsinghua, China, August 2013.

- "Purdue Publishing Experience in the Libraries Publishing Coalition," Association of American University Presses Annual Meeting, Press-Library Coalition Panel, Boston, Massachusetts, June 21, 2013.

- "Indiana University Librarians Day: Purdue University Libraries Ready for the 21st Century," Indiana University Purdue University Indianapolis (IUPUI), June 7, 2013.

- "Purdue University Libraries and Open Access; CNI Project Update," Coalition for Networked Information, San Antonio, TX, April 5, 2013.

Memorial Resolution, honoring Joseph Brannon, to the Board of the Association of College & Research Libraries, Seattle, WA, January 2013.

- "An overview of sustaining e-Science collaboration in an Academic Research Library—the Purdue experience," Duraspace e-Science Institute webcast, October 17, 2012.

- "The Role of Libraries in Data Curation, Access, and Preservation: an International Perspective, "Panel Moderator, 78th General Conference and Assembly, International Federation of Library Associations, Helsinki, Finland, August 15, 2012.

- "21st Century Libraries," moderator of First Plenary Session, International Association of Technological University Libraries 33rd Annual Conference, Singapore, June 4, 2012.

- "Planning for New Buildings on Campus," panel presenter, University of Calgary Building Symposium on Designing Libraries for the 21st Century, Calgary, Alberta, Canada, May 17, 2012.

- "Data Management and e-Science, the Purdue Response." Wiley-Blackwell Executive Seminar-2012, Washington, DC, March 23, 2012.

- "An overview of Sustaining e-Science Collaboration in Academic Research Libraries and the Purdue Experience." Leadership & Career Development Program Institute, Association of Research Libraries (ARL). Houston, TX, March 21, 2012.

- "An overview of Data Activities at Purdue University in response to Data Management Requirements." Coalition for Academic Scientific Computation (CASC). Arlington, VA, September 8, 2011.

- "Getting on Track with Tenure," Association of College and Research Libraries (ACRL) Research Program Committee. Washington, DC, June 26, 2011.

- "Integration of the Press and Libraries Collaboration to Promote Scholarly Communication," Association of Library Collections & Technical Services (ALCTS) Scholarly Communication Interest Group American Library Association, New Orleans, Louisiana, June 25, 2011.

- "Cooperation for improving access to scholarly communication," with N. Lossau (Germany), C. Mazurek (Poland), J. Stokker (Australia), panel moderator and presenter, Second Plenary Session, International Association of Scientific and Technological University Libraries (IATUL) 32nd Conference 2011, Warsaw, Poland. May 29-June 2, 2011.

- "Riding the Wave of Data," STM Annual Spring Conference 2011. <u>Trailblazing & transforming scholarly publishing 2011</u>. Washington, D.C., April 28, 2011.

- "Confronting old assumptions to assume new roles: physical and operational integration of the Press and Libraries at Purdue University," keynote speaker, 2011 BioOne Publishers & Partners Meeting. Washington, D. C., April 22, 2011.

"Are MLS Graduates Being Prepared for the Changing and Emerging Roles that Librarians must now assume within Research Libraries?" University of Oklahoma Libraries Seminar, March 4, 2011, Oklahoma City, Oklahoma.

"The Future Role of University Librarians," the University of Cape Town, South Africa, February 25, 2011.

"New Roles for Librarians: the Application of Library Science to Scientific/Technical Research – Purdue University – a case study. International Council for Science and Technology (ICSTI); Ottawa, Canada. June 9, 2009.

"Reinventing Science Librarianship: Models for the Future," Association of Research Libraries / Coalition for Networked Information. October 16-17th, 2008, Arlington, VA. Moderator and convener of Data Curation: Issues and Challenges.

"Practical Implementation and Opportunities Created at Purdue University," African Digital Curation Conference, Pretoria, South Africa, (live video transmission), February 12, 2008.

Keynote speaker. "Scholarly Communication & Academe: The Winter of Our Discontent," XXVII Charleston Conference on Issues in Book and Serial Acquisition, Charleston, South Carolina. November 8, 2007.

Keynote speaker. "Enabling Access to Scientific & Technical Data-sets in e-Science: a role for Library and Archival Sciences," Greater Western Library Alliance (GWLA), Tucson, Arizona. September 17, 2007. A meeting of library directors and vice presidents for research of member institutions.

"The Challenge of e-Science Data-set Management to Domain Sciences and Engineering: a Role for Academic Libraries and Librarians," KIT (Kanazawa Institute of Technology)/CLIR (Council of Library and Information Resources) International Roundtable for Library and Information Science, July 5-6, 2007. Invited to participate by the Deputy Librarian of Congress.

International Association of Technological University Libraries (IATUL), Stockholm, Sweden. June 8, 2007. Invited paper, *Enabling International Access to Scientific Data-sets: creation of the Distributed Data Curation Center (D2C2)*.

"A New Collaboration for Librarians: The Principles of Library and Archival Sciences Applied to the Curation of Datasets," Symposium of the Libraries and the College of Engineering, University of Louisville, April 6, 2007.

"Purdue University Libraries: Through Pre-eminent Innovation and Creativity, Meeting the Challenges of the Information Age," Board of Trustees, Purdue University, February 15, 2007.

ARL Workshop on New Collaborative Relationships: The Role of Academic Libraries in the Digital Data Universe, September 26-27, 2006, Arlington, VA. Invited participant.

NARA and SDSC: A partnership. A panel before the National Science Foundation, June 27, 2006. Arlington, VA. Invited participant.

"Kaleidoscope of Scientific Literacy: fusing new connections," with Diane Rein, American Library Association, Association of College and Research Libraries, Science & Technology Section, Annual Conference, New Orleans, June 26th, 2006.

"Leadership for Learning: Building a Culture of Teaching in Academic Libraries – an administrative perspective," American Library Association, Association of College and Research Libraries, Instruction Section, Annual Conference, New Orleans, June 25th, 2006.

"Building an interdisciplinary research program in an academic library: how the Libraries' associate dean for research makes a difference at Purdue University," International Association of Technological University Libraries (IATUL), Porto, Portugal, May 23rd, 2006.

"Enabling Interaction and Quality in a Distributed Data DRIS," *Enabling Interaction and Quality: Beyond the Hanseatic League*. 8th International Conference on Current Research Information Systems, with D. Scott Brandt and Michael Witt. Promoted by euro CRIS, Bergen, Norway, May 12th, 2006, Brandt and Witt presented in person

"Interdisciplinary Research," with D. Scott Brandt, Coalition for Networked Information (CNI) Spring Meeting: Project Briefing, Washington, D.C., April 3rd, 2006.

"An Interview with Purdue's James Mullins," a podcast submitted by Matt Pasiewicz, on *Educause Connect*, http://connect.educause.edu/James L Mullins Interview CNI 2005.

"Managing Long-Lived Digital Data-sets and their Curation: Interdisciplinary Policy Issues," Managing Digital Assets Forum, Association of Research Libraries (ARL), Washington, D.C., October 28th, 2005.

"The Odyssey of a Librarian." Indiana Library Federation (ILF), District 2 Meeting, South Bend, Indiana. October 4th, 2005.

"New College Library Standards," Standards Committee Presentation, ALA, Chicago, July 7, 2000.

SUNY Library Directors, Lake George, New York. "The College Library Standards: a Tool for Assessment." April 5, 2000.

Tri-State College Library Association, *Finding You Have Talents You Never Knew You Had*, Penn State Great Valley, March 25, 2000.

Using Web Statistics, American Library Association, New Orleans, June 24, 1999.

Keynote speaker at the JSTOR Workshop, January 29, 30, 1999. University of Pennsylvania, Philadelphia, PA.

"The New Standards for Electronic Resources Statistics," Society of Scholarly Publishers, Washington, D.C., September 17, 1998.

"Evaluating Online Resources: Now that you've got them what do you do?," joint presenter with Chuck Hamaker, LSU, at the NASIG Conference, Boulder, Colorado. June 1998.

"What Employers Are Looking for in New Librarians?" Pennsylvania Library Association, Philadelphia. September 26, 1997.

"The Theory of Matrix Management" panel presentation of the Comparative Library Organization Committee of the Library Organization and Management Section of the Library Administration and Management Association, a division of the American Library Association, Annual Meeting, Chicago, June 24, 1990.

#### **Professional Involvement: (summary of recent emphasis)**

The focus for my professional involvement and research has moved recently toward managing massive data-sets. This has resulted in working with faculty in the sciences and technology to determine how librarians can collaborate in managing, curating, and preserving data-sets for future access and documentation. This has included various speaking opportunities as well as participation in