# Homayoun

# Reference 18

**DOCKET A L A R M** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

US007856545B2

#### (12) United States Patent Casselman

#### (54) FPGA CO-PROCESSOR FOR ACCELERATED COMPUTATION

- (75) Inventor: Steven Casselman, Sunnyvale, CA (US)

- (73) Assignee: **DRC Computer Corporation**, Sunnyvale, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 727 days.

- (21) Appl. No.: 11/829,801

- (22) Filed: Jul. 27, 2007

#### (65) Prior Publication Data

US 2008/0028186 A1 Jan. 31, 2008

#### Related U.S. Application Data

- (60) Provisional application No. 60/820,730, filed on Jul. 28, 2006.

- (51) Int. Cl. *G06F 15/00* (2006.01) *G06F 15/76* (2006.01)

| (52) | U.S. Cl.                       | 712/34 |

|------|--------------------------------|--------|

| (58) | Field of Classification Search | 712/34 |

See application file for complete search history.

#### (56) References Cited

DOCKF

#### U.S. PATENT DOCUMENTS

| 6,961,841    | B2 * | 11/2005 | Huppenthal et al | 712/34 |

|--------------|------|---------|------------------|--------|

| 7,210,022    | B2 * | 4/2007  | Jungck et al.    | 712/34 |

| 7,386,704    | B2 * | 6/2008  | Schulz et al     | 712/15 |

| 2004/0250046 | Al   | 12/2004 | Gonzalez         |        |

# (10) Patent No.: US 7,856,545 B2 (45) Date of Patent: Dec. 21, 2010

| FOREIGN PATENT DOCUMENTS |                   |        |  |  |  |

|--------------------------|-------------------|--------|--|--|--|

| wo                       | PCT/US2007/074660 | 7/2008 |  |  |  |

| WOWO | PCT/US2007/    |            |  |

|------|----------------|------------|--|

|      | 074661         | 7/2008     |  |

| WO   | WO 2008/014493 | A3 10/2008 |  |

#### OTHER PUBLICATIONS

Blume et al.; Integration of High-Performance ASICs into Reconfigurable Systems Providing Additional Multimedia Functionality; 2000; IEEE.\*

(Continued)

Primary Examiner—Eddie P Chan Assistant Examiner—Corey Faherty (74) Attempt Agent on Firm The Wakested F

(74) Attorney, Agent, or Firm-The Webostad Firm

#### (57) ABSTRACT

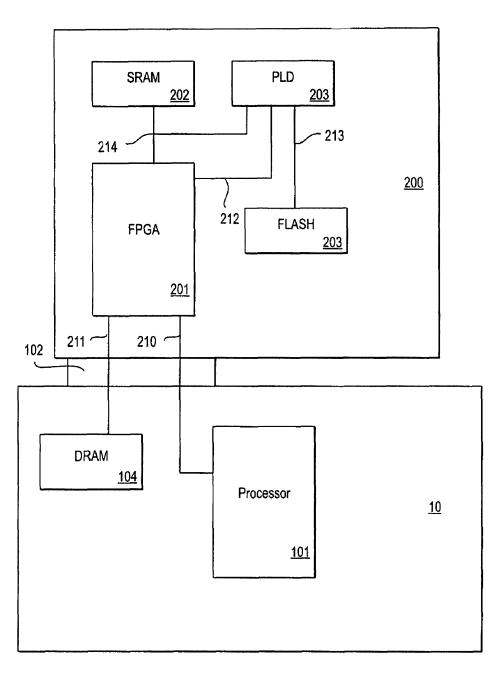

A co-processor module for accelerating computational performance includes a Field Programmable Gate Array ("FPGA") and a Programmable Logic Device ("PLD") coupled to the FPGA and configured to control start-up configuration of the FPGA. A non-volatile memory is coupled to the PLD and configured to store a start-up bitstream for the start-up configuration of the FPGA. A mechanical and electrical interface is for being plugged into a microprocessor socket of a motherboard for direct communication with at least one microprocessor capable of being coupled to the motherboard. After completion of a start-up cycle, the FPGA is configured for direct communication with the at least one microprocessor via a microprocessor bus to which the microprocessor socket is coupled.

#### 14 Claims, 6 Drawing Sheets

#### OTHER PUBLICATIONS

Fawcett; Taking Advantage of Reconfigurable Logic; 1994; IEEE.\* Blume etal.; Integration of High-Performance ASICs Into Reconfigurable Systems Providing Additional Multimedia Functionality; 2000; IEEE.

Letter from Jody Bishop to Steve Casselman dated Nov. 26, 2008. Letter from Jody Bishop to Steve Casselman dated Dec. 16, 2008. Maya Gokhale & Paul S. Graham, Reconfigurable Computing: Accelerating Computation with Field-Programmable Gate Arrays, 2003, pp. 4-5, The Netherlands, Springer Pub. Jeffrey M. Arnold, Duncan A .Buell, Dzung T. Hoang, Daniel V. Pryor, Nabeel Shirazi, Mark R. Thistle, The Splash 2 Processor and Applications, 1993, pp. 282-285, IEEE.

XSA Board V1.1, V1.2 User Manual, Jun. 23, 2005, XESS Corporation.

XSA-50 Spartan-2 Prototyping Board with 2.5V, 50,000-gate FPGA, 1998-2008, XESS, from http:...www.xess.com/prod027.php3.

\* cited by examiner

FIG. 1

**DOCKET A L A R M** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

DOCKET Α RM Find authenticated court documents without watermarks at docketalarm.com.

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.