# UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

Intel Corporation Petitioner

v.

Qualcomm Incorporated Patent Owner of U.S. Patent No. 8,838,949 Claims 10-17

Trial No. IPR2018-01335

# DECLARATION OF BILL LIN, PH.D. ON BEHALF OF PETITIONER

**INTEL 1102**

# **TABLE OF CONTENTS**

| I.   | BAC                                   | CKGROUND1                                                  |                                                          |     |  |  |  |

|------|---------------------------------------|------------------------------------------------------------|----------------------------------------------------------|-----|--|--|--|

| II.  | MAT                                   | TERIALS CONSIDERED                                         |                                                          |     |  |  |  |

| III. | LEGAL PRINCIPLES                      |                                                            |                                                          |     |  |  |  |

|      | А.                                    | Claim Construction                                         |                                                          |     |  |  |  |

|      | B.                                    | Anticipation                                               |                                                          |     |  |  |  |

|      | C.                                    | Obviousness7                                               |                                                          |     |  |  |  |

|      | D.                                    | Means-Plus-Function Claims                                 |                                                          |     |  |  |  |

| IV.  | SUM                                   | MMARY OF OPINIONS10                                        |                                                          |     |  |  |  |

| V.   | BRIEF DESCRIPTION OF THE TECHNOLOGY10 |                                                            |                                                          |     |  |  |  |

|      | A.                                    | A. Multi-Processor Systems                                 |                                                          |     |  |  |  |

|      |                                       | 1.                                                         | Processor-To-Processor Communications                    | .10 |  |  |  |

|      |                                       | 2.                                                         | Processor Software Code                                  | .14 |  |  |  |

|      |                                       | 3.                                                         | Characteristics of Memory                                | .15 |  |  |  |

|      | В.                                    | Storing, Loading, and Executing Processor Software<br>Code |                                                          |     |  |  |  |

|      |                                       | 1.                                                         | Storing the Processor Software Code in Memory            | .16 |  |  |  |

|      |                                       | 2.                                                         | Loading and Executing Multi-Segmented Software<br>Images |     |  |  |  |

|      |                                       | 3.                                                         | Sharing Memory in Multi-Processor Systems                | .19 |  |  |  |

|      | C.                                    | Boot Loading2                                              |                                                          |     |  |  |  |

| VI.  | OVERVIEW OF THE '949 PATENT           |                                                            |                                                          |     |  |  |  |

|      | A.                                    | Alleged Problem of the Prior Art                           |                                                          |     |  |  |  |

# U.S. Patent No. 8,838,949 Declaration of Bill Lin, Ph.D.

| C. Prosecution History of the '949 Patent                                                                                                                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                 |    |

| VIII CLAIM CONCEDUCEION                                                                                                                                                                                                                                                         | 33 |

| VIII. CLAIM CONSTRUCTION                                                                                                                                                                                                                                                        |    |

| A. "image header" (claims 10 and 16)                                                                                                                                                                                                                                            |    |

| B. "means for receiving at a secondary processor, from a primary processor via an inter-chip communication bus, an image header for an executable software image for the secondary processor that is stored in memory coupled to the primary processor" (claim 16)              | 35 |

| 1. Function                                                                                                                                                                                                                                                                     | 35 |

| 2. Structure                                                                                                                                                                                                                                                                    |    |

| C. "means for processing, by the secondary processor, the<br>image header to determine at least one location within<br>system memory to which the secondary processor is<br>coupled to store each data segment" (claim 16)                                                      | 36 |

| 1. Function                                                                                                                                                                                                                                                                     |    |

| 2. Structure                                                                                                                                                                                                                                                                    |    |

| D. "means for receiving at the secondary processor, from the primary processor via the inter-chip communication bus, each data segment" (claim 16)                                                                                                                              | 37 |

| 1. Function                                                                                                                                                                                                                                                                     |    |

| 2. Structure                                                                                                                                                                                                                                                                    |    |

| E. "means for scatter loading, by the secondary processor,<br>each data segment directly to the determined at least one<br>location within the system memory, and each data<br>segment being scatter loaded based at least in part on the<br>processed image header" (claim 16) |    |

|     |                                            | 1.                                                                                                      | Function                                                                               |     |  |

|-----|--------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|--|

|     |                                            | 2.                                                                                                      | Structure                                                                              |     |  |

| IX. | OVERVIEW OF PRINCIPAL PRIOR ART REFERENCES |                                                                                                         |                                                                                        |     |  |

|     | A.                                         | Svensson (Ex-1110)                                                                                      |                                                                                        |     |  |

|     | B.                                         | Bauer (Ex-1109)                                                                                         |                                                                                        |     |  |

|     | C.                                         | Kim (Ex-1111) (Including English Translation (Ex-<br>1112))47                                           |                                                                                        |     |  |

|     | D.                                         | Zhao                                                                                                    | (Ex-1113)                                                                              | 50  |  |

| X.  | SPECIFIC GROUNDS FOR CHALLENGE             |                                                                                                         |                                                                                        |     |  |

|     | A.                                         |                                                                                                         | nd 1: Claims 10-15 Are Rendered Obvious By The<br>pination Of Bauer, Svensson, And Kim | 52  |  |

|     |                                            | 1.                                                                                                      | Reference to "Bauer and Svensson Combined"                                             | 52  |  |

|     |                                            | 2.                                                                                                      | Claim 10                                                                               | 54  |  |

|     |                                            | 3.                                                                                                      | Claim 11                                                                               | 80  |  |

|     |                                            | 4.                                                                                                      | Claim 12                                                                               | 83  |  |

|     |                                            | 5.                                                                                                      | Claim 13                                                                               | 86  |  |

|     |                                            | 6.                                                                                                      | Claim 14                                                                               |     |  |

|     |                                            | 7.                                                                                                      | Claim 15                                                                               | 89  |  |

|     | В.                                         | Ground 2: Claims 16 And 17 Are Rendered Obvious By<br>The Combination Of Bauer, Svensson, Kim, And Zhao |                                                                                        |     |  |

|     |                                            | 1.                                                                                                      | Reference to "Bauer and Svensson Combined"                                             | 90  |  |

|     |                                            | 2.                                                                                                      | Claim 16                                                                               | 90  |  |

|     |                                            | 3.                                                                                                      | Claim 17                                                                               | 100 |  |

| XI. | AVA                                        | ILABI                                                                                                   | LITY FOR CROSS-EXAMINATION                                                             | 166 |  |

# U.S. Patent No. 8,838,949 Declaration of Bill Lin, Ph.D.

| XII.  | RIGHT TO SUPPLEMENT | 167 |

|-------|---------------------|-----|

| XIII. | JURAT               | 167 |

I, Bill Lin, Ph.D. declare as follows:

#### I. BACKGROUND

I am currently Professor and Vice Chair of Electrical and Computer

Engineering at the University of California, San Diego (UCSD). I am also Adjunct

Professor of Computer Science and Engineering at UCSD.

2. My Curriculum Vitae, which states my qualifications more fully, is attached as Appendix A. A list of all cases in which I have testified as an expert at trial or by deposition in the last four years is also included in Appendix A.

3. I received a Bachelor's of Science degree in 1985, a Master's of Science degree in 1988, and a Ph.D. in 1991, all in Electrical Engineering and Computer Sciences from the University of California, Berkeley.

4. I joined UCSD in 1997, and I have been a tenured professor since 1999. My teaching and research has focused on computer architecture and computer network problems, including the design of multiprocessor and multi-core processor architectures, multiprocessor and multi-core processor interconnection buses and networks, network processors, systems-on-chips, and data networks. I regularly teach a senior-level design course on the design of advanced processors, and I have taught graduate courses in hardware/software co-design and advanced special topics in computer architecture.

- 1 -

## U.S. Patent No. 8,838,949 Declaration of Bill Lin, Ph.D.

5. At UCSD, I am a Principal Investigator in the UCSD Center for Networked Systems (CNS). CNS brings together researchers to work on a range of challenges in the design of future networked systems. My contribution to CNS has been expertise in the design of computer architecture solutions for packet processing and computer networking. I am also a Principal Investigator in the UCSD Center for Wireless Communications (CWC). CWC brings together researchers to work on a range of challenges in the design of future wireless communications systems. My contribution to CWC has been expertise in the design of multi-core processor architectures for wireless communications and mobile computing.

6. Prior to joining UCSD, I was the Head of the Systems and Communications Group at IMEC in Leuven, Belgium, where I led a team of researchers who worked on a range of computer design problems, including hardware/software co-design, processor interfaces, multiprocessor and multi-core processor design methodologies, and specialized processors for wireless communications and computer networking.

7. During my career, I have received or worked on research efforts that received millions of dollars in research funding from both government agencies and industry, including funding for research in multi-core processor design,

- 2 -

system-on-chips, hardware/software co-design, packet processing, and computer networks.

8. I have served as an Associate or Guest Editor for several journals published by the Association for Computing Machinery ("ACM") and the Institute of Electrical and Electronics Engineers ("IEEE"). I have also served as General Chair of several ACM/IEEE conferences, and on the Organizing or Steering Committees of many ACM/IEEE conferences, and I have served on the Technical Program Committees of numerous ACM/IEEE conferences. I am the author of over 170 peer-reviewed publications in the field of computer engineering dating to the 1980s, including journal articles, conference papers, book chapters, technical reports, and invited papers. A number of these publications have received best paper awards or distinguished paper citations. I have also given numerous invited and keynote talks around the world. A list of my publications within the last ten years is included in my CV.

9. I am the inventor of five patents: U.S. Patent Nos. 8,443,444,7,860,004, 7,672,005, 5,870,588, and 5,748,487.

I have been retained by counsel for Intel Corporation ("Petitioner") as an independent expert witness for the above captioned Petition for *Inter Partes* Review of U.S. Patent No. 8,838,949 (the "'949 patent") (Ex-1101). I am being compensated at my normal hourly consulting rate of \$550 for my work. My

- 3 -

compensation is not dependent on and in no way affects the substance of my statements in this Declaration.

11. I have no financial interest in the Petitioner. I similarly have no financial interest in the '949 patent, and have had no contact with the named inventors of the '949 patent.

# II. MATERIALS CONSIDERED

I have reviewed the specification, claims, and file history of the '949 patent. I understand that the '949 patent claims priority to U.S. Provisional Application No. 61/324,035, filed April 14, 2010, U.S. Provisional Application No. 61/316,369, filed March 22, 2010, U.S. Provisional Application No. 61/324,122, filed April 14, 2010, and U.S. Provisional Application No. 61/325,519, filed April 19, 2010.

13. I have also reviewed the following references, all of which I understand to be prior art to the '949 patent:

- U.S. Patent Application Publication No. US2006/0288019A1 to Bauer et al. ("Bauer") (Ex-1109)

- U.S. Patent No. 7,356,680 to Svensson et al. ("Svensson") (Ex-1110).

- Korean Patent Application Publication No. 10-2002-0036354 to Kim ("Kim") (Ex-1111) (English language translation – Ex-1112).

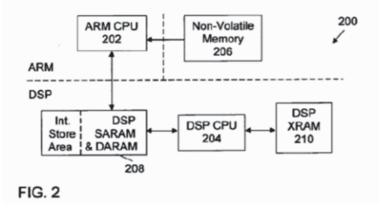

- U.S. Patent Application Publication No. 2007/0140199 to Zhao et al. ("Zhao") (Ex-1113).

14. In addition to the documents listed above, I have also reviewed the file history of the '949 patent, all of the documents listed in Petitioner's List of Exhibits in the accompanying petition and all other documents cited in this declaration.

## **III. LEGAL PRINCIPLES**

15. I am not an attorney. For the purposes of this declaration, I have been informed about certain aspects of the law that are relevant to my opinions. My understanding of the law is as follows:

## A. Claim Construction

16. I have been informed that claim construction is a matter of law and that the final claim construction will ultimately be determined by the Board. For the purposes of my analysis in this proceeding and with respect to the prior art, I have been informed that patents are currently reviewed in an *inter partes* review (IPR) proceeding under the "broadest reasonable interpretation" standard (hereinafter "BRI standard"). I also have been informed that IPRs may soon be reviewed under what is known as "the Phillips standard."

17. I have been informed that the BRI standard refers to the broadest reasonable interpretation that a person of ordinary skill in the art would give to a claim term in light of the specification.

18. I have been informed that under the Phillips standard, claim terms are generally given their plain and ordinary meaning as understood by a person of ordinary skill in the art at the time of the invention, with the claim term read not only in the context of the particular claim in which the disputed term appears, but also in the context of the entire patent, including the specification.

19. I have been informed that the patentee can serve as his or her own lexicographer. As such, if a claim term is provided with a specific definition in the specification, that claim term should be interpreted in light of the particular definition provided by the patentee.

#### **B.** Anticipation

20. I have been informed and understand that a patent claim is invalid if it is "anticipated" by prior art. For the claim to be invalid because it is anticipated, all of its requirements must have existed in a single device or method that predates the claimed invention, or must have been described in a single publication or patent that predates the claimed invention. A patent claim may be "anticipated" if

- 6 -

each element of that claim is present either explicitly, implicitly, or inherently in a single prior art reference. I have also been informed that, to be an inherent disclosure, the prior art reference must necessarily disclose the limitation, and the fact that the reference might possibly practice or contain a claimed limitation is insufficient to establish that the reference inherently teaches the limitation.

## C. Obviousness

21. I have been informed and understand that a patent claim is invalid if the claimed invention would have been obvious to a person of ordinary skill in the art at the time the application was filed. This means that, even if all of the requirements of a claim are not found in a single prior art reference, the claim is not patentable if the differences between the subject matter in the prior art and the subject matter in the claim would have been obvious to a person of ordinary skill in the art at the time the application was filed.

22. I have been informed and understand that a determination of whether a claim would have been obvious should be based upon several factors, including, among others:

- the level of ordinary skill in the art at the time the application was filed;

- the scope and content of the prior art; and

• what differences, if any, existed between the claimed invention and the prior art.

23. I have been informed and understand that the teachings of two or more references may be combined in the same way as disclosed in the claims, if such a combination would have been obvious to one having ordinary skill in the art. In determining whether a combination based on either a single reference or multiple references would have been obvious, it is appropriate to consider, among other factors:

- whether the teachings of the prior art references disclose known concepts combined in familiar ways, which, when combined, would yield predictable results;

- whether a person of ordinary skill in the art could implement a predictable variation, and would see the benefit of doing so;

- whether the claimed elements represent one of a limited number of known design choices, and would have a reasonable expectation of success by those skilled in the art;

- whether a person of ordinary skill would have recognized a reason to combine known elements in the manner described in the claim;

- whether there is some teaching or suggestion in the prior art to make the modification or combination of elements claimed in the patent; and

- whether the innovation applies a known technique that had been used to improve a similar device or method in a similar way.

24. I understand that one of ordinary skill in the art has ordinary creativity, and is not an automaton.

25. I understand that in considering obviousness, it is important not to determine obviousness using the benefit of hindsight derived from the patent being considered.

26. I have been informed and understand that a single reference alone can render a patent claim obvious, if any differences between that reference and the claims would have been obvious to a person of ordinary skill in the art at the time of the alleged invention—that is, if the person of ordinary skill could readily adapt the reference to meet the claims of the patent, by applying known concepts to achieve expected results in the adaptation of the reference.

## **D.** Means-Plus-Function Claims

27. I have been informed and understand that for means-plus-function limitations, a prior art reference or combination of references must disclose the identical function in the claim limitation and must disclose a structure that

- 9 -

performs the function that is either identical to or the equivalent of the structure in the specification of the challenged patent that performs the claimed function. I understand that a structure is equivalent if it performs the identical function in substantially the same way to achieve substantially the same result as the claim limitation at issue.

### **IV. SUMMARY OF OPINIONS**

28. It is my opinion that every limitation of claims 10-17 of the '949 patent is disclosed by the prior art, and that claims 10-17 are rendered obvious by the prior art cited in this declaration.

### V. BRIEF DESCRIPTION OF THE TECHNOLOGY

#### A. Multi-Processor Systems

## 1. Processor-To-Processor Communications

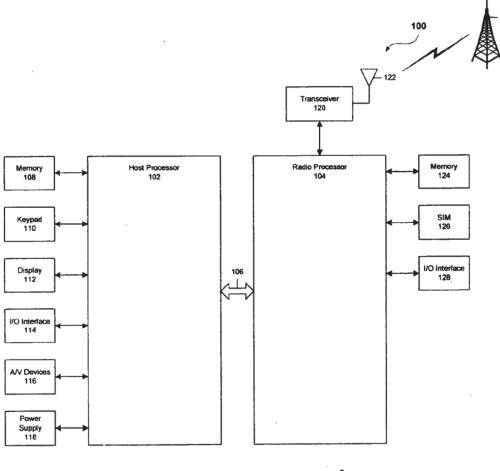

29. The '949 patent generally relates to communications between processors. Processors are common components in electrical devices that perform various functions to make the devices operate. Electrical devices may have multiple processors to handle different responsibilities. For example, a mobile telephone may include a "baseband" processor—which the '949 patent calls a "modem" processor—and an "application" processor. Ex-1101, 1:41-44.

30. The baseband/modem processor typically performs tasks relating to the transmission and reception of data to/from other devices over a network such as

- 10 -

## U.S. Patent No. 8,838,949 Declaration of Bill Lin, Ph.D.

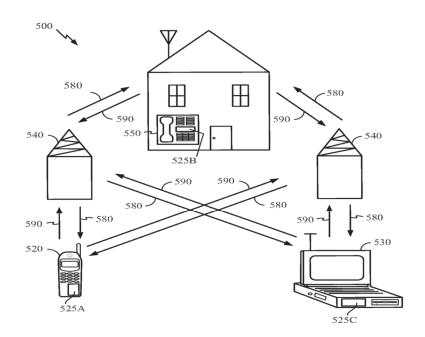

a wireless communication network. For example, Figure 5 of the '949 patent shows a mobile telephone 520 communicating with base stations 540 in a wireless communication system 500.

Ex-1101, Fig. 5.

31. The baseband/modem processor in the mobile telephone 520 is responsible for sending data to and receiving data from base stations 540. The base stations 540 facilitate communication between the mobile telephone 520 and other devices, such as a portable computer 530, in the wireless communication system 500. Ex-1101, 11:25-39, Fig. 5. 32. The application processor typically runs applications and other computer programs on the mobile telephone—*e.g.*, email applications, video chat, text messaging, phone applications, GPS applications, etc.

33. The baseband/modem and application processors need to communicate with each other. For example, when a user of a mobile telephone composes an email or text message using an application running on the application processor, the application processor must send the message to the baseband/modem processor so that the baseband/modem processor can transmit the message to the base station. Similarly, when a mobile telephone receives data from the base station, the baseband/modem processor receives the data and then transfers it to the application processor so that the user can view the data in an email or other application.

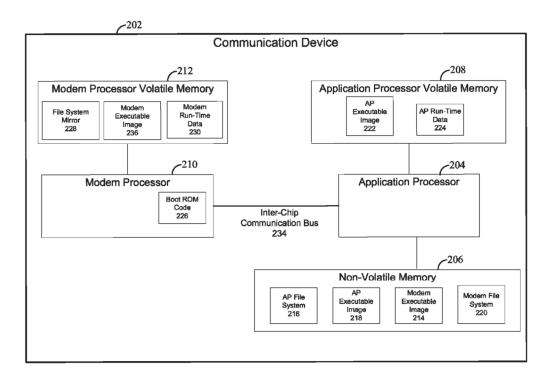

34. The baseband/modem and application processors typically communicate with each other by sending pieces of data over a "bus." A bus, sometimes referred to as an "interface," is typically a set of wires over which processors send electrical signals to each other. For example, Figure 2 of the '949 patent shows two processors (Application Processor 204 and Modem Processor 210) connected by Inter-Chip Communication Bus 234.

FIG. 2

Ex-1101, Fig. 2.

35. Many different types of buses were known prior to the alleged invention of the '949 patent. To enable compatibility between processors of different manufacturers, buses usually operate according to one of a number of well-known standards. Standardized buses that were commonly used in mobile telephones and other multi-processor devices include High Speed Synchronous Interface (HSI), Universal Serial Bus (USB), USB High Speed Inter-Chip (HSIC), Mobile Industry Processor Interface (MIPI), Secure Digital Input/Output (SDIO), Universal Asynchronous Receiver-Transmitter (UART), Serial Peripheral Interface (SPI) and Inter-Integrated Ciruit (I<sup>2</sup>C). *See, e.g.,* Ex-1101, 5:35-43; *see also* Ex1113, ¶32, Fig. 5 (disclosing interfaces such as "one or more universal serial bus (USB) interfaces, micro-USB interfaces, universal asynchronous receivertransmitter (UART) interfaces, general purpose input/output (GPIO) interfaces, control/status lines, control/data lines, shared memory, and so forth").

#### 2. Processor Software Code

36. A processor operates by executing software code that instructs the processor to perform specific operations. There are different types of software code for performing different types of operations. For example, when a processor is initially powered up, it typically executes "boot code" that instructs the processor to perform certain initialization operations. Such initialization operations may include determining what other devices may be connected to the processor and where such other devices may be located. For example, the boot code may instruct the processor to determine addresses associated with hardware peripherals, such as a keypad, a visual display, and memory.

37. After the processor executes its boot code, it typically executes "program code" that instructs the processor to perform various operations that the processor has been designated to perform. For example, in the case of the above-described baseband/modem processor, the program code may instruct the baseband/modem processor to transfer received data to the application processor so that a user can view the data in an email or other application. In the case of the

- 14 -

above-described application processor, the program code may instruct the application processor to send a message to the baseband/modem processor so that the baseband/modem processor can transmit the message to the base station.

## **3.** Characteristics of Memory

38. To be executed, software code must be stored in memory that is accessible to the processor. The processor reads the code from the memory and then executes the code. There are basically two types of memory—non-volatile memory and volatile memory. Non-volatile (or persistent) memory is designed to store code and other data regardless of whether power is being applied to the memory. In contrast, volatile memory can only store code and other data when power is being applied to the memory. That is, once power is removed from volatile memory, all code and other data previously stored in the memory will be lost.

39. Examples of non-volatile memory include electrically erasable programmable read-only memory (EEPROM) and flash memory. These types of non-volatile memory, as well as others, have characteristics that make them suitable for long-term persistent storage. For example, non-volatile memory can store code and other data for long periods of time after they have been initially programmed regardless of whether power is being applied to the memory.

- 15 -

However, non-volatile memory typically costs more, provides lower performance (*e.g.*, operates slower), and requires more space than volatile memory.

40. Examples of volatile memory include random access memory (RAM), dynamic RAM (DRAM) and static RAM (SRAM). These types of volatile memory, as well as others, have characteristics that make them suitable for short-term storage. For example, code and other data can be quickly stored and retrieved from volatile memory, thereby increasing system performance. But any code or other data stored in volatile memory is lost after power is removed from the memory, so using volatile memory for long-term storage is typically not feasible in devices that may lose power (*e.g.*, mobile telephones).

41. A data buffer is typically used as a temporary storage area that allows data to be moved from one location to another. The data buffer is often some portion of volatile memory.

#### **B.** Storing, Loading, and Executing Processor Software Code

## **1.** Storing the Processor Software Code in Memory

42. Software code is typically stored, at least initially, in non-volatile memory. The code is often later transferred from non-volatile memory to volatile memory, which is typically faster (and can be less expensive) than non-volatile memory. It is common for system designers to have processors use a type of volatile memory as a work space where the processor can execute software and

- 16 -

perform other processing functions. When coupled to a processor, engineers will often refer to this type of volatile memory coupled to the processor as "system memory."

43. Software code is typically packaged and stored in memory as a software file or program called an "executable image" or "executable software image." The '949 patent makes clear that executable software images were known in the prior art, including "multi-segmented" images that included (1) one or more headers, tables, or other structures that contain information about the overall image and/or its underlying data, and (2) one or more segments containing code or other data used by the image, which the patent refers to as "data segments."<sup>1</sup> Ex-1101, 2:14-16, 4:34-42.

#### 2. Loading and Executing Multi-Segmented Software Images

44. Before a processor can execute a multi-segmented software image, the processor usually must load the image into its system memory, from where it is then executed. Most multi-segmented executable software images are designed to be loaded in multiple steps. In the first step, the processor reads information in the one or more headers, tables, and/or other structures of the software image. That

<sup>&</sup>lt;sup>1</sup> References to "data" include code and/or data, and references to "data segment" include segments containing code and/or data.

information might identify the type of image (*e.g.*, an image format such as Executable and Linking Format (ELF)), the size of the image, the number and size of any data segments in the image, the storage locations of the data segments, and the locations in system memory where the data segments are to be loaded for execution. In one or more other steps, the processor uses that information to load the data segments into memory and execute the image.

When transferred into memory, the data segments of a software image 45. can be stored either in contiguous (*i.e.*, continuous) memory locations or spread across non-contiguous (*i.e.*, non-continuous) memory locations. "Scatter loading" is a well-known loading process in which one or more portions of a software image are loaded (or "scattered") into memory. When there are multiple portions of a software image, the portions are loaded across either contiguous or non-contiguous locations in memory. Given this aspect of scatter loading, a mapping mechanism is typically needed to allow a processor (or other component loading the code or other data) to know the destination locations where the various parts of the image are to be stored in memory. Many prior art executable software image formats (such as ELF) were designed for scatter loading—by including information in the image about where segments of the image should be loaded in memory for later execution.

U.S. Patent No. 8,838,949 Declaration of Bill Lin, Ph.D.

# 3. Sharing Memory in Multi-Processor Systems

46. In order to reduce costs and space requirements in a multi-processor system, such as a mobile telephone having a baseband/modem processor and an application processor, program code for both processors may be stored in a single non-volatile memory. For example, the application processor may have direct access to non-volatile memory that stores program code for both the application processor and the baseband/modem processor. The application processor may also have direct access to volatile memory for storing its program code after power up.

47. The baseband/modem processor, on the other hand, may have direct access to only volatile memory and not non-volatile memory. Upon power up, therefore, the application processor may have to transfer program code from nonvolatile memory to volatile memory so that the baseband/modem processor can use it. The application processor can transfer the baseband/modem processor's program code from the non-volatile memory connected to the application processor to the baseband/modem processor, which may then store the program code in the volatile memory connected to the baseband/modem processor.

48. The transfer of the program code is typically performed by transferring segments of code or other data over a bus, where it is then loaded into memory. A large software image may be split into smaller data segments to facilitate its transfer. Each segment of data is typically transferred with a header.

- 19 -

Each segment of data is typically received by a processor and stored in memory temporarily while the processor reads the information in the header to determine where the data payload should be later stored in the same or different memory. Thereafter, the processor stores the data at the destination address in memory.

## C. Boot Loading

49. When a computing device is first powered on, one or more processors in the device typically load and execute software (sometimes called "boot code" or "boot software") to enable the processor(s) to begin to operate. Because a processor must execute its boot code each time it powers up, the boot code is often stored in a non-volatile memory that is coupled to the processor. In this arrangement, during boot up, the boot code is typically loaded and executed from system memory that is coupled to the processor.

50. In a multi-processor system, each processor can store its own boot code, as the '949 patent acknowledges is prior art. Ex-1101, 1:38-44 ("Processors may require some software code, commonly referred to as boot code, to be executed for [booting] up. In a multi-processor system, each processor may require respective boot code for booting up. As an example, in a smartphone device that includes an application processor and a modem processor, each of the processors may have respective boot code for booting up."), 1:51-56 ("For instance, a processor's boot code may be stored to the processor's respective non-

- 20 -

volatile memory (e.g., Flash memory, read-only memory (ROM), etc.), and upon power-up the boot code software is loaded for execution by the processor from its respective non-volatile memory.").

51. The boot-up of a processor often occurs in multiple stages. As the first step, a primitive "boot loader" function usually loads and then executes a relatively small amount of boot code stored in a local boot ROM that the processor can access easily. This first stage enables the processor to begin performing basic functions. In one or more later stages, the processor then typically loads additional boot code (usually stored in a different, larger non-volatile memory), which enables the processor to perform more sophisticated functions.

52. As the '949 patent acknowledges, in the prior art, it was known that boot code for a processor could be stored in a non-volatile memory coupled to a different processor (especially for the later-stage boot code, which was often too large to store in ROM). Ex-1101, 2:9-13 ("In this type of system, the software (e.g., boot image) is downloaded from the first processor to the other processor(s) (e.g., to volatile memory of the other processor(s)), and thereafter the receiving processor(s) boots with the downloaded image.").

## VI. OVERVIEW OF THE '949 PATENT

53. The application that issued as the '949 patent (Ex-1101) was filed on Mar. 21, 2011. The '949 patent claims priority to four provisional applications, the earliest of which was filed on Mar. 22, 2010.<sup>2</sup>

54. The '949 patent is directed to scatter loading an executable software image from a memory connected to a primary processor to a memory connected to a secondary processor. Ex-1101, 1:24-33.

# A. Alleged Problem of the Prior Art

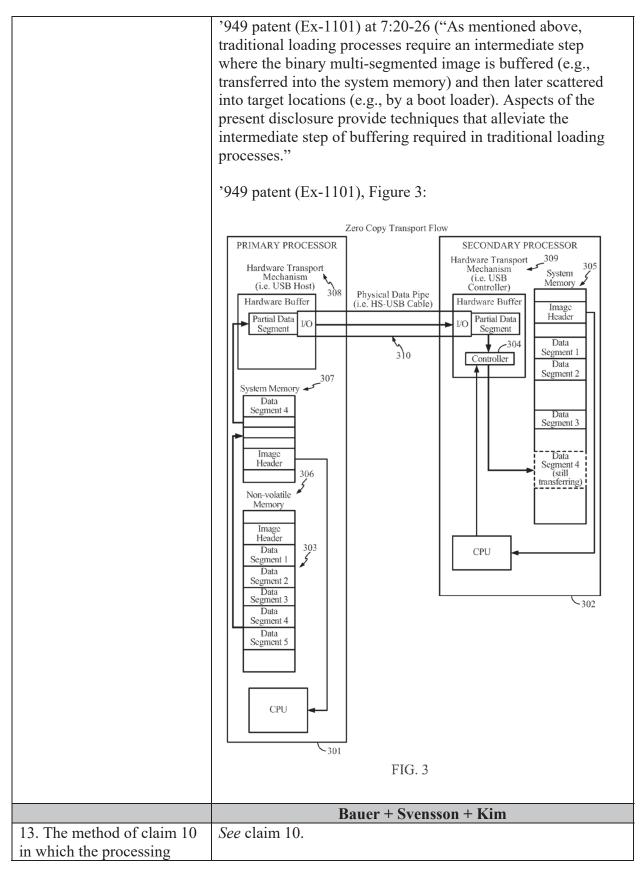

55. According to the '949 patent, however, prior art systems and methods for transferring software code between processors were inefficient. In particular, the '949 patent states that when retrieving an image for a modem processor from a non-volatile memory coupled to the application processor, prior art devices required copying the entire software image into one part of system memory coupled to the modem processor, and then copying the image into another part of system memory when loading it for execution:

[T]raditional loading processes require an intermediate step where the binary multi-segmented image is buffered (e.g., transferred into the

<sup>2</sup> For purposes of this declaration, I treat Mar. 22, 2010 as the effective filing date, but do not take any position regarding whether the '949 patent is fully enabled by any of its provisional applications. system memory) and then later scattered into target locations (e.g., by a boot loader). Aspects of the present disclosure provide techniques that alleviate the intermediate step of buffering required in traditional loading processes.

Ex-1101, 7:20-26.

56. The '949 patent describes this double copy (or "extra memory copy") approach as inefficient. Ex-1101, 7:27-30 ("Thus, aspects of the present disclosure avoid extra memory copy operations, thereby improving performance (e.g., reducing the time required to boot secondary processors in a multi-processor system)."); *see also id.*, 2:1-54, 9:42-56, 11:11-24. However, this alleged problem was well-known in the prior art.

#### **B.** Purported Solution of the '949 Patent

57. The '949 patent does not claim to invent a new type of processor, a new type of processor architecture, a new type of executable software image format, or a new type of image header or data segment. The patent also does not claim to invent the well-known idea of scatter loading executable software images into system memory, including based on information contained in an image header. All those things were well known in the prior art.

58. Indeed, the '949 patent admits that many claimed features of the patent are in the prior art, including:

- 23 -

- multi-processor systems in which a first processor uses non-volatile memory to store a software image (*e.g.*, boot code) for a second processor, and where the software image is downloaded from the first processor to the second processor (*e.g.*, to a volatile memory at the second processor) (Ex-1101, 2:1-13);

- that a software image would often comprise a header and multiple segments of code (*id.*, 2:14-16);

- that a transfer of a software image from a first ("primary") processor to a second ("secondary") processor may occur via a temporary buffer (also referred to as an intermediate buffer) (*id.*, 2:17-37);

- that a software image could be scattered (*i.e.*, scatter loaded) from a temporary buffer into the memory (*e.g.*, volatile memory) of a secondary processor (*id.*, 2:35-41);

- that the primary processor and its non-volatile memory may be implemented on a different chip from that of the secondary processor (*id.*, 2:42-45); and

- that each processor can have a non-volatile memory (*e.g.*, flash memory, ROM) that store executable images and file systems, including the processor's boot code such that upon power-up, the boot code is loaded from memory for execution by that processor (*id.*, 1:48-56).

59. Instead, what the '949 patent claims to have invented is a new way to avoid the "double copy" or "extra memory" approach described above. The purported solution of the '949 patent is for a secondary (or modem) processor to (1) first receive from the primary (or application) processor the "image header" of an executable software image, and (2) then *separately* receive each "data segment" of the image, each of which is then scatter loaded into the secondary processor's system memory using the data segment's destination address from the earlier-received image header—*all without first copying the entire image into the secondary processor's system memory*. The data received by the secondary (or modem) processor is temporarily stored in a hardware buffer separate from the secondary processor's system memory. Ex-1101, 2:58-3:67, 9:42-56, 11:11-24. However, this purported solution was well-known in the prior art.

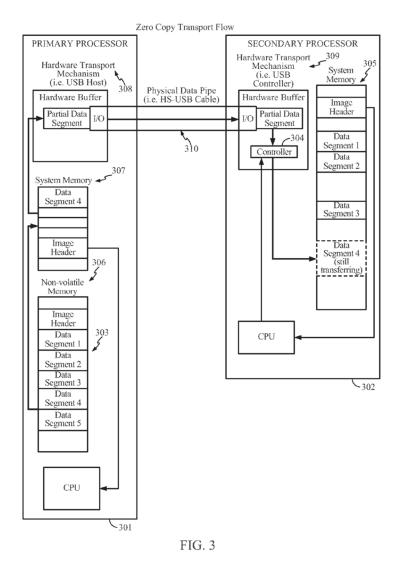

60. To illustrate this concept, Figure 3 of the '949 patent shows a primary processor 301 (*e.g.*, an application processor) connected to a secondary processor 302 (*e.g.*, a baseband/modem processor) via an inter-chip communication bus 310 (*e.g.*, a High-Speed USB (HS-USB) cable).

# U.S. Patent No. 8,838,949 Declaration of Bill Lin, Ph.D.

Ex-1101, Fig. 3.

61. The primary processor 301 comprises a non-volatile memory 306 storing a software image 303 for the secondary processor 302. Ex-1101, 7:60-8:18, Fig. 3. The software image 303 may be a multi-segment image that includes an image header and at least one data segment. *Id.*, 8:2-5, Fig. 3. The primary processor 301 also comprises a system (*i.e.*, volatile) memory 307 and a hardware transport mechanism 308 (*e.g.*, a USB host). *Id.*, 8:11-26, Fig. 3.

- 26 -

62. The secondary processor 302 comprises a system (*i.e.*, volatile) memory 305 and a hardware transport mechanism 309 (*e.g.*, a USB controller). Ex-1101, 8:9-30, Fig. 3. The hardware transport mechanism 309 includes a scatter loader controller 304 for controlling the scatter loading of software image data segments received from the primary processor 301 into the system memory 305 of the secondary processor 302. *Id.*, 8:60-62, 9:21-27, Fig. 3.

63. The '949 patent describes the scatter loading process in two stages. In the first stage, the image header of the software image 303 is transferred from the primary processor 301 to the secondary processor 302. Ex-1101, 8:9-12, Fig. 3. The image header of the software image 303 includes information that is used to determine where each data segment is to be loaded in the system (*i.e.*, volatile) memory 305 of the secondary processor 302. *Id.*, 8:18-21, Fig. 3. This information generally includes a list of addresses indicating where each data segment is to be loaded. *Id.*, 8:57-60, Fig. 3.

64. The first stage of the scatter loading process begins by the secondary processor 302 requesting the image header from the primary processor 301 in accordance with a boot loader program running on the secondary processor 302. Ex-1101, 8:40-43, Fig. 3. Once requested, the primary processor 301 transfers the image header from the non-volatile memory 306 to the primary processor's system (*i.e.*, volatile) memory 307. *Id.*, 8:14-18, Fig. 3.

- 27 -

65. Within the primary processor 301, the image header is transferred from the system (*i.e.*, volatile) memory 307 to the hardware transport mechanism 308. Ex-1101, 8:24-26, Fig. 3. The image header is then transferred from the hardware transport mechanism 308, over the inter-chip communication bus 310, to the hardware transport mechanism 309 of the secondary processor 302. *Id.*, 8:9-35, Fig. 3.

66. In the second stage of the scatter loading process, the boot loader program running on the secondary processor 302 programs the scatter loader controller 304 with the information included in the image header. Ex-1101, 8:63-67, Fig. 3. As discussed above, this information is used to determine where each data segment is to be loaded in the secondary processor's system memory 305, as well as the size of each data segment and its location within the primary processor 301. Thus, once programmed, the scatter loader controller 304 may transfer to the system memory each data segment. *Id.*, 9:13-37, Fig. 3. With scatter loading, the data segments may be placed into consecutive or non-consecutive locations within the system memory. *Id.*, 9:12-15, 9:21-41. The primary processor 301 may transfer each data segment to the secondary processor 302 over the inter-chip communication bus 310. *Id.*, 8:26-30, Fig. 3.

67. Once received at the secondary processor 302, each data segment is temporarily stored not in system memory but in a hardware buffer 309. Ex-1101,

- 28 -

9:50-54, Fig. 3. Thereafter, the scatter loader controller 304 may load each data segment directly into the system (*i.e.*, volatile) memory 305 of the secondary processor 302 at the location determined from the information included in the image header and previously programmed into the scatter loader controller 304. Ex-1101, 9:21-37, Fig. 3. Thus, during the above-described scatter loading process, each data segment is transferred from the primary processor 301 to the secondary processor's system (*i.e.*, volatile) memory 305. *Id.*, 9:42-56.

### C. Prosecution History of the '949 Patent

68. The '949 patent was filed on Mar. 21, 2011 with twenty-four claims, including six independent claims. During prosecution, the Applicants amended several independent claims to incorporate the contents of cancelled claim 4, in addition to other features, to overcome the cited prior art.

69. Initially, the Examiner rejected all original claims of the '949 patent under 35 U.S.C. § 102(b) as being anticipated by PCT Publication No. WO 2006/077068 to Svensson et al. ("Svensson PCT").<sup>3</sup> Ex-1104, 2-5. The Examiner found that Svensson PCT discloses:

<sup>&</sup>lt;sup>3</sup> Svensson PCT claims priority to Svensson. Svensson PCT at cover (Ex-1103); Svensson at cover (Ex-1110).

- a "secondary processor [*client processor 104*] comprising system memory [*DSPXRAM 110*] and a hardware buffer [*An intermediate storage area is defined within the memory 108*]";

- a "scatter loader controller...[*The slave copies the contents of the intermediate storage area to appropriate locations in its slave-private memory (Step 220), thereby implementing its actual loading, see page 7, last line page 8, line 2*]";

- a "primary processor [host processor102] coupled with a memory [non-volatile memory 106]";

- an "interface...[*The arrows in FIG. 1 indicate access paths, e.g., busses and DMA paths...*]"; and

- "the executable software image comprises an image header and at least one data segment [*Fig. 3, it is clear that the executable software image comprises an image header and at least one segment*]."

- Id., 2-3 (emphasis in original); see also Ex-1103, Fig. 1 (below).

70. In response, the Applicants did not contest that Svensson PCT anticipated the original claims. Instead, the Applicants amended claim 1 to require that (1) the claimed "hardware buffer" must receive "an image header and at least one data segment" of an executable software image, "the image header and each data segment being received separately"; and (2) the claimed "scatter loader controller" is configured "to load the image header; and to scatter load each received data segment, based at least in part on the loaded image header." Ex-1105, 2-9. Similar amendments were made to independent claims 11, 17, 19, 21, and 23. *Id.*, 4-7. In connection with these amendments, the Applicants admitted that "Svensson [PCT] arguably discloses that the software includes a header and a data segment." *Id.*, 8.

71. In an attempt to distinguish Svensson PCT, the Applicants argued that Svensson PCT "fails to disclose that the image header and each data segment are received separately" (*i.e.*, the requirement added by amendment). Ex-1105, 9. The

- 31 -

Applicants further asserted that "loading *each data segment directly*<sup>4</sup> from the hardware buffer to the system memory," as required by Applicants' amendment, "is patentably distinguishable from concatenating the data blocks and headers in the intermediate storage area and then transferring the concatenated data to the memory, as recited in Svensson [PCT]." *Id.*

72. Following an additional rejection on lack of enablement grounds, the Examiner allowed the claims. Ex-1106, 5. Thus, the Examiner allowed the application only after the Applicants amended the claims to require that (1) the image header and each data segment be received *separately* at the secondary processor, as well as (2) each data segment be scatter loaded *directly* to the system memory of the secondary processor. *Id.* The '949 patent then issued on Sep. 16, 2014. Ex-1101, cover.<sup>5</sup>

73. I explain below how Bauer and Kim disclose the same two claim features that the Examiner found allowable over Svensson PCT. These new references—in combination with Svensson, the U.S. counterpart to Svensson

<sup>&</sup>lt;sup>4</sup> All emphasis added unless otherwise noted.

<sup>&</sup>lt;sup>5</sup> The claims were re-numbered such that original claims 5-24 became issued claims 4-23, respectively.

PCT—present new art and a new combination that the Examiner never had a chance to consider.

#### VII. LEVEL OF ORDINARY SKILL IN THE ART

74. A person of ordinary skill in the art of the '949 patent would have had a Master's degree in Electrical Engineering, Computer Engineering or Computer Science plus at least two years of experience in mobile device architecture and multi-processor systems, or a Bachelor's degree in one of those fields plus at least four years of experience in mobile device architecture and multi-processor systems. I understand that in the Related ITC Case, the CALJ held this to be the level of ordinary skill in the art. Ex-1107, 11-13.

#### **VIII. CLAIM CONSTRUCTION**

75. I have applied the "broadest reasonable interpretation" standard for the claim terms of the challenged claims. However, based on my reading of the '949 patent's specification and the ordinary meanings of the claim terms, the prior art teaches each claim limitation under any reasonable interpretation of the claim terms. My analysis is, therefore, not dependent on application of the "broadest reasonable interpretation" standard.

76. I understand that the Petitioner has set forth its proposed construction of a term of the '949 patent and its support for the construction. Those are copied below. I also understand that the remaining terms of the claims described below are readily understandable and I have given them their broadest reasonable interpretation in light of the specification as commonly understood by those of ordinary skill in the art.

#### A. "image header" (claims 10 and 16)

As used in the '949 patent, a person of ordinary skill would have 77. understood the term "image header" to mean "a header associated with the entire image that specifies where the data segments are to be placed in the system memory" under either the BRI or *Phillips* standard. This understanding is consistent with the specification of the '949 patent. See Ex-1101, 8:18-21 ("The image header includes information used to identify where the modem image executable data is to be eventually placed into the system memory of the secondary processor 305."), 7:50-52 ("The image header also specifies the destination address") of the image in target memory."), 9:23-24 ("That image header provides information as to where the data segments are to be located in the system memory 305."), 10:6 ("... the header associated with the entire image."). This understanding is also consistent with the claims of the '949 patent. For example, independent claim 10 recites "processing...the image header to determine at least one location within system memory...to store each data segment." Id., claim 10. In the Related ITC Case, the parties (including the Patent Owner) agreed to this construction for this term. Ex-1108, 3.

#### **B.** Means-Plus-Function Terms (Claim 16)

78. The limitations of claim 16—(1) "means for receiving at a secondary processor ... an image header ..."; (2) "means for processing ..."; (3) "means for receiving at the secondary processor ... each data segment ..."; and (4) "means for scatter loading ..."—each uses the term "means" followed by a function without reciting sufficient structure for performing that function. Ex-1101, claim 16. Accordingly, I have interpreted each of these limitations as a means-plus-function limitations.

C. "means for receiving at a secondary processor, from a primary processor via an inter-chip communication bus, an image header for an executable software image for the secondary processor that is stored in memory coupled to the primary processor" (claim 16)

79. I understand that this is a means-plus-function limitation, which requires an identification of the claimed function and the structure in the specification that performs the claimed function.

#### 1. Function

80. As recited in claim 16, the function performed by this claim element is "receiving at a secondary processor, from a primary processor via an inter-chip communication bus, an image header for an executable software image for the secondary processor that is stored in memory coupled to the primary processor" under either the BRI or *Phillips* standard. This is in accordance with the determination of the CALJ in the Related ITC Case. Ex-1107, 17.

## 2. Structure

81. The corresponding structure for performing the above-stated function is "a secondary processor (*e.g.*, 110, 210, 302) connected to a primary processor (*e.g.*, 104, 204, 301) via an inter-chip communication bus (*e.g.*, 134, 234, 310) for a USB-based High Speed Inter-Chip (HSIC) bus, a MIPI High Speed Synchronous Interface (HSI) bus, a Secure Digital I/O Interface (SDIO) bus, a Universal Asynchronous Receiver/Transmitter (UART) bus, a Serial Peripheral Interface (SPI) bus, or an Inter-Integrated Circuit (I2C) bus, and equivalents thereof" under either the BRI or *Phillips* standard, as described in the '949 patent at Ex-1101, 5:35-43 and shown in Fig. 3. This is in accordance with the determination of the CALJ in the Related ITC Case. Ex-1107, 17-18.

- D. "means for processing, by the secondary processor, the image header to determine at least one location within system memory to which the secondary processor is coupled to store each data segment" (claim 16)

- 1. Function

82. As recited in claim 16, the function associated with this means-plusfunction limitation is "processing, by the secondary processor, the image header to determine at least one location within system memory to which the secondary processor is coupled to store each data segment" under either the BRI or *Phillips* standard. In the Related ITC Case, the parties (including the Patent Owner) proposed this construction as the corresponding function for this term.<sup>6</sup> Ex-1107, 4-5.

## 2. Structure

83. The purported "structure" identified in the specification that relates to the claimed function is "a modem processor coupled to a system memory," as described in the '949 patent at Ex-1101, 3:9-12, 4:58-5:43, 5:59-6:39, 7:60-10:44, 8:50-56, 9:27-41, and shown in Figs. 1-3.<sup>7</sup> In the Related ITC Case, the Patent Owner proposed this construction as the corresponding structure for this term.<sup>8</sup> Ex-1108, 4-5. Therefore, for purposes of the Petition, the structure for this mean-plus-function term is "a modem processor coupled to a system memory, and equivalents thereof" under either the BRI or *Phillips* standard.

## E. "means for receiving at the secondary processor, from the primary processor via the inter-chip communication bus, each data segment" (claim 16)

1. Function

84. As recited in claim 16, the function associated with this means-plusfunction limitation is "receiving at the secondary processor, from the primary

different argument regarding this claim term in litigation.

<sup>&</sup>lt;sup>6</sup> The CALJ did not construe this term.

<sup>&</sup>lt;sup>7</sup> I do not concede that this structure is sufficient and reserves the right to advance a

<sup>&</sup>lt;sup>8</sup> The CALJ did not construe this term.

processor via the inter-chip communication bus, each data segment" under either the BRI or *Phillips* standard. This is in accordance with the determination of the CALJ in the Related ITC Case. Ex-1107, 19.

#### 2. Structure

85. The corresponding structure for performing the above-stated function is "a secondary processor (*e.g.*, 110, 210, 302) connected to a primary processor (*e.g.*, 104, 204, 301) via an inter-chip communication bus (*e.g.*, 134, 234, 310) for a USB-based High Speed Inter-Chip (HSIC) bus, a MIPI High Speed Synchronous Interface (HSI) bus, a Secure Digital I/O Interface (SDIO) bus, a Universal Asynchronous Receiver/Transmitter (UART) bus, a Serial Peripheral Interface (SPI) bus, or an Inter-Integrated Circuit (I2C) bus, and equivalents thereof" under either the BRI or *Phillips* standard, as described in the '949 patent at Ex-1101, 5:35-43 and shown in Fig. 3. This is in accordance with the determination of the CALJ in the Related ITC Case. Ex-1107, 19.

- F. "means for scatter loading, by the secondary processor, each data segment directly to the determined at least one location within the system memory, and each data segment being scatter loaded based at least in part on the processed image header" (claim 16)

- 1. Function

86. As recited in claim 16, the function associated with this means-plusfunction limitation is "scatter loading, by the secondary processor, each data segment directly to the determined at least one location within the system memory, and each data segment being scatter loaded based at least in part on the processed image header" under either the BRI or *Phillips* standard. In the Related ITC Case, the parties (including the Patent Owner) proposed this construction as the corresponding function for this term.<sup>9</sup> Ex-1108, 6.

#### 2. Structure

87. The purported "structure" identified in the specification that relates to the claimed function is "a modem processor coupled to a system memory," as described in the '949 patent at Ex. 1101, Abstract, 1:24-33, 4:10-15, 4:58-5:43, 5:59-6:39, 7:60-10:44, 8:21-30, 8:62-67, 9:3-8, 9:16-56, 10:13-18 and 10:27-32, and as shown in Figs. 1-3.<sup>10</sup> In the Related ITC Case, the Patent Owner proposed this construction as the corresponding structure for this term.<sup>11</sup> Ex-1108, 6. Therefore, for purposes of this Petition, the structure for this mean-plus-function term is "a modem processor coupled to a system memory, and equivalents thereof" under either the BRI or *Phillips* standard.

<sup>&</sup>lt;sup>9</sup> The CALJ did not construe this term.

<sup>&</sup>lt;sup>10</sup> I do not concede that this structure is sufficient and reserves the right to advance a different argument regarding this claim term in litigation.

<sup>&</sup>lt;sup>11</sup> The CALJ did not construe this term.

#### IX. OVERVIEW OF PRINCIPAL PRIOR ART REFERENCES

#### A. Svensson (Ex-1110)

88. Svensson is generally directed to an "OS-friendly bootloader." Ex-

1110, Abstract. In particular, Svensson discloses a technique for loading code and/or data from memory associated with a host processor to memory associated with a client processor in a multi-processor system. *Id.*, 2:24-27.

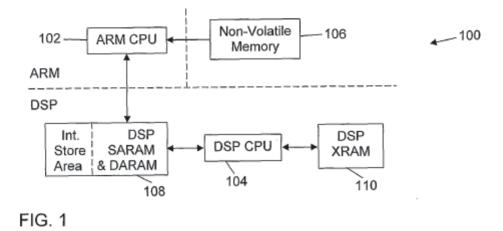

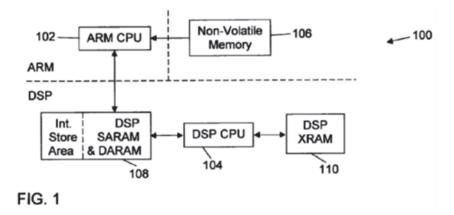

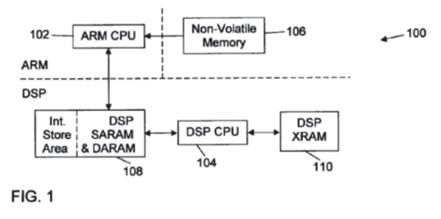

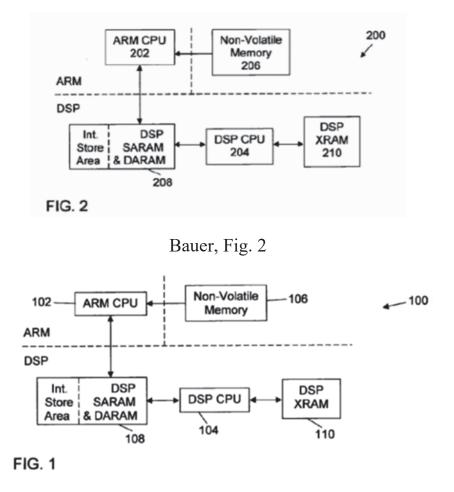

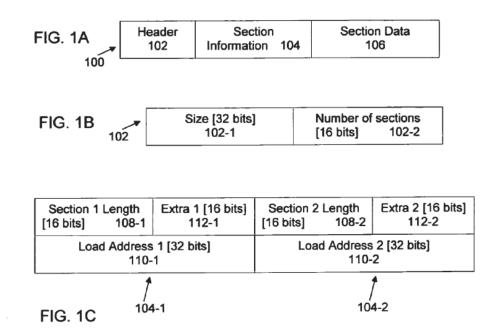

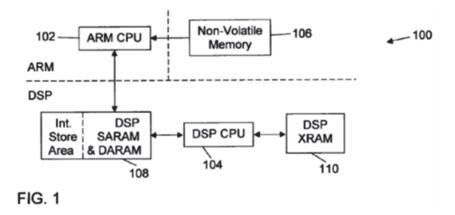

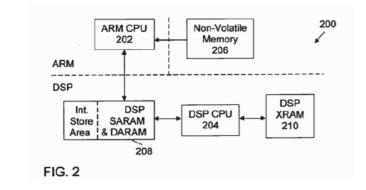

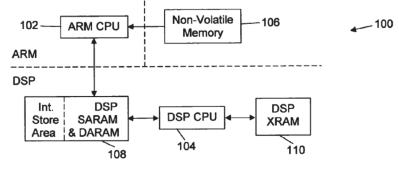

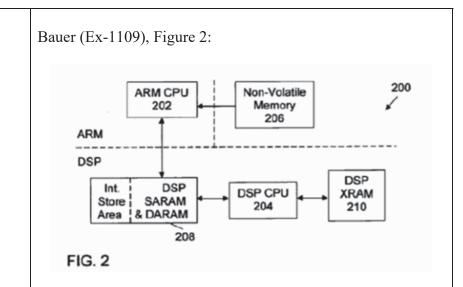

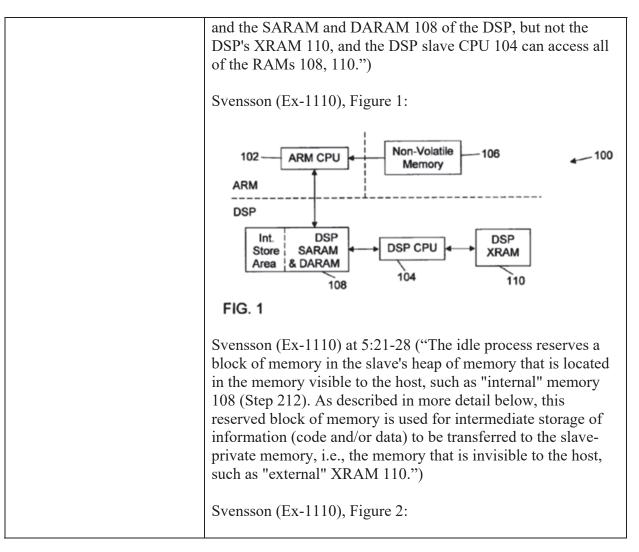

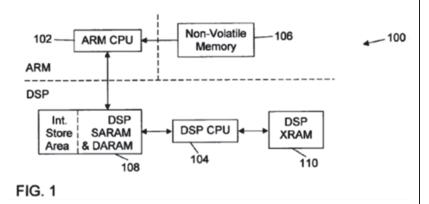

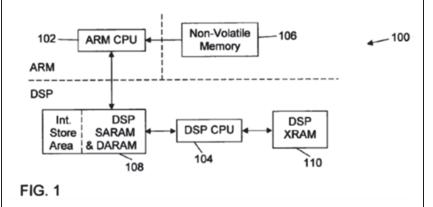

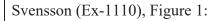

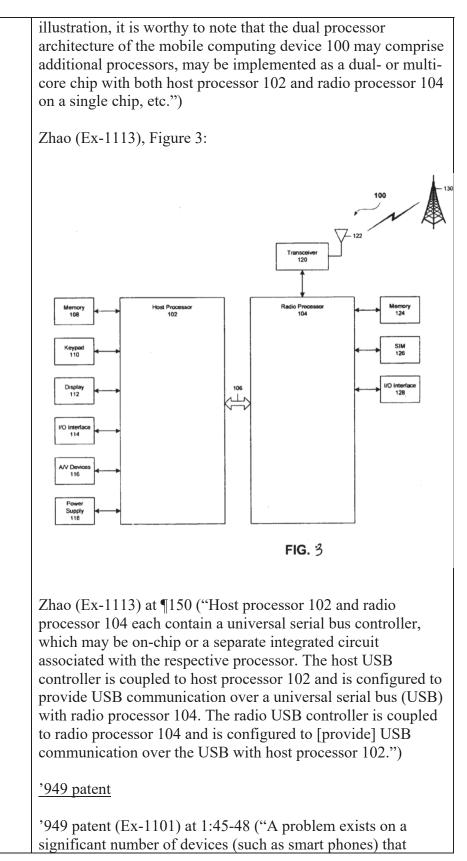

89. Figure 1 of Svensson below shows a multi-processor system 100. Ex-1110, 3:49-50, Fig. 1.

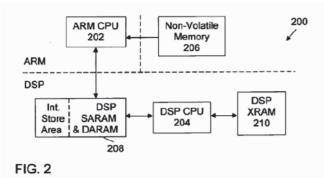

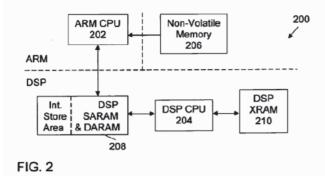

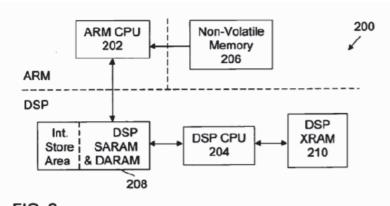

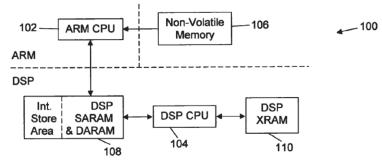

Multi-processor system 100 has an advanced RISC machine (ARM) device and a digital signal processor (DSP) device. *Id.*, 3:54-58, Fig. 1. The ARM device includes a host processor (ARM CPU) 102 that is coupled to a non-volatile memory 106 and to the DSP device. *Id.*, 3:49-63, 4:3-5, Fig. 1. The DSP device includes a client processor (DSP CPU) 104, a system memory (DSP external RAM (XRAM)) 110, and an internal volatile memory (single-access RAM (SARAM) or dual-access RAM (DARAM)) 108 that can have an intermediate storage area (Int.

Store Area). *Id.*, 3:64-4:3, Fig. 1. The multi-processor system includes access paths, such as buses and DMA paths, that connect the CPUs and memories. *Id.*, 4:3-5, Fig. 1. The host processor 102 can directly access the non-volatile memory 106 and the shared volatile memory 108 (including the intermediate storage area) at the client, but not the system memory 110 at the client processor 104. *Id.*, 4:5-8, Fig. 1. The client processor 104, on the other hand, can directly access the shared volatile memory 108 as well as the system memory 110, but not the non-volatile memory 106 coupled to the host. *Id.*

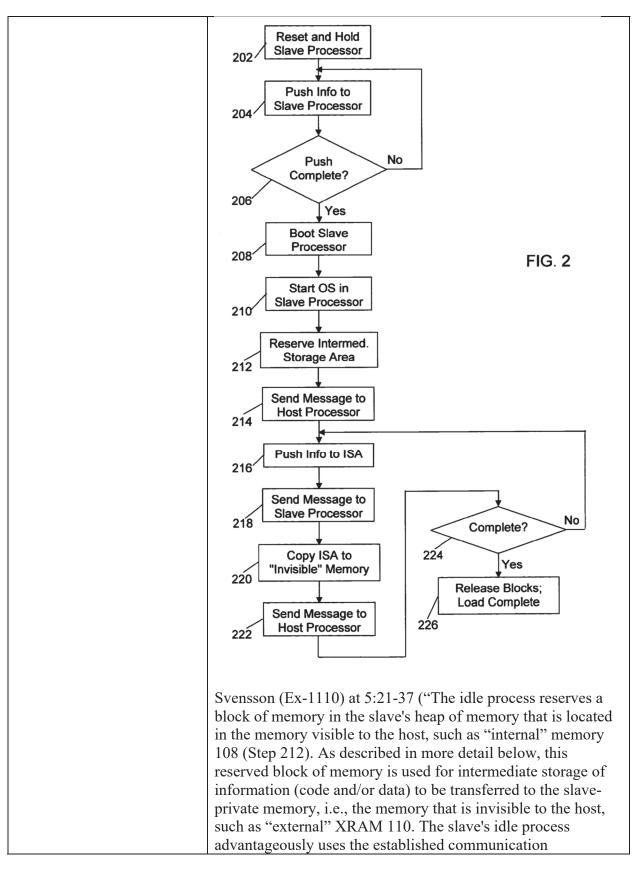

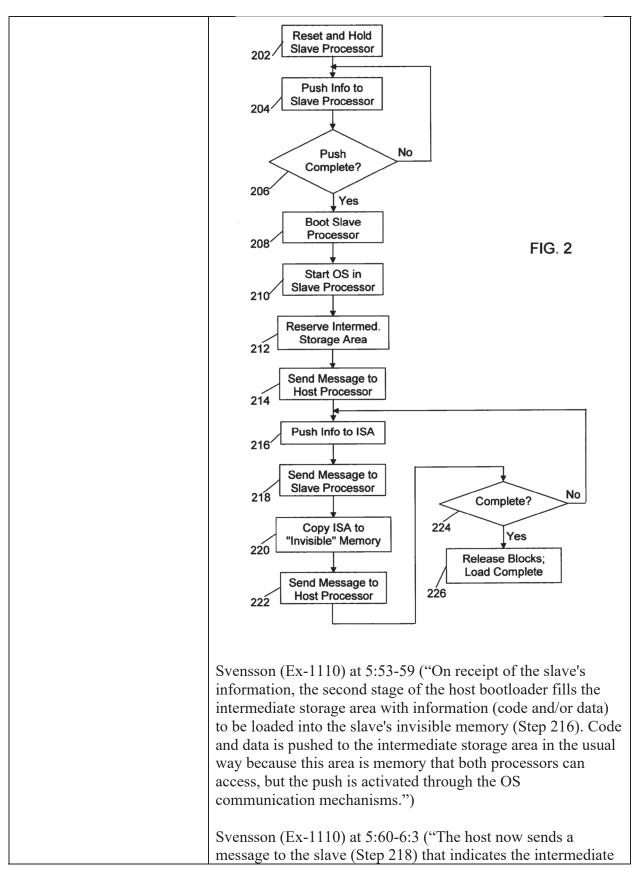

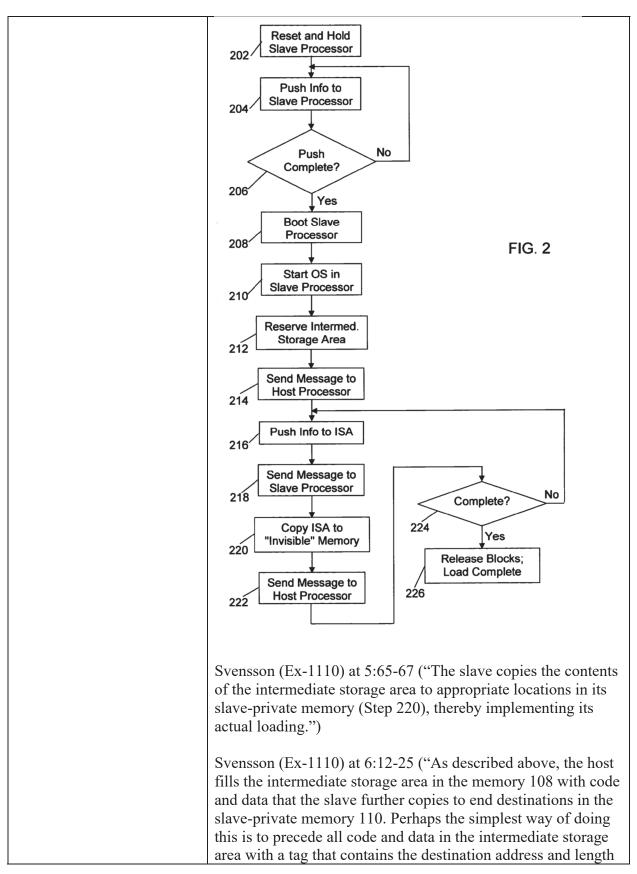

90. Svensson discloses that the host processor 102 loads the code and/or data from the non-volatile memory 106 to the intermediate storage area in the shared volatile memory 108 at the client, and the client processor 104 then copies the code and/or data to end destinations in the system memory 110. Ex-1110, 1:11-15, 2:6-20, 4:9-14, 4:22-26, 6:12-15, Fig. 1; *see also id.*, 4:15-6:11, Fig. 2. Svensson describes the intermediate storage area as "a block of [reserved] memory in the slave's heap of memory that is located in the memory visible to the host, such as 'internal memory 108''' and is "used for intermediate storage of information (code and/or data) to be transferred to the slave-private memory, i.e., the memory that is invisible to the host, such as 'external' XRAM 110." *Id.*, 5:21-36, Fig. 1.

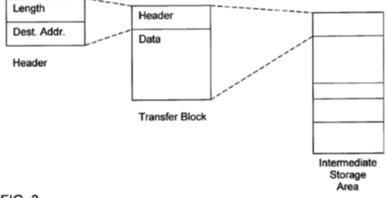

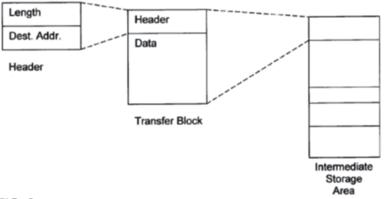

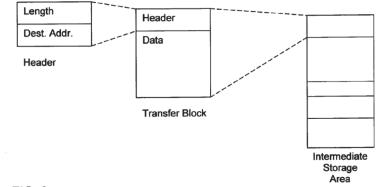

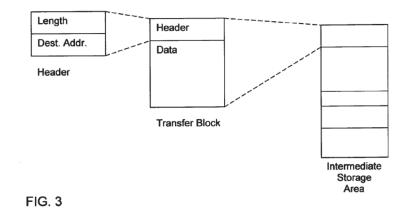

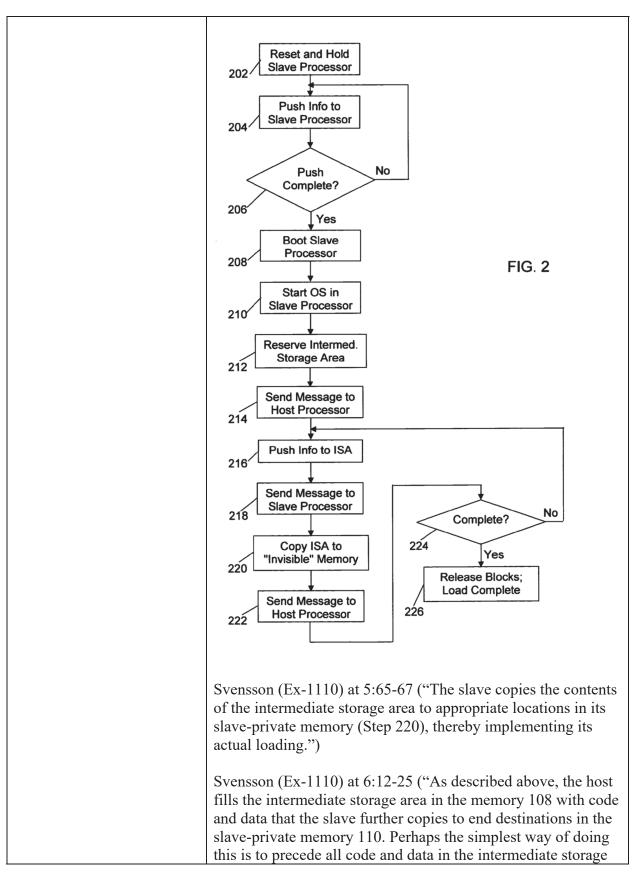

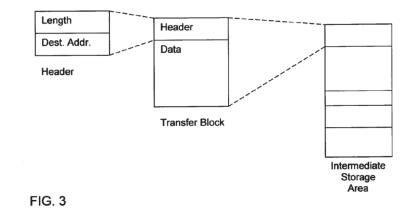

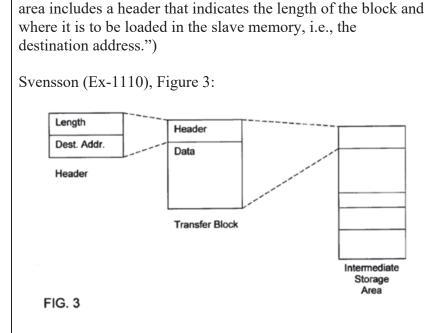

91. Figure 3 of Svensson below shows how the code and/or data can be transferred from the host processor into the intermediate storage area using one or more transfer blocks. *Id.*, 6:12-23, Fig. 3.

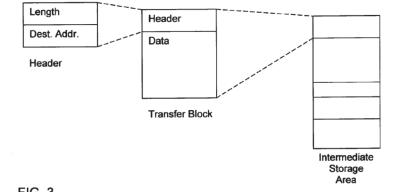

Each transfer block includes a header that indicates the length (Length) of the block and a destination address (Dest. Addr.) indicating where the block is to be loaded in the system memory 110. *Id.* As shown by the dashed lines in Figure 3, several such blocks may be concatenated in the intermediate storage area. *Id.*, 6:23-25, Fig. 3. Svensson further discloses that the size of the code and/or data can be larger than the intermediate storage area. *Id.*, 6:26-28, 6:37-43.

92. Svensson discloses that the client receives code and/or data in one or more transfer blocks from the host processor 102. Ex-1110, 6:12-25, 6:60-7:2, Fig.

1. For each transfer block, the client processor 104 first reads the header, which includes the destination address for the data block. *Id.*, 5:65-67, 6:15-23, Fig. 2. The client processor then uses the destination address to load the data block into

the system memory 110. *Id.* Svensson discloses that the client processor 104 can have a communication mechanism such as a DMA unit "to perform the actual transfers of information between memories." *Id.*, 6:48-58, 6:60-7:2, 7:52-60.

## **B.** Bauer (Ex-1109)

93. Bauer is closely interrelated with Svensson. Bauer has the same four inventors and the same assignee as Svensson, and was filed only four months after Svensson. Ex-1109, cover; Ex-1110, cover.

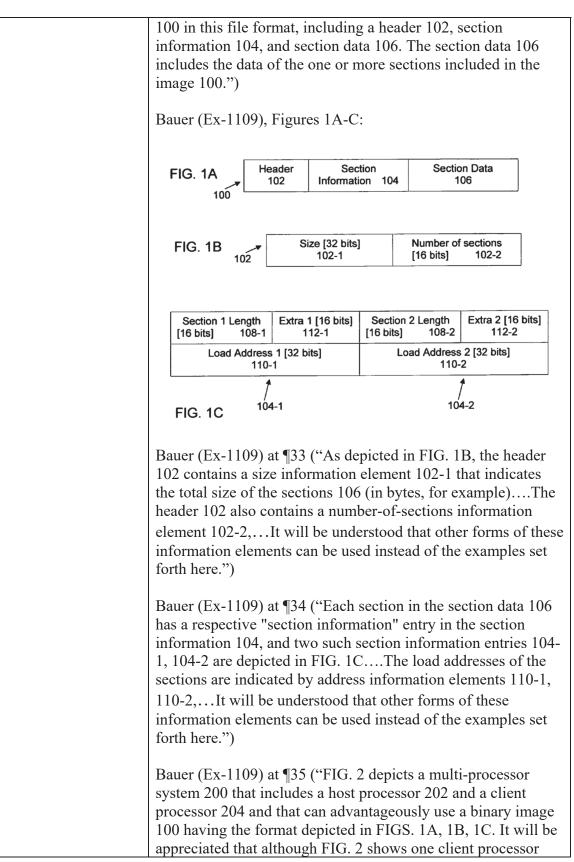

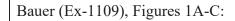

94. Bauer describes a new file format that is an improvement upon the file format described in Svensson. Instead of using a separate block header to store a destination address for each block of an image, the file format in Bauer has that information collected in one place as section information. Ex-1109, ¶¶27, 32-34, 43, Figs. 1A-1C. Bauer describes the benefit of this approach: "[t]his simplifies optimization in a number of circumstances, for instance, if sections are to be loaded into memory" and "makes memory loading efficient as there is no need to search through an image for section headers when loading." *Id.*, ¶43; *see also id.*, ¶16 ("Greater efficiency in loading data can reduce response times in such systems, and space-efficient storage saves valuable memory."), ¶27. This section information is near the beginning of the image—after the header but before all the data sections of an image—so that the section information can be retrieved separately before the data sections are read and processed. *Id.*, Abstract, ¶¶28-30, 47, Figs. 1A-1C.

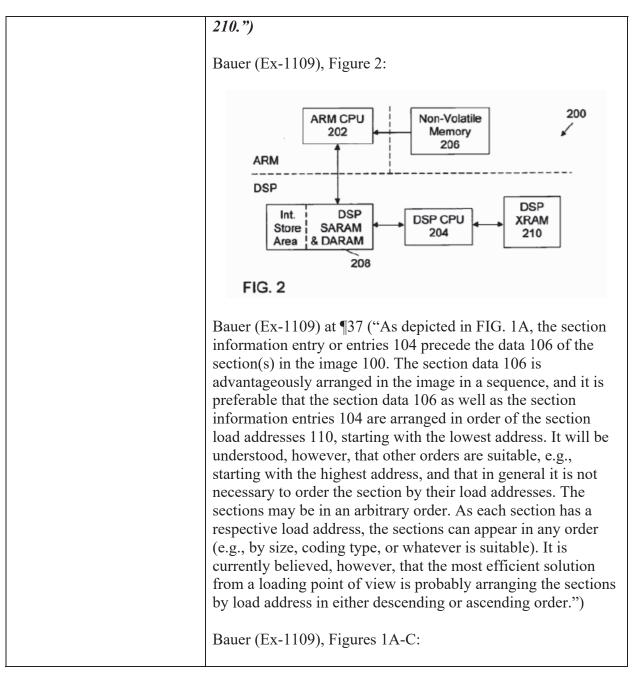

95. Bauer teaches that this new file format can be used in the same multiprocessor system described in Svensson. Bauer shows and describes the same system as Svensson and even cites to Svensson as an example of a program loader for loading an image with this file format in that same multi-processor system.

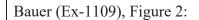

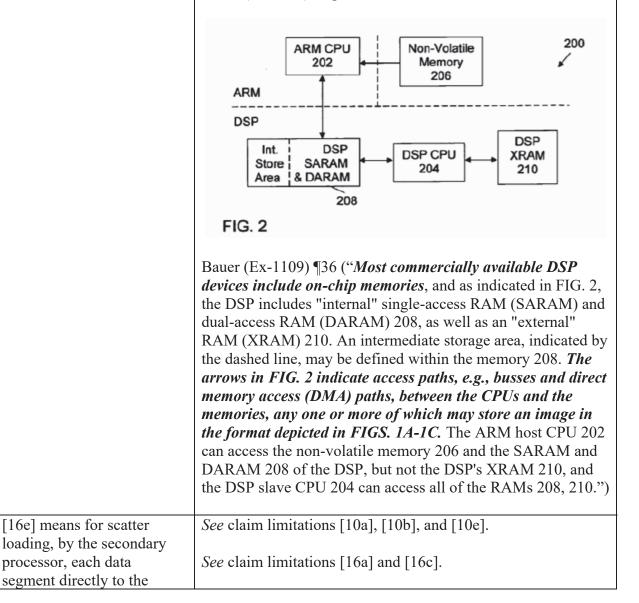

96. In particular, Bauer discloses the same circuit architecture as Svensson—Bauer and Svensson disclose loading different image file formats from an ARM device to a DSP device's system memory in the same multi-processor system. *See* Ex-1109, Fig. 2, ¶¶35, 36; *cf.* Ex-1110, Fig. 1, 3:49-4:8.

Bauer, Fig. 2

Svensson, Fig. 1

97. Bauer, in its detailed description of the specification, cites to Svensson as one example of a program loader that can use the invention described in Bauer:

There are many possible applications of this format and its individually coded sections....Object code and data can also be stored in this file format, with a program loader reading the stored information and processing stored sections accordingly. One example of such a program loader is described in U.S. patent application Ser. No. 11/040,798 filed on Jan. 22, 2005, by M. Svensson et al. for "Operating-System-Friendly Bootloader."

Ex-1109, ¶31.

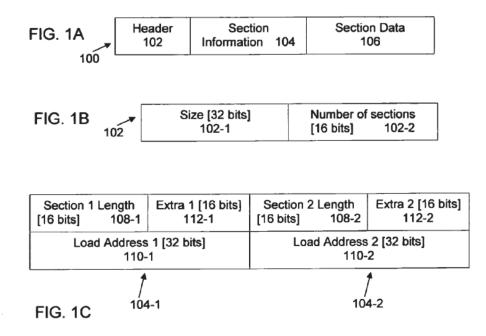

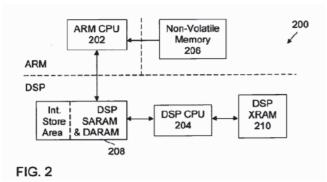

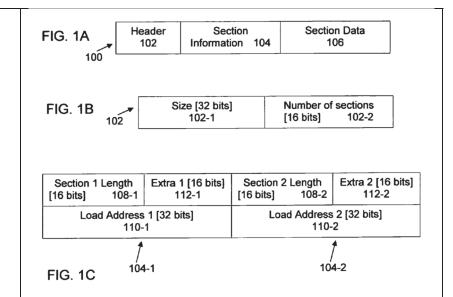

98. Figures 1A-1C of Bauer below show the file format of the binary data image 100:

## U.S. Patent No. 8,838,949 Declaration of Bill Lin, Ph.D.

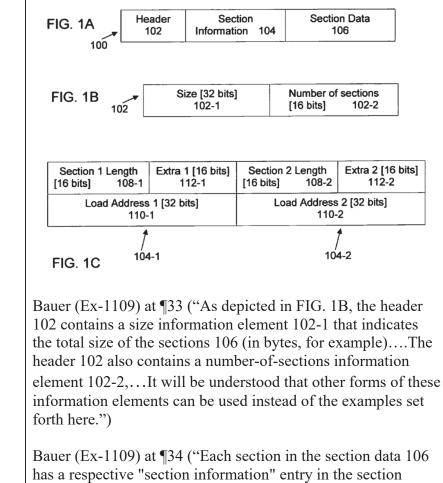

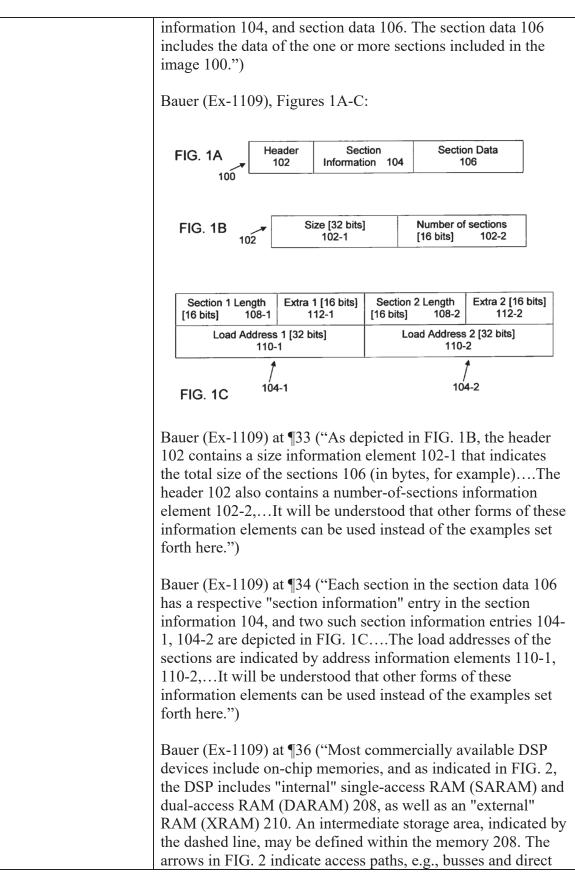

Ex-1109, Figs. 1A-1C.

99. As shown in Figure 1A, the file format includes a header 102, section information 104, and section data 106. Ex-1109, ¶32, Fig. 1A. As shown in Figure 1B, the header 102 indicates the size 102-1 and number of sections 102-2 in the section data 106. *Id.*, ¶33, Fig. 1B. As shown in Figure 1C, the section information 104 indicates the length 108 and load (or destination) address 110 of each section in the section data 106. *Id.*, ¶34, Fig. 1C. Each data section has its own load address in the section information and can be arranged in the image in any suitable order (*e.g.*, in order of load address or in an arbitrary order). *Id.*, ¶37. The section data 106 includes one or more sections containing object code and data for the image. *Id.*, ¶32-34, Figs. 1A-1C.

100. Bauer discloses that the file format shown in Figures 1A-1C can be stored in any of the memories of multi-processor system 200, including the nonvolatile memory 206 at the host, the shared volatile memory 208 that has an intermediate storage area (Int. Store Area), and the system memory 210. Ex-1109, ¶35 ("The memory 206 may be a ROM, a flash memory, or other type of nonvolatile memory device, within which an image in the format depicted in FIGS. 1A-1C can be stored."), ¶36 ("…between the CPUs and the memories, any one or more of which may store an image in the format depicted in FIGS. 1A-1C."), Fig. 2. Bauer also discloses that the client processor can have an operating system memory manager for "load[ing] and unload[ing] sections of memory" or a DMA unit for "DMA transfer[s]." *Id.*, ¶¶31, 38.

#### C. Kim (Ex-1111) (Including English Translation (Ex-1112))

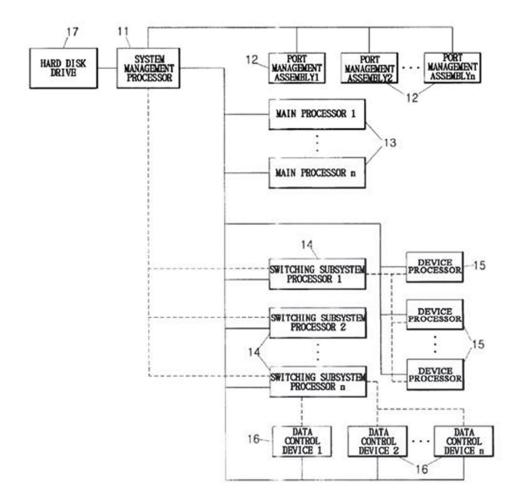

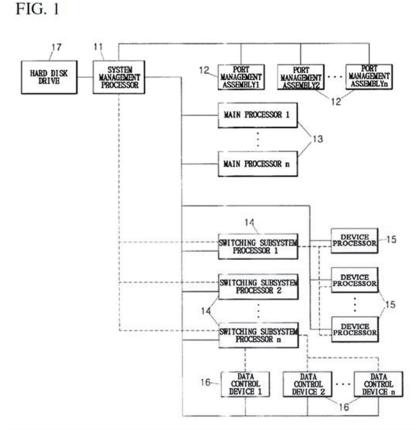

101. Kim discloses a multi-processor system in which a secondary processor receives program block header information separately from a primary processor before receiving a corresponding program block from the primary processor during a loading procedure. Ex-1112, 5:12-6:5. Figure 1 of Kim below shows a primary processor (system management processor 11) that is coupled to a plurality of secondary processors (main processors 13, switching subsystem processors 14, device processors 15), as well as to a non-volatile memory (hard disk drive 17). *Id.*, 4:7-14, Fig. 1.

FIG. 1 17 11 SYSTEM MANAGEMENT PROCESSOR PORT MANAGEMENT ASSEMBLY1 PORT MANAGEMENT ASSEMBLY2 PORT MANAGEMENT ASSEMBLYn 12 HARD DISK DRIVE 12 MAIN PROCESSOR 1 13 MAIN PROCESSOR n 14 DEVICE -15 SWITCHING SUBSYSTE PROCESSOR 1 DEVICE SWITCHING SUBSYSTE PROCESSOR 2 15 DEVICE SWITCHING SUBSYSTEM PROCESSOR n DATA CONTROL DEVICE 1 DATA CONTROL DEVICE 2 DATA CONTROL DEVICE n 16 16

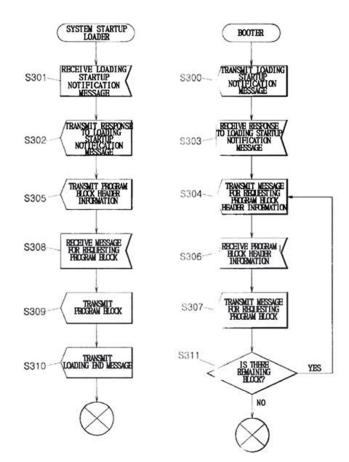

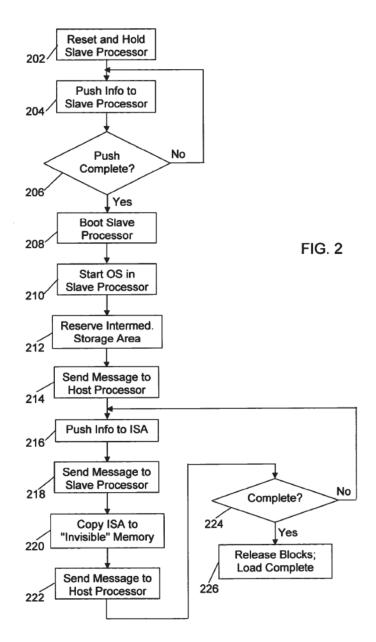

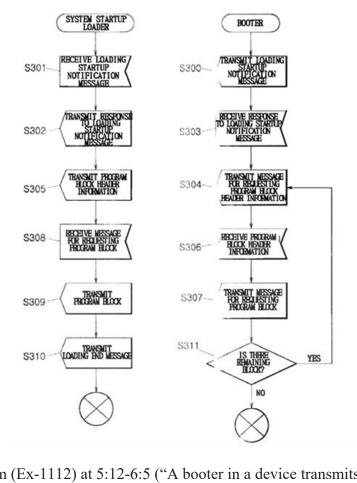

102. Figure 3 of Kim below shows a "conventional loading method" for loading a program stored in the non-volatile memory to one of the plurality of secondary processors. Ex-1112, 5:9-6:7, Fig. 3.

FIG. 3

103. As part of the loading procedure, the secondary processor first

requests the *program block header information* (step 304) from the primary

processor. Ex-1112, 5:16-19, Fig. 3. The program block header information is

then sent (steps S305 and S306) from the primary processor to the secondary

processor. *Id.*, 5:19-21, Fig. 3 Once the secondary processor receives the program

block header information, it then requests a *program block corresponding to actual program content* (step S307) from the primary processor. *Id.*, 5:21-23, Fig.

3. The program block is then sent from the primary processor to the secondary

processor (step S309). Ex-1112, 5:25-6:2, Fig. 3. In this way, the multi-processor system of Kim provides a system in which the program block header information is transmitted and *received separately* from the program block.

## **D. Zhao** (Ex-1113)

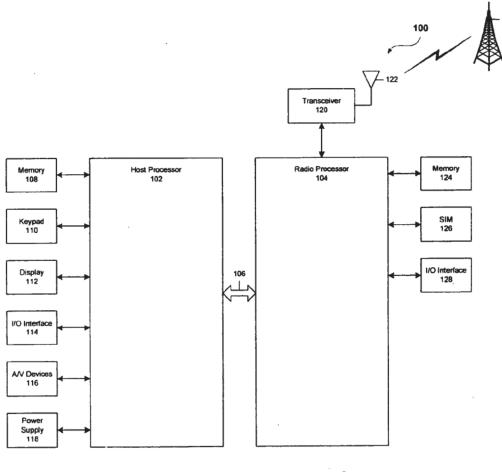

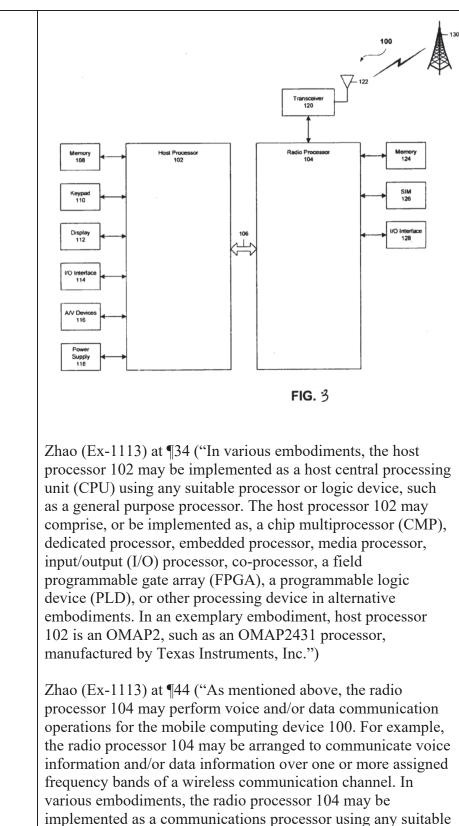

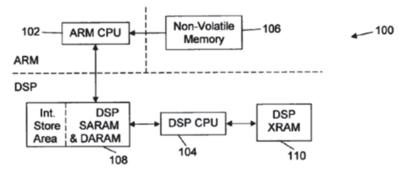

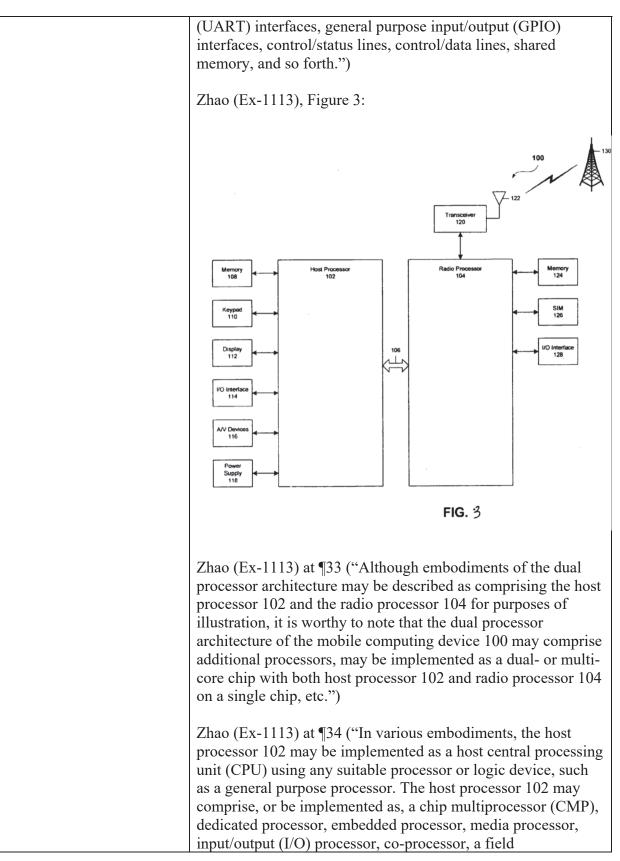

104. Zhao discloses a "mobile computing device" that can be, for example, a smartphone or laptop computer. Ex-1113, ¶26. As shown in Figure 3 of Zhao below, the mobile computing device 100 "may comprise a dual processor architecture including a host processor 102 and a radio processor 104" that can "communicate with each other using interfaces 106." *Id.*, ¶32, Fig. 3.

105. Radio processor 104 "may be implemented as a communications processor using any suitable processor or logic device, such as a modem processor or baseband processor." *Id.*, ¶44. Interfaces 106 can include "one or more universal serial bus (USB) interfaces, micro-USB interfaces, universal asynchronous receiver-transmitter (UART) interfaces, general purpose input/output (GPIO) interfaces, control/status lines, control/data lines, shared memory, and so forth." *Id.*, ¶32, Fig. 5.

#### X. SPECIFIC GROUNDS FOR CHALLENGE

106. In the following sections I describe in detail how the prior art renders obvious each and every limitation of claims 10-17 of the '949 patent.

## A. Ground 1: Claims 10-15 Are Rendered Obvious By The Combination Of Bauer, Svensson, And Kim

## 1. Reference to "Bauer and Svensson Combined"

107. Bauer is so closely interrelated with Svensson that, for ease of reference, the declaration uses "Bauer and Svensson combined" to illustrate what Bauer alone, or Bauer in combination with Svensson, teaches to a person of ordinary skill in the art.

108. Bauer has the same four inventors and the same assignee as Svensson, and was filed only four months after Svensson. Ex-1109, cover; Ex-1110, cover. Bauer describes a file format where section information containing destination addresses for each data section in an image is collected in one place and precedes all the data sections, and explicitly describes that format as an improvement over using multiple, separate block headers as described in Svensson. Ex-1109, ¶¶27, 32-34, 43, Figs. 1A-1C. *See* Section IX.B;

109. Bauer teaches that its file format can be used in the same multiprocessor system as Svensson. Indeed, they have the exact same figures of that system. *See* Ex-1109, Fig. 2 (below), ¶¶35, 36; *cf.* Ex-1110, Fig. 1 (below), 3:49-4:8.

Svensson, Fig. 1

110. In addition, Bauer explicitly cites to Svensson as an example forloading an image with Bauer's file format in that same multi-processor system.Ex-1109, ¶31. See Section IX.B;

111. For these same reasons, as explained in more detail below, it would have been obvious to a person of ordinary skill in the art to combine Svensson with Bauer.

112. Although it is readily apparent that the file format of Bauer can be used in the multiprocessor system of Svensson, Bauer does not describe the multiprocessor system with the same level of detail as Svensson. Because of that, this declaration refers to "Bauer and Svensson combined," but is clear in identifying the relevant disclosures from each reference in its citations.

## 2. Claim 10

## 113. Claim 10 is rendered obvious by Bauer and Svensson combined;

however, to the extent the Patent Owner contends that Bauer and Svensson combined does not teach that different parts of an executable software image are received separately (claim [10b]), this claim is rendered obvious by the combination of Bauer, Svensson, and Kim.

> a. [10a] "A method comprising: receiving at a secondary processor, from a primary processor via an inter-chip communication bus, an image header for an executable software image for the secondary processor that is stored in memory coupled to the primary processor, the executable software image comprising the image header and at least one data segment;"