#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property Organization International Bureau

## AIPO OMPI

## (10) International Publication Number WO 2010/091105 A2

#### (43) International Publication Date 12 August 2010 (12.08.2010)

(51) International Patent Classification: H03K 17/22 (2006.01)

(21) International Application Number:

PCT/US2010/023081

(22) International Filing Date:

3 February 2010 (03.02.2010)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

12/365,559 4 February 2009 (04.02.2009) US

(71) Applicant (for all designated States except US): QUAL-COMM INCORPORATED [US/US]; Attn: International Ip Administration, 5775 Morehouse Drive, San Diego, CA 92121 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): KWON, Cheng, Ki [KR/US]; 5775 Morehouse Drive, San Diego, CA 92121 (US). MOHAN, Vivek [US/US]; 5775 Morehouse Drive, San Diego, CA 92121 (US).

(74) Agent: TALPALATSKY, Sam; 5775 Morehouse Drive, San Diego, CA 92121 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Declarations under Rule 4.17:

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

#### (54) Title: MULTIPLE SUPPLY-VOLTAGE POWER-UP/DOWN DETECTORS

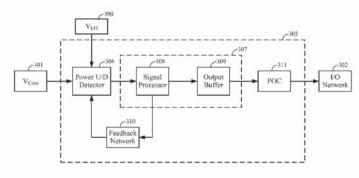

FIG. 3B

(57) Abstract: A multiple supply voltage device includes an input/output (I/O) network operative at a first supply voltage, a core network coupled to the I/O network and operative at a second supply voltage, and a power-on-control (POC) network coupled to the I/O network and the core network. The POC network is configured to transmit a POC signal to the I/O network and includes an adjustable current power up/down detector configured to detect a power state of the core network. The POC network also includes processing circuitry coupled to the adjustable current power up/down detector and configured to process the power state into the POC signal, and one or more feedback circuits. For reducing the leakage current while also improving the power-up/down detector speed, the feedback circuit(s) are coupled to the adjustable current power up/down detector and configured to

1

PCT/US2010/023081

#### MULTIPLE SUPPLY-VOLTAGE POWER-UP/DOWN DETECTORS

#### TECHNICAL FIELD

[0001] The present disclosure is related, in general, to integrated circuit devices and, more particularly, to power up/down detectors for multiple supply voltages devices.

#### BACKGROUND

[0002] As technology has advanced there has been an increased ability to include more and more devices and components within integrated circuits.

Semiconductor fabrication techniques have allowed these embedded devices to become smaller and have lower voltage requirements, while still operating at high-speeds. However, because these new integrated devices often interface with older technology devices or legacy products, input/output (I/O) circuits within the integrated circuit have remained at higher operating voltages to interface with the higher voltage requirements of these older systems. Therefore, many newer integrated circuit devices include dual power supplies: one lower-voltage power supply for the internally operating or core applications, and a second higher-voltage power supply for the I/O circuits and devices.

[0003] Core devices and applications communicate with operations outside of the integrated component through the I/O devices. In order to facilitate communication between the core and I/O devices, level shifters are employed. Because the I/O devices are connected to the core devices through level shifters, problems may occur when the core devices are powered-down. Powering down or power collapsing is a common technique used to save power when no device operations are pending or in progress. For example, if the core network is power collapsed, it is possible that the level shifters, whether through stray currents or the like, could send a signal to the I/O devices for transmission. The I/O devices assume that the core devices have initiated this communication, and will, therefore, transmit the erroneous signal into the external environment.

[0004] It has been found useful to have the I/O devices in a known state when the core networks are powered down. In order to guarantee these known states,

Annia Ina -- Ourleanne Incomanded

solutions have included the addition of hardware or software for managing additional external signals to control the I/O circuitry. By using these external signals, the I/O circuitry can be controlled (e.g., placed in a known state) whenever the core power is collapsed. However, whether implementing this external signal management system using hardware or software, a considerable amount of delay is added to the operation of the integrated device. Although hardware is slightly faster than software controls, , hardware solutions may have problems caused by significant additional power leakage on the I/O device side.

[0005] One hardware solution currently in use provides power-up/down detectors to generate a power-on/off-control (POC) signal internally. The POC signal instructs the I/O devices when the core devices are shut down. FIGURE 1 is a circuit diagram illustrating standard POC system 10 for multiple supply voltage devices. POC system 10 is made up of three functional blocks: power-up/down detector 100, signal amplifier 101, and output stage 102. Power-up/down detector 100 has PMOS transistor M1 and NMOS transistors M2 – M3. The gate terminals for each of M1-M3 are connected to core power supply 103,  $V_{core}$ . When core power supply 103 is power collapsed, M2 and M3 are switched off while M1 is switched on, pulling up the input node to amplifier 105 to  $V_{I/O}$ , i.e., I/O power supply 104. A "high" signal is input into amplifier 105 which inverts the output to a "low" signal. In output stage 102, the low signal from amplifier 105 is processed in output buffer 106 and again inverted to a high signal for POC 107. The high signal for POC 107 is transmitted to the I/O circuitry indicating that core power supply 103 has been shut down.

[0006] When core power supply 103, V<sub>core</sub>, is on, M1 becomes very weak and M2 and M3 both switch strongly on, pulling the input node to amplifier 105 to V<sub>SS</sub>, i.e., core power supply 103. V<sub>SS</sub> is considered the logical low signal. Therefore, amplifier 105 inverts it to a high signal which is then processed in output buffer 106 and inverted again to a low signal. This signal detection process operates acceptably when either I/O power supply 104 is on and core power supply 103 is power collapsed or when core power supply 103 is powered-up before I/O power supply 104 is powered-up. However, when I/O power supply 104 is powered-up before core power supply 103 powers-up, substantial current leakage may occur in the power up/down detector 100 or in the POC 10.

WO 2010/091105 PCT/US2010/023081

3

[0007] In the situation where I/O power supply 104 is on and core power supply 103 is off, M1 is switched on with M2 and M3 switched off. When core power supply 103 is then powered up, M2 and M3 switch on, and M1 becomes very weak. However, before M1 can switch completely off, there is a period in which all three transistors within power up/down detector 100 are on. Thus, a virtual short is created to ground causing a significant amount of current to flow from I/O power supply 104 to ground. This "glitch" current consumes unnecessary power.

[0008] In order to reduce this stray power consumption, one solution may be adopted to decrease the sizes of transistors M1-M3. By reducing the size of M1-M3, the actual amount of current that can pass through the transistors is physically limited. However, because the transistors are now smaller, their switching speeds are also reduced. The reduced switching speed translates into less sensitivity in detecting power-up/down of core supply voltage 103 or longer processing time for power-up/down events.

[0009] FIGURE 2 is an illustration of diagram 20 presenting the signal interactions in POC circuit 10 of FIGURE 1. Diagram 20 includes power supply diagram 21 and POC diagram 22. As I/O power supply 104 is powered up, there is a steady increase until it reaches V<sub>I/O</sub>. POC 107 follows I/O power supply 104 as it powers up to reach the high level. Similarly, when I/O power supply 104 maintains steady at V<sub>I/O</sub> at time 200, POC 107 remains steady at the high signal. When core power supply 103 begins to power on at time 201 power up/down detector 100 (FIGURE 1) takes a little time to actually detect this new power level. Once detected, at time 202, POC 107 is switched to the low value. POC 107 should, thereafter, remain at the low level until core power supply 103 is power collapsed, between times 203 and 205. Again, because power up/down detector 100 (FIGURE 1) takes a little time to actually detect the new power level, POC 107 remains in the low state until time 204, when the powering down is actually detected by power up/down detector 100. This low state time, between time 202 and 204 is referred to as the normal operation region. Once core power supply 103 is completely off or power collapsed at time 205, the input to amplifier 105 (FIGURE 1) is again pulled up to the high signal. POC 107 will then follow I/O power supply 104 as it also powers down between times 206 and 207.

[0010] The leakage current between I/O power supply 104 and ground can be lessened because of the smaller transistor size. Thus, during the time between times 201 and 205 any leakage that occurs is reduced. However, this reduced leakage comes at the price of faster detection. If POC circuit 10 may include the lower-threshold or bigger transistors, switching/detecting times would be faster. For example, as core power supply 103 begins to power up at time 201, the lower-threshold or bigger transistors of power up/down detector 100 would detect the power-up at time 208, instead of time 202. Moreover when core power supply 103 begins powering down at time 203, the power up/down detector 100 would detect the power-down at time 209, instead of time 204. This increase may be represented by the difference between the time periods of time 202 to 204 vs. time 208 to 209. Therefore, the conventional solutions still have problems with leakage and switching times.

#### SUMMARY

[0011] Various representative embodiments of the disclosure relate to integrated devices having multiple supply voltages. Further representative embodiments of the present disclosure relate to methods for reducing power consumption in a power on/off control (POC) network of a multiple supply voltage device. Additional representative embodiments of the present disclosure relate to systems for reducing power consumption in a POC network of a multiple supply voltage device.

[0012] A multiple supply voltage device includes a core network operative at a first supply voltage and a control network coupled to the core network. The control network is configured to transmit a control signal. The control network includes an up/down (up/down) detector configured to detect a power state of the core network. The control network further includes processing circuitry coupled to the up/down detector and is configured to generate the control signal based on the power state. The control network further includes one or more feedback circuits coupled to the up/down detector. The one or more feedback circuits are configured to provide feedback signals to adjust a current capacity of said up/down detector.

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

### **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

#### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.