Exhibit 1024 Apple v. Qualcomm IPR2018-01316

Fourth Edition

# John F. Wakerly

*Cisco Systems, Inc. Stanford University*

Upper Saddle River, New Jersey 07458

Wakerly, John F.

Digital design: principles and practices/ John F. Wakerly.--4th ed.

p. cm.

Includes index

ISBN 0-13-186389-4

1. Digital integrated circuits--Design and construction. I. Title

TK7874.65,W34 2005

621.39'5-dc22

2005048710

Vice President and Editorial Director, ECS: Marcia Horton Editorial Assistant: Richard Virginia Executive Managing Editor: Vince O'Brien Managing Editor: David A. George Production Editor: Scott Disanno Director of Creative Services: Paul Belfanti Art Director: Kenny Beck Cover Designer: Bruce Kenselaar Art Editor: Xiaohong Zhu Manufacturing Manager: Alexis Heydt-Long Manufacturing Buyer: Lisa McDowell Senior Marketing Manager: Holly Stark About the Cover: Original cover artwork © 2001 Ken Bakeman, www.kennyzen.com

© 2006, 2000, 1994, 1990 by Pearson Education, Inc. Pearson Prentice Hall Pearson Education Inc. Upper Saddle River, NJ 07458

Pearson Prentice Hall<sup>™</sup> is a trademark of Pearson Education Inc.

The author and publisher of this book have used their best efforts in preparing this book. These efforts include the development, research, and testing of the theories and programs to determine their effectiveness. The author and publisher shall not be liable in any event for incidental or consequential damages with, or arising out of, the furnishing, performance, or use of these programs.

Verilog is a trademark of Cadence Design Systems, Inc. Silos is a trademark of Simucad Inc. Synopsys, and Foundation Express are trademarks of Synopsys, Inc. Xilinx<sup>®</sup> is a registered trademark of Xilinx Corp. Aldec is a trademark of Aldec.

ISBN 0-13-186389-4

11 12 13 14 15 16 17 18 19 20 V092 18 17 16 15

Pearson Education Ltd., London Pearson Education Australia Pty., Ltd., Sydney Pearson Education Singapore, Pte. Ltd. Pearson Education North Asia Ltd., Hong Kong Pearson Education Canada, Inc., Toronto Pearson Educación de Mexico, S.A. de C.V. Pearson Education—Japan, Tokyo Pearson Education Malaysia, Pte. Ltd. Pearson Education, Inc., Upper Saddle River, New Jersey

# CONTENTS

#### PREFACE xv

#### 1 INTRODUCTION 1

- 1.1 About Digital Design 1

- 1.2 Analog versus Digital 3

- 1.3 Digital Devices 6

- 1.4 Electronic Aspects of Digital Design 7

- 1.5 Software Aspects of Digital Design 8

- 1.6 Integrated Circuits 11

- 1.7 Programmable Logic Devices 14

- 1.8 Application-Specific ICs 16

- 1.9 Printed-Circuit Boards 17

- 1.10 Digital-Design Levels 18

- 1.11 The Name of the Game 22

- 1.12 Going Forward 23

- Drill Problems 23

#### 2 NUMBER SYSTEMS AND CODES 25

- 2.1 Positional Number Systems 26

- 2.2 Octal and Hexadecimal Numbers 27

- 2.3 General Positional-Number-System Conversions 29

- 2.4 Addition and Subtraction of Nondecimal Numbers 32

- 2.5 Representation of Negative Numbers 34

- 2.5.1 Signed-Magnitude Representation 2.5.2 Complement Number Systems

- 2.5.3 Radix-Complement Representation

- 2.5.4 Two's-Complement Representation

- 2.5.5 Diminished Radix-Complement Representation

- 2.5.6 Ones'-Complement Representation 2.5.7 Excess Representations

- 2.6 Two's-Complement Addition and Subtraction 39

- 2.6.1 Addition Rules 2.6.2 A Graphical View 2.6.3 Overflow

- 2.6.4 Subtraction Rules 2.6.5 Two's-Complement and Unsigned Binary Numbers

- 2.7 Ones'-Complement Addition and Subtraction 44

- 2.8 Binary Multiplication 45

viii Contents

2.9 Binary Division 47

- 2.10 Binary Codes for Decimal Numbers 48

- 2.11 Gray Code 51

- 2.12 Character Codes 53

- 2.13 Codes for Actions, Conditions, and States 53

- 2.14 n-Cubes and Distance 57

- 2.15 Codes for Detecting and Correcting Errors 58

- 2.15.1 Error-Detecting Codes

- 2.15.2 Error-Correcting and Multiple-Error-Detecting Codes

- 2.15.3 Hamming Codes 2.15.4 CRC Codes

- 2.15.5 Two-Dimensional Codes 2.15.6 Checksum Codes

- 2.15.7 m-out-of-n Codes

- 2.16

Codes for Serial Data Transmission and Storage

69

2.16.1

Parallel and Serial Data

2.16.2

Serial Line Codes

- References 73

- Drill Problems 74

Exercises 76

#### 3 DIGITAL CIRCUITS 79

- 3.1 Logic Signals and Gates 80

- 3.2 Logic Families 84

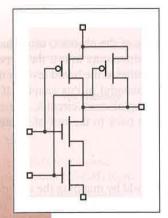

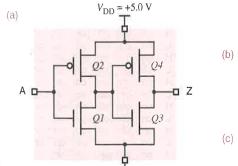

- 3.3 CMOS Logic 86

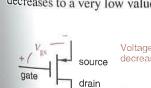

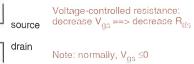

- 3.3.1 CMOS Logic Levels 3.3.2 MOS Transistors

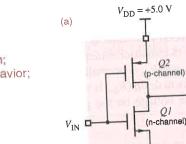

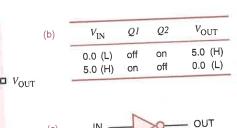

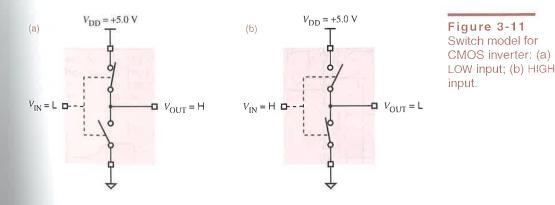

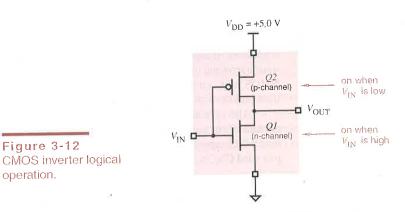

- 3.3.3 Basic CMOS Inverter Circuit

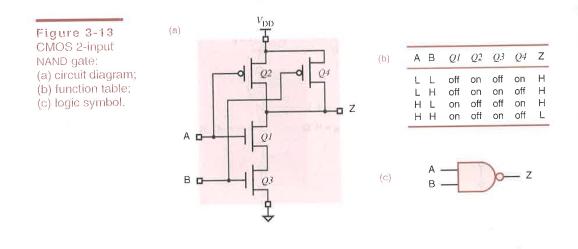

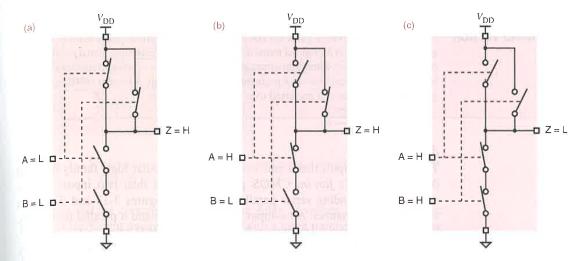

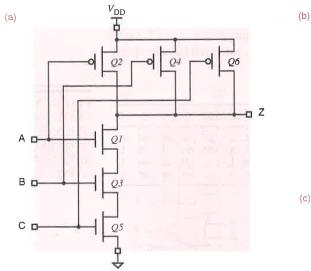

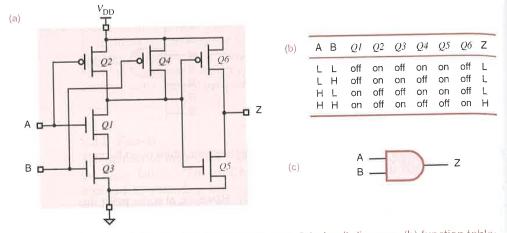

- 3,3,4 CMOS NAND and NOR Gates 3.3.5 Fan-In

- 3.3.6 Noninverting Gates

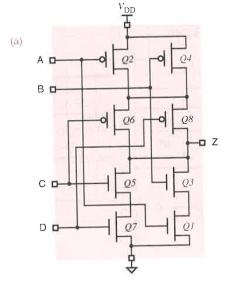

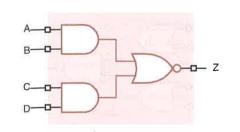

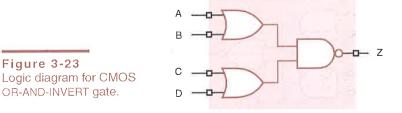

- 3.3.7 CMOS AND-OR-INVERT and OR-AND-INVERT Gates

- 3.4 Electrical Behavior of CMOS Circuits 96

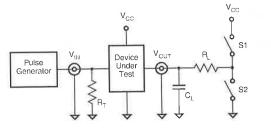

- 3.4.1 Overview 3.4.2 Data Sheets and Specifications

- 3.5 CMOS Static Electrical Behavior 101

- 3.5.1 Logic Levels and Noise Margins

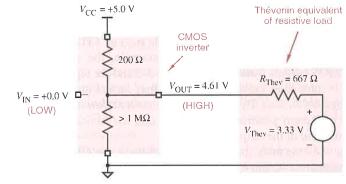

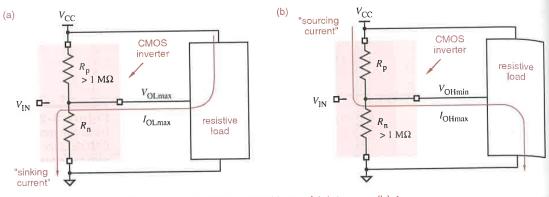

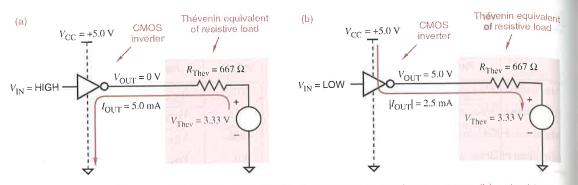

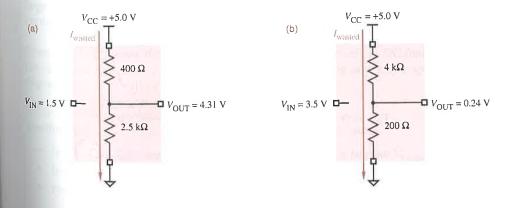

- 3.5.2 Circuit Behavior with Resistive Loads

- 3.5.3 Circuit Behavior with Nonideal Inputs 3.5.4 Fanout

- 3.5.5 Effects of Loading 3.5.6 Unused Inputs

- 3.5.7 How to Destroy a CMOS Device

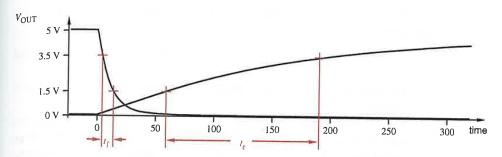

- 3.6 CMOS Dynamic Electrical Behavior 114

- 3.6.1 Transition Time 3.6.2 Propagation Delay

- 3.6.3 Power Consumption

- 3.6.4 Current Spikes and Decoupling Capacitors

- 3.6.5 Inductive Effects

- 3.6.6 Simultaneous Switching and Ground Bounce

- 3.7 Other CMOS Input and Output Structures 129

- 3.7.1 Transmission Gates 3.7.2 Schmitt-Trigger Inputs

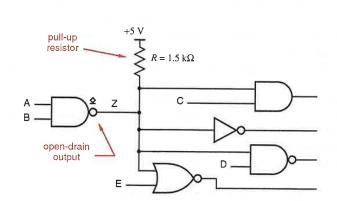

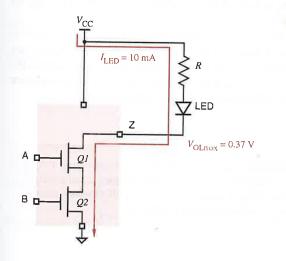

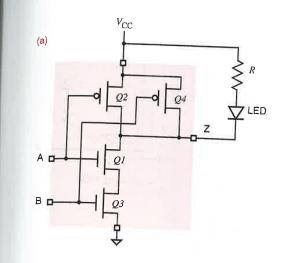

- 3.7.3 Three-State Outputs 3.7.4 Open-Drain Outputs

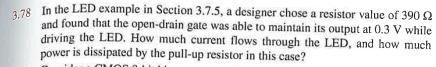

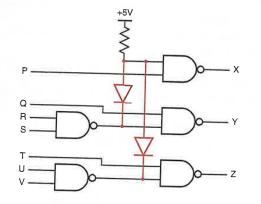

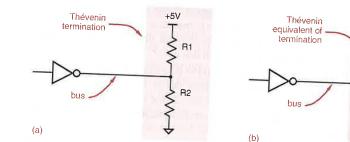

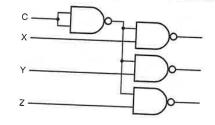

- 3.7.5 Driving LEDs 3.7.6 Multisource Buses 3.7.7 Wired Logic

- 3.7.8 Pull-Up Resistors

Contents ix

3.8 CMOS Logic Families 141 3.8.1 HC and HCT 3.8.2 AHC and AHCT 3.8.3 HC, HCT, AHC, and AHCT Electrical Characteristics 3.8.4 AC and ACT 3.8.5 FCT and FCT-T 3.8.6 FCT-T Electrical Characteristics 3.9 Low-Voltage CMOS Logic and Interfacing 151 3.9.1 3.3-V LVTTL and LVCMOS Logic 3.9.2 5-V Tolerant Inputs 3.9.4 TTL/LVTTL Interfacing Summary 3.9.3 5-V Tolerant Outputs 3.9.5 Logic Levels Less Than 3.3 V 3.10 Bipolar Logic 155 3.10.1 Diode Logic 3.10.2 Bipolar Junction Transistors 3.10.3 Transistor-Transistor Logic 3.10.4 TTL Logic Levels and Noise Margins 3.10.5 TTL Fanout 3.10.6 TTL Families 3.10.7 A TTL Data Sheet 3.10.9 Emitter-Coupled Logic 3.10.8 CMOS/TTL Interfacing References 174 Drill Problems 175 Exercises 179 4 COMBINATIONAL LOGIC DESIGN PRINCIPLES 183 4.1 Switching Algebra 184 4.1.1 Axioms 4.1.2 Single-Variable Theorems 4.1.3 Two- and Three-Variable Theorems 4.1.4 n-Variable Theorems 4.1.5 Duality 4.1.6 Standard Representations of Logic Functions 4.2 Combinational-Circuit Analysis 199 4.3 Combinational-Circuit Synthesis 205 4.3.1 Circuit Descriptions and Designs 4.3.2 Circuit Manipulations 4.3.3 Combinational-Circuit Minimization 4.3.4 Karnaugh Maps 4.3.5 Minimizing Sums of Products 4.3.6 Other Minimization Topics 4.3.7 Programmed Minimization Methods 4.4 Timing Hazards 224 4.4.1 Static Hazards 4.4.2 Finding Static Hazards Using Maps 4.4.3 Dynamic Hazards 4.4.4 Designing Hazard-Free Circuits 229 References Drill Problems 230 Exercises 232 5 HARDWARE DESCRIPTION LANGUAGES 237 5.1 HDL-Based Digital Design 238 5.1.1 Why HDLs? 5.1.2 HDL Tool Suites 5.1.3 HDL-Based Design Flow 5.2 The ABEL Hardware Description Language 243 5.2.2 ABEL Compiler Operation 5.2.1 ABEL Program Structure 5.2.4 Truth Tables 5.2.3 WHEN Statements and Equation Blocks

5.2.5 Ranges, Sets, and Relations

5.2.7 Additional ABEL Features

d Logic

6

5.2.6 Test Vectors

Contents

Х

- 5.3 The VHDL Hardware Description Language 256

- 5.3.1 Program Structure 5.3.2 Types, Constants, and Arrays

- 5.3.3 Functions and Procedures 5.3.4 Libraries and Packages

- 5.3.5 Structural Design Elements 5.3.6 Dataflow Design Elements

- 5.3.7 Behavioral Design Elements 5.3.8 The Time Dimension

- 5.3.9 Simulation 5.3.10 Test Benches

- 5.3.11 VHDL Features for Sequential Logic Design 5.3.12 Synthesis

- 5.4 The Verilog Hardware Description Language 290

- 5.4.1 Program Structure

- 5.4.2 Logic System, Nets, Variables, and Constants

- 5.4.3 Vectors and Operators 5.4.4 Arrays

- 5.4.5 Logical Operators and Expressions 5.4.6 Compiler Directives

- 5.4.7 Structural Design Elements 5.4.8 Dataflow Design Elements

- 5.4.9 Behavioral Design Elements (Procedural Code)

- 5.4.10 Functions and Tasks 5.4.11 The Time Dimension

- 5.4.12 Simulation 5.4.13 Test Benches

- 5.4.14 Verilog Features for Sequential Logic Design 5.4.15 Synthesis References 335

- Drill Problems 337

Exercises 338

## 6 COMBINATIONAL LOGIC DESIGN PRACTICES 341

- 6.1 Documentation Standards 342

- 6.1.1 Block Diagrams 6.1.2 Gate Symbols

- 6.1.3 Signal Names and Active Levels 6.1.4 Active Levels for Pins

- 6.1.5 Bubble-to-Bubble Logic Design

- 6.1.6 Signal Naming in HDL Programs 6.1.7 Drawing Layout

- 6.1.8 Buses 6.1.9 Additional Schematic Information

- 6.2 Circuit Timing 362

- 6.2.1 Timing Diagrams 6.2.2 Propagation Delay

- 6.2.3 Timing Specifications 6.2.4 Timing Analysis

- 6.2.5 Timing Analysis Tools

- 6.3 Combinational PLDs 370

- 6.3.1 Programmable Logic Arrays

- 6.3.2 Programmable Array Logic Devices

- 6.3.3 Generic Array Logic Devices

- 6.3.4 Complex Programmable Logic Devices (CPLDs)

- 6.3.5 CMOS PLD Circuits 6.3.6 Device Programming and Testing

- 6.4 Decoders 384

- 6.4.1 Binary Decoders

- 6.4.2 Logic Symbols for Larger-Scale Elements

- 6.4.3 The 74x138 3-to-8 Decoder 6.4.4 Cascading Binary Decoders

- 6.4.5 Decoders in ABEL and PLDs 6.4.6 Decoders in VHDL

- 6.4.7 Decoders in Verilog 6.4.8 Seven-Segment Decoders

- 6.5 Encoders 408

7

- 6.5.1 Priority Encoders 6.5.2 The 74x148 Priority Encoder

- 6.5.3 Encoders in ABEL and PLDs 6.5.4 Encoders in VHDL

- 6.5.5 Encoders in Verilog

Contents xi

|         | 6.6 Three-State Devices 418                                                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

|         | 6.6.1 Three-State Buffers 6.6.2 Standard MSI Three-State Buffers                                                                       |

|         | 6.6.3 Three-State Outputs in ABEL and PLDs                                                                                             |

| ents    | 6.6.4 Three-State Outputs in VHDL                                                                                                      |

|         | 6.6.5 Three-State Outputs in Verilog                                                                                                   |

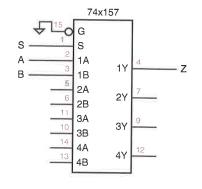

|         | 6.7 Multiplexers 432                                                                                                                   |

| thesis  | 6.7.1 Standard MSI Multiplexers 6.7.2 Expanding Multiplexers                                                                           |

|         | 6.7.3 Multiplexers, Demultiplexers, and Buses                                                                                          |

|         | 6.7.4 Multiplexers in ABEL and PLDs 6.7.5 Multiplexers in VHDL                                                                         |

|         | 6.7.6 Multiplexers in Verilog                                                                                                          |

| de la   | 6.8 Exclusive-OR Gates and Parity Circuits 447                                                                                         |

| ctives  | 6.8.1 Exclusive-OR and Exclusive-NOR Gates 6.8.2 Parity Circuits                                                                       |

| ents    | 6.8.3 The 74x280 9-Bit Parity Generator                                                                                                |

|         | 6.8.4 Parity-Checking Applications                                                                                                     |

|         | 6.8.5 Exclusive-OR Gates and Parity Circuits in ABEL and PLDs                                                                          |

| mthesis | 6.8.6 Exclusive-OR Gates and Parity Circuits in VHDL<br>6.8.7 Exclusive-OR Gates and Parity Circuits in Verilog                        |

|         | 6.9 Comparators 458                                                                                                                    |

|         | 6.9.1 Comparator Structure 6.9.2 Iterative Circuits                                                                                    |

|         | 6.9.3 An Iterative Comparator Circuit                                                                                                  |

|         | 6.9.4 Standard MSI Magnitude Comparators                                                                                               |

|         | 6.9.5 Comparators in HDLs 6.9.6 Comparators in ABEL and PLDs                                                                           |

|         | 6.9.7 Comparators in VHDL 6.9.8 Comparators in Verilog                                                                                 |

|         | 6.10 Adders, Subtractors, and ALUs 474                                                                                                 |

| Pins    | 6.10.1 Half Adders and Full Adders 6.10.2 Ripple Adders                                                                                |

|         | 6.10.3 Subtractors 6.10.4 Carry-Lookahead Adders                                                                                       |

| t       | 6.10.5 MSI Adders 6.10.6 MSI Arithmetic and Logic Units                                                                                |

|         | 6.10.7 Group-Carry Lookahead 6.10.8 Adders in ABEL and PLDs                                                                            |

|         | 6.10.9 Adders in VHDL 6.10.10 Adders in Verilog                                                                                        |

|         | 6.11 Combinational Multipliers 494                                                                                                     |

|         | 6.11.1 Combinational Multiplier Structures                                                                                             |

|         | 6.11.2 Multiplication in ABEL and PLDs 6.11.3 Multiplication in VHDL                                                                   |

|         | 6.11.4 Multiplication in Verilog                                                                                                       |

|         | References 508                                                                                                                         |

|         | Drill Problems 509                                                                                                                     |

|         | Exercises 511                                                                                                                          |

| esting  | 7 SEQUENTIAL LOGIC DESIGN PRINCIPLES 521                                                                                               |

|         |                                                                                                                                        |

|         | 7.1 Bistable Elements 523                                                                                                              |

|         | 7.1.1 Digital Analysis 7.1.2 Analog Analysis                                                                                           |

| ecoders | 7.1.3 Metastable Behavior                                                                                                              |

|         | 7.2 Latches and Flip-Flops 526                                                                                                         |

| 10      | 7.2.1 S-R Latch 7.2.2 S-R Latch 7.2.3 S-R Latch with Enable                                                                            |

|         | 7.2.4 D Latch 7.2.5 Edge-Triggered D Flip-Flop<br>7.2.6 Edge Triggered D Flip Elon with English 7.2.7 Scan Flip Flop                   |

|         | 7.2.6 Edge-Triggered D Flip-Flop with Enable 7.2.7 Scan Flip-Flop<br>7.2.8 Master/Slave S-R Flip-Flop 7.2.9 Master/Slave J-K Flip-Flop |

| ×       | 7.2.8 Master/Slave S-R Flip-Flop 7.2.9 Master/Slave J-K Flip-Flop<br>7.2.10 Edge-Triggered J-K Flip-Flop 7.2.11 T Flip-Flop            |

|         | 7.2.10 Eugermagerea on rapriop 7.2.11 rrapriop                                                                                         |

|         |                                                                                                                                        |

|         |                                                                                                                                        |

Contents xii

- 7.3 Clocked Synchronous State-Machine Analysis 542 7.3.2 Output Logic 7.3.1 State-Machine Structure

- 7.3.3 Characteristic Equations

- 7.3.4 Analysis of State Machines with D Flip-Flops

- 7.4 Clocked Synchronous State-Machine Design 553 7.4.2 State Minimization 7.4.1 State-Table Design Example 7.4.4 Synthesis Using D Flip-Flops 7.4.3 State Assignment

- 7.4.5 Synthesis Using J-K Flip-Flops

- 7.4.6 More Design Examples Using D Flip-Flops

- 7.5 Designing State Machines Using State Diagrams 570

- 7.6 State-Machine Synthesis Using Transition Lists 577 7.6.2 Excitation Equations 7.6.1 Transition Equations 7.6.4 Realizing the State Machine 7.6.3 Variations on the Scheme 580

- 7.7 Another State-Machine Design Example 7.7.2 Unused States 7.7.1 The Guessing Game

- 7.7.3 Output-Coded State Assignment

- 7.7.4 "Don't-Care" State Codings

- 7.8 Decomposing State Machines 587

- 7.9 Feedback Sequential-Circuit Analysis 590

- 7.9.1 Basic Analysis

- 7.9.2 Analyzing Circuits with Multiple Feedback Loops

- 7.9.4 State Tables and Flow Tables 7.9.3 Races

- 7.9.5 CMOS D Flip-Flop Analysis

- 7.10 Feedback Sequential-Circuit Design 601

- 7.10.2 Designing Fundamental-Mode Flow Table 7.10.1 Latches

- 7.10.4 Race-Free State Assignment 7.10.3 Flow-Table Minimization

- 7.10.6 Essential Hazards 7.10.5 Excitation Equations

- 7.10.7 Summary

- 7.11 ABEL Sequential-Circuit Design Features 612

- 7.11.2 State Diagrams 7.11.1 Registered Outputs

- 7.11.4 Specifying Moore Outputs 7.11.3 External State Memory

- 7.11.5 Specifying Mealy and Pipelined Outputs with WITH

- 7.11.6 Test Vectors

- 7.12 Sequential-Circuit Design with VHDL 625

- 7.12.2 State-Machine Design with VHDL 7.12.1 Clocked Circuits

- 7.12.3 A VHDL State-Machine Example

- 7.12.5 Pipelined Outputs in VHDL 7.12.4 State Assignment in VHDL

- 7.12.6 Direct VHDL Coding Without a State Table

- 7.12.7 More VHDL State-Machine Examples

- 7.12.8 Specifying Flip-Flops in VHDL

- 7.12.9 VHDL State-Machine Test Benches

- 7.12.10 Feedback Sequential Circuits

- 7.13 Sequential-Circuit Design with Verilog 646

- 7.13.2 State-Machine Design with Verilog 7.13.1 Clocked Circuits

- 7.13.3 A Verilog State-Machine Example

- 7.13.4 Pipelined Outputs in Verilog

- 7.13.5 Direct Verilog Coding Without a State Table

- 7.13.6 More Verilog State-Machine Examples

Contents xiii

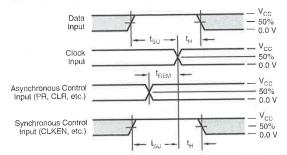

7.13.7 Specifying Flip-Flops in Verilog 7.13.8 Verilog State-Machine Test Benches 7.13.9 Feedback Sequential Circuits References 663 Drill Problems 664 Exercises 669 SEQUENTIAL LOGIC DESIGN PRACTICES 679 8 680 Sequential-Circuit Documentation Standards 8.1 8.1.1 General Requirements 8.1.2 Logic Symbols 8.1.3 State-Machine Descriptions 8.1.4 Timing Diagrams and Specifications 8.2 Latches and Flip-Flops 686 8.2.1 SSI Latches and Flip-Flops 8.2.2 Switch Debouncing 8.2.3 The Simplest Switch Debouncer 8.2.4 Bus Holder Circuit 8.2.5 Multibit Registers and Latches 8.2.6 Registers and Latches in ABEL and PLDs 8.2.7 Registers and Latches in VHDL 8.2.8 Registers and Latches in Verilog Sequential PLDs 703 8.3 8.3.1 Sequential GAL Devices 8.3.2 PLD Timing Specifications 8.4 Counters 710 8.4.1 Ripple Counters 8.4.2 Synchronous Counters 8.4.3 MSI Counters and Applications 8.4.4 Decoding Binary-Counter States 8.4.6 Counters in VHDL 8.4.5 Counters in ABEL and PLDs nment 8.4.7 Counters in Verilog 8.5 Shift Registers 727 8.5.1 Shift-Register Structure 8.5.2 MSI Shift Registers 8.5.3 Shift-Register Counters 8.5.4 Ring Counters 8.5.5 Johnson Counters 8.5.6 Linear Feedback Shift-Register Counters 8.5.7 Shift Registers in ABEL and PLDs 8.5.8 Shift Registers in VHDL 8.5.9 Shift Registers in Verilog 752 Iterative versus Sequential Circuits 8.6 756 Synchronous Design Methodology 8.7 758 IDL 8.7.1 Synchronous System Structure 8.8 Impediments to Synchronous Design 762 1 VHDL 8.8.2 Gating the Clock 8.8.1 Clock Skew 8.8.3 Asynchronous Inputs 8.9 Synchronizer Failure and Metastability 769 8.9.2 Metastability Resolution Time 8.9.1 Synchronizer Failure 8.9.3 Reliable Synchronizer Design 8.9.5 Better Synchronizers 8.9.4 Analysis of Metastable Timing 8.9.6 Other Synchronizer Designs erilog 8.9.7 Synchronizing High-Speed Data Transfers References 788 Drill Problems 790 Exercises 792

ne

ble

ts

xiv Contents

## 9 MEMORY, CPLDS, AND FPGAS 799

- 9.1 Read-Only Memory 800

- 9.1.1 Using ROMs for "Random" Combinational Logic Functions 9.1.2 Internal ROM Structure 9.1.3 Two-Dimensional Decoding

- 9.1.4 Commercial ROM Types

- 9.1.5 ROM Control Inputs and Timing 9.1.6 ROM Applications

- 9.2 Read/Write Memory 821

- 9.3 Static RAM 822

- 9.3.1 Static-RAM Inputs and Outputs

- 9.3.2 Static-RAM Internal Structure

- 9.3.3 Static-RAM Timing 9.3.4 Standard Static RAMs

- 9.3.5 Synchronous SRAM

- 9.4 Dynamic RAM 833

- 9.4.1 Dynamic-RAM Structure 9.4.2 SDRAM Timing 9.4.3 DDR SDRAMs

- 9.5 Complex Programmable Logic Devices 840

- 9.5.1 Xilinx XC9500 CPLD Family

- 9.5.2 Function-Block Architecture

- 9.5.3 Input/Output-Block Architecture 9.5.4 Switch Matrix

- 9.6 Field-Programmable Gate Arrays 850

- 9.6.1 Xilinx XC4000 FPGA Family 9.6.2 Configurable Logic Block 9.6.3 Input/Output Block 9.6.4 Programmable Interconnect

- References 859

- Drill Problems 859

- Exercises 860

INDEX 863

11

chapter

# Introduction

elcome to the world of digital design. Perhaps you're a computer science student who knows all about computer software and programming, but you're still trying to figure out how all that fancy hardware could possibly work. Or perhaps you're an electrical engineering student who already knows

something about analog electronics and circuit design, but you wouldn't know a bit if it bit you. No matter. Starting from a fairly basic level, this book will show you how to design digital circuits and subsystems.

We'll give you the basic principles that you need to figure things out, and we'll give you lots of examples. Along with principles, we'll try to convey the flavor of real-world digital design by discussing current, practical considerations whenever possible. And I, the author, will often refer to myself as "we" in the hope that you'll be drawn in and feel that we're walking through the learning process together.

## 1.1 About Digital Design

Some people call it "logic design." That's OK, but ultimately the goal of design is to build systems. To that end, we'll cover a whole lot more in this text than logic equations and theorems.

This book claims to be about principles and practices. Most of the principles that we present will continue to be important years from now;

2

some may be applied in ways that have not even been discovered yet. As for practices, they may be a little different from what's presented here by the time you start working in the field, and they will certainly continue to change throughout your career. So you should treat the "practices" material in this book as a way to reinforce principles, and as a way to learn design methods by example.

One of the book's goals is to present enough about basic principles for you to know what's happening when you use software tools to "turn the crank" for you. The same basic principles can help you get to the root of problems when the tools happen to get in your way.

Listed in the box on this page are several key points that you should learn through your studies with this text. Most of these items probably make no sense to you right now, but you should come back and review them later.

Digital design is engineering, and engineering means "problem solving." My experience is that only 5%-10% of digital design is "the fun stuff"—the creative part of design, the flash of insight, the invention of a new approach. Much of the rest is just "turning the crank." To be sure, turning the crank is much easier now than it was 25 or even 10 years ago, but you still can't spend 100% or even 50% of your time on the fun stuff.

| IMPORTANT<br>THEMES IN | • Good tools do not guarantee good design, but they help a lot by taking the pain out of doing things right.                                                     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL DESIGN         | Digital circuits have analog characteristics.                                                                                                                    |

|                        | <ul> <li>Know when to worry and when not to worry about the analog aspects of digital<br/>design.</li> </ul>                                                     |

|                        | <ul> <li>Always document your designs to make them understandable to yourself and to<br/>others.</li> </ul>                                                      |

|                        | <ul> <li>Use consistent coding, organizational, and documentation styles in your HDL-<br/>based designs, following your company's guidelines.</li> </ul>         |

|                        | • Understand and use standard functional building blocks.                                                                                                        |

|                        | • State-machine design is like programming; approach it that way.                                                                                                |

|                        | <ul> <li>Design for minimum cost at the system level, including your own engineering<br/>effort as part of the cost.</li> </ul>                                  |

|                        | <ul> <li>Design for testability and manufacturability.</li> </ul>                                                                                                |

|                        | • Use programmable logic to simplify designs, reduce cost, and accommodate last-<br>minute modifications.                                                        |

|                        | <ul> <li>Avoid asynchronous design. Practice synchronous design until a better method-<br/>ology comes along (if ever).</li> </ul>                               |

|                        | <ul> <li>Pinpoint the unavoidable asynchronous interfaces between different subsystems<br/>and the outside world, and provide reliable synchronizers.</li> </ul> |

З

et. As for y the time to change this book tethods by

les for you crank" for s when the

nould learn ce no sense

n solving." stuff"—the / approach. nk is much nd 100% or

of digital

g the pain

elf and to

our HDL-

ngineering

odate last-

er method-

subsystems

Besides the fun stuff and turning the crank, there are many other areas in which a successful digital designer must be competent, including the following:

- *Debugging*. It's next to impossible to be a good designer without being a good troubleshooter. Successful debugging takes planning, a systematic approach, patience, and logic: if you can't discover where a problem *is*, find out where it *is not*!

- Business requirements and practices. A digital designer's work is affected by a lot of nonengineering factors, including documentation standards, component availability, feature definitions, target specifications, task scheduling, office politics, and going to lunch with vendors.

- *Risk-taking.* When you begin a design project you must carefully balance risks against potential rewards and consequences, in areas ranging from component selection (will it be available when I'm ready to build the first prototype?) to schedule commitments (will I still have a job if I'm late?).

- *Communication*. Eventually, you'll hand off your successful designs to other engineers, other departments, and customers. Without good communication skills, you'll never complete this step successfully. Keep in mind that communication includes not just transmitting but also receiving; learn to be a good listener!

In the rest of this chapter, and throughout the text, I'll continue to state some opinions about what's important and what is not. I think I'm entitled to do so as a moderately successful practitioner of digital design.

Additional materials related to this book, such as supplemental chapter sections, selected exercise solutions, and downloadable source code for all programs, can be found at <u>DDPPonline</u> (via www.ddpp.com; see the Preface).

## 1.2 Analog versus Digital

Analog devices and systems process time-varying signals that can take on any value across a continuous range of voltage, current, or other metric. So do *digital* circuits and systems; the difference is that we can pretend that they don't! A digital signal is modeled as taking on, at any time, only one of two discrete values, which we call 0 and 1 (or LOW and HIGH, FALSE and TRUE, negated and asserted, Frank and Teri, or whatever).

Digital computers have been around since the 1940s and have been in widespread commercial use since the 1960s. Yet only in the past 10 to 20 years has the "digital revolution" spread to many other aspects of life. Examples of once-analog systems that have now "gone digital" include the following:

• *Still pictures*. Ten years ago, the majority of cameras still used silver-halide film to record images. Today, inexpensive digital cameras record a picture as a 1024×768 or larger array of pixels, where each pixel stores the inten-

analog digital

Ō

4 Chapter 1 Introduction

sities of its red, green, and blue color components as 8 or more bits each. This data, over 18 million bits in this example, is processed and compressed in JPEG format down to as few as 5% of the original number of bits. So, digital cameras rely on both digital storage and digital processing.

- Video recordings. A digital versatile disc (DVD) stores video in a highly compressed digital format called MPEG-2. This standard encodes a small fraction of the individual video frames in a compressed format similar to JPEG, and encodes each other frame as the difference between it and the previous one. The capacity of a single-layer, single-sided DVD is about 35 billion bits, sufficient for about 2 hours of high-quality video, and a twolayer, double-sided disc has four times that capacity.

- Audio recordings. Once made exclusively by impressing analog waveforms onto vinyl or magnetic tape, audio recordings now commonly use digital compact discs (CDs). A CD stores music as a sequence of 16-bit numbers corresponding to samples of the original analog waveform, one sample per stereo channel every 22.7 microseconds. A full-length CD recording (73 minutes) contains over 6 billion bits of information.

- Automobile carburetors. Once controlled strictly by mechanical linkages (including clever "analog" mechanical devices that sensed temperature, pressure, etc.), automobile engines are now controlled by embedded microprocessors. Various electronic and electromechanical sensors convert engine conditions into numbers that the microprocessor can examine to determine how to control the flow of fuel and oxygen to the engine. The microprocessor's output is a time-varying sequence of numbers that operate electromechanical actuators which, in turn, control the engine.

- The telephone system. It started out over a hundred years ago with analog microphones and receivers connected to the ends of a pair of copper wires (or was it string?). Even today, most homes still use analog telephones, which transmit analog signals to the phone company's central office (CO). However, in the majority of COs, these analog signals are converted into a digital format before they are routed to their destinations, be they in the same CO or across the world. For many years the private branch exchanges (PBXs) used by businesses have carried the digital format all the way to the desktop. Now many businesses, COs, and traditional telephony service providers are converting to integrated systems that combine digital voice with data traffic over a single IP (Internet Protocol) network.

- *Traffic lights.* Stop lights used to be controlled by electromechanical timers that would give the green light to each direction for a predetermined amount of time. Later, relays were used in controllers that could activate the lights according to the pattern of traffic detected by sensors embedded in the pavement. Today's controllers use microprocessors and can control

11

bits each. mpressed f bits. So, 3.

a highly es a small similar to it and the s about 35 and a two-

log wavemonly use e of 16-bit eform, one length CD on.

al linkages mperature, embedded insors conan examine ingine. The mbers that engine.

with analog opper wires telephones, office (CO). verted into a they in the h exchanges ie way to the iony service digital voice

anical timers edetermined ould activate rs embedded d can control the lights in ways that maximize vehicle throughput or, in Sunnyvale, California, frustrate drivers with all kinds of perverse behavior.

• *Movie effects*. Special effects used to be created exclusively with miniature clay models, stop action, trick photography, and numerous overlays of film on a frame-by-frame basis. Today, spaceships, bugs, otherworldly scenes, and even babies from hell (in Pixar's animated short *Tin Toy*) are synthesized entirely using digital computers. Might the stunt man or woman someday no longer be needed, either?

The electronics revolution has been going on for quite some time now, and the "solid-state" revolution began with analog devices and applications like transistors and transistor radios. So why has there now been a *digital* revolution? There are in fact many reasons to favor digital circuits over analog ones:

- *Reproducibility of results*. Given the same set of inputs (in both value and time sequence), a properly designed digital circuit always produces exactly the same results. The outputs of an analog circuit vary with temperature, power-supply voltage, component aging, and other factors.

- *Ease of design*. Digital design, often called "logic design," is logical. No special math skills are needed, and the behavior of small logic circuits can be visualized mentally without any special insights about the operation of capacitors, transistors, or other devices that require calculus to model.

- *Flexibility and functionality.* Once a problem has been reduced to digital form, it can be solved using a set of logical steps in space and time. For example, you can design a digital circuit that scrambles your recorded voice so that it is absolutely indecipherable by anyone who does not have your "key" (password), but it can be heard virtually undistorted by anyone who does. Try doing that with an analog circuit.

- Programmability. You're probably already quite familiar with digital computers and the ease with which you can design, write, and debug programs for them. Well, guess what? Much of digital design is carried out today by writing programs, too, in *hardware description languages (HDLs)*. These languages allow both structure and function of a digital circuit to be specified or *modeled*. Besides a compiler, a typical HDL also comes with simulation and synthesis programs. These software tools are used to test the hardware model's behavior before any real hardware is built, and then to synthesize the model into a circuit in a particular component technology.

- *Speed.* Today's digital devices are very fast. Individual transistors in the fastest integrated circuits can switch in less than 10 picoseconds, and a complete, complex device built from these transistors can examine its inputs and produce an output in less than a nanosecond. This means that such a device can produce a billion or more results per second.

hardware description language (HDL) hardware model

| and the second sec |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHORT TIMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A millisecond (ms) is $10^{-3}$ second, and a microsecond ( $\mu$ s) is $10^{-6}$ second. A nanosecond (ns) is just $10^{-9}$ second, and a picosecond (ps) is $10^{-12}$ second. In a vacuum, light travels about a foot in a nanosecond, and an inch in 85 picoseconds. With individual transistors in the fastest integrated circuits now switching in less than 10 picoseconds, the speed-of-light delay between these transistors across a half-inch-square silicon chip has become a limiting factor in circuit design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li><i>Economy.</i> Digital circuits can provide a lot of functionality in a small space. Circuits that are used repetitively can be "integrated" into a single "chip" and mass-produced at very low cost, making possible throw-away items like calculators, digital watches, and singing birthday cards. (You may ask, "Is this such a good thing?" Never mind!)</li> <li><i>Steadily advancing technology.</i> When you design a digital system, you almost always know that there will be a faster, cheaper, or otherwise better technology for it in a few years. Clever designers can accommodate these expected advances during the initial design of a system, to forestall system obsolescence and to add value for customers. For example, desktop computers often have "expansion sockets" to accommodate faster processors or larger memories than are available at the time of the computer's introduction.</li> <li>So, that's enough of a sales pitch on digital design. The rest of this chapter will give you a bit more technical background to prepare you for the rest of the book.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.3 Digital Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

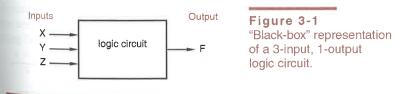

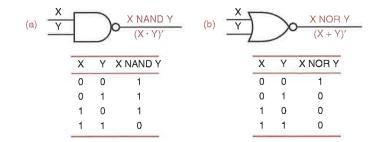

| gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The most basic digital devices are called <i>gates</i> , and no, they were not named after the founder of a large software company. Gates originally got their name from their function of allowing or retarding ("gating") the flow of digital information. In general, a gate has one or more inputs and produces an output that is a function of the current input value(s). While the inputs and outputs may be analog conditions such as voltage, current, even hydraulic pressure, they are modeled as taking on just two discrete values, 0 and 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

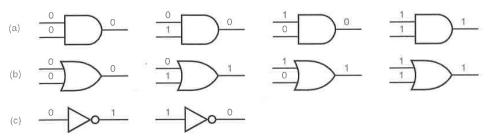

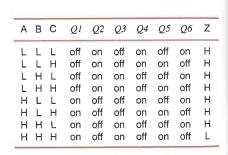

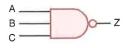

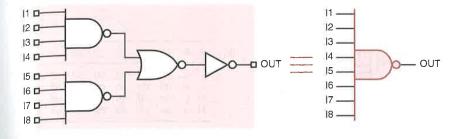

| AND gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-input AND gate, shown in (a), produces a 1 output in both of its input of the state of the sta |

| combinational circuit<br>input combination<br>OR gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | the four possible combinations of inputs that may be upp<br>ing outputs. A gate is called a <i>combinational circuit</i> because its output depends<br>only on the current combination of input values (called an <i>input combination</i> ).<br>A 2-input <i>OR gate</i> , shown in (b), produces a 1 output if one or both of its<br>inputs are 1; it produces a 0 output only if both inputs are 0. Once again, there are<br>four possible input combinations, resulting in the outputs shown in the figure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 1.4 Electronic Aspects of Digital Design

7

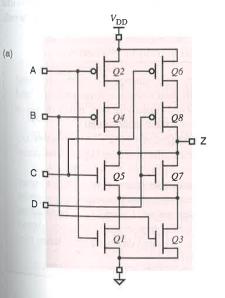

Figure 1-1 Digital devices: (a) AND gate; (b) OR gate; (c) NOT gate or inverter.

A *NOT gate*, more commonly called an *inverter*, produces an output value that is the opposite of the input value, as shown in (c).

We called these three gates the most important for good reason. Any digital function can be realized using just these three kinds of gates. In Chapter 3 we'll show how gates are realized using transistor circuits. You should know, however, that gates have been built or proposed using other technologies, such as relays, vacuum tubes, hydraulic devices, and molecular structures.

A *flip-flop* is a device that stores either a 0 or 1. The *state* of a flip-flop is the value that it currently stores. The stored value can be changed only at certain times determined by a "clock" input, and the new value may further depend on the flip-flop's current state and its "control" inputs. A flip-flop can be built from a collection of gates hooked up in a clever way, as we'll show in Section 7.2.

A digital circuit that contains flip-flops is called a *sequential circuit*, because its output at any time depends not only on its current input but also on the past sequence of inputs that have been applied to it. In other words, a sequential circuit has *memory* of past events.

## 1.4 Electronic Aspects of Digital Design

Digital circuits are not exactly a binary version of alphabet soup—with all due respect to Figure 1-1, they don't have little 0s and 1s floating around in them. As we'll see in Chapter 3, digital circuits deal with analog voltages and currents and are built with analog components. The "digital abstraction" allows analog behavior to be ignored in most cases, so circuits can be modeled as if they really did process 0s and 1s.

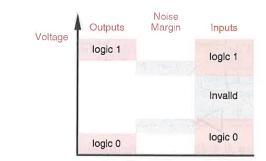

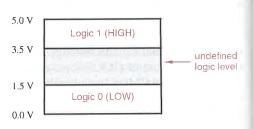

One important aspect of the digital abstraction is to associate a *range* of analog values with each logic value (0 or 1). As shown in Figure 1-2 on the next page, a typical gate is not guaranteed to have a precise voltage level for a logic 0 output. Rather, it may produce a voltage somewhere in a range that is a *subset* of the range guaranteed to be recognized as a 0 by other gate inputs. The difference between the range boundaries is called *noise margin*—in a real circuit, a gate's output can be corrupted by this much noise and still be correctly interpreted at the inputs of other gates.

NOT gate inverter

flip-flop state

sequential circuit

memory

noise margin

ond. In a seconds. g in less across a

in a small nto a single throw-away cards. (You

cond. A

system, you rwise better nodate these estall system esktop comr processors computer's

t of the book.

re not named ot their name ow of digital ices an output d outputs may ssure, they are

Ids of gates. A is inputs are 1; our times, with and the resultoutput depends combination). If or both of its again, there are in the figure. Figure 1-2 Logic values and

noise margins.

Behavior for logic 1 outputs is similar. Note in the figure that there is an "invalid" region between the input ranges for logic 0 and logic 1. Although any given digital device operating at a particular voltage and temperature will have a fairly well defined boundary (or threshold) between the two ranges, different devices may have different boundaries. Still, all properly operating devices have their boundary *somewhere* in the "invalid" range. Therefore, any signal that is within the defined ranges for 0 and 1 will be interpreted identically by different devices. This characteristic is essential for reproducibility of results.

It is the job of an *electronic* circuit designer to ensure that logic gates produce and recognize logic signals that are within the appropriate ranges. This is an analog circuit-design problem; we touch upon some of its aspects in Chapter 3. It's not possible to design a circuit that has the desired behavior under every possible condition of power-supply voltage, temperature, loading, and other factors. Instead, the electronic circuit designer or device manufacturer provides *specifications* (also known as *specs*) that define the conditions under which correct behavior is guaranteed.

As a *digital* designer, then, you need not delve into the detailed analog behavior of a digital device to ensure its correct operation. Rather, you need only study enough about the device's operating environment to determine that it is operating within its published specifications. Granted, some analog knowledge is needed to perform this study, but not nearly what you'd need to design a digital device starting from scratch. In Chapter 3 we'll give you just what you need.

## 1.5 Software Aspects of Digital Design

Digital design need not involve any software tools. For example, Figure 1-3 shows the primary tool of the "old school" of digital design—a plastic template for drawing logic symbols in schematic diagrams by hand (the designer's name was engraved into the plastic with a soldering iron).

Today, however, software tools are an essential part of digital design. Indeed, the availability and practicality of hardware description languages (HDLs) and accompanying circuit simulation and synthesis tools have changed

specifications (specs)

#### 1.5 Software Aspects of Digital Design 9

It there is an Although any 'e will have a ges, different devices have signal that is / by different 3.

t logic gates ranges. This ts aspects in havior under loading, and manufacturer ditions under

tailed analog /ou need only nine that it is og knowledge esign a digital you need.

le, Figure 1-3 astic template signer's name

ligital design. on languages have changed

Figure 1-3 A logic-design template.

the entire landscape of digital design over the past several years. We'll make extensive use of HDLs throughout this book.

In *computer-aided design* (also called *computer-aided engineering*, *CAE*), various software tools improve the designer's productivity and help to improve the correctness and quality of designs. In a competitive world, the use of software tools is mandatory to obtain high-quality results on aggressive schedules. Important examples of software tools for digital design are listed below:

- Schematic entry. This is the digital designer's equivalent of a word processor. It allows schematic diagrams to be drawn "on-line," instead of with paper and pencil. The more advanced schematic-entry programs also check for common, easy-to-spot errors, such as shorted outputs, signals that don't go anywhere, and so on. Such programs are discussed in greater detail in Section CAD.2 at DDPPonline.

- *HDLs*. Hardware description languages, originally developed for circuit modeling, are now being used extensively for hardware *design*. They can be used to design anything from individual function modules to large, multichip digital systems. We'll introduce three commonly used HDLs, ABEL, VHDL, and Verilog, in Chapter 5, and we'll provide examples in later chapters. (Don't worry, you needn't learn all three languages!)

- *HDL text editors, compilers, and synthesizers.* A typical HDL software package has many components. The designer uses a text editor to write an HDL "program," and an HDL compiler checks it for syntax and related errors. The designer then can give the program to a synthesizer that creates a corresponding circuit realization that is targeted to a particular hardware technology. Most often, though, before synthesis, the designer runs the HDL program on a "simulator" to verify the behavior of the design.

- *Simulators*. The design cycle for a customized, single-chip digital integrated circuit is long and expensive. Once the first chip is built, it's very difficult, often impossible, to debug it by probing internal connections (they are really tiny), or to change the gates and interconnections. Usually, changes must be made in the original design database and a new chip must

computer-aided design (CAD) computer-aided engineering (CAE) 10 Chapter 1 Introduction

be manufactured to incorporate the required changes. Since this process can take months to complete, chip designers are highly motivated to "get it right" on the first try. Simulators help designers predict the electrical and functional behavior of a chip without actually building it, allowing most if not all bugs to be found before the chip is fabricated.

- Simulators are also used in the overall design of systems that incorporate many individual components. They are somewhat less critical in this case because it's easier for the designer to make changes in components and interconnections on a printed-circuit board. However, even a little bit of simulation can save time by catching mistakes early.

- *Test benches*. HDL-based digital designs are simulated and tested in software environments called "test benches." The idea is to build a set of programs around the HDL programs to automatically exercise them, checking both their functional and timing behavior. This is especially handy when small design changes are made—the test bench can be run to ensure that bug fixes or "improvements" in one area do not break something else. Test-bench programs may be written in the same HDL as the design itself, in C or C++, or in a combination of languages including scripting languages like Perl.

- *Timing analyzers and verifiers.* The time dimension is very important in digital design. All digital circuits take time to produce a new output value in response to an input change, and much of a designer's effort is spent ensuring that such output changes occur quickly enough (or, in some cases, not too quickly). Specialized programs can automate the tedious task of drawing timing diagrams and specifying and verifying the timing relationships between different signals in a complex system.

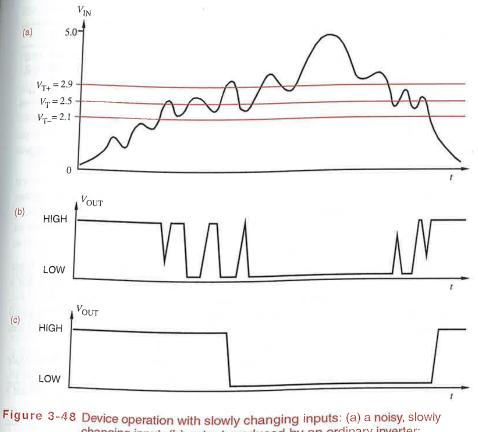

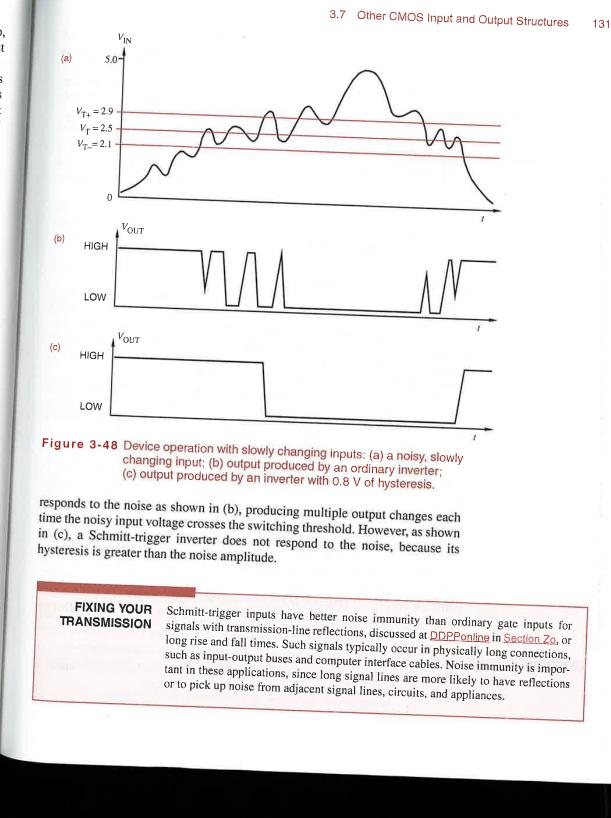

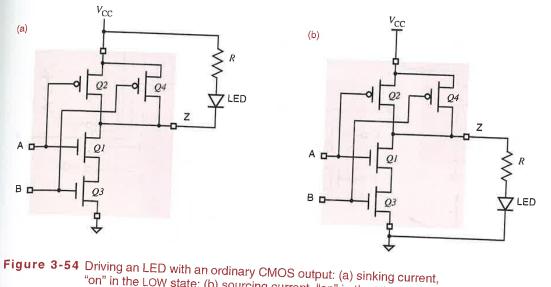

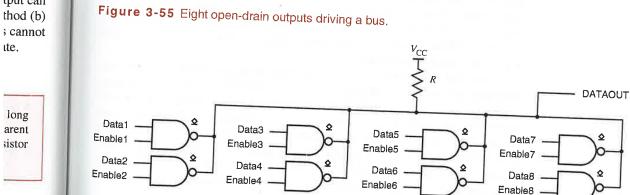

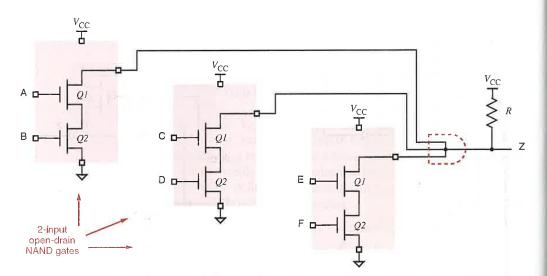

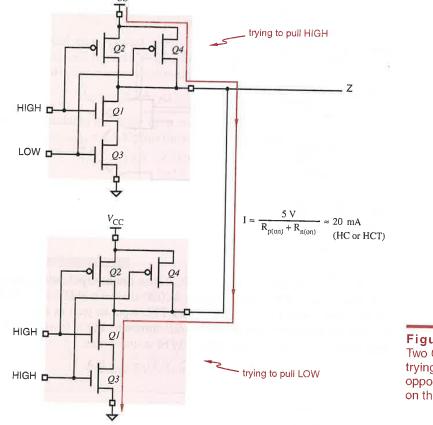

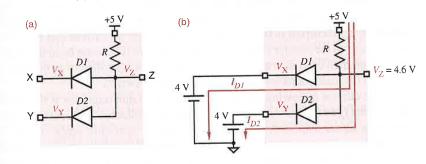

- *Word processors*. HDL-specific text editors are useful for writing source code, but word processors supporting fancy fonts and pretty graphics also have an important use in every design—to create documentation!