#

DELL INC. Petitioner

V.

ALACRITECH, INC. Patent Owner

\_\_\_\_\_

Case IPR. No. IPR2018-01307

U.S. Patent No. 8,850,948

Title: INTELLIGENT NETWORK INTERFACE SYSTEM AND METHOD FOR PROTOCOL PROCESSING

Declaration of Robert Horst, Ph.D. in Support of Petition for *Inter Partes* Review of U.S. Patent No. 8,850,948

### **TABLE OF CONTENTS**

|      |                                    |                                 |                                          | Page |  |  |  |

|------|------------------------------------|---------------------------------|------------------------------------------|------|--|--|--|

| I.   | I                                  | INTRODUCTION AND QUALIFICATIONS |                                          |      |  |  |  |

| II.  | N                                  | MATE:                           | ATERIALS RELIED ON IN FORMING MY OPINION |      |  |  |  |

| III. | UNDERSTANDING OF THE GOVERNING LAW |                                 |                                          |      |  |  |  |

|      | A.                                 | Inva                            | llidity by Anticipation                  | 4    |  |  |  |

|      | B.                                 | Inva                            | llidity by Obviousness                   | 5    |  |  |  |

| IV.  | I                                  | LEVEL                           | L OF ORDINARY SKILL IN THE ART7          |      |  |  |  |

| V.   |                                    |                                 | OF THE ART AND OVERVIEW OF TECHNOLOGY    |      |  |  |  |

|      | A. Layer                           |                                 | ered Network Protocols                   | 8    |  |  |  |

|      |                                    | 1.                              | OSI Layers                               | 8    |  |  |  |

|      |                                    | 2.                              | TCP/IP Layers                            | 9    |  |  |  |

|      | B.                                 | TCP                             | P/IP                                     | 11   |  |  |  |

|      |                                    | 1.                              | Encapsulation                            | 12   |  |  |  |

|      |                                    | 2.                              | Ethernet Header                          | 14   |  |  |  |

|      |                                    | 3.                              | IP Header                                | 16   |  |  |  |

|      |                                    | 4.                              | TCP header                               | 17   |  |  |  |

|      |                                    | 5.                              | Application Data                         | 21   |  |  |  |

|      |                                    | 6.                              | RFC 793 – TCP Specification              | 21   |  |  |  |

|      | B.                                 | Prot                            | ocol Offload and Fast-Path Processing    | 21   |  |  |  |

|      |                                    | 1.                              | RFC 647 – Front-Ending                   | 22   |  |  |  |

|      |                                    | 2.                              | RFC 929 – Outboard Processing            | 23   |  |  |  |

|      |                                    | 3.                              | Mediation Levels                         | 24   |  |  |  |

|      | C.                                 | Offl                            | oaded Protocols                          | 27   |  |  |  |

|      |                                    | 1.                              | OSI Protocol Offload                     | 27   |  |  |  |

|      |                                    | 2.                              | TCP/IP Protocol Offload                  | 27   |  |  |  |

|      |                                    | 3.                              | VMTP and XTP Protocol Offload            | 28   |  |  |  |

|      |                                    | 4.                              | Multi-Protocol Offload                   | 28   |  |  |  |

|       | D.                          | Portions of the Protocol Offloaded                                                                     |                                                                          | 29 |  |

|-------|-----------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----|--|

|       |                             | 1.                                                                                                     | Checksum Offload                                                         | 29 |  |

|       |                             | 2.                                                                                                     | Full Offload                                                             | 30 |  |

|       |                             | 3.                                                                                                     | Multi-Level Offload                                                      | 30 |  |

|       |                             | 4.                                                                                                     | Header Prediction                                                        | 30 |  |

|       | E.                          | Offload Implementation                                                                                 |                                                                          |    |  |

|       |                             | 1.                                                                                                     | Multiprocessor Offload                                                   | 34 |  |

|       |                             | 2.                                                                                                     | Offload Adapters based on Microprocessors                                | 35 |  |

|       |                             | 3.                                                                                                     | Offload Adapters based on Custom Processors or Custom Logic              | 37 |  |

|       | F. Protocol Offload Summary |                                                                                                        | 40                                                                       |    |  |

|       | G.                          | Add                                                                                                    | Additional Background Technology                                         |    |  |

|       |                             | 1.                                                                                                     | DMA                                                                      | 41 |  |

|       |                             | 2.                                                                                                     | Virtual and Physical Memory Addresses                                    | 43 |  |

| VI.   |                             | OVERV                                                                                                  | VIEW OF 948 PATENT                                                       | 45 |  |

| VII.  |                             | 948 PA                                                                                                 | TENT PROSECUTION HISTORY                                                 | 48 |  |

| VIII. |                             | CLAIM                                                                                                  | 1 CONSTRUCTIONS                                                          | 49 |  |

|       | A.                          | . Lega                                                                                                 | al Standard                                                              | 49 |  |

| IX.   | THE PRIOR ART               |                                                                                                        |                                                                          |    |  |

|       | A.                          | Thia: Thia, A Reduced Operation Protocol Engine (ROPE) for a mulitple-layer bypass architecture (1995) |                                                                          | 50 |  |

|       | В.                          |                                                                                                        | Tanenbaum96: A. Tanenbaum, Computer Networks, 3rd ed. (1996)             |    |  |

|       | C.                          | C. Stevens2: Stevens, TCP-IP Illustrated, Vol. 2                                                       |                                                                          | 68 |  |

| X.    |                             | Obviou                                                                                                 | sness Combinations – Motivations To Combine                              | 70 |  |

|       | A.                          | . Thia                                                                                                 | Thia in Combination with Tanenbaum96                                     |    |  |

|       | В.                          |                                                                                                        | a in Combination with Tanenbaum96 and further in abination with Stevens2 | 75 |  |

| XI.   |                             | GROUI                                                                                                  | NDS OF INVALIDITY                                                        | 77 |  |

I, Robert Horst, hereby declare as follows:

### I. INTRODUCTION AND QUALIFICATIONS

- 1. My name is Robert Horst. I have been retained on behalf of Petitioner Dell Inc. ("Dell") to provide this Declaration concerning technical subject matter relevant to the petition for *inter partes* review ("Petition") concerning U.S. Patent No. 8,850,948 (Ex.1001, the "948 Patent"). I previously offered a substantially identical declaration in connection with Case Nos. IPR2018-00234 (by Intel Corporation) and IPR2018-00403 (by Cavium, Inc.). I reserve the right to supplement this Declaration in response to additional evidence that may come to light.

- 2. I am over 18 years of age. I have personal knowledge of the facts stated in this Declaration and could testify competently to them if asked to do so.

- 3. My compensation is not based on the resolution of this matter. My findings are based on my education, experience, and background in the fields discussed below.

- 4. I am an independent consultant with more than 30 years of expertise in the design and architecture of computer systems. My current curriculum vitae is submitted as Exhibit 1004 and some highlights follow.

- 5. Currently, I am an independent consultant at HT Consulting where my work includes consulting on technology and intellectual property. I am also

currently an Adjunct Research Professor at the University of Illinois at Urbana-Champaign. I have testified as an expert witness and consultant in patent and intellectual property litigation as well as *inter partes* reviews and re-examination proceedings.

- 6. I earned my M.S. (1978) in electrical engineering and Ph.D. (1991) in computer science from the University of Illinois at Urbana-Champaign after earning my B.S. (1975) in electrical engineering from Bradley University. During my master's program, I designed, constructed and debugged a shared memory parallel microprocessor system. During my doctoral program, I designed and simulated a massively parallel, multi-threaded task flow computer.

- 7. After receiving my bachelor's degree and while pursuing my master's degree, I worked for Hewlett-Packard Co. While at Hewlett-Packard, I designed the micro-sequencer and cache of the HP3000 Series 64 processor. From 1980 to 1999, I worked at Tandem Computers, which was acquired by Compaq Computers in 1997. While at Tandem, I was a designer and architect of several generations of fault-tolerant computer systems and was the principal architect of the NonStop Cyclone superscalar processor. The system development work at Tandem also included development of the ServerNet System Area Network and applications of this network to fault tolerant systems and clusters of database servers.

- 8. Since leaving Compaq in 1999, I have worked with several technology companies, including 3Ware, Network Appliance, Tibion, and AlterG in the areas of network-attached storage and biomedical devices. From 2012 to 2015, I was Chief Technology Officer of Robotics at AlterG, Inc., where I worked on the design of anti-gravity treadmills and battery-powered orthotic devices to assist those with impaired mobility.

- 9. In 2001, I was elected an IEEE Fellow "for contributions to the architecture and design of fault tolerant systems and networks." I have authored over 30 publications, have worked with patent attorneys on numerous patent applications, and I am a named inventor on 82 issued U.S. patents.

- 10. My patents include those directed to networks (e.g., U.S. Pat. No. 6,157,967: Method of data communication flow control in a data processing system using busy/ready commands), storage (e.g., U.S. Pat. No. 6,549,977: Use of deferred write completion interrupts to increase the performance of disk operations), and multi-processor systems (e.g., U.S. Pat. No. 5,751,932: Fail-fast, fail-functional, fault-tolerant multiprocessor system). My publications include a conference paper that examined the performance and efficacy of protocol offload engines Ex.1004.

11. My Curriculum Vitae, which is filed as a separate Exhibit (Ex.1004), contains further details on my education, experience, publications, and other qualifications to render this opinion as expert.

### II. MATERIALS RELIED ON IN FORMING MY OPINION

12. In addition to reviewing U.S. Patent No. 8,850,948 (Ex.1001), I also reviewed and considered the prosecution history of the 948 Patent (Ex.1002). I also reviewed Thia, A ROPE for multiple-layer bypass architecture ("Thia") (Ex.1015), A. Tanenbaum, 3rd ed. (1996) (Ex.1006), and Stevens, TCP-IP Illustrated, Vol.2 ("Stevens2") (Ex.1013). I also considered the background materials cited herein.

#### III. UNDERSTANDING OF THE GOVERNING LAW

13. I understand that a patent claim is invalid if it is anticipated or rendered obvious in view of the prior art. I further understand that invalidity of a patent claim requires that the claim be anticipated or obvious from the perspective of a person of ordinary skill in the relevant art at the time the invention was made.

### A. Invalidity by Anticipation

- 14. I have been informed that a patent claim is invalid as anticipated under 35 U.S.C. § 102 if each and every element of a claim, as properly construed, is found either explicitly or inherently in a single prior art reference.

- 15. I have been informed that a claim is invalid under 35 U.S.C. § 102(a) if the claimed invention was patented or published anywhere, before the applicant's

invention. I further have been informed that a claim is invalid under 35 U.S.C. § 102(b) if the invention was patented or published anywhere more than one year prior to the first effective filing date of the patent application (critical date). I further have been informed that a claim is invalid under 35 U.S.C. § 102(e) if an invention described by that claim was disclosed in a U.S. patent granted on an application for a patent by another that was filed in the U.S. before the date of invention for such a claim.

### B. Invalidity by Obviousness

16. I have been informed that a patent claim is invalid as obvious under 35 U.S.C. § 103 if it would have been obvious to a person of ordinary skill in the art, taking into account (1) the scope and content of the prior art, (2) the differences between the prior art and the claims, (3) the level of ordinary skill in the art, and (4) any so called "secondary considerations" of non-obviousness, which include: (i) "long felt need" for the claimed invention, (ii) commercial success attributable to the claimed invention, (iii) unexpected results of the claimed invention, and (iv) "copying" of the claimed invention by others. I further understand that it is improper to rely on hindsight in making the obviousness determination. I have been informed that Alacritech claims a filing priority date no later than October 14, 1997 for claims 1, 3, 6-9, 11, 14-17, 19, and 21-22 of the 948 Patent. Accordingly my analysis of the prior art for the claims of the 948 Patent is based on the prior art

and knowledge of a person having ordinary skill in the art ("POSA") as of October 14, 1997.

- 17. I have been informed that a claim can be obvious in light of a single prior art reference or multiple prior art references. I further understand that exemplary rationales that may support a conclusion of obviousness include:

- (A) Combining prior art elements according to known methods to yield predictable results;

- (B) Simple substitution of one known element for another to obtain predictable results;

- (C) Use of known technique to improve similar devices (methods, or products) in the same way;

- (D) Applying a known technique to a known device (method, or product) ready for improvement to yield predictable results;

- (E) "Obvious to try" choosing from a finite number of identified, predictable solutions, with a reasonable expectation of success;

- (F) Known work in one field of endeavor may prompt variations of it for use in either the same field or a different one based on design incentives or other market forces if the variations are predictable to one of ordinary skill in the art;

(G) Some teaching, suggestion, or motivation in the prior art that would have led one of ordinary skill to modify the prior art reference or to combine prior art reference teachings to arrive at the claimed invention.

#### IV. LEVEL OF ORDINARY SKILL IN THE ART

- I have been informed that factors that may be considered in 18. determining the level of ordinary skill in the art may include: (A) "type of problems encountered in the art;" (B) "prior art solutions to those problems;" (C) "rapidity with which innovations are made;" (D) "sophistication of the technology;" and (E) "educational level of active workers in the field." I also understand that, every factor may not be present for a given case, and one or more factors may predominate. Here, the 948 Patent is directed to an apparatus and methods for receive side network protocol offload. In my experience, systems such as those capable of protocol offload are not designed by a single person but instead require a design team with wide ranging skills and experience including computer architecture, network design, software development and hardware Moreover, the design team typically would have comprised development. individuals with advanced degrees and some industry experience, or significant industry experience.

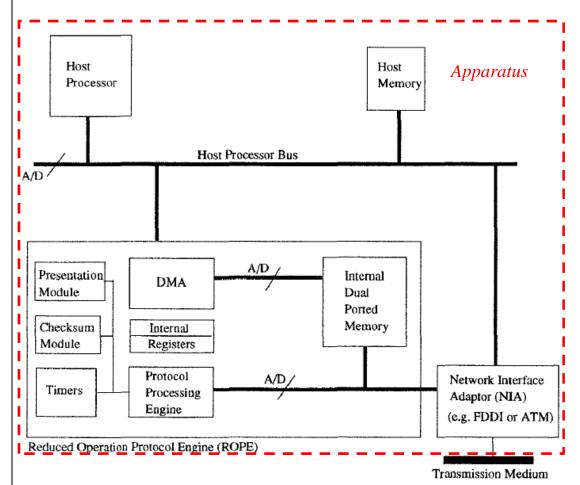

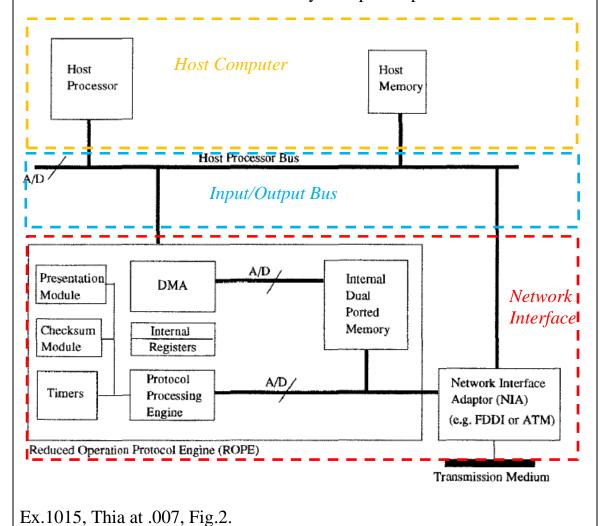

- 19. Accordingly, and while it would be rare to find all of these skills in a single individual, it is my opinion that a person of ordinary skill in the art

("POSA") is a person with at least the equivalent of a B.S. degree in computer science, computer engineering or electrical engineering with at least five years of industry experience including experience in computer architecture, network design, network protocols, software development, and hardware development.

20. The statements that I make in this declaration when I refer to a POSA are from the perspective of October 14, 1997.

## V. STATE OF THE ART AND OVERVIEW OF TECHNOLOGY AT ISSUE

21. In this section, I provide an overview of the technology at issue and illustrate the state of the art.

### A. Layered Network Protocols

22. The primary goal of computer networking is to provide fast, reliable data communications between computer systems. Interoperability has been accomplished through adherence to standards, and performance has steadily increased through new technology and optimizations of hardware and software.

### 1. OSI Layers

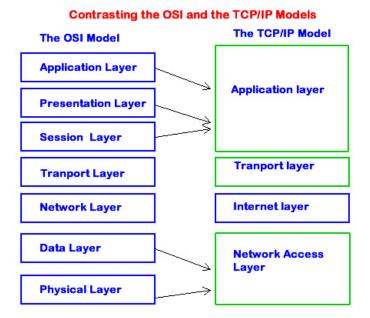

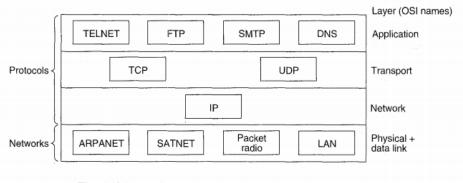

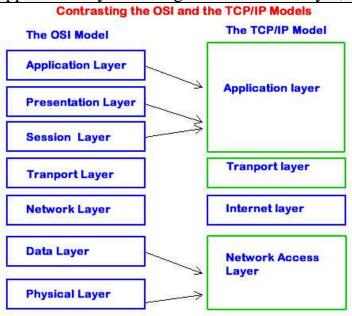

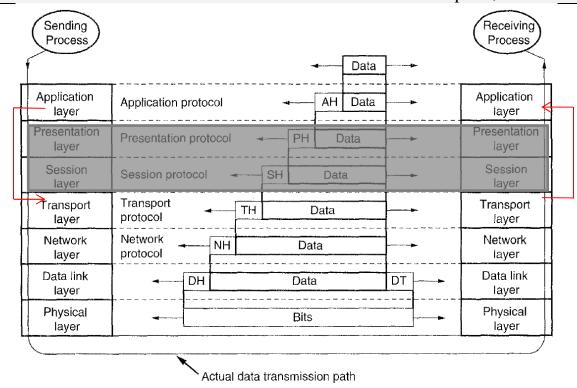

23. Computer networking standards provide inter-system communications across a wide range of hardware and software implementations. The seven-layer OSI model describes a logical layering including physical, data link, network, transport, session, presentation and application as illustrated below.

### 2. TCP/IP Layers

24. The TCP/IP layering is slightly different and corresponds more closely to the way the networking code is typically partitioned in some popular Unix variants. TCP/IP layers include physical (e.g. 100baseT, 1000baseT), data link<sup>1</sup> (e.g. IEEE 802 Ethernet, ATM, Token Ring), Internet (e.g. IPv4, IPv6), transport (e.g. TCP, UDP, VMTP, XTP), and Application (e.g. FTP, SMTP, Telnet, HTTP). A network interface connected to a TCP/IP network receives TCP/IP packets that comply with the TCP/IP protocol. The following figure shows the relationship between the OSI and TCP/IP layering.

Tanenebaum96 and the "interface layer" in Stevens2 (see below for description of

these references). Some Alacritech patents use "data link layer," "link layer" and

"MAC layer." Prior art references use many of these terms and also sometimes use

the name of a specific implementation (e.g. Ethernet, ATM).

<sup>&</sup>lt;sup>1</sup> References on TCP/IP use different terminology to describe the layer under IP layer. The data link layer is also called the "host-to-network layer" in

Available at <a href="http://mitigationlog.com/how-tcpip-and-reference-osi-model-works/">http://mitigationlog.com/how-tcpip-and-reference-osi-model-works/</a>.

An application layer is above the transport layer in both protocols.

25. At a conceptual level, each layer is responsible only for its respective functions. This enables, for example, hiding the complexity of the physical data connection (that is, actually transmitting the data onto the physical wires) from layers above the physical, data link, and network layers above. Likewise, the lower layers must transmit the data on the physical wires, but need not worry about what application the data belongs to or even whether it is receiving packets in the correct order.

10

<sup>&</sup>lt;sup>2</sup> It appears that this diagram was made in 2012. It is being used for illustrative purposes only.

### B. TCP/IP

26. The 948 Patent relates to an intelligent network interface card that provides a "fast path" that avoids host protocol processing for most packets in a large multipacket message. Ex.1001, 948 Patent at Abstract. The claims are all directed to TCP/IP.

27. By the mid 1990s, TCP/IP was a firmly entrenched standard and was a widespread networking protocol to, for example, access the Internet and World Wide Web, overtaking the OSI protocols. *See* Ex.1006, Tanenbaum96 at .016 ("The OSI protocols have quietly vanished, and the TCP/IP protocol suite has become dominant.") By that time, detailed descriptions of the protocols and opensource implementations were widely available from books technical papers, and code repositories. Free implementations of TCP/IP, such as Free BSD, were widely available and widely used. Standard reference books on TCP/IP included Stevens1 (Ex.1008), Stevens2 (Ex.1013), and Tanenbaum96 (Ex.1006), all of which were widely cited and relied upon.<sup>3</sup> A series of technical memos called RFCs (request for comments) document the progression of design concepts of the Internet. TCP/IP was standardized in a series of publically available Request for

<sup>&</sup>lt;sup>3</sup> These books were well known resources to a POSA. Consistent with that, Alacritech patents cite editions of the Tanenbaum and Stevens books.

Comments (RFCs) published by the Internet Engineering Task Force, including RFC 793, entitled "Transmission Control Protocol" and RFC 791, entitled "Internet Protocol." Ex.1007, RFC 793; Ex.1036, RFC 791. A few of the key RFCs are quoted below to establish when certain concepts were proposed and documented.

28. TCP/IP consists of two parts: (1) Transmission Control Protocol (TCP), which provides virtual bi-directional connections that are guaranteed inorder, error-free delivery of arbitrary amounts of data between programs running on different computers over the Internet; and (2) Internet Protocol (IP), which provides delivery of datagrams (IP packets) to any routable Internet address, without any reliability or ordering guarantees. IP also provides for fragmentation during transmission and reassembly when received. Fragmentation occurs when an IP packet must be divided ("fragmented") into smaller packets when a packet travels over an intermediate network with a small packet size. TCP network interface includes the ability to receive multiple TCP packets for the same connection. TCP/IP can be transmitted over a variety of physical media (e.g. Ethernet).

### 1. Encapsulation

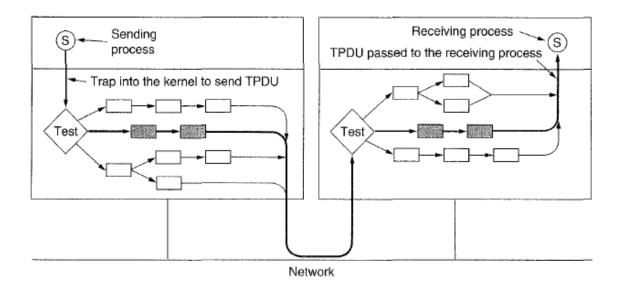

29. Network layering corresponds to the encapsulation of higher levels by lower levels. TCP runs on "top" of IP by first dividing application data to be

transmitted into segments that become the data payloads of TCP packets and concatenating each payload with a TCP header to form a TCP packet, a process called TCP segmentation. TCP/IP then places the resulting TCP packet (TCP header + payload) into the data payload of an IP packet by concatenating the TCP packet (IP data payload) with an IP header. The TCP packet is thus "encapsulated" in an IP packet.

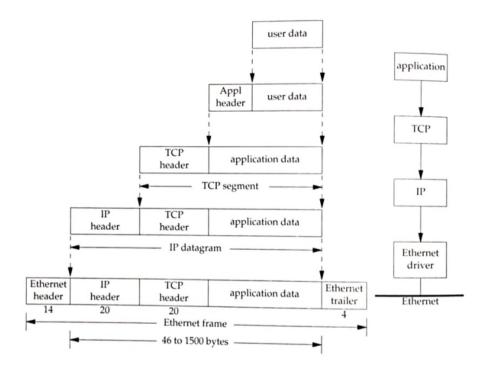

30. The following figure shows an example with application data accompanied by an application header. As shown in the figure below, in typical TCP/IP processing, the packet is built from the top down, i.e., each layer encapsulates what it receives from the above layer by concatenating an additional header associated with that layer. The application header-data combination becomes the application data of a TCP segment. The TCP segment containing the application header-data combination along with the IP header forms an IP datagram. The IP datagram along with an appropriate MAC (media access control) layer header forms the frame that is sent over the physical interconnect. The diagram below shows an example of such encapsulation where the MAC layer is Ethernet. Some software implementations implement the layers separately with data, or pointers to data, passed between the software modules for each layer. In this case, one module creates the user data and application header, another module

then encapsulates that with a TCP header, etc. The processing occurs sequentially, from top to bottom, as shown below.

Figure 1.7 Encapsulation of data as it goes down the protocol stack.

Ex.1008, Stevens1 at .034. When receiving a packet from the network, the layers work in reverse, with each layer stripping its header and providing the resulting packet to the above layer. The user data without headers is eventually delivered to the relevant application.

#### 2. Ethernet Header

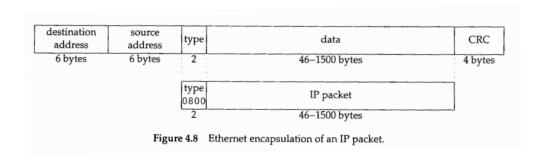

31. The lowest layer, the MAC (media access control) layer handles the actual transmission on the physical media. A 14-byte Ethernet header, for example, includes 48-bit (6 byte) source and destination MAC addresses for

uniquely identifying the network interface (e.g., on a computer or router) on a local area network at each end of the link.

Ex.1013, Stevens2 at .125.

32. The MAC address can be determined by a routing table in the protocol stack. In an Ethernet-based network, the 48-bit MAC address corresponds to a physical interface, such as a network interface card (NIC) or WiFi modem in a server or router. The MAC address field of the destination in the Ethernet header determines the next hop along the route to the destination. At each router along the path, the MAC address field is changed to the MAC address of the next router. The final router changes the MAC address field to the MAC address of the destination.

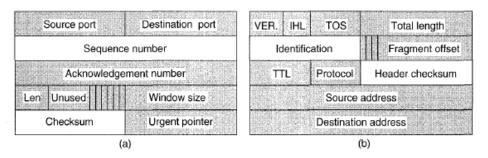

### 3. IP Header

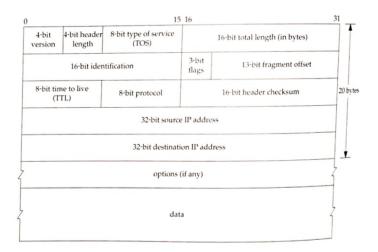

Figure 3.1 IP datagram, showing the fields in the IP header.

Ex.1008, Stevens1 at .058.

33. Above the MAC layer is the Internet protocol layer (IP layer). An IP header is illustrated by the figure above from Stevens1. The IP header includes source and destination IP addresses for identifying the end points (e.g., computer) of the connection. The IP header also has a flag that indicates whether the packet has been fragmented. The 32-bit IPv4 addresses are usually expressed in dotted decimal notion. For example, an IP address of Google.com is 216.58.216.46.

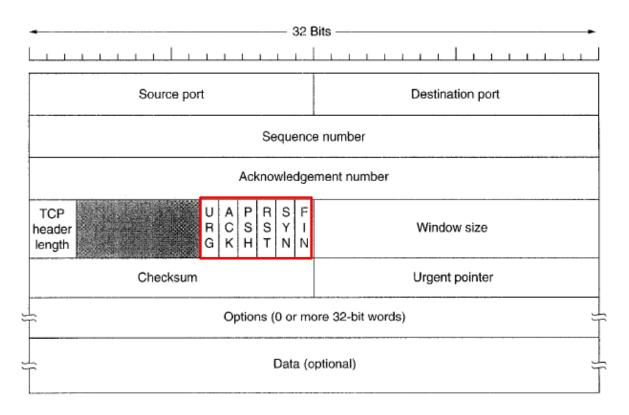

### 4. TCP header

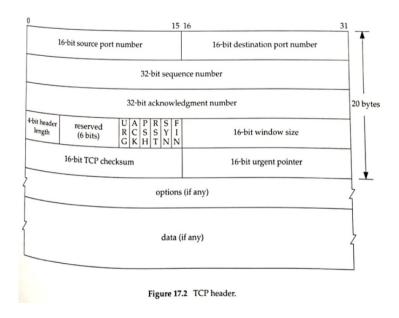

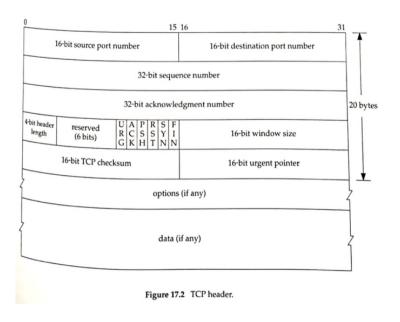

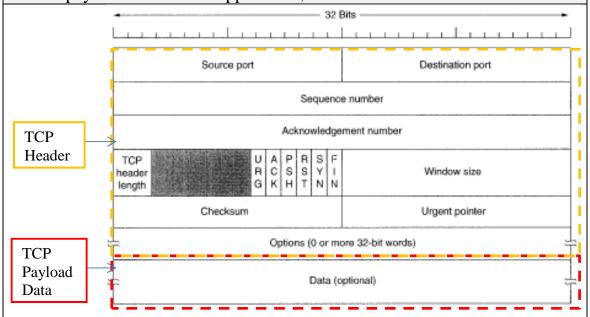

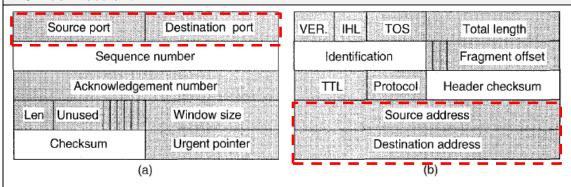

Ex.1008, Stevens1 at .249.

34. Above the IP layer is the TCP (Transport) layer. A TCP header is illustrated by the figure above from Stevens1. The TCP header includes 16-bit source and destination port numbers for identifying the processes that are communicating. These port numbers identify the end points (e.g., client or server programs) sending and receiving data on each end of the connection. TCP is used to establish connections between processes at IP addresses across the network and the TCP port numbers identify which processes are communicating. For instance, Email may use SMTP (simple mail transfer protocol) on port 25 (SMTP's well-known port number) while a web server is using HTTP on port 80 (HTTP's well-known port number).

Petition for *Inter Partes* Review of 8,850,948 Ex. 1003 ("Horst Decl.")

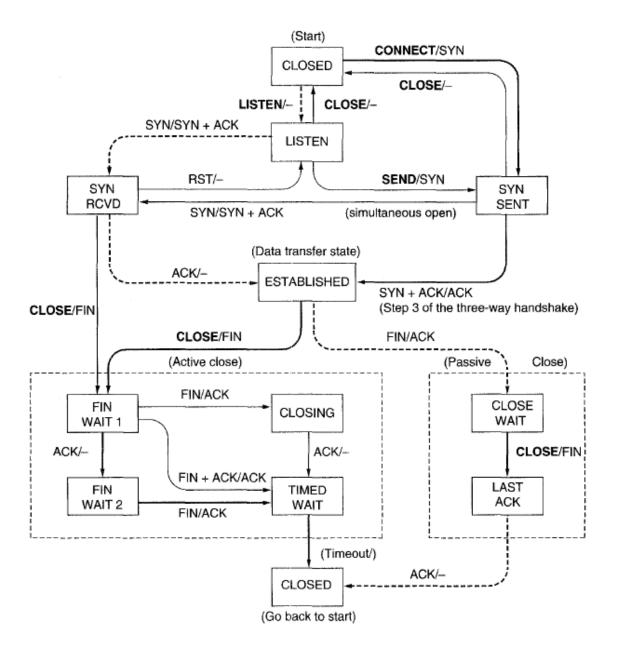

- 35. The TCP layer performs several important functions such as tracking the sequence of packets to ensure that the TCP packets are assembled in the proper order. As shown above, a "sequence number" is included in the TCP header for several reasons such as identifying TCP packets and performing reassembly of these packets. The TCP layer tracks and acknowledges the sequence of packets, so that the sending TCP layer can re-send lost (and therefore unacknowledged) data so that the application does not have to manage this process. The TCP layer assembles the data from packet payloads in the proper order by using sequence numbers in the TCP packet headers.

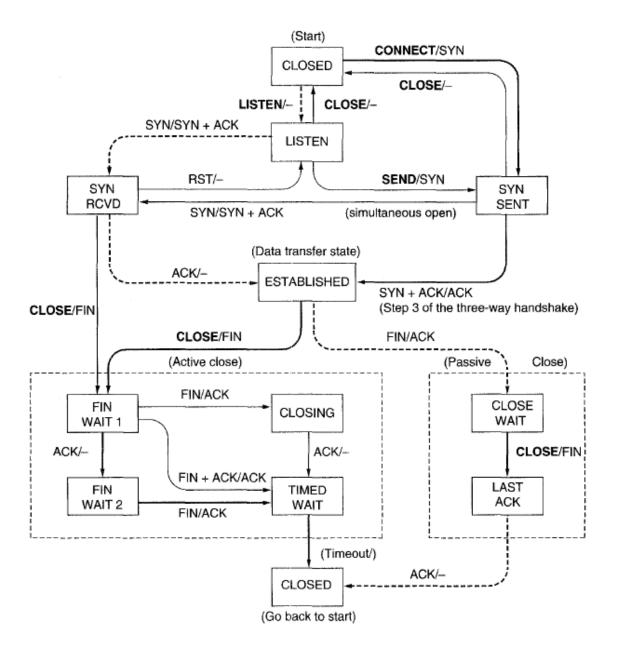

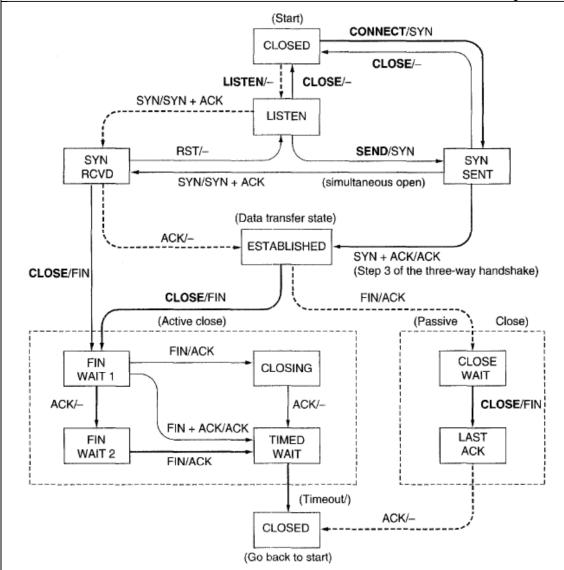

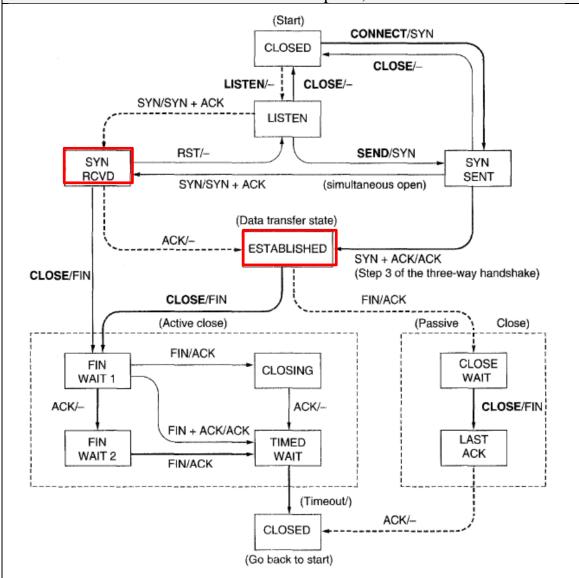

- 36. TCP maintains the status of each connection with a finite state machine. The TCP finite state machine and associated messages are described in detail in RFC 793. RFC 793 describes the data structure for storing the information needed to maintain a TCP connection as a Transmission Control Block (TCB). Ex.1007, RFC 793 at .016. The finite state machine is also illustrated in Tanenbaum96 below.

**Fig. 6-28.** TCP connection management finite state machine. The heavy solid line is the normal path for a client. The heavy dashed line is the normal path for a server. The light lines are unusual events.

Connections begin in a CLOSED state. Different control flags in the TCP header of packets sent between client and server affect the state of the connection. These control flags are URG, ACK, PSH, RST, SYN, and FIN as illustrated below.

Ex.1008, Stevens1 at .249. Certain control flags indicate that the connection is not yet established or will be closed. A server can move from CLOSED into a LISTEN state, where it will wait until a request to initialize a connection is received in a packet with the SYN flag set. A server is not in the ESTABLISHED state until the server acknowledges the SYN packet. In the ESTABLISHED state, data is transferred over the connection. Either side can close the connection by sending a special packet called a FIN packet. Control flags URG, and RST are also requests to close a connection, which indicates that the server is no longer in the ESTABLISHED state.

37. Accordingly, routing packets between source and destination processes over a TCP/IP connection using Ethernet requires TCP source and destination port numbers, source and destination IP addresses, and source and

destination MAC addresses. For more information on TCP, *see* Stevens1 (Ex.1008) Chapter 17, "TCP: Transmission Control Protocol," .247-252.

### 5. Application Data

38. Each user application typically has at least one range of addresses in the user space region of host memory where it places data for transmission and receives data from the network. For transmission, the protocol stack can retrieve data from this area in host memory, encapsulate it in packets as described above, and then transmit it over the network. For receipt of data, the protocol stack puts data in the assigned host memory after it has processed and stripped off the MAC, IP, and TCP headers from the packet.

### 6. RFC 793 – TCP Specification

39. The original TCP specification was published in RFC 793 (Ex.1007) in September 1981. RFC 793 is a full specification for TCP and shows, among many other things, that identifying a TCP connection by its source and destination IP addresses and TCP ports were known more than 15 years before the earliest priority dates of the Alacritech patents.

### **B.** Protocol Offload and Fast-Path Processing

40. To increase performance and reduce demands on the host computer required for protocol processing, designers have employed different techniques such as parallel processing, improved hardware, memory copy reduction via hardware and/or software, and hardware to offload all or part of the protocol stack.

### 1. RFC 647 – Front-Ending

41. As early as 1974, front-end protocol offload was already being considered for standardization as described in request-for-comments RFC 647. This represents the consensus at the time that front ending (the offloading of protocol processing) was desirable. At that time, NCP (Network Control Protocol) was the protocol used in ARPANET, the predecessor to the modern Internet.

### "FRONT-ENDING"

In what might be thought of as the greater network community, the consensus is so broad that the front-ending is desirable that the topic needs almost no discussion here. Basically, a small machine (a PDP-11 is widely held to be most suitable) is interposed between the IMP and the host in order to shield the host from the complexities of the NCP.

Ex.1019, RFC 647 at .002.

42. RFC 647 goes on to discuss rigid and flexible front-end (FE) alternatives and includes a high-level discussion of a protocol for interfacing between the host and FE.

### 2. RFC 929 – Outboard Processing

43. In 1984, RFC 929 was distributed to begin work on a possible standard for interfacing between a host and an OPE (Outboard Processing Environment)<sup>4</sup>:

There are two fundamental motivations for doing outboard processing. One is to conserve the Hosts' resources (CPU cycles and memory) in a resource sharing intercomputer network, by offloading as much of the required networking software from the Hosts to Outboard Processing Environments (or "Network Front-Ends") as possible. The other is to facilitate procurement of implementations of the various intercomputer networking protocols for the several types of Host in play in a typical heterogeneous intercomputer network, by employing common implementations in the OPE.

Ex.1009, RFC 929 at .002.

<sup>&</sup>lt;sup>4</sup> Other names have been used to describe the OPE concept. Names for protocol offload implementations included Front-End Processor, Network Front-End, Protocol Processor, Protocol Engine, Protocol Accelerator, Hardware Bypass, Smart Network Interface, SMART NIC, Smart Adapter, Protocol Processing Engine, IO Adapter, Intelligent I/O Processor and intelligent Network Interface Card.

The interaction between the Host and the OPE must be capable of providing a suitable interface between processes (or protocol interpreters) in the Host and the off-loaded protocol interpreters in the OPE. This interaction must not, however, burden the Host more heavily than would have resulted from supporting the protocols inboard, lest the advantage of using an OPE be overridden.

*Id.* at .003.

44. RFC 929 includes a "protocol parameter" for selecting the protocol to be offloaded. TCP, UDP and IP were among the protocols to be offloaded:

| Generic | Specific | Comment                                 |

|---------|----------|-----------------------------------------|

| GIP     | IP       | Datagram Internetwork Protocol          |

| HHP     | TCP      | Connection Transport/Host-Host Protocol |

| GDP     | UDP      | Datagram Transport/Host-Host Protocol   |

| VTP     | TEL      | Virtual Terminal (Telnet) Protocol      |

| GFP     | FTP      | File Transfer Protocol                  |

| MAIL    | SMTP     | Mail Transfer Protocol                  |

| PROX    | PROX     | Proximate Net Interface Protocol        |

|         |          |                                         |

*Id.* at .013.

### 3. Mediation Levels

45. The 1984 proposal to standardize offload implementations in RFC 929 is evidence that there was already much activity in offload implementations at that time. The authors of RFC 929 anticipated different types of outboard processors and recognized that the amount of work to be done by the outboard processor might vary from none to partial to full offload. To handle this range, a "mediation level" parameter was proposed.

The mediation level parameter is an indication of the role the Host wishes the OPE to play in the operation of the protocol. The extreme ranges of this mediation would be the case where the Host wished to remain completely uninvolved, and the case where the Host wished to make every possible decision. The specific interpretation of this parameter is dependent upon the particular off-loaded protocol.

The concept of mediation level can best be clarified by means of example. A full inboard implementation of the Telnet protocol places several responsibilities on the Host. These responsibilities include negotiation and provision of protocol options, translation between local and network character codes and formats, and monitoring the well-known socket for incoming connection requests. The mediation level indicates whether these responsibilities are assigned to the Host or to the OPE when the Telnet implementation is outboard. If no OPE mediation is selected, the Host is involved with all negotiation of the Telnet options, and all format conversions.

With full OPE mediation, all option negotiation and all format conversions are performed by the OPE. An intermediate level of mediation might have ordinary option negotiation, format conversion, and socket monitoring done in the OPE, while options not known to the OPE are handled by the Host.

The parameter is represented with a single ASCII digit. The value 9 represents full OPE mediation, and the value 0 represents no OPE mediation. Other values may be defined for some protocols (e.g., the

intermediate mediation level discussed above for Telnet). The default value for this parameter is 9.

*Id.* at.015-.016.

46. More than a decade passed between the publication of RFC 929 and the priority date of the earliest Alacritech provisional application. During that time, protocol offload was the subject of many papers and systems across the range anticipated by RFC 929. These implementations can be categorized based on the three principal dimensions of protocol offload: 1) The set of protocols to be offloaded (e.g. TCP/IP, VMTP, OSI), 2) the portions of the protocol that are offloaded (e.g. full offload, partial offload, fast path offload, no offload), 3) the offload implementation (e.g. parallel processor, standard microprocessor, custom processor, custom hardware). The cited references below include many different combinations of these three dimensions, but it should be noted that each cited combination was primarily a design decision among a small, finite number of choices. It would have been obvious to alter these implementations along one or more of the dimensions for a new implementation that would have produced predictable results. In other words, it was well recognized that depending on the application, it was desirable to vary the extent of offloading. The simplest example is that while offloading the entire protocol may seem on the surface advantageous, it was expensive because handling every type of data packet requires a complex

offloading device. For example, it was well known that setting up a connection and entering the ESTABLISHED state was much more complex than simply receiving and sending data packets. Ex.1006, Tanenbaum96 at .583 ("The key to fast TPDU processing is to separate out the normal case (one-way data transfer) and handle it specially. Although a sequence of special TPDUs are needed to get into the *ESTABLISHED* state, once there, TPDU processing is straightforward until one side starts to close the connection.").

#### C. Offloaded Protocols

47. By the mid-1990s, TCP/IP was becoming a predominant network standard, but many other networks were still in use and new network protocols were being investigated.

### 1. OSI Protocol Offload

48. OSI protocol offload engines were built and tested by Thia and Woodside. Ex.1015, Thia and Ex.1038, Woodside.

#### 2. TCP/IP Protocol Offload

49. TCP/IP offload engines were built or described by many in the field including Bach, Erickson, Morris, Cooper, Kung, Rütsche and Chesson. Ex.1020, Bach; Ex.1005, Erickson; Ex.1021, Morris; Ex.1022, Cooper; Ex.1023, Kung; Ex.1017, Rütsche92; Ex.1018, Rütsche93; Ex.1024, Chesson.

### 3. VMTP and XTP Protocol Offload

50. VMTP and XTP were proposed as alternatives to TCP. A VMTP offload engine was described by Kanakia, and an XTP protocol accelerator was described by Chesson. Ex.1025, Kanakia; Ex.1024, Chesson.

#### 4. Multi-Protocol Offload

51. General-purpose offload engines were also proposed. Erickson discloses a range of protocol scripts for offloading different protocols.

Each type of protocol will have its own script. Types of protocols include, but are not limited to, TCP/IP, UDP/IP, BYNET lightweight datagrams, deliberate shared memory, active message handler, SCSI, and File [sic:Fibre] Channel.

Ex.1005, Erickson at 5:47-51.

52. Kung and Cooper describe the Nectar network-based multicomputer system in which the processors communicate via Communications Acceleration Boards (CABs) that can run different protocols.

The CAB runtime system currently supports several transport protocols with different reliability/overhead tradeoffs [10]. They include the standard TCP/IP protocol suite besides a number of Nectar-specific protocols.

Ex.1026, Kung and Cooper at .003.

#### D. Portions of the Protocol Offloaded

53. The portion of the protocol offloaded (called "mediation level" in RFC 929) falls into several types that range from partial offload to full offload. That is, either part of the protocol processing can be offloaded (partial offload) or the entire protocol processing can be offload (full offload).

#### 1. Checksum Offload

- 54. One of the first parts of protocol processing to be offloaded was the checksum calculation (a partial offload). An adapter doing only checksum offload is less complex because it does not require the adapter to maintain the connection state.

- 55. Dalton describes the HP Afterburner card with optional hardware for checksum calculation:

To support the use of the on-card memory as clusters, we have written a small number of functions. The most important is a special copy routine, functionally equivalent to the BSD function bcopy. It is optimized for moving data over the I/O bus, and also optionally uses the <u>card's built-in unit to calculate the IP checksum</u> of the data it moves. Another function converts a single-copy cluster into a chain of normal clusters and mbufs; it also calculates the checksum.

Ex.1027, Dalton at .011 (emphasis added).

#### 2. Full Offload

56. Exemplary full offload papers and systems include Murphy, Bach, MacLean, Cooper and Rütsche.<sup>5</sup> Ex.1028, Murphy; Ex.1020, Bach; Ex.1029, MacLean; Ex.1022, Cooper; Ex.1017, Rütsche92; Ex.1018, Rütsche93.

### 3. Multi-Level Offload

57. Chesson describes a protocol chip plus an optional control processor that can do a range of offloads from partial (checksum, sequence numbers, etc.) to full offload. Ex.1024, Chesson.

### 4. Header Prediction

58. In 1988, Van Jacobson proposed a header prediction algorithm for improving the performance of TCP/IP implementations. This "header prediction" teaching led to various types of partial offload. The code, which uses header templates, is partitioned into one module for the commonly executed path (the fast

<sup>&</sup>lt;sup>5</sup> In a "full offload," the adapter does not typically initiate connections on its own. The host initiates the connection by opening a socket to an IP address and TCP port. The host establishes the connection and directs the stack of protocol layers to create the connection. Yet those of skill in the art often still refer to such systems as "full offload."

path) and another module to handle the more complex cases and exception handling (the slow path).

59. Code to implement the header prediction algorithm was incorporated in the BSD 4.4-Lite distribution.

Most IP packets carry no options. Of the 20-byte header, 14 of the bytes will be the same for all IP packets sent by a particular TCP connection. The IP length, ID, and checksum fields (6 bytes total) will probably be different for each packet. Also, if a packet carries any options, all packets for that TCP connection will be likely to carry the same options.

The Berkeley implementation of UNIX makes some use of this observation, associating with each connection a template of the IP and TCP headers with a few of the fixed fields filled in. To get better performance, we designed an IP layer that created a template with all the constant fields filled in. When TCP wished to send a packet on that connection, it would call IP and pass it the template and the length of the packet. Then IP would block-copy the template into the space for the IP header, fill in the length field, fill in the unique ID field, and calculate the IP header checksum.

This idea can also be used with TCP, as was demonstrated in an earlier, very simple TCP implemented by some of us at MIT [6]. In that TCP, which was designed to support remote login, the entire state of the output side, including the unsent data, was stored as a

preformatted output packet. This reduced the cost of sending a packet to a few lines of code.

A more sophisticated example of header prediction involves applying the idea to the input side. In the most recent version of TCP for Berkeley UNIX, one of us (Jacobson) and Mike Karels have added code to precompute what values should be found in the next incoming packet header for the connection. If the packets arrive in order, a few simple comparisons suffice to complete header processing.

Ex.1030, Clark at .003.

- 60. The 1995 book (Stevens2) walks through the Jacobson BSD header prediction code including the conditions for selecting the fast or slow path. In order to take the fast receive path, six conditions must be met, including:

- 1. The connection must be established.

- 2. The following four control flags must not be on: SYN, FIN, RST, or URG. The ACK flag must be on.

- 3.-6. [Conditions to assure that the received segments are in-order] Ex.1013, Stevens2 at .962-.963.

### a) Partial Offload with Header Prediction

61. The fast and slow paths described by Stevens gave a natural division for protocol offload implementations. Building on the Jacobson BSD header prediction code, Biersack (Ex.1016) describes TCP protocol offload with fast and slow paths. This and Woodside (Ex.1015) also build upon the Jacobson BSD

header prediction algorithm and apply its teachings to derive an OSI protocol offload with the fast path implemented in hardware.

62. The header prediction code in the FreeBSD release is also discussed in the Alacritech 1997 Provisional application:

The base for the receive processing done by the INIC on an existing context is the fast-path or "header prediction" code in the FreeBSD release.

Ex. 1031, Alacritech 1997 Provisional Application at .057.

63. Thus, the Jacobson header prediction code forms the basis of what Alacritech offloads to its intelligent network interface card (INIC).

### E. Offload Implementation

64. Offloading the transport layer to an interface card was discussed in Tanenbaum96:

The hardware and/or software within the transport layer that does the work is called the transport entity. The transport entity can be in the operating system kernel, in a separate user process, in a library package bound into network applications, or on the network interface card.

Ex.1006, Tanenbaum96 at .498 (emphasis added).

65. Others have disclosed more details of offload hardware including implementations based on multiprocessors, microprocessors, custom processors and custom logic.

## 1. Multiprocessor Offload

66. Several groups proposed or built systems in which protocol processing is offloaded from the application processor to one or more dedicated processors in a multiprocessor configuration to protocol processing.

## 67. The Nectar system:

The Nectar communication processor together with its host can be viewed as a (heterogeneous) shared-memory multiprocessor. Dedicating one processor of a multiprocessor host to communication tasks can achieve some of the benefits of the Nectar approach, but this constrains the choice of host operating system and hardware. In contrast, the Nectar communication processor has been used with a variety of hosts and host operating systems.

Ex.1022, Cooper at .006.

## 68. The Parallel Protocol Engine:

In this paper our goal is to demonstrate that a careful implementation of a standard transport protocol stack on a general purpose multiprocessor architecture allows efficient use of the bandwidth available in today's high-speed networks. As an example, we chose to implement the TCP/IP protocol suite on our 4-processor prototype of the PPE.

Ex.1017, Rütsche92 at .009.

69. Rütsche also designed a Gb/s Multimedia Protocol Adapter based on the PPE:

In this paper we present a new multiprocessor communication subsystem architecture, the Multimedia Protocol Adapter (MPA), which is based on the experience with the Parallel Protocol Engine (PPE) [Kaiserswerth 92] and is designed to connect to a 622 Mb/s ATM network. The MPA architecture exploits the inherent parallelism between the transmitter and receiver parts of a protocol and provides support for the handling of new multimedia protocols.

Ex.1018, Rütsche93 at .001.

## 2. Offload Adapters based on Microprocessors

- 70. Protocol offloading may be implemented by executing code in one or more microprocessors on an intelligent network interface card or on a network accelerator board used in conjunction with a standard NIC (network interface card).

- 71. Kanakia describes a network adapter board with a microprocessor and other support chips:

The prototype Network Adapter Board (NAB) has been designed using Motorola's MC68020 as the on-board processor, running at 16 Mhz clock rate; it uses about 200 hundred standard MSI and LSI components. The current version is designed for connecting two VMP multiprocessor system with a 100 megabit/sec point-to-point connection.

Ex.1025, Kanakia at .010.

72. MacLean describes microprocessor-based protocol accelerators residing on a VME card:

The internal functions and data flows of the protocol accelerator shown in Figure 2. We use a dual CPU approach to protocol processing, with one CPU subsystem dedicated to the transmission, and the other to the reception. The transmit and receive CPUs are both 68020 (25 MHz) based, each with its own private resources: ROM, parallel I/O, interrupt circuitry and 128 kilobytes of random access memory (RAM). In addition there is 128 kilobytes of RAM shared by both CPUs which is also accessible to the two host busses, VME and VSB.

Ex.1029, MacLean at .004.

73. Rütsche describes a multimedia protocol adapter (MPA) using a pair of "transputer" microprocessors:

The selection of the inmos<sup>2</sup> T9000 [inmos 91] is based on our good experience with the transputer family of processors in the PPE. The most significant improvements of the T9000 over the T425 for protocol processing are faster programmable link interfaces, a faster memory interface, and a cache.

Ex.1018, Rütsche93 at .003.

# 3. Offload Adapters based on Custom Processors or Custom Logic

74. Other designers have proposed custom processors and/or custom logic for protocol offload. Chesson describes a Protocol Engine chipset for real-time protocol processing. Depending on the amount of protocol offload desired, an adapter can be built with or without the custom control processor (CP):

The Protocol Engine® chipset offers real-time protocol processing for high-speed networks. A wide range of cost-performance subsystem solutions are available through various configurations based on the PE Chipset. The chipset (shown in Figure 1) consists of four chips: MPORT, HPORT, BCTL, and CP. A basic configuration consists of MPORT, HPORT, and BCTL.

Ex.1024, Chesson at .006.

75. The optional Chesson Control processor is a custom processor designed for fast protocol processing:

Control Processor (CP) of the Protocol Engine® chipset is a 32-bit, multi-thread execution unit that provides high speed protocol processing.

*Id.* at .039.

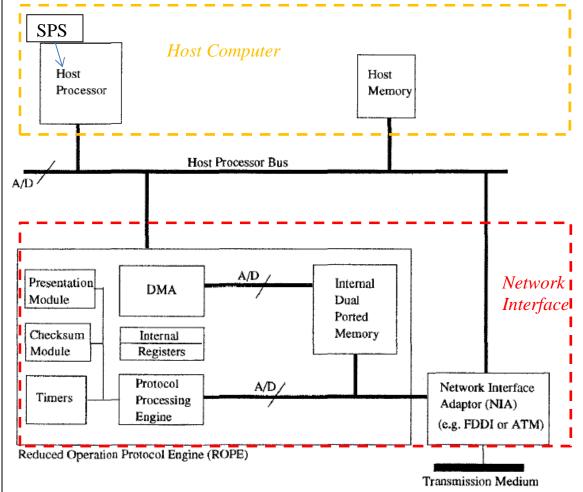

76. Thia also discloses the design of a custom VLSI chip for protocol offload:

The chip design based on bypassing is called ROPE, for Reduced Operation Protocol Engine. The contribution of this paper is to define

the host/chip interface and the chip operation, and to report on a VHDL-based feasibility study of the chip design. It appears to be feasible to support an end-system single-connection data rate approaching 1 Gbps.

Ex.1015, Thia at .002 and Ex. 1038, Woodside.

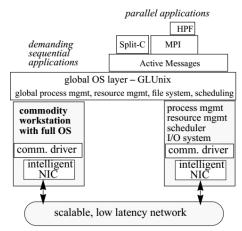

77. Culler describes the Berkeley Network of Workstations (NOW) in which the Active Messages protocol is offloaded to intelligent NICs built with Myricom LANai chips:

The hardware configuration of the Berkeley NOW system consists of one hundred and five Sun Ultra 170 workstations, connected by a large Myricom network[Bode95], and packaged into 19-inch racks. Each workstation contains a 167 MHz Ultra1 microprocessor with 512 KB level-2 cache, 128 MB of memory, two 2.3 GB disks, ethernet, and a Myricom "Lanai" network interface card (NIC) on the SBus. The NIC has a 37.5 MHz embedded processor and three DMA engines, which compete for bandwidth to 256 KB of embedded SRAM. The node architecture is shown in Figure 1.

Ex.1032, Culler at .001.

Figure 4. NOW software architecture

*Id.* at .003.

78. Alteon describes their third generation intelligent Ethernet adapter that includes performance improvements from protocol offload, reduction in memory copies and reduction of interrupts.

Using an intelligent adapter with an onboard RISC-based processor specially designed for embedded application processing, Alteon's Gigabit Ethernet technology not only reduces the number of times data is copied among processing entities, it allows a single interrupt to be issued for multiple data packets—radically altering the ratio of interrupts to packets, and eliminating the scalability problems inherent in older adapter designs.

Ex.1033, Alteon at .022.

79. HP discloses a custom chip called Tachyon that includes send offload, receive offload, hardware checksum calculation, DMA, and headers/data splitting:

Petition for *Inter Partes* Review of 8,850,948 Ex. 1003 ("Horst Decl.")

To provide support for customer networking applications, Tachyon:

- Manages the protocol for sending and receiving network sequences over Fibre Channel.

- Provides complete support of networking connections.

- Computes exact checksums for outbound IP packets and inserts them in the data stream, thereby offloading

the host of a very compute-intensive task.

- Computes an approximate checksum for inbound IP packets that partially offloads the checksum task from the host.

- Contains hardware header/data splitting for inbound SNAP/IP sequences.

Ex.1034, Smith at .004.

## F. Protocol Offload Summary

80. The preceding paragraphs have shown many offload implementations foreshadowed by RFC 929 described above. These implementations include many variations along the three dimensions of network protocol offload: 1) the set of protocols to be offloaded, 2) the portions of the protocol that are offloaded, and 3) the offload implementation. The citations show that each of the individual concepts was well known and that many different combinations along the three dimensions were successfully implemented by practitioners. It would have been obvious to alter these implementations along one or more of the dimensions for a new implementation that would have produced predictable results.

## G. Additional Background Technology

81. Protocol offload adapters have incorporated many well-known design techniques originally developed for general purpose processors. Some of these concepts, such as DMA and virtual memory, are briefly described below. More information is available from textbooks on Computer Architecture. See e.g., David A. Patterson and John L. Hennessy, Computer Architecture: A Quantitative

Approach, Morgan Kaufmann Publishers Inc., San Mateo, CA, USA., 1990. (Ex.1035, Patterson).

#### 1. DMA

82. DMA (Direct Memory Access) is a hardware-based technique for transferring data between memory systems or between a host memory and an I/O device.

Since I/O events so often involve block transfers, direct memory access (DMA) hardware is added to many computer systems to allow transfers of numbers of words without intervention by the CPU.

Ex.1035, Patterson at .151. Hardware that processes the received TCP/IP packets on the fast path must make the received data accessible to the application running on the host machine (e.g., in the designated host memory as discussed above).

DMA was a common and efficient way to achieve this, as I discuss below.

83. Before DMA was common, processors used I/O (input/output) instructions to transfer data to I/O devices. A benefit of using DMA is that fewer processor cycles are required to transfer the data. With DMA, the DMA engine is loaded with an address and count of data to be moved, then the data movement proceeds while the processor is doing other tasks. In some implementations, DMA engines are under the control of a host processor, while in others a DMA engine is controlled by an intelligent controller on an I/O adapter. The DMA engine itself may be located either in the host or on an I/O adapter.

84. DMA may be used either to read from host memory or to write to host memory. In some implementation, there are separate send and receive DMA engines and in others, a common DMA engine can be programmed to transfer to or from host memory:

Outbound Block Mover. The outbound block mover block's function is to transfer outbound data from host memory to the outbound sequence manager via DMA. It takes as input an address/length pair from the outbound sequence manager block, initiates the Tachyon system interface bus ownerships, and performs the most efficient number and size of transactions on the Tachyon system interface bus to pull in the data requested.

. . .

Inbound Block Mover. The inbound block mover is responsible for DMA transfers of inbound data into buffers specified by the multiframe sequence buffer queue, the single-frame sequence buffer queue, the inbound message queue, or the SCSI buffer manager. The inbound block mover accepts an address from the inbound data manager, then accepts the subsequent data stream and places the data into the location specified by the address.

Ex.1034, Smith at .007, .009.

Movement of data across the host bus interface are minimized by using an on-chip DMA for fast block data transfer to/from the host system memory.

Ex.1015, Thia at .007 and Ex.1038, Woodside.

Bus Controller (BC): The BC is a programmable busmaster DMA controller. It provides a small FIFO and a table for DMA requests. The FIFO contains a pointer to the linked list of source data and a connection identifier. The BC determines the destination memory address through the connection identifier in the table. The list format is the same for the BC and the DMAU. In the transmit BC the host writes to the FIFO and the protocol processor to the table. In the receive BC the protocol processor writes to the FIFO and the host to the table.

Ex.1018, Rütsche93 at .004-.005.

## 2. Virtual and Physical Memory Addresses

85. I/O adapters that transfer data directly to or from memory need to be provided with the memory addresses of the buffers. Many processors use virtual addressing in which large buffers appear to the processor as single contiguous memory space even though the addressed pages may not be contiguous in physical memory. To translate from virtual to physical memory addresses, the processor uses page tables that store the appropriate mappings from virtual to physical pages.

With virtual memory, the CPU produces *virtual addresses* that are translated by a combination of hardware and software to *physical addresses*, which can be used to access main memory. This process is called *memory mapping* or *address translation*.

Ex.1035, Patterson at .050 (emphasis in original).

86. In order for an I/O device to access the main memory buffers, either the physical address may be supplied for each page, or a translation table may be maintained on the I/O controller to allow it to operate on virtual addresses. Erickson has a "physical address buffer map" in the adapter memory and discusses some options for handling the translation:

The vtophys() function performs a translation of the user-provided virtual address into a physical address usable by the adapter. In all likelihood, the adapter would have a very limited knowledge of the user process' virtual address space, probably only knowing how to map virtual-to-physical for a very limited range, maybe as small as a single page. Pages in the user process' virtual address space for such buffers would need to be fixed. The udpscript procedure would need to be enhanced if the user data were allowed to span page boundaries.

Ex.1005, Erickson at 8:14-24.

- 87. Tanenbaum 96 suggests the use of direct copying into the user buffer to avoid unnecessary copy. Ex.1006, Tanenbaum96 at .585. Tanenbaum96 also identified a goal of system design for better performance was to avoid unnecessary copying ("[a packet] is copied to a network layer buffer, then to a transport layer buffer, and finally to the receiving application process.") Ex.1006, Tanenbaum96 at .579, .582.

- 88. In implementations that avoid the extra copy steps, the DMA engine transfers the reassembled original byte stream into user space for use by the

application layer. Once the headers are processed, the application has no need for those headers, as demonstrated by the illustration of the protocol stack above in Section V.B.1. See Ex.1006, Tanenbaum96 at .055-56, .541. For example, Tanenbaum96 discloses that the headers are checksummed before transferring data to user space to verify that it is going to the correct location: "The header and data should be separately checksummed, for two reasons. First, to make it possible to checksum the header but not the data. Second, to verify that the header is correct before starting to copy the data into user space. It is desirable to do the data checksum at the time the data are copied to user space, but if the header is incorrect, the copy may be to the wrong process." *Id.* at .589. The TCP/IP headers are added (and stripped off) by intermediate layers as the data moves through the protocol stack.

#### VI. OVERVIEW OF 948 PATENT

- 89. The 948 Patent relates to offloading TCP protocol processing for established TCP connections to a network interface card (NIC). Ex.1001, 948 Patent at Abstract. The specification of the 948 Patent refers to the disclosed NIC, which performs offloading, as an "intelligent network interface card (INIC)". *See id.* at Abstract.

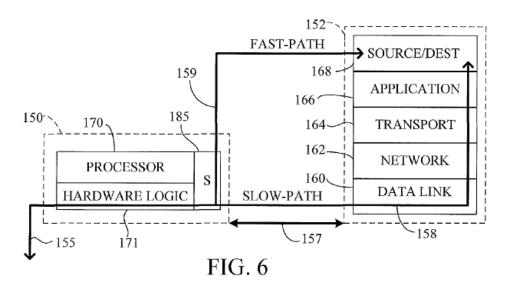

- 90. The INIC of the 948 Patent permits two modes of operation: a "fast path" in which protocol processing from the physical layer through the TCP layer

bypasses the host protocol stack and is instead performed on the INIC, and a "slow path" in which network frames are handed to the host at the MAC layer and passed up through the host protocol stack conventionally. The concept is illustrated in Fig. 6, shown below:

A simplified intelligent network interface card (INIC) 150 is shown in FIG. 6 to provide a network interface for a host 152. Hardware logic 171 of the INIC 150 is connected to a network 155, with a peripheral bus (PCI) 157 connecting the INIC and host. The host 152 in this embodiment has a TCP/IP protocol stack, which provides a slow-path 158 for sequential software processing of message frames received from the network 155. The host 152 protocol stack includes a data link layer 160, network layer 162, a transport layer 164 and an application layer 166, which provides a source or destination 168 for the communication data in the host 152.... The INIC 150 has a network processor 170 which chooses between processing messages

along a slow-path 158 that includes the protocol stack of the host, or along a fast-path 159 that bypasses the protocol stack of the host.

Ex.1001, 948 Patent at Fig.6; 9:11-29.

91. When a connection is created, the host computer creates a connection record that is referred to in the 948 Patent as a "Communication Control Block (CCB)." Ex.1001, 948 Patent at 5:22-29. This contains similar information as in the Transmission Control Block (TCB) in RFC791, namely connection and state information for the connection. Ex.1001, 948 Patent at 12:32-39. When the INIC receives a packet, it checks whether a connection exists by looking for a CCB corresponding to the connection information in the received packet header. The INIC uses the result of this comparison to determine which "path" should be used for a received packet. If the connection exists, the packet is processed on the fast path, bypassing the host protocol stack:

The processor 170 chooses, for each received message packet held in storage 185, whether that packet is a candidate for the fast-path 159 and, if so, checks to see whether a fast-path has already been set up for the connection that the packet belongs to. To do this, the processor 170 first checks the header status summary to determine whether the packet headers are of a protocol defined for fast-path candidates.... For fast-path 159 candidates, the processor 170 checks to see whether the header status summary matches a CCB held by the INIC. If so, the data from the packet is sent along fast-path 159 to the destination 168

in the host. If the fast-path 159 candidate's packet summary does not match a CCB held by the INIC, the packet may be sent to the host 152 for slow-path processing to create a CCB for the message.

Ex.1001, 948 Patent at 31:7-22, 11:57-12:10.

92. The claims of the 948 Patent are directed to fast-path TCP receive processing when a connection is in the ESTABLISHED state (in other words, there are no exceptions such as no IP fragmentation, or one of the SYN, FIN or RST flags set in the received packet).

#### VII. 948 PATENT PROSECUTION HISTORY

- 93. I have reviewed the prosecution history of the 948 Patent. There were no rejections or amendments during the prosecution of the 948 Patent.

- 94. The 948 Patent is a continuation of U.S. Patent Application No. 09/692,561, filed October 18, 2000, which is a continuation of U.S. Patent No. 6,226,680, filed April 28, 1998, which claims the benefit of U.S. Patent Application No. 60/061,809 filed October 14, 1997. Therefore, the earliest possible priority date of the 948 Patent is October 14, 1997.

- 95. On December 19, 2013, Applicant filed an Information Disclosure Statement with 383 patents, 41 applications, 13 foreign patents, and 112 non-patent literature documents, including Thia and Tanenbaum96. *See* Ex.1002 at .075-99. Neither Thia nor Tanenbaum96 were discussed during the prosecution of the application leading to the 948 Patent.

- 96. On June 20, 2014, the Examiner gave the following reasons for allowance:

- 2. The following is an examiner's statement of reasons for allowance: None of the prior art of record taken singularly or in combination teaches or suggest a network interface of a host computer for checking whether received packets have certain exception conditions, including whether the packets are IP fragmented, have a FIN flag set, or out of order; processing any of the received packet that have the exception conditions, and storing payload data of the received packets that do not have any of the exception conditions in a buffer of the host computer and without any TCP header stored between the payload data of the received packets.

Ex. 1002, 948 Prosecution History at .117.

#### VIII. CLAIM CONSTRUCTIONS

## A. Legal Standard

- 97. I understand that in deciding whether to institute *inter partes* review, "[a] claim in an unexpired patent shall be given its broadest reasonable construction in light of the specification of the patent in which it appears." 37 C.F.R. § 42.100(b). I further understand that "the broader standard serves to identify ambiguities in the claims that can then be clarified through claim amendments." Final Rule, 77 Fed. Reg. 48680, 48699 (Aug. 14, 2012).

- 98. In forming my opinions as set forth in this declaration, I have accorded all claim terms in claims 1, 3, 6-9, 11, 14-17, 19, and 21-22 in the 948 Patent their broadest reasonable interpretation, as would be understood by a person

of ordinary skill in the art at the time of the alleged invention of the alleged invention of the 948 Patent.

### IX. THE PRIOR ART

- A. Thia: Thia, A Reduced Operation Protocol Engine (ROPE) for a mulitple-layer bypass architecture (1995)<sup>6</sup>

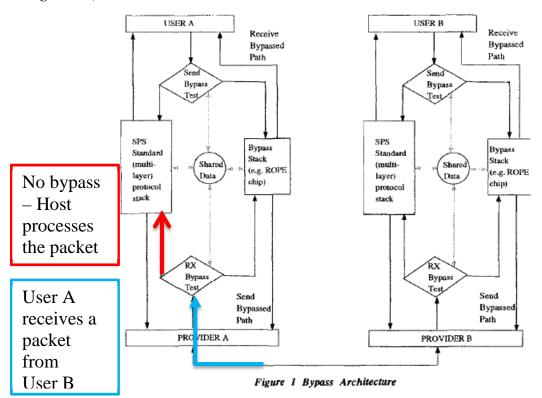

- 99. Thia describes a hardware protocol engine for fast-path data transfer, where the hardware bypasses the host protocol stack for certain packets:

Abstract - The Reduced Operation Protocol Engine (ROPE) presented here offloads critical functions of a multiple-layer protocol stack, based on the "bypass concept" of a fast path for data transfer.

Ex.1015, Thia at .001. Thia is based on the Open System Interconnect (OSI) protocol that I discussed above in Section V.A.1.

100. Thia's hardware protocol offload system compares the incoming packet headers with a template that identifies "predicted bypassable headers" (in other words, those that are in a "data transfer phase" (consecutive packets for the same connection). Thia refers to the ROPE hardware as a reduced operation protocol engine because it only handles this subset of packets. Ex.1015, Thia at

<sup>&</sup>lt;sup>6</sup> Thia was published in 1995. I understand that it is prior art because it was published before October 14, 1997, the date to which Alacritech claims priority. *See* Ex.1015, Thia.

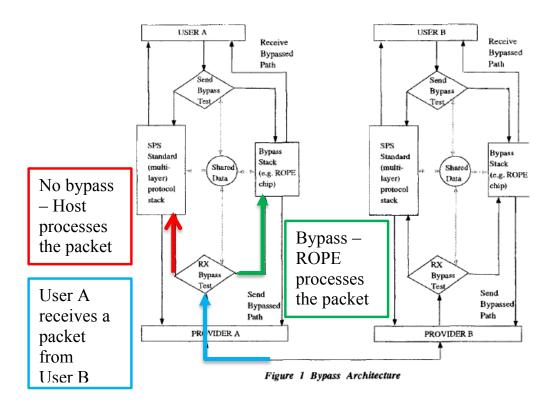

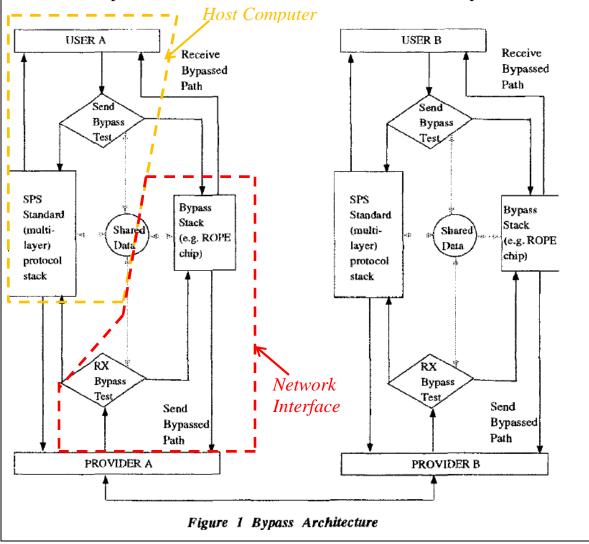

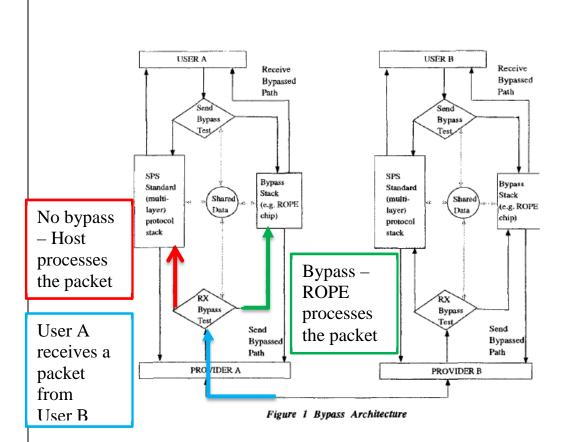

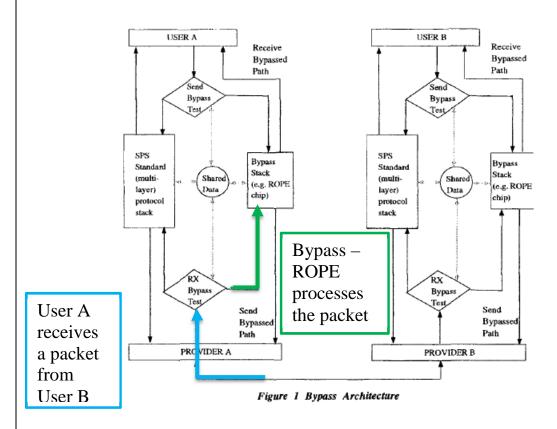

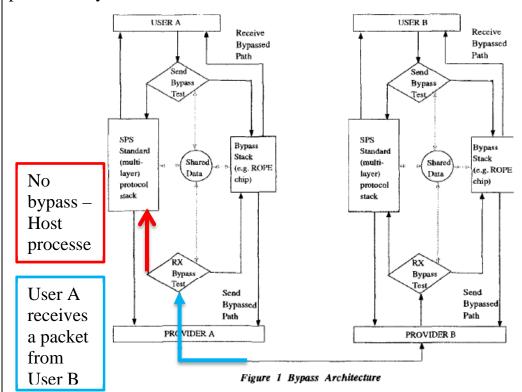

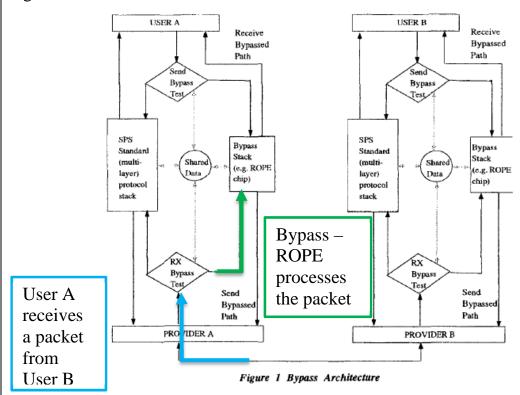

.004 ("The number of possible PDU formats in the bypass path is reduced to data transfer PDUs"). This discloses the use of a receive bypass test (RX bypass test in Figure 1) where the ROPE hardware performs all protocol processing for packets in this "data transfer phase," bypassing the standard protocol stack (SPS) (host protocol stack):

## 2.1 Bypass Architecture

Figure 1 illustrates the architecture of a bypass implementation for any standard protocol. The standard protocol stack (SPS) is the processing path taken by all PDUs [Protocol Data Units i.e. packets] during a connection without the bypass.... The receive bypass test matches the incoming PDU headers with a template that identifies the predicted bypassable headers. The bypass stack performs all the relevant protocol processing in the data transfer phase. The shared data are used to maintain state consistency between the SPS and the bypass stack, including window flow control parameters and connection identifiers.

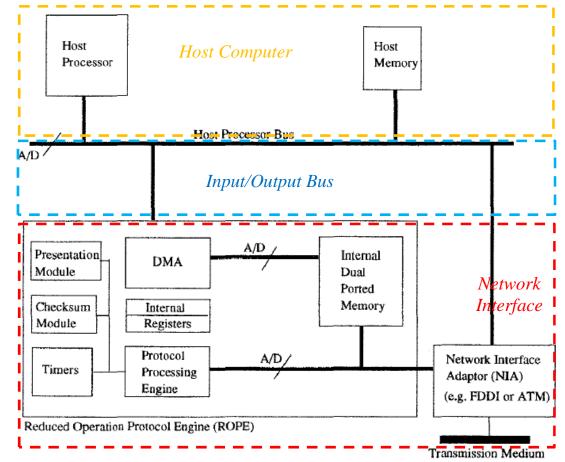

Ex.1015, Thia at .003. This "receive bypass test" is performed on the ROPE (i.e., the Network Interface Adapter). Ex.1015, Thia at .006. I've illustrated the fast and slow path processing disclosed by Thia below.

Id. at .003 (annotated).

101. Thia's receive bypass test is a generalization of Jacobson's well-known Header Prediction Algorithm" for TCP/IP, which is also described in the Tanenbaum96 and Stephens2 references discussed below. *Id.* at .002. Thia teaches that the receive bypass test ensures that the protocol bypass on the ROPE is for packets without exceptions – i.e., those in the "data transfer phase" (this is also what Stevens2 referred to as the ESTABLISHED state for TCP) and that the SPS on the host handles packets in the other phases:

A multiple-layer bypass path is a concatenation of processing procedures performed by the adjacent layers when they are simultaneously in the data transfer phase. Meanwhile, the separate

layers in the SPS [Standard Protocol Stack] path handle the other phases.

In <u>summary</u>, the separation of the bypass path offers the following advantages:

- · The processing path of data PDUs can be optimized;

- The number of possible PDU [Protocol Data Unit i.e. packet] formats in the bypass path is reduced to data transfer PDUs;

- The finite state machine of the protocol is now reduced to only the "OPEN" state, for as <u>long</u> as processing remains in the bypass path. The state of the system does not change during the entire data transfer phase and the protocol processing is reduced to ensuring reliable transfer of data across the communications network.

Id.

headers with a template that identifies the next in sequence (predicted) bypassable headers. *Id.* at .003. To be part of the data transfer, the received packets must indicate that they are for the same connection. A POSA would have understood that the headers would be parsed to identify the fields to be matched with the template. The bypass stack then "performs all the relevant protocol processing in the data transfer phase." *Id.* As I described above in Section V.A, on the receive side, this includes stripping off the headers and handing up the payload to the layer above. The bypass stack on the ROPE performs header decoding and can perform the checksum on the transport layer. *Id.* at .006.

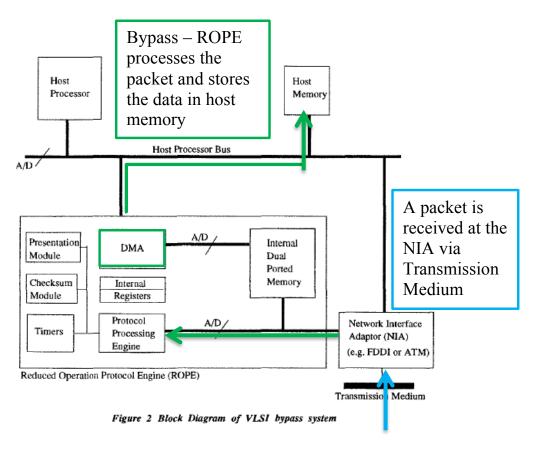

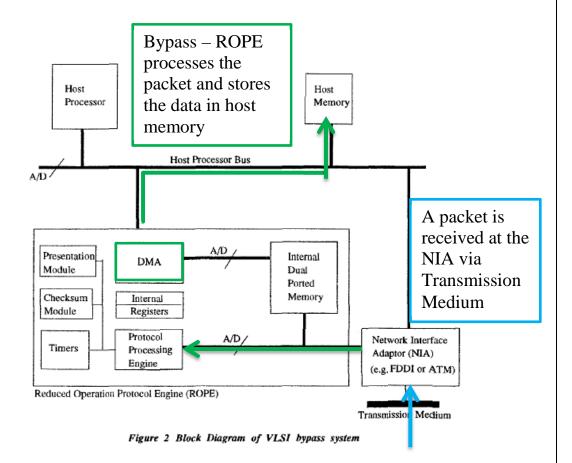

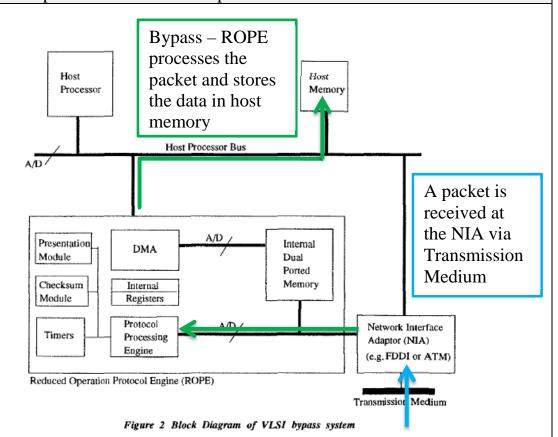

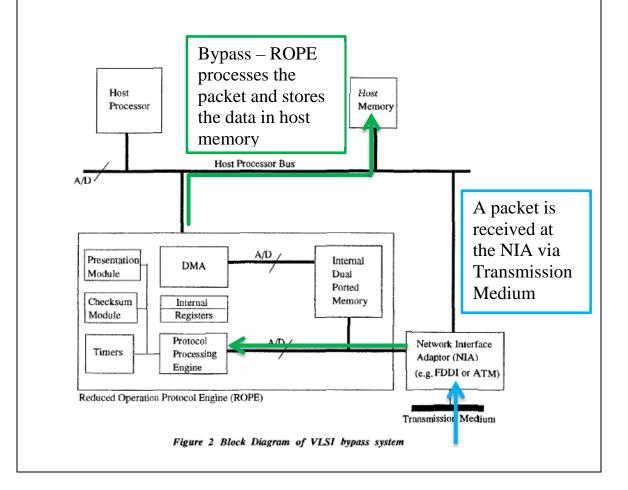

103. Thia's DMA then copies the data to Host Memory, eliminating data copying within layers. *Id.* at .007 ("Movement of data across the host bus interface are minimized by using an on-chip DMA for <u>fast block data transfer to/from the host system memory."</u>) (emphasis added). A POSA would understand that only the payload data is transferred. The headers need not be transferred because they are decoded and checked by the bypass chip. Highlighted Table 1 and Figure 2 of Thia show these functions:

| Layer                  | Procedure                                   | Bypass Chip                                                                   | Host | Per-Octet<br>(A) | Per-Packet<br>(B) | Per-Group-Of-Packets<br>Aggregated to Per-Packet<br>for bulk data transfer (B) | Remarks                                  |

|------------------------|---------------------------------------------|-------------------------------------------------------------------------------|------|------------------|-------------------|--------------------------------------------------------------------------------|------------------------------------------|

| Presentation           | Encoding                                    | х                                                                             | İ    | Х                |                   |                                                                                |                                          |

|                        | Encryption                                  | x                                                                             | Ī    | х                |                   |                                                                                |                                          |

|                        | Compression                                 | x                                                                             |      | x                |                   |                                                                                |                                          |

|                        | Context Alteration                          |                                                                               | х    |                  |                   | X                                                                              |                                          |

| Session                | Synchronization<br>Management               |                                                                               | x    |                  |                   | х                                                                              |                                          |

|                        | Token management                            |                                                                               | х    |                  |                   | х                                                                              |                                          |