## IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

| In re Patent of:  | Jentsung Lin      |                                   |

|-------------------|-------------------|-----------------------------------|

| U.S. Pat. No.:    | 7,693,002         | Attorney Docket No.:39521-0054IP1 |

| Issue Date:       | April 6, 2010     |                                   |

| Appl. Serial No.: | 11/548,132        |                                   |

| Filing Date:      | October 10, 2006  |                                   |

| Title:            | DYNAMIC WORD LINE | E DRIVERS AND DECODERS FOR        |

|                   | MEMORY ARRAYS     |                                   |

## **DECLARATION OF EDWARD G. FAETH**

I, Edward G. Faeth, of Rockville, MD, declare:

1. My name is Edward G. Faeth. I am over the age of 21, and I have personal knowledge of the facts contained herein unless otherwise indicated. I am an employee at Fish & Richardson P.C.

2. On March 27, 2018, I visited the Jefferson Building of the Library of Congress in Washington, D.C., where I previously requested a copy of the book identified below to compare the electronic copy of the book, submitted as an exhibit with this petition, with the physical copy maintained by the Library of Congress.

3. Using the Library of Congress record for APPLE-1007 ("Itoh") (Appendix A), located through the title and author of APPLE-1007, I requested a copy of CALL NUMBER TK7895.M4 I876 2001 from the library system. I compared the contents of APPLE-1007 to the physical copy provided to me by the Library of Congress and the appearance, contents, substance, and other characteristics of

APPLE-1007 appeared to be the same as the copy maintained by the Library of Congress.

1. On April 10, 2018, I again visited the Jefferson Building of the Library of Congress in Washington, D.C., where I previously requested a copy of the book identified below to compare the electronic copy of the book, submitted as an exhibit with this petition, with the physical copy maintained by the Library of Congress.

2. Using the Library of Congress record for APPLE-1009 ("Brown") (Appendix B), located through the title and author of APPLE-1009, I requested a copy of CALL NUMBER TK7868.L6 B76 2002 from the library system. I compared the contents of APPLE-1009 to the physical copy provided to me by the Library of Congress and the appearance, contents, substance, and other characteristics of APPLE-1009 appeared to be the same as the copy maintained by the Library of Congress.

I declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under 18 U.S.C. § 1001.

Date: <u>April 10, 2018</u> By: <u>/Edward G. Faeth/</u> Edward G. Faeth, Rockville, MD

2

# **APPENDIX** A

## 1. VLSI memory chip design

| LCCN              | 00068735                                                                                                                                                                          |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type of material  | Book                                                                                                                                                                              |

| Personal name     | Itoh, Kiyoo, 1941-                                                                                                                                                                |

| Main title        | VLSI memory chip design / Kiyoo Itoh.                                                                                                                                             |

| Published/Created | Berlin ; New York : Springer, 2001.                                                                                                                                               |

| Description       | xi, 495 p. : ill. ; 25 cm.                                                                                                                                                        |

| Links             | Publisher description<br>http://www.loc.gov/catdir/enhancements/fy0816/00068735-d.html<br>Table of contents only<br>http://www.loc.gov/catdir/enhancements/fy0816/00068735-t.html |

| ISBN              | 3540678204 (alk. paper)                                                                                                                                                           |

| LC classification | TK7895.M4 l876 2001                                                                                                                                                               |

| Subjects          | Semiconductor storage devicesDesign and construction.<br>Integrated circuitsVery large scale integrationDesign and construction.                                                  |

| Notes             | Includes bibliographical references (p. [473]-488) and index.                                                                                                                     |

| Series            | Springer series in advanced microelectronics ; 5                                                                                                                                  |

| Dewey class no.   | 621.39/732                                                                                                                                                                        |

| CALL NUMBER       | TK7895.M4 l876 2001<br>Copy 1                                                                                                                                                     |

| Request in        | Jefferson or Adams Building Reading Rooms                                                                                                                                         |

LIBRARY OF CONGRESS ONLINE CATALOG Library of Congress 101 Independence Ave., SE Washington, DC 20540

Questions? Ask a Librarian: https://www.loc.gov/rr/askalib/ask-contactus.html

## RONICS

rovides systematic information on manufacturing of microelectronic rchers or engineers in their fields, th as wafer processing, materials, /LSI implementation, and subsysphysics and engineering and the as research scientists.

## ss Communication

ooks/ssam/

Kiyoo Itoh

# VLSI Memory Chip Design

With 416 Figures and 26 Tables

Dr. Kiyoo Itoh Hitachi Ltd., Central Research Laboratory 1-280, Higashi-Koigakubo Kokubunii-shi Toky0185-8601 Japan e-mail: k-itoh@crl.hitachi.co.jp

#### Series Editors:

Dr. Kiyoo Itoh Hitachi Ltd., Central Research Laboratory 1-280 Higashi-Koigakubo Kokubunji-shi Tokyo 185-8601 Јарап

Professor Takayasu Sakurai Center for Collaborative Research University of Tokyo 7-22-1 Roppongi, Minato-ku, Tokyo 106-8558 Japan

Library of Congress Cataloging-in-Publication Data

Itoh, Kiyoo, 1941-VLSI memory chip design / Kiyoo Itoh. p. cm. -- (Springer series in advanced microelectronics; 5) Includes bibliographical references and index. ISBN 3540678204 (alk. paper) Semiconductor storage devices--Design and construction. 2. Integrated circuits--Very large scale integration--Design and construction. I. Title. II. Series.

TK7895.M4 I876 2001 621.39'732--dc21

00-068735

## ISSN 1437-0387

ISBN 3-540-67820-4 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of Springer Science+Business Media

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2001 Printed in Germany

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

#### Typesetting by the author.

Data conversion and hgure processing by LE-1EX Jelonek, Schmidt & Vöckler GbR, 04229 Leipzig.

Cover concept by eStudio Calmar Steinen using a background picture from Photo Studio "SONO". Courtesy of Mr. Yukio Sono, 3-18-4 Uchi-Kanda, Chiyoda-ku, Tokyo. Cover design: design & production GmbH, Heidelberg

Printed on acid-free paper SPIN: 12187942 57/3180 - 5 4 3 ance, the basic technologies peripheral circuits are descy are explained. Chapter 4 .M which strongly influences , in the chip. The relationving/sensing is explained in on-chip voltage generators tors are essential for powerapter 6 discusses subsystemmportant in providing wide S. Chapters 7 and 8 describe sizing the importance of the f lowering power-supply volnold-current reduction which

leagues and the office admi-Ohta, at Hitachi Ltd. They to finalize my work. Special inuing support and patience

Kiyoo Itoh

## Contents

| 1.  | $\mathbf{An}$ | Introd                                       | luction to Memory Chip Design                  | 1          |

|-----|---------------|----------------------------------------------|------------------------------------------------|------------|

|     | 1.1           | Intro                                        | luction                                        | 1          |

|     | 1.2           | The I                                        | nternal Organization of Memory Chips           | 3          |

|     |               | 1.2.1                                        | The Memory Cell Array                          | 3          |

|     |               | 1.2.2                                        | The Peripheral Circuit                         | 5          |

|     |               | 1.2.3                                        | The I/O Interface Circuit                      | 6          |

|     | 1.3           | 0                                            | ories of Memory Chip                           | 6          |

|     | 1.4           | Gener                                        | al Trends in DRAM Design and Technology        | 11         |

|     |               | 1.4.1                                        | The History of Memory-Cell Development         | 11         |

|     |               | 1.4.2                                        | The Basic Operation of The 1-T Cell            | 15         |

|     |               | 1.4.3                                        | Advances in DRAM Design and Technology         | 19         |

|     | 1.5           | Gener                                        | al Trends in SRAM Design and Technology        | <b>24</b>  |

|     |               | 1.5.1                                        | The History of Memory-Cell Development         | <b>24</b>  |

|     |               | 1.5.2                                        | The Basic Operation of a SRAM Cell             | 26         |

|     |               | 1.5.3                                        | Advances in SRAM Design and Technology         | 29         |

|     | 1.6           | General Trends in Non-Volatile Memory Design |                                                |            |

|     |               |                                              | echnology                                      | 31         |

|     |               | 1.6.1                                        | The History of Memory-Cell Development         | 31         |

|     |               | 1.6.2                                        | The Basic Operation of Flash Memory Cells      | <b>34</b>  |

|     |               | 1.6.3                                        | Advances in Flash-Memory Design and Technology | 46         |

| 2.  | The           | e Basio                                      | cs of RAM Design and Technology                | 49         |

|     | 2.1           | Intro                                        | luction                                        | <b>4</b> 9 |

|     | 2.2           | Devic                                        | es                                             | 49         |

| 100 |               | 2.2.1                                        | MOSFETs                                        | 49         |

|     |               | 2.2.2                                        | Capacitors                                     | 57         |

|     |               | 2.2.3                                        | Resistors                                      | 60         |

|     |               | 2.2.4                                        | Wiring and Wiring Materials                    | 61         |

|     |               | 2.2.5                                        | Silicon Substrates and CMOS Latch-Up           | 65         |

|     |               | 2.2.6                                        | Other Devices                                  | 67         |

|     | 2.3           |                                              | S Static Circuits                              |            |

|     |               | 2.3.1                                        | The dc Characteristics of an Inverter          | 68         |

|     |               | 2.3.2                                        | The ac Characteristics of an Inverter          | 70         |

|     |               | 2.3.3                                        | The Improved NMOS Static Inverter              | 74         |

| VIII |     | Contents | *                                                     |

|------|-----|----------|-------------------------------------------------------|

|      | 2.4 | NMOS     | S Dynamic Circuits                                    |

|      |     | 2.4.1    | The Dynamic Inverter                                  |

|      |     | 2.4.2    | The Bootstrap Driver                                  |

|      | 2.5 | 5 CMOS   | S Circuits                                            |

|      |     | 2.5.1    | The dc Characteristics                                |

|      |     | 2.5.2    | The ac Characteristics                                |

|      | 2.6 | Basic    | Memory Circuits                                       |

|      |     | 2.6.1    | The Inverter and the Basic Logic Gate                 |

|      |     | 2.6.2    | The Current Mirror                                    |

|      |     | 2.6.3    | The Differential Amplifier 83                         |

|      |     | 2.6.4    | The Voltage Booster                                   |

|      |     | 2.6.5    | The Level Shifter                                     |

|      |     | 2.6.6    | The Ring Oscillator 88                                |

|      |     | 2.6.7    | The Counter                                           |

|      | 2.7 | The Se   | caling Law                                            |

|      |     | 2.7.1    | Constant Electric-Field Scaling                       |

|      |     | 2.7.2    | Constant Operation-Voltage Scaling                    |

|      |     | 2.7.3    | Combined Scaling                                      |

|      | 2.8 |          | graphy                                                |

|      | 2.9 | Packag   | ging                                                  |

| 3.   | DI  | RAM C    | ircuits                                               |

|      | 3.1 |          | uction                                                |

|      |     | 3.1.1    | High-Density Technology                               |

|      |     | 3.1.2    | High-Performance Circuits 100                         |

|      | 3.2 | The ca   | atalog Specifications of the Standard DRAM 102        |

|      |     | 3.2.1    | Operational Conditions 102                            |

|      |     | 3.2.2    | Modes of Operation and Timing Specifications 105      |

|      | 3.3 | The B    | asic Configuration and Operation of the DRAM Chip 110 |

|      |     | 3.3.1    | Chip Configuration 110                                |

|      |     | 3.3.2    | Address Multiplexing 111                              |

|      | 3.4 |          | mental Chip Technologies 113                          |

|      |     | 3.4.1    | A Larger Memory Capacity and Scaled-Down Devices. 113 |

|      |     | 3.4.2    | High S/N Ratio Circuits 116                           |

|      |     | 3.4.3    | Low Power Circuits 117                                |

|      |     | 3.4.4    | Iligh-Speed Circuits                                  |

|      |     | 3.4.5    | The Multidivision of a Memory Array 128               |

|      | 3.5 |          | Iultidivided Data Line and Word Line                  |

|      |     | 3.5.1    | The Multidivided Data Line                            |

|      |     | 3.5.2    | The Multidivided Word Line                            |

|      | 3.6 |          | and Relevant Circuits                                 |

|      |     | 3.6.1    | The Address Buffer                                    |

|      |     | 3.6.2    | The Address Decoder                                   |

|      |     | 3.6.3    | The Word Driver                                       |

|      |     | 3.6.4    | The Sensing Circuit                                   |

## Contents IX

|    |      | 3.6.5 The Common I/O-Line Relevant Circuit 167              |

|----|------|-------------------------------------------------------------|

|    |      | 3.6.6 The Data-Output Buffer                                |

|    | 3.7  | Write and Relevant Circuits                                 |

|    | 3.8  | Refresh-Relevant Circuits                                   |

|    |      | 3.8.1 Refresh Schemes                                       |

|    |      | 3.8.2 The Extension of Data-Retention Time                  |

|    |      | in Active Mode                                              |

|    |      | 3.8.3 Current Reduction Circuits in Data-Retention Mode 176 |

|    | 3.9  | Redundancy Techniques 178                                   |

|    |      | 3.9.1 Issues for Large-Memory-Capacity Chips                |

|    |      | 3.9.2 Intra-Subarray Replacement Redundancy                 |

|    |      | 3.9.3 Inter-Subarray Replacement Redundancy                 |

|    |      | 3.9.4 The Repair of dc-Characteristics Faults               |

|    | 3.10 | On-Chip Testing Circuits 192                                |

| 4. | Hig  | h Signal-to-Noise Ratio                                     |

| 4. |      | AM Design and Technology                                    |

|    | 4.1  | Introduction                                                |

|    | 4.2  | Trends in High S/N Ratio Design                             |

|    | 1.2  | 4.2.1 The Signal Charge                                     |

|    |      | 4.2.2 Leakage Charge                                        |

|    |      | 4.2.3 The Soft-Error Critical Charge                        |

|    |      | 4.2.4 The Data-Line Noise Charge                            |

|    | 4.3  | Data-Line Noise Reduction                                   |

|    |      | 4.3.1 Noise Sources and Their Reduction                     |

|    |      | 4.3.2 Word-Line Drive Noise                                 |

|    |      | 4.3.3 Data-Line and Sense-Amplifier Imbalances              |

|    |      | 4.3.4 Word-Line to Data-Line Coupling Noise                 |

|    |      | 4.3.5 Data-Line Interference Noise                          |

|    |      | 4.3.6 Power-Supply Voltage Bounce                           |

|    |      | 4.3.7 Variation in the Reference Voltage                    |

|    |      | 4.3.8 Other Noises                                          |

|    | 4.4  | Summary                                                     |

| 5. | On-  | Chip Voltage Generators                                     |

|    | 5.1  | Introduction                                                |

|    | 5.2  | The Substrate-Bias Voltage $(V_{BB})$ Generator             |

|    |      | 5.2.1 The Roles of the $V_{\rm BB}$ generator               |

|    |      | 5.2.2 Basic Operation and Design Issues 256                 |

|    |      | 5.2.3 Power-On Characteristics                              |

|    |      | 5.2.4 Characteristics in the High- $V_{\rm DD}$ Region      |

|    |      | 5.2.5 The $V_{\rm BB}$ Bump                                 |

|    |      | 5.2.6 Substrate-Current Generation                          |

|    |      | 5.2.7 Triple-Well Structures                                |

|    |      | 5.2.8 Low-Power $V_{\rm BB}$ Generators                     |

| х  | С   | ontents                                       |                                                                                |

|----|-----|-----------------------------------------------|--------------------------------------------------------------------------------|

|    | 5.3 | The V                                         | Voltage Up-Converter                                                           |

|    |     | 5.3.1                                         | The Roles of the Voltage Up-Converter                                          |

|    |     | 5.3.2                                         | Design Approaches and Issues 278                                               |

|    |     | 5.3.3                                         | High Boost-Ratio Converters                                                    |

|    |     | 5.3.4                                         | Low-Power, High Supply Current Converters                                      |

|    | 5.4 | The V                                         | Oltage Down-Converter                                                          |

|    |     | 5.4.1                                         | The Roles of the Voltage Down-Converter                                        |

|    |     | 5.4.2                                         | The Negative-Feedback Converter and Design Issues 293                          |

|    |     | 5.4.3                                         | Optimum Design                                                                 |

|    |     | 5.4.4                                         | Phase Compensation                                                             |

|    |     | 5.4.5                                         | Reference-Voltage Generators                                                   |

|    |     | 5.4.6                                         | Burn-In Test Circuits                                                          |

|    |     | 5.4.7                                         | Voltage Trimming                                                               |

|    |     | 5.4.8                                         | Low-Power Circuits                                                             |

|    | 5.5 |                                               | $falf-V_{DD} Generator \qquad 332$                                             |

|    | 5.6 | Exam                                          | ples of Advanced On-Chip Voltage Generators                                    |

| 6. | Hig | h-Perf                                        | ormance Subsystem Memories                                                     |

|    | 6.1 | Introd                                        | uction                                                                         |

|    | 6.2 | Hierar                                        | chical Memory Systems 341                                                      |

|    |     | 6.2.1                                         | Memory Hierarchy                                                               |

|    |     | 6.2.2                                         | Improvements in Memory-Subsystem Performance 344                               |

|    |     | 6.2.3                                         | Memory-Chip Performance                                                        |

|    | 6.3 |                                               | ry-Subsystem Technologies                                                      |

|    |     | 6.3.1                                         | Wide-Bit I/O Chip Configurations                                               |

|    |     | 6.3.2                                         | Parallel Operation of Multidivided Arrays                                      |

|    |     | 6.3.3                                         | Multibank Interleaving                                                         |

|    |     | $\begin{array}{c} 6.3.4 \\ 6.3.5 \end{array}$ | Synchronous Operation       358         Pipeline/Prefetch Operations       362 |

|    |     | 6.3.6                                         | High-Speed Clocking Schemes                                                    |

|    |     | 6.3.7                                         | Terminated I/O Interfaces                                                      |

|    |     | 6.3.8                                         | High-Density Packaging                                                         |

|    | 6.4 |                                               | Performance Standard DRAMs                                                     |

|    | 0.1 | 6.4.1                                         | Trends in Chip Development                                                     |

|    |     | 6.4.2                                         | Synchronous DRAM                                                               |

|    |     | 6.4.3                                         | Rambus DRAM                                                                    |

|    | 6.5 | Embe                                          | dded Memories                                                                  |

| 7. | Low | -Powe                                         | er Memory Circuits                                                             |

|    | 7.1 |                                               | uction                                                                         |

|    | 7.2 |                                               | and Reduction of Power Dissipation                                             |

|    |     |                                               | AM Subsystem                                                                   |

|    |     | 7.2.1                                         | Wide-Bit I/O Chip Configuration                                                |

|    |     | 7.2.2                                         | Small Package                                                                  |

|    |     | 7.2.3                                         | The Low-Voltage Data-Bus Interface                                             |

|    |     |                                               |                                                                                |

| Contents | XI |

|----------|----|

|          |    |

|                     | 276 |

|---------------------|-----|

| verter              | 276 |

|                     | 278 |

|                     | 283 |

| Converters          | 285 |

|                     | 290 |

| Converter           | 290 |

| r and Design Issues | 293 |

|                     | 297 |

|                     | 301 |

|                     | 316 |

|                     | 323 |

|                     | 327 |

|                     | 329 |

|                     | 332 |

| • Generators        | 333 |

|                     |     |

| s                   | 339 |

|                     | 339 |

|                     | 341 |

|                     |     |

| stem Performance    | 344 |

|                     | 349 |

|                     | 354 |

| ns                  | 354 |

| ed Arrays           | 354 |

|                     | 357 |

|                     | 358 |

|                     | 362 |

|                     | 363 |

|                     | 363 |

|                     | 364 |

|                     | 365 |

|                     | 365 |

|                     | 368 |

|                     | 380 |

|                     | 383 |

|                     |     |

|                     | 389 |

|                     | 389 |

| ation               |     |

|                     | 392 |

| n                   | 393 |

|                     | 394 |

| rface               | 396 |

|                     |     |

|     | 7.3  | Sources of Power Dissipation in the RAM Chip 402 |                                           |

|-----|------|--------------------------------------------------|-------------------------------------------|

|     |      | 7.3.1                                            | Active Power Sources 402                  |

|     |      | 7.3.2                                            | Data-Retention Power Sources              |

|     | 7.4  | Low-P                                            | ower DRAM Circuits 406                    |

|     |      | 7.4.1                                            | Active Power Reduction 406                |

|     |      | 7.4.2                                            | Data-Retention Power Reduction 412        |

|     | 7.5  | Low-P                                            | ower SRAM Circuits 413                    |

|     |      | 7.5.1                                            | Active Power Reduction 413                |

|     |      | 7.5.2                                            | Data-Retention Power Reduction 423        |

| 8.  | Ult  | ra-Low                                           | -Voltage Memory Circuits 425              |

| 2.5 | 8.1  |                                                  | uction                                    |

|     | 8.2  |                                                  | Issues for Ultra-Low-Voltage RAM Circuits |

|     |      | 8.2.1                                            | Reduction of the Subthreshold Current     |

|     |      | 8.2.2                                            | Stable Memory-Cell Operation              |

|     |      | 8.2.3                                            | Suppression of, or Compensation for,      |

|     |      | 0.2.0                                            | Design Parameter Variations               |

|     |      | 8.2.4                                            | Power-Supply Standardization              |

|     | 8.3  | Ultra-l                                          | Low-Voltage DRAM Circuits                 |

|     |      | 8.3.1                                            | Gate Boosting Circuit                     |

|     |      | 8.3.2                                            | The Multi- $V_{\rm T}$ Circuit            |

|     |      | 8.3.3                                            | The Gate–Source Back-Biasing Circuit      |

|     |      | 8.3.4                                            | The Well Control Circuit                  |

|     |      | 8.3.5                                            | The Source Control Circuit                |

|     |      | 8.3.6                                            | The Well and Source Control Circuit       |

|     | 8.4  | Ultra-I                                          | Low-Voltage SRAM Circuits                 |

|     | 8.5  |                                                  | Low-Voltage SOI Circuits                  |

|     |      |                                                  |                                           |

| Ref | eren |                                                  |                                           |

| Ind | ex   |                                                  |                                           |

f data lines [3.3, 3.4]. A  $C_{\rm D}$  of 200 fF

se amplifiers in a DRAM chip [3.4]

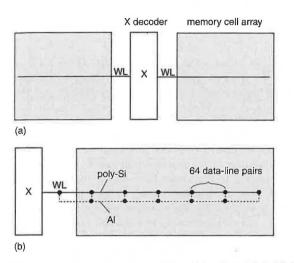

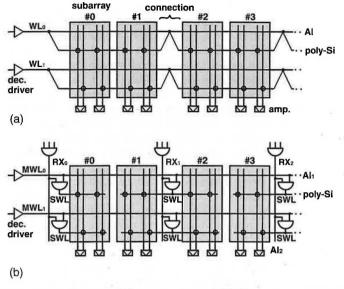

y of a word line made of a resistive r of divisions has been determined ltant area penalty. In the 64 Kb . short and the speed requirement .e, as shown in Fig. 3.40a [3.9], was , poly-Si was replaced by a lowerresistance polycide, in order to double or quadruple the number of memory cells to be driven. To further reduce the RC delay, a poly-Si or polycide word line strapped with a low-resistance aluminum line in each string of 64–128 cells [3.17], as shown in Fig. 3.40b, has been widely accepted in commercial chips since the 1 Mb generation. In the 64 Mb generation, even a hybrid division of the two types shown in Fig. 3.40 has been proposed. However, the aluminum-strapped word-line structure suffers from some drawbacks. It becomes difficult to achieve fine patterning of aluminum at a tight pitch of word lines on a hilly surface, while still connecting to the poly-Si line at the bottom, as the memory cell is miniaturized. In addition, even the word-line structure starts to create quite a large RC delay as many memory cells are connected to a word or subword line. A multidivided word-line scheme using a hierarchical word-line structure [3.18, 3.19], as shown in Fig. 3.25, solves these problems, and is discussed later in detail.

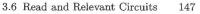

## 3.6 Read and Relevant Circuits

### 3.6.1 The Address Buffer

In the NMOS era of the 16-256 Kb generations, a differential address buffer using an on-chip reference voltage [3.14] was widely used. Since the 1 Mb

142 3. DRAM Circuits

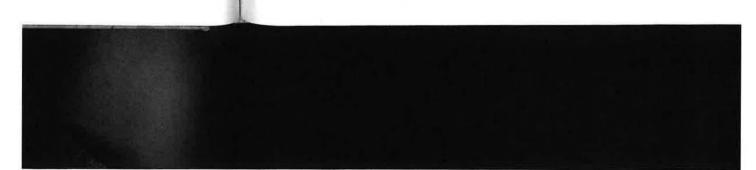

Fig. 3.41. The RAS clock buffer [3.21]

generation, various simple CMOS address buffers have been proposed. In principle, the same circuit configuration is applicable to both the row and column address buffers. Recently, however, a high-speed column address buffer has been especially important to enhance the data throughput by shortening the column address access time  $t_{AA}$ , which is dominated by the address buffer (about 40% of  $t_{AA}$  [3.20]).

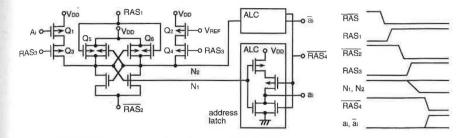

Figure 3.41 shows a typical  $\overline{\text{RAS}}$ -clock buffer [3.21] to control the row address buffers. To discriminate between the TTL logic levels of over 2.4 V or below 0.8 V for an input  $\overline{\text{RAS}}$  signal, the logical threshold voltage is adjusted to be about 1.6 V by tuning the channel-width ratios of the NMOS and the PMOS at the first input stage. A multistage CMOS circuit controls the row internal circuits, using pulses with differing polarities and delays.

Figure 3.42 shows an address buffer that features a cross-coupled differential amplifier [3.21]. It enables an almost constant speed due to a differential circuit configuration, independently of the power-supply noise. Address buffers consisting of inverters, similar to the above  $\overline{RAS}$  buffer, have also been widely accepted. In general, however, the operation of inverter-type buffers is susceptible to power-supply noise [3.20]. For example, as soon as the input logic signals to many buffers are simultaneously switched to the other logic state so that the ground  $(V_{SS})$  line voltage is instantaneously raised and maximized, the speed of each buffer is degraded, with a reduced NMOS gate-source voltage. For a 64 Mb design [3.20], a simultaneous switching of 13 address buffers caused a  $V_{\rm SS}$  noise of 0.4 V and a speed difference of 2.3 us between the inverter and cross-coupled types, although the difference depended on the quality of the  $V_{\rm SS}$  layout. In the figure, the input voltage of address Ai is compared with a reference  $V_{\text{REF}}$  (1.6 V) to discriminate between a high logic level (H) and a low logic level. The resultant differential signal developed between  $N_1$  and  $N_2$  is quickly amplified to a full  $V_{DD}$  by the crosscoupled amplifier, as a result of the application of RAS<sub>2</sub>. After that, the complementary addresses  $a_i$  and  $\overline{a}_i$  are generated by the application of  $\overline{RAS}_4$ to address latches (ALCs). Note that during standby periods (i.e. RAS: H) both  $a_i$  and  $\overline{a_i}$  are kept low and there is no current path in the buffer.

#### Fig. 3.42

Figur although address c pulses ge ATD pul as to cor sition is the I/O the tranwithout can be c amplifier

address I input

Fig. 3. buffers

Fig. 3.42. The cross-coupled address buffer [3.21]

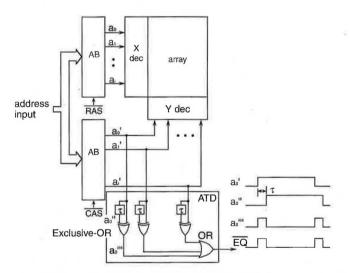

Figure 3.43 shows a typical address transition detector (ATD) [3.22], although the variations are shown in Fig. 7.18. Exclusive OR of  $a'_0$  and the address delayed by  $\tau$  generates a short pulse every  $a'_0$  transition. All the short pulses generated from all the address input transitions are summed up to one ATD pulse,  $\overline{EQ}$ . Thus, an ATD pulse is generated at any address transition so as to control internal circuits instead of external clocks. If any address transition is quickly detected by ATD and the resultant ATD signal precharges the I/O line in advance, a data line will be selected using addresses just after the transition, so that a data on the data line is outputted on the I/O line without waiting for the I/O precharging. Thus, a long I/O precharging time can be concealed. The ATD signal reduces the power dissipation of main amplifier by cutting the dc current during periods when it is not needed.

**AS**<sup>4</sup>

ffers have been proposed. In icable to both the row and co-1-speed column address buffer .ata throughput by shortening minated by the address buffer

ffer [3.21] to control the row TL logic levels of over 2.4 V or l threshold voltage is adjusted  $\iota$  ratios of the NMOS and the 2MOS circuit controls the row larities and delays.

tures a cross-coupled differenant speed due to a differential rer-supply noise. Address bufre RAS buffer, have also been ration of inverter-type buffers example, as soon as the input ly switched to the other logic is instantaneously raised and ided, with a reduced NMOS :0], a simultaneous switching 4 V and a speed difference of types, although the difference he figure, the input voltage of 1.6 V) to discriminate between ne resultant differential signal fied to a full  $V_{\rm DD}$  by the crossion of  $\overline{RAS}_2$ . After that, the ed by the application of  $\overline{RAS}_4$ standby periods (i.e.  $\overline{RAS}$ : H) crent path in the buffer.

## 144 3. DRAM Circuits

### 3.6.2 The Address Decoder

Major concerns for the address-decoder block are power dissipation, speed, and area, because the block includes a huge number of circuits and occupies quite a large segment of the chip.

There are two kinds of decoder; row decoders and column decoders. In DRAM design, unlike SRAM designs, the circuit configurations of the two are totally different. Each row decoder must be a dynamic circuit, while each column decoder can be a static circuit, as explained previously. Note that to precharge all the row decoders without any dc current path, all of the complementary addresses are fixed at a low level during a precharge period, as shown in Fig. 3.42.

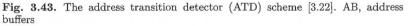

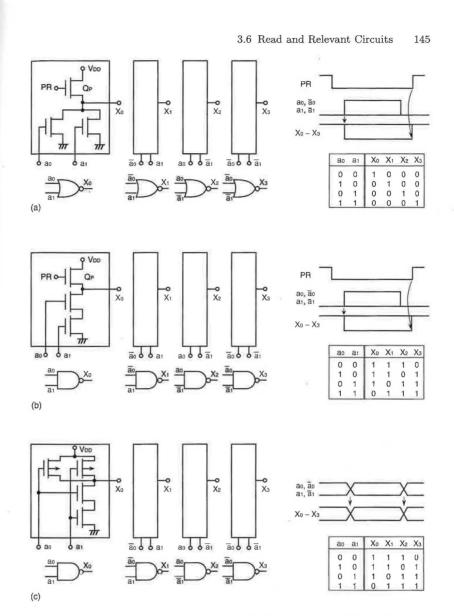

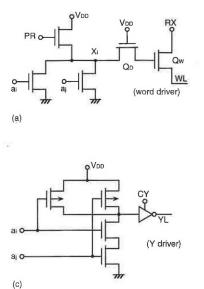

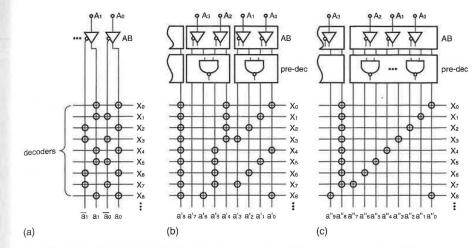

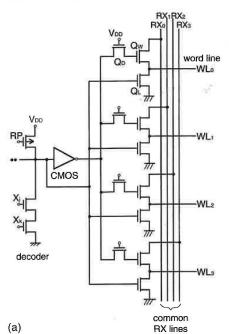

Figure 3.44 shows dynamic and static decoders, exemplified by two-bit address signals. There are two kinds of dynamic decoder in DRAM applications; NOR and NAND decoders. First, all of the output nodes  $(X_0-X_3)$ are precharged to  $V_{DD}$  by transistors  $Q_P$ , while keeping all addresses low. Then, according to the succeeding valid address signals, the output nodes are discharged or kept high. Obviously, in NOR decoders all output nodes except for a selected one are discharged, while in NAND decoders all output nodes except for a selected one are kept high. Thus, NOR decoders suffer from a drawback of the large charging and discharging power. The power increases with memory capacity, because an increased number of the nodes - for example, a few thousands, for multimegabit DRAMs - is involved. On the other hand, in NAND decoders only one node is discharged or charged up, independently of memory capacity. NAND decoders, however, suffer the drawback of a slower speed, because the node is discharged by serially connected (i.e. stacked) transistors. The number of stacked transistors is also limited by the body effect of the transistor. Static NAND decoders for the column are simple, as shown in Fig. 3.44c.

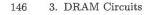

Figure 3.45 shows applications of dynamic decoders to the row and static decoders to the column. In dynamic decoders, a word line WL is activated by an RX pulse that is applied after the decoder output Xi has been settled. In the selected decoder, the  $Q_W$  gate-drain (i.e. RX terminal) capacitance  $C_{GD}$ is large, because the  $Q_W$  gate stays at the high level of  $V_{DD} - V_T$ . Thus, an RX pulse positively going from 0 V to  $V_{DD}$  can boost the  $Q_W$  gate voltage. The boost ratio is large, because a diode  $Q_D$  isolates the  $Q_W$  gate from the node Xi capacitance. Due to the resulting boosted gate voltage, to higher than  $V_{\rm DD} + V_{\rm T}$ , the word line is quickly driven to  $V_{\rm DD}$ . In the non-selected decoders, an RX pulse application never raises the Q<sub>W</sub> gate voltages, since the gate voltages are 0 V and thus their  $C_{GD}$  values are almost zero. For NOR decoders, even the heavily capacitive Q<sub>W</sub> gate is quickly discharged by at least one transistor of the decoder. For NAND decoders, however, to accomplish rapid decoding, Q<sub>W</sub> is driven with the help of a small CMOS inverter, whose input capacitance is small enough to be quickly driven even by stacked transistors. Despite the area penalty, the inverter added to each

PR

PRC

a

deco reaso ders

Fig. 3.44. Decoders and operations, exemplified by two address bits [3.4]. (a) Dynamic NOR; (b) dynamic NAND; (c) static NAND

decoder never increases the decoder power because it is a CMOS inverter. The reason why NMOS NOR decoders have been replaced by CMOS NAND decoders since the 1 Mb generation is just to reduce the ever-increasing decoder

ower dissipation, speed, of circuits and occupies

and column decoders. In onfigurations of the two namic circuit, while each ed previously. Note that current path, all of the uring a precharge period,

, exemplified by two-bit .ecoder in DRAM applie output nodes  $(X_0-X_3)$ seping all addresses low. gnals, the output nodes ecoders all output nodes AND decoders all output 1s, NOR decoders suffer rging power. The power sed number of the nodes )RAMs - is involved. On is discharged or charged ders, however, suffer the scharged by serially conacked transistors is also NAND decoders for the

lers to the row and static d line WL is activated by ıt Xi has been settled. In rminal) capacitance  $C_{\rm GD}$ el of  $V_{\rm DD} - V_{\rm T}$ . Thus, an ost the Q<sub>W</sub> gate voltage. es the Qw gate from the l gate voltage, to higher  $V_{\rm DD}$ . In the non-selected Q<sub>W</sub> gate voltages, since ues are almost zero. For ate is quickly discharged JD decoders, however, to e help of a small CMOS to be quickly driven even ie inverter added to each

Fig. 3.45. Applications of decoders to word and column drivers [3.4]. (a) Dynamic NOR; (b) dynamic NAND; (c) static NAND

(b)

Voo

Qw WL

(word driver)

power. Even for a small memory capacity chip of 1 Mb, CMOS NAND decoders have reduced the decoder power down to 4% of that needed for NMOS NOR decoders [3.7, 3.23] as shown in Fig. 3.17. However, to improve the performance of CMOS NAND decoders further, it is essential to reduce the number of stacked transistors. This is realized by predecoding schemes [3.21], as follows.

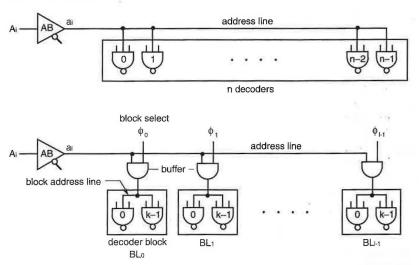

A predecoding scheme achieves a faster decoding and area reduction of a decoder while reducing the number of stacked transistor in a CMOS NAND decoder. In addition, it reduces the input capacitance and the necessary address input lines of the decoder. Figure 3.46 compares predecoding schemes [3.4]. Direct decoding, 2 bit predecoding, and 3 bit predecoding are shown in Figs. 3.46a-c, respectively. A circle in the figures denotes a transistor connection. For example, when a high level is applied to  $a_0$  and  $a_1$ in Fig. 3.46a, decoders  $X_0$ ,  $X_4$ , and  $X_8$  are selected as a result of NAND decoding. Each 2 bit predecoder can select one of four address input lines coming to the decoders by using two sets of complementary addresses from two address buffers, while each 3 bit predecoder can select one of eight address input lines by using three sets of complementary addresses. Here, let us cite an example of a total external address bits of 6 bits ( $A_0-A_5$ ). The numbers of address lines to the decoders for direct decoding, 2 bit decoding, and 3 bit decoding are 12, 12, and 16, respectively. The numbers of transistors

Fig. 3.46. Predecoding [3.4]. (a) no predecoding; (b) 2-bit predecoding; (c) 3-bit predecoding

connected to each address line are 32, 16, and 8, and the numbers of transistors consisting of each decoder are six, three, and two, in the same order. Hence, the predecoding schemes achieve a higher speed with reduction of the address-line capacitance and the number of stacked transistors needed for each NAND decoder, given an acceptable number of address lines. They also reduce the decoder area. The resulting improvement in speed offsets an additional delay caused by the predecoders. Here, predecoding schemes with more than 4 bits are not practical because of a rapid increase in the number of address lines.

Figure 3.47 shows a reduction in the delay of an address line [3.24], which is an example of the buffer insertions shown in Fig. 3.20. Quite a long delay time is developed, despite the aluminum address line, because the line becomes resistive and capacitive due to fine patterning, and is loaded by the distributed gate capacitances of the decoder transistors, as shown in Fig. 3.47a. However, the delay is reduced by the multidivided decoder shown in Fig. 3.47b. The resulting block decoder is driven by a buffer. Each block is constructed so as to correspond to a subarray and only one block is selectively activated by the subarray activation pulse  $\Phi_{i}$ .

## 3.6.3 The Word Driver

A word driver needs to be designed carefully – more so than a column driver – because its load has the following unique features:

1. A Boosted Word Voltage. The need for a boosted word voltage, for full write and read operations, means that row decoders and word drivers

1 drivers [3.4]. (a) Dynamic

(word driver)

/DD

Mb, CMOS NAND decoof that needed for NMOS However, to improve the is essential to reduce the edecoding schemes [3.21],

ling and area reduction d transistor in a CMOS apacitance and the neces-46 compares predecoding and 3 bit predecoding are are figures denotes a tranis applied to  $a_0$  and  $a_1$ ed as a result of NAND four address input lines lementary addresses from select one of eight address ddresses. Here, let us cite ts (A<sub>0</sub>-A<sub>5</sub>). The numbers ing, 2 bit decoding, and are numbers of transistors

## 148 3. DRAM Circuits

Fig. 3.47. The delay reduction of an address line running on decoders (upper) by insertion of buffers (lower) [3.4, 3.24]

have complicated designs. On the other hand, column-relevant circuits, such as column decoders and drivers, do not need any boosting. Even without boosting, an amplified signal voltage from a data line can be transmitted to the I/O line, and a data-input voltage of  $V_{\rm DD}$  can be fully transmitted from the I/O line to the data line with the help of the CMOS sense amplifier.

- 2. A Large Word-Line Capacitance and Resistance. The electrical characteristics of a word line differ from those of column line YL in the shared Y decoder scheme. Word-line capacitance is quite heavy, because of connections with many memory cells. On the other hand, column-line capacitance is light, because a small number of transistors, equal to the number of data-line divisions (i.e. q in Fig. 3.14), are connected to a YL line. Thus, a larger word driver is needed. As for line resistance, there is also a large difference between the two. A word line made of poly-Si or polycide is resistive for a folded data-line cell, while a column line is made of aluminum.

- 3. Loss of Stored Information. If the stored charges of a non-selected cell are allowed to escape to a data line through the transfer transistor, the refresh time or S/N ratio of the cell is degraded, as discussed in Chap. 4. Thus, noise suppression is essential on non-selected word lines. Moreover, to avoid loss of stored information, data-line precharging must be started after completely turning off the word pulse. Such considerations are not

#### 3.6 Read and Relevant Circuits 149

ning on decoders (upper) by

, column-relevant circuits, need any boosting. Even from a data line can be roltage of  $V_{\rm DD}$  can be fully vith the help of the CMOS

*ice.* The electrical characlumn line YL in the shais quite heavy, because of e other hand, column-line of transistors, equal to the 4), are connected to a YL for line resistance, there is rd line made of poly-Si or while a column line is made

rges of a non-selected cell the transfer transistor, the d, as discussed in Chap. 4. teted word lines. Moreover, recharging must be started uch considerations are not needed for the column. Here, an explanation of the column driver is omitted in what follows, because the driver is almost the same as in Fig. 3.45.

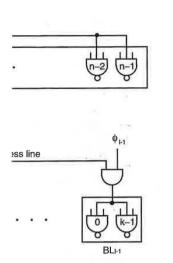

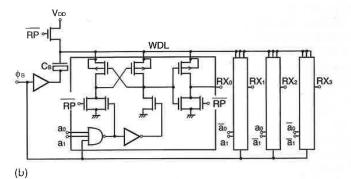

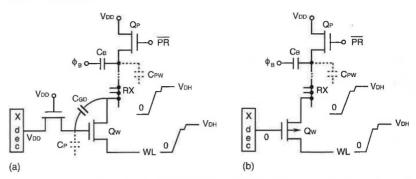

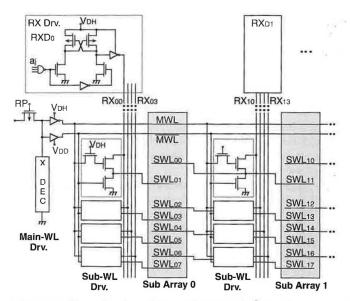

A Basic Word Driver. Figure 3.48 shows the basic unit of conventional word drivers [3.13, 3.21, 3.23]. Each word line is divided into two, to reduce word-line delay (see Fig. 3.40), and the resulting divided word line has its own word driver, Q<sub>W</sub>. Since a CMOS NAND decoder cannot be placed at a tight word-line pitch, it is shared with two sets (left and right) of four word drivers, although only the right section is shown in the figure. Address signals  $X_i$  and  $X_k$  are inputted from 2-bit predecoders to the decoder. Each of the four word drivers selected by the decoder is selectively driven by decoded row select lines RX  $(RX_0-RX_3)$ , enabling the corresponding word line to be driven. The RX drivers in Fig. 3.48b provide a boost word voltage to one of RXs as a result of two-address bit (a<sub>0</sub>, a<sub>1</sub>) decoding, as follows. At first, node WDL is precharged almost to  $V_{DD}$  during the precharge period (i.e.  $\overline{RP}$ : H) and all address signals and thus all RX lines are fixed at 0 V. When the addresses have been valid after starting activation with  $\overline{RP}$ : L, a clock  $\Phi_{\rm B}$  generated by the RAS buffer is applied, so that only one selected RX line is driven at a high enough voltage, boosted by  $C_{\rm B}$ .

The latch transistor Q<sub>L</sub> in the word driver suppresses noise on each nonselected word line while fixing the word line at 0 V as follows. During precharge period all of the non-selected word lines are fixed at 0 V because the QLs are turned on. When one set of four word lines is selected by a decoder, the gate voltages of the corresponding four  $Q_{\rm L}s$  are changed from  $V_{\rm DD}$  to 0 V and the  $Q_L s$  are thus cut off. At this moment, the gate voltages of the corresponding four word-driver transistors Q<sub>W</sub> are increased from 0V to  $V_{\rm DD} - V_{\rm T}$ . During this process, the word lines are not at any floating voltage that easily couples noise to the lines, because the four word lines  $WL_0-WL_3$ are fixed at the voltages (i.e. 0 V) of RX<sub>0</sub>-RX<sub>3</sub> through the respective Q<sub>W</sub>s. After that, for example,  $RX_0$  is selected and a  $V_{DH}$  pulse is sent to  $WL_0$ , fixing the remaining non-selected word lines at 0 V. Note that all of the word lines belonging to the non-selected decoders continue to be fixed at 0 V, because the Q<sub>L</sub>s are turned on. Thus, the noise coupled to each non-selected word line, even during signal amplifications performed at a large voltage swing of  $V_{\rm DD}$ or a half- $V_{\rm DD}$  on data lines, can be sufficiently suppressed. To further reduce noise on the word lines, another scheme of an additional transistor, which is controlled by address signals, on each word line has been proposed [3.25].

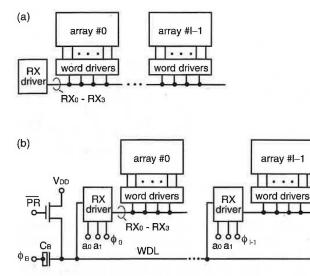

High-speed driving of the RX line is also important, because a long delay is developed by the heavy loading of the large  $Q_Ws$  and the long RX line running along a memory array. An RX driver placed at the end of the subarrays in Fig. 3.49a increases the line delay. However, a RX driver for each subarray in Fig. 3.49b [3.26], which is similar to the scheme in Fig. 3.47, shortens the delay. In this scheme, only one subarray is selected by the address signals and a subarray selection signal  $\Phi_i$ . The node WDL of the RX line in Fig. 3.48 corresponds to a line WDL that is common to a number of subarrays in

## 150 3. DRAM Circuits

Fig. 3.48. The configuration of word drivers and relevant circuits [3.4, 3.13, 3.21, 3.23]. (a) Word drivers; (b) RX drivers

Fig. 3.49b. As soon as  $\overline{\text{RAS}}$  activation starts, the heavily capacitive WDL line is boosted. After that, the addresses are valid and a subarray is thus selected so that a  $V_{\text{DH}}$  pulse is applied to a common RX line belonging to the subarray. Consequently, the boosting time of the WDL line can be concealed and the RX line that the RX driver must drive is shortened to one subarray. Thus, the driving speed is improved.

22

Fig. 3.49. Driving schemes of RX lines [3.4, 3.26]. (a) Direct driving of RX lines; (b) selective driving of multidivided RX lines

The Voltage-Stress Relaxed Word Driver. This is the word driver that must operate at the highest voltage in a DRAM chip. Therefore, many circuits have been proposed to relax the voltage stress applied at normal and/or burnin tst operations. They are categorized as the use of PMOS transistor in the word driver instead of NMOS transistor, the changing of the boost ratio according to  $V_{\rm DD}$ , and the use of a well-regulated boosted dc voltage.

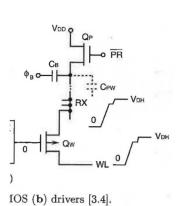

The PMOS Output Transistor [3.4]. The stress voltages applied to the worddriver output transistor are high, because the word-line voltage must be higher than  $V_{\rm DD} + V_{\rm TM}$  (where  $V_{\rm TM}$  is the threshold voltage of the memorycell transistor). However, the PMOS transistor can relax the voltage stress, ensuring high reliability, as follows. For the NMOS transistor in Fig. 3.50a, in order that an increased voltage  $V_{\rm DH}$  (>  $V_{\rm DD} + V_{\rm TM}$ ) boosted by  $C_{\rm B}$  at the drain (i.e. RX) is available at the source (i.e. word line), the gate voltage must be boosted to a level that is somewhat higher than  $V_{\rm DH} + V_{\rm TD}$  by utilizing  $C_{GD}$ . Here,  $V_{TD}$  is threshold voltage of the output transistor, which is usually smaller than  $V_{\rm TM}$  due to the narrow channel effect, and so on. This dual boosting raises the gate voltage to a considerably high voltage. The PMOS output transistor in Fig. 3.50b does not need dual boosting, since the activation is performed only by lowering the gate voltage from  $V_{\rm DH}$  to 0 V. Hence, the PMOS transistor reduces the gate voltage by at least  $V_{\rm TD}$ . In actual practice, the difference in gate voltage between the PMOS and NMOS transistors becomes larger, due to variations in the boost ratio at the

rs and relevant circuits

e heavily capacitive WDL id and a subarray is thus n RX line belonging to the VDL line can be concealed shortened to one subarray. 152 3. DRAM Circuits

Fig. 3.50. Word boosting for NMOS (a) and PMOS (b) drivers [3.4].

NMOS transistor caused by variations in the  $V_{\rm DD}$  and fabrication-process. The PMOS transistor may allow the gate-source voltage to be large enough to achieve a faster speed despite the lower conductance of the PMOS, compared to the NMOS transistor, in which the gate-source voltage is usually insufficient. Moreover, for lower- $V_{\rm DD}$  operation, the boost ratio must be larger, since there is a minimal threshold voltage for  $V_{\rm TD}$  to prevent a degradation of the  $V_{\rm DH}$  level caused by a subthreshold current; this is discussed in Chap 8. Thus, the PMOS transistor has been widely used instead of the NMOS transistor.

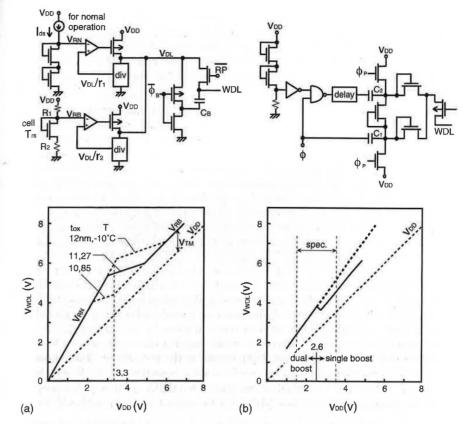

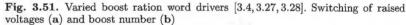

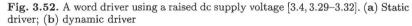

The Varied Boost-Ratio Driver. There are some operating modes in which MOS devices must not break down even when the operating voltage varies widely. These are the burn-in test mode, which ensures device reliability by applying an increased voltage, and battery operations, which require a wide voltage margin. Figure 3.51a shows a word driver for boosting a well-regulated low-voltage  $V_{\rm DL}$ , which is lowered from  $V_{\rm DD}$  (= 3.3 V) using an on-chip voltage down-converter [3.27]. The node WDL, which corresponds to WDL in Figs. 3.48 and 3.49, is boosted by activating  $\overline{\Phi}_{\rm B}$  to a low level after it has been precharged to  $V_{\rm DL}$ . An excessively high stress voltage is applied to devices in the burn-in test mode, since the boost ratio is almost constant. A voltage down-converter dedicated to the test mode relaxes the stress voltage in a high-voltage region as follows. The reference voltage  $V_{\rm RN}$  increases when  $V_{\rm DD}$  is increased. Eventually, however, it is clamped at a voltage of two MOSdiode drops and thus  $V_{\rm DL}$  becomes equal to  $r_1 V_{\rm RN}$ . Here,  $r_1$  is a resistance division ratio. Although  $V_{DL}$  increases slightly with  $V_{DD}$  because of a slight increase in the diode drops caused by the increased diode current,  $V_{\rm DL}$  is determined in turn by the other voltage down-converter for the burn-in mode. The converter generates a boosted voltage, monitoring the threshold voltage  $V_{\rm TM}$  of the memory-cell transistor as follows. The input voltage  $V_{\rm RB}$  of the comparator is given by

$V_{DD}$  and fabrication-process. ce voltage to be large enough to stance of the PMOS, compared surce voltage is usually insuffioost ratio must be larger, since o prevent a degradation of the is is discussed in Chap 8. Thus, stead of the NMOS transistor.

me operating modes in which n the operating voltage varies sh ensures device reliability by erations, which require a wide er for boosting a well-regulated (= 3.3 V) using an on-chip L, which corresponds to WDL ing  $\overline{\Phi}_{\rm B}$  to a low level after it igh stress voltage is applied to oost ratio is almost constant. mode relaxes the stress voltage ce voltage  $V_{\rm RN}$  increases when nped at a voltage of two MOS- $_{1}V_{\rm RN}$ . Here,  $r_1$  is a resistance ' with  $V_{\rm DD}$  because of a slight creased diode current,  $V_{DL}$  is :onverter for the burn-in mode. nitoring the threshold voltage The input voltage  $V_{\rm RB}$  of the

$$V_{\rm RB} = \frac{R_2}{R_1 + R_2} \left\{ V_{\rm DD} + \frac{R_1 + R_2}{R_2} V_{\rm TM} \right\}$$

:  $V_{\rm WDL} = BV_{\rm DL} = B(r_2 V_{\rm RB}) ,$

where  $V_{\rm DD} \gg V_{\rm TM}, r_2$  is a resistance division ratio, and B is a boost ratio. Hence,

## $V_{\rm WDL} = V_{\rm DD} + r_2 B V_{\rm TM}$ ,

for  $Br_2R_2/(R_1 + R_2) = 1$ . An additional voltage  $r_2BV_{\rm TM}$  is thus  $V_{\rm TM}$  for  $r_2B = 1$ , which minimizes the necessary boosted voltage. The boosted word voltage  $V_{\rm WDL}$  can track variations of  $V_{\rm TM}$  because a memory-cell transistor is used.

Figure 3.51b shows a voltage up-converter for a battery operation [3.28]. It features dual boosting in the low- $V_{\rm DD}$  region, but single boosting in the

## 154 3. DRAM Circuits

high- $V_{\rm DD}$  region. Thus, a raised S/N ratio even in the low- $V_{\rm DD}$  region, and the suppression of an excessive stress voltage in the high- $V_{\rm DD}$  region are obtained. This is essential to ensure the wide operational range of  $V_{\rm DD} = 2.6 \pm 1$  V that is inherent in battery operations. A voltage up-converter [3.29] described in Chap. 5 is a variation of this concept, in which the boost ratio is almost continuously changed over a wide range of  $V_{\rm DD}$  values.

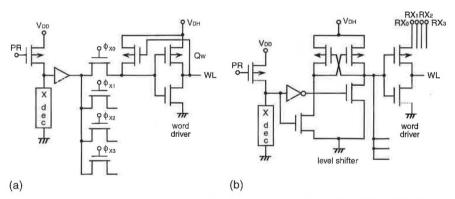

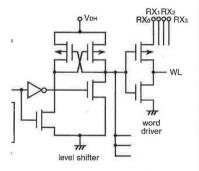

The Raised dc Supply-Voltage Driver [3.29-3.32]. A quasi-static supplyvoltage  $(V_{\text{DH}})$  generator, discussed in Chap. 5, would not only minimize the stress voltage to devices, but also enable fast operation, as follows. Figure 3.52a shows a word driver using the dc power supply  $V_{\rm DH}$ . One decoder is shared with four word lines through transistors controlled by the decoded signals  $\Phi_{X0} - \Phi_{X3}$ . At the beginning of activation, the non-selected three of the four signals, which were all at  $V_{\rm DD}$ , go down to 0 V while the remaining selected one goes to  $V_{\rm DD}$ . After that, the decoder output goes down to 0 V and the selected PMOS word transistor is thus turned on, with a change in the gate voltage from  $V_{\rm DH}$  to 0 V, so that the word line is activated at  $V_{\rm DH}$ . During this process, the remaining three word lines are latched at 0 V. This driver eliminates the need to drive a heavily capacitive RX line and thus eventually realizes a higher speed, although it needs a little additional time to ensure the sequence of the enabling decoder after enabling  $\Phi_{Xi}$ . Figure 3.52b shows the other word driver. A decoder and a level shifter are both shared with four word drivers. The decoder function given by  $\Phi_{Xi}$  in Fig. 3.52a is replaced by a decoded RX scheme, in which each RX driver comprises a level shifter and an inverter (see Fig. 3.54), similar to the word driver. The timing requirement between the application of RX and the enabling of the decoder is relaxed, permitting even an advanced application of RX. Without a boosting effect, which is available at the NMOS word transistor combined with a MOS-

(b) Fig. 3.18 diod is du The ved rema show word is be num in th incre ( conc sche: subv  $\operatorname{cont}$ activ  $RX_1$ the : poly a hu

drive

(a)

dec.

drive

in the low- $V_{\rm DD}$  region, and the high- $V_{\rm DD}$  region are obtained. range of  $V_{\rm DD} = 2.6 \pm 1 \,\mathrm{V}$  that >-converter [3.29] described in ich the boost ratio is almost > values.

3.32]. A quasi-static supply-5, would not only minimize fast operation, as follows. Fiwer supply  $V_{\rm DH}$ . One decoder tors controlled by the decoded ion, the non-selected three of vn to 0 V while the remaining der output goes down to 0 V us turned on, with a change the word line is activated at word lines are latched at 0 V. ly capacitive RX line and thus eeds a little additional time to er enabling  $\Phi_{Xi}$ . Figure 3.52b , level shifter are both shared given by  $\Phi_{Xi}$  in Fig. 3.52a is ch RX driver comprises a level o the word driver. The timing the enabling of the decoder is on of RX. Without a boosting nsistor combined with a MOS-

oltage [3.4, 3.29–3.32]. (a) Static

Fig. 3.53. The concept behing partial activation of a multidivided word line [3.18, 3.19, 3.33]. (a) No division; (b) multidivision

diode shown in Fig. 3.48, an increased word voltage is quickly outputted. This is due to the use of a  $V_{\rm DH}$  level shifter.

The Reduction of Word-Line Delay. Even if word-driver speed is improved by using a PMOS transistor, the need to reduce a large word-line delay remains. Although the aluminum-strapped poly-Si or polycide word line, as shown in Fig. 3.53a, has been popular since the 1 Mb generation, a large RC word-line delay has been prominent in the 64 Mb generation and beyond. This is because of the ever-finer and longer aluminum line and the ever-increasing number of memory cells connected to a word line. Unfortunately, an increase in the number of word-line divisions causes an area penalty, with a resulting increased number of word drivers.

One solution is the hierarchical word-line structure [3.18, 3.19, 3.33], as conceptually shown in Fig. 3.53b. This is an example of the delay reduction scheme in Fig. 3.19d. One word line is divided into several by the small subword-line (SWL) drivers. All of the subword lines in a row are commonly controlled by a main word line (MWL). Therefore, they are simultaneously activated by selecting a main word line and all of the row select lines (RX<sub>0</sub>, RX<sub>1</sub>, etc.). The choice of aluminum lines for MWL and RX would improve the speed of the simple aluminum strapping in Fig. 3.53a, despite poly-Si or polycide subword lines. In simple strapping, a word line is heavily loaded with a huge number of memory cells in a row. The resulting heavy capacitance

## 156 3. DRAM Circuits

develops a long delay even on a low-resistance aluminum line. In this case the total delay is approximately the sum of a large MWL delay and the subwordline delay. On the other hand, in the hierarchical structure a main word line is loaded by only quite a small number of AND logic gates, which is the same as the number of word-line divisions. Considering that the number of memory cells connected to one subword line ranges from 256 to 512, the loading for the main word line is quite light, which enables an extremely small delay compared with the subword-line delay. An RX line also enables a small delay because of the aluminum material. The delay could be further shortened if it is driven by a RX driver located at each data-line division. Eventually, the total delay of the hierarchical structure is almost confined to the subword-line delay. Thus, the delay is less than that for simple strapping.

Figure 3.54 shows an actual hierarchical structure applied to a 256 Mb chip [3.18, 3.19, 3.33]. It relaxes the MWL pitch to one-quarter so that aluminum wiring is enabled even on the top surface of the substrate, and it allows SWL drivers to be placed alternately to meet the tight word-line layout pitch. Eight-row word lines, each of which is divided into a number of subword lines (SWL<sub>00</sub>,  $\overline{SWL}_{10}, \ldots$ ), are controlled by a set of complimentary main word lines (MWL, MWL), which are driven by a row decoder and a set of word drivers. One set of four SWL drivers is located at each end of each subarray. One of four SWL drivers is activated by one of the decoded RX lines from a RX driver. The full use of NMOS transistors realizes a small

Fig. 3.54. Hierarchical word-line architecture [3.18, 3.19]

# **APPENDIX B**

## 1. Fundamentals of digital logic with Verilog design

| LCCN                  | 2002071439                                                                                                                          |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| Type of material Book |                                                                                                                                     |  |

| Personal name         | Brown, Stephen D.                                                                                                                   |  |

| Main title            | Fundamentals of digital logic with Verilog design / Stephen Brown and Zvonko Vranesic.                                              |  |

| Edition               | 1st ed.                                                                                                                             |  |

| Published/Created     | Boston : McGraw-Hill, c2003.                                                                                                        |  |

| Description           | xx, 844 p. : ill. ; 25 cm. + 1 CD-ROM (4 3/4 in.)                                                                                   |  |

| Links                 | Table of contents only http://www.loc.gov/catdir/enhancements/fy0702/2002071439-t.html                                              |  |

| ISBN                  | 0072823151 (alk. paper)                                                                                                             |  |

| LC classification     | TK7868.L6 B76 2003                                                                                                                  |  |

| Related names         | Vranesic, Zvonko G.                                                                                                                 |  |

| Subjects              | Logic circuitsDesign and constructionData processing.<br>Verilog (Computer hardware description language)<br>Computer-aided design. |  |

| Notes                 | Includes bibliographical references and index.                                                                                      |  |

| Series                | McGraw-Hill series in electrical and computer engineering                                                                           |  |

| Dewey class no.       | 621.39/2                                                                                                                            |  |

| CALL NUMBER           | TK7868.L6 B76 2002 FT MEADE<br>Copy 1                                                                                               |  |

| Request in            | Machine Readable Collections - STORED OFFSITE                                                                                       |  |

| CALL NUMBER           | TK7868.L6 B76 2003 FT MEADE<br>Copy 2                                                                                               |  |

| Request in            | Machine Readable Collections - STORED OFFSITE                                                                                       |  |

LIBRARY OF CONGRESS ONLINE CATALOG Library of Congress 101 Independence Ave., SE Washington, DC 20540

Questions? Ask a Librarian: https://www.loc.gov/rr/askalib/ask-contactus.html

## Fundamentals of Digital Logic with Verilog Design

## **Stephen Brown and Zvonko Vranesic**

Department of Electrical and Computer Engineering University of Toronto

BostonBurr Ridge, ILDubuque, IAMadison, WINew YorkSan FranciscoSt. LouisBangkokBogotáCaracasKuala LumpurLisbonLondonMadridMexico CityMilanMontrealNew DelhiSantiagoSeoulSingaporeSydneyTaipeiToronto

## McGraw-Hill Higher Education 👷

A Division of The McGraw-Hill Companies

FUNDAMENTALS OF DIGITAL LOGIC WITH VERILOG DESIGN

Published by McGraw-Hill, a business unit of The McGraw-Hill Companies, Inc., 1221 Avenue of the Americas, New York, NY 10020. Copyright © 2003 by The McGraw-Hill Companies, Inc. All rights reserved. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written consent of The McGraw-Hill Companies, Inc., including, but not limited to, in any network or other electronic storage or transmission, or broadcast for distance learning.

Some ancillaries, including electronic and print components, may not be available to customers outside the United States.

This book is printed on acid-free paper.

International

1 2 3 4 5 6 7 8 9 0 QPF/QPF 0 9 8 7 6 5 4 3 2

Domestic

1 2 3 4 5 6 7 8 9 0 QPF/QPF 0 9 8 7 6 5 4 3 2

ISBN 0-07-282315-1 ISBN 0-07-121322-8 (ISE)

Publisher: Elizabeth A. Jones Senior sponsoring editor: Carlise Paulson Administrative assistant: Michaela M. Graham Executive marketing manager: John Wannemacher Senior project manager: John Wannemacher Production supervisor: Kara Kudronowicz Lead media project manager: Judi David Senior media technology producer: Phillip Meek Coordinator of freelance design: Michelle D. Whitaker Cover designer: Rokusek Design Cover image: Stephen Brown and Zvonko Vranesic Senior photo research coordinator: Lori Hancock Compositor: Techsetters, Inc. Typeface: 10/12 Times Roman Printer: Quebecor World Fairfield, PA

#### Library of Congress Cataloging-in-Publication Data

Brown, Stephen D.

Fundamentals of digital logic with Verilog design / Stephen D. Brown, Zvonko G. Vranesic.—1st ed. p. cm. (McGraw-Hill Series in electrical and computer engineering)

Includes index.

ISBN 0-07-282315-1

1. Logic circuits—Design and construction—Data processing. 2. Verilog (Computer hardware description language). 3. Computer-aided design. I. Vranesic, Zvonko G II. Title. III. Series.

TK7868.L6 B76 2003 621.39'2—dc21

2002071439 CIP

#### INTERNATIONAL EDITION ISBN 0-07-121322-8

Copyright © 2003. Exclusive rights by The McGraw-Hill Companies, Inc., for manufacture and export. This book cannot be re-exported from the country to which is is sold by McGraw-Hill. The International Edition is not available in North America.

www.mhhe.com

To Susan and Anne

Sheet number 1 Page number v

#### black

## **ABOUT THE AUTHORS**

Stephen Brown received his B.A.Sc. degree in Electrical Engineering from the University of New Brunswick, Canada, and the M.A.Sc. and Ph.D. degrees in Electrical Engineering from the University of Toronto. He joined the University of Toronto faculty in 1992, where he is now an Associate Professor in the Department of Electrical & Computer Engineering. He is also Director of Software Development at the Altera Toronto Technology Center.

His research interests include field-programmable VLSI technology and computer architecture. He won the Canadian Natural Sciences and Engineering Research Council's 1992 Doctoral Prize for the best Ph.D. thesis in Canada.

He has won four awards for excellence in teaching electrical engineering, computer engineering, and computer science courses. He is a coauthor of two other books: Fundamentals of Digital Logic with VHDL Design and Field-Programmable Gate Arrays.

Zvonko Vranesic received his B.A.Sc., M.A.Sc., and Ph.D. degrees, all in Electrical Engineering, from the University of Toronto. From 1963-1965, he worked as a design engineer with the Northern Electric Co. Ltd. in Bramalea, Ontario. In 1968 he joined the University of Toronto, where he is now a Professor in the Departments of Electrical & Computer Engineering and Computer Science. During the 1978-79 academic year, he was a Senior Visitor at the University of Cambridge, England, and during 1984-85 he was at the University of Paris, 6. From 1995 to 2000 he served as Chair of the Division of Engineering Science at the University of Toronto. He is also involved in research and development at the Altera Toronto Technology Center.

His current research interests include computer architecture, field-programmable VLSI technology, and multiple-valued logic systems.

He is a coauthor of four other books: Computer Organization, 5th ed.; Fundamentals of Digital Logic with VHDL Design; Microcomputer Structures; and Field-Programmable Gate Arrays. In 1990, he received the Wighton Fellowship for "innovative and distinctive contributions to undergraduate laboratory instruction."

He has represented Canada in numerous chess competitions. He holds the title of International Master.

6.2 DECODERS

311

$$f = \overline{w}_2 f_{\overline{w}_2} + w_2 f_{w_2}$$

=  $\overline{w}_2 (w_3 + w_1 \overline{w}_4) + w_2 (\overline{w}_1 \overline{w}_3 + \overline{w}_3 w_4)$

Observe that  $\overline{f}_{\overline{w}_2} = f_{w_2}$ ; hence only two 3-LUTs are needed, as illustrated in Figure 6.14*b*. The LUT on the right implements the two-variable function  $\overline{w}_2 f_{\overline{w}_2} + w_2 \overline{f}_{\overline{w}_2}$ .

Since it is possible to implement any logic function using multiplexers, general-purpose chips exist that contain multiplexers as their basic logic resources. Both Actel Corporation [2] and QuickLogic Corporation [3] offer FPGAs in which the logic block comprises an arrangement of multiplexers. Texas Instruments offers gate array chips that have multiplexerbased logic blocks [4].

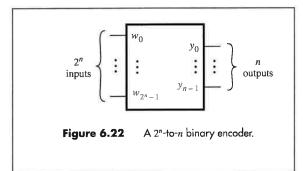

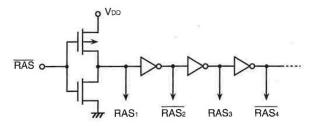

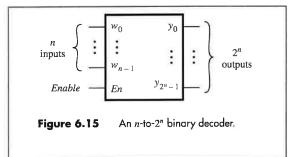

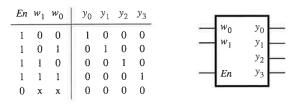

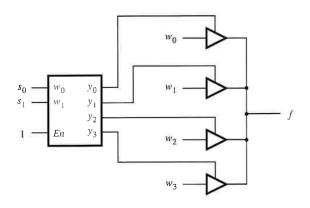

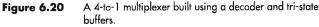

## 6.2 DECODERS

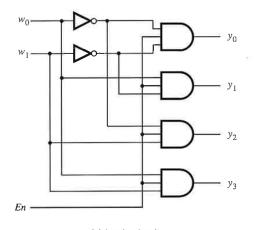

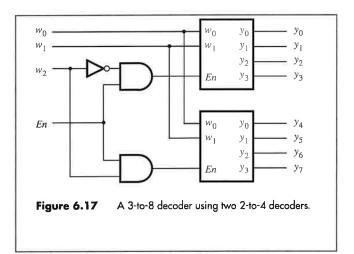

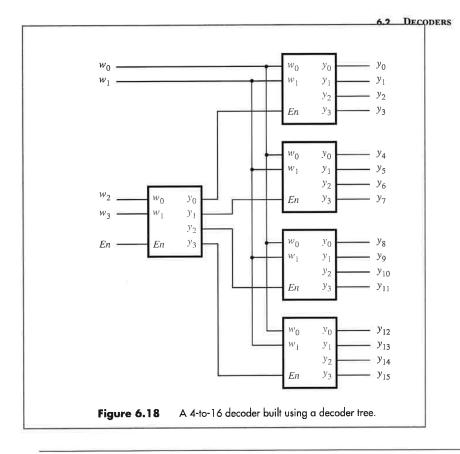

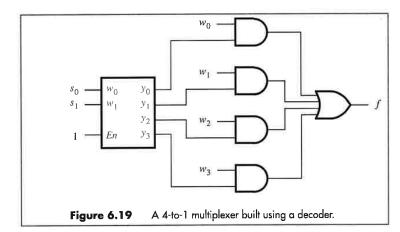

Decoder circuits are used to decode encoded information. A binary decoder, depicted in Figure 6.15, is a logic circuit with *n* inputs and  $2^n$  outputs. Only one output is asserted at a time, and each output corresponds to one valuation of the inputs. The decoder also has an enable input, *En*, that is used to disable the outputs; if En = 0, then none of the decoder outputs is asserted. If En = 1, the valuation of  $w_{n-1} \cdots w_1 w_0$  determines which of the outputs is asserted. An *n*-bit binary code in which exactly one of the bits is set to 1 at a time is referred to as *one-hot encoded*, meaning that the single bit that is set to 1 is deemed to be "hot." The outputs of a binary decoder are one-hot encoded.