Find authenticated court documents without watermarks at docketalarm.com.

## Microchip Fabrication

A Practical Guide to Semiconductor Processing

### **Peter Van Zant**

**Fourth Edition**

#### McGraw-Hill

ï

New York San Francisco Washington, D.C. Auckland Bogotá Caracas Lisbon London Madrid Mexico City Milan Montreal New Delhi San Juan Singapore Sydney Tokyo Toronto

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

DOCK

Δ

## Library of Congress Cataloging-in-Publication Data

Van Zant, Peter. Microchip fabrication : a practical guide to semiconductor processing / Peter Van Zant.—4th ed. p. cm. Includes bibliographical references and index. ISBN 0-07-135636-3

1. Semiconductors—Design and construction. I. Title. TK7871.85.V36 2000

621.3815'2—dc21

00-02317

McGraw-Hill

A Division of The McGraw Hill Companies

Copyright © 2000, 1997, 1984 by The McGraw-Hill Companies, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1 2 3 4 5 6 7 8 9 0 DOC/DOC 0 9 8 7 6 5 4 3 2 1 0

#### ISBN 0-07-135636-3

The sponsoring editor for this book was Stephen Chapman and the production supervisor was Sherri Souffrance. It was set in Century Schoolbook by Pro-Image Corporation.

Printed and bound by R. R. Donnelley & Sons Company.

This book is printed on recycled, acid-free paper containing a minimum of 50% recycled, de-inked fiber.

Information contained in this work has been obtained by The Mc-Graw-Hill Companies, Inc. ("Mc-Graw-Hill") from sources believed to be reliable. However, neither McGraw-Hill nor its authors guarantee the accuracy or completeness of any information published herein, and neither McGraw-Hill nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that McGraw-Hill and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

## ФГФВМ DOCKET

# **13** Metallization

Chapter

#### Overview

Fabrication of circuits is divided into two major segments. First the active and passive parts are fabricated in and on the wafer surface. These is called the Front End Of the Line or FEOL. In the Back End of the Line (or BEOL), the metal systems necessary to connect the devices and different layers are added to the chip. In this chapter the materials, specifications, and methods used to complete the metallization segment is presented along with other uses of metals in chip manufacturing. Vacuum pumps, used in CVD, evaporation, ion implant, and sputtering systems are explained at the end of the chapter.

#### Objectives

Upon completion of this chapter, you should be able to:

- 1. List the requirements of a material for use as a chip surface conductor.

- 2. Draw cross sections of single and multilayer metal schemes.

- <sup>3</sup>. Describe the purpose and operation of a thin-film fuse.

- 4. Make a list of materials used in the metallization of semiconductor devices. Identify their specific use(s).

- <sup>5</sup>. Draw and identify the parts of a vacuum evaporator.

- 6. Describe the principle of sputtering.

- 7. Draw and identify the parts of a sputtering system.

- 8. Describe the principle and operation of oil diffusion, turbo and cryogenic high-vacuum pumps.

395

Cree Ex. 1005

#### 396 Chapter Thirteen

#### Introduction

The most common and familiar use of metal films in semiconductor technology is for surface wiring. The materials, methods, and processes of "wiring" the component parts together is generally referred to as *metallization* or the *metallization process*. Metallization includes all of the steps in the metallization sequence described in Chapter 5.

#### **Conductors-Single Level Metal**

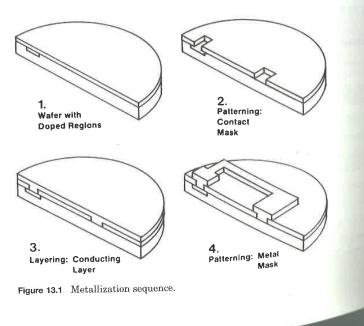

In the MSI era metallization was relatively straight forward (Fig. 13.1), requiring only a single level metal process. Small holes, called *contact holes* or *contacts*, are etched through the surface layers, to the device/circuit component parts. Following contact masking, a thin layer (10,000 to 15,000 Å) of the conducting metal (mostly aluminum or aluminum alloys) was deposited by vacuum evaporation, sputtering, or CVD techniques over the entire wafer. The unwanted portions of this layer are removed by a conventional photomasking and etch procedure or by lift-off. This step leaves the surface covered with thin lines of the metal that are called *leads, metal lines*, or *interconnects*. Generally a heat-treatment step, called *alloying*, is performed after metal patterning to ensure good electrical contact between the metal and the wafer surface.

Regardless of the structure, a metal system must meet the following criteria:

- Ease

- Good

- High

- Corr

- Long

- Capa

- Unife

#### Conduc

Increasi face, wh The an schemes it is exp two-met *layer* for

DOCKE