Media Oriented Systems Transport

Multimedia and Control Networking Technology

**OS8104**

**Preliminary Product Data Sheet**

DS8104PP2

Sept. 2000

© Copyright 1997-2000 Oasis SiliconSystems AG

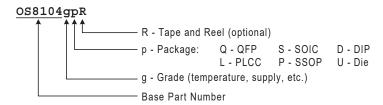

## **Ordering Information**

#### Valid Part Numbers:

| Order Number | Grade         |              | Packago                    |  |

|--------------|---------------|--------------|----------------------------|--|

| Order Number | Temperature   | Supply       | Package                    |  |

| OS8104AQ     | -40 to +85° C | 4.5 to 5.5 V | 44-pin TQFP                |  |

| OS8104AQR    | -40 to +85° C | 4.5 to 5.5 V | 44-pin TQFP, Tape and Reel |  |

This table represents parts that were available at the time of printing and may not represent parts that are currently available. For the latest list of valid ordering numbers for this product, please contact your local sales office.

## Support and Further Information

For more information on the MOST technology, product line, and custom IC development using MOST tools, contact one of our offices below.

#### Oasis SiliconSystems AG

1101 S. Capital of Texas Highway Building B, Suite 101 Austin, Texas 78746 USA

Tel: (+1) 512 306-8450 Fax: (+1) 512 306-8442 america@oasis.com

#### Oasis SiliconSystems AG

Bannwaldallee 48 D-76185 Karlsruhe Germany

Tel: (+49) (0) 721 6 25 37 - 0 Fax: (+49) (0) 721 6 25 37 - 119

europe@oasis.de

#### Oasis SiliconSystems AG

4-16 Oomaru Tsuzuki-ku Yokohama 224-0061, Japan

Tel: (+81) (90) 2757 1419 Fax: (+81) (45) 941 7818 pacrim@oasis.de

# **Technical Support**

For technical support please refer to one of the following email addresses: support@oasis.de support@oasis.com

Preliminary Product Data Sheet Page 2

© Copyright 1997-2000 Oasis SiliconSystems AG

DS8104PP2

## **Intellectual Property**

Duplication of this document without permission is prohibited. All rights reserved. The information within this document is confidential and Oasis SiliconSystems intellectual property.

### **Trademarks**

MOST is a registered trademark of Oasis SiliconSystems. All other trademarks used in this document are the property of their respective owners.

## **Patents**

There are a number of patents and patents pending on the MOST technology. The rights to these patents are not granted without any specific Agreement between the users and the patent owners.

## **Preliminary Product Data Sheet**

A Preliminary Product Data Sheet describes a product which is in limited production and subject to change. Oasis SiliconSystems has worked diligently to ensure that the information in this document is accurate and reliable. However, the information in this document is subject to change without notice and is provided "as is" without warranty of any kind (expressed or implied).

Preliminary Product Data Sheet

© Copyright 1997-2000 Oasis SiliconSystems AG

DS8104PP2 Page 3

## **Conventions**

Within this manual, the following abbreviations and symbols are used for improving readability:

|              | Comment                                                                   |

|--------------|---------------------------------------------------------------------------|

| PIN          | Name of a PIN                                                             |

| BIT          | Name of a single bit within a register                                    |

| xy           | Range from x to y. Used as abbreviation e.g. for a group of bits like D70 |

| [a,b,c]      | List of alternative elements to choose from.                              |

| 0xzz         | Hexadecimal number (value zz)                                             |

| bREG         | Single-byte (8-bit) register                                              |

| wREG         | Single-word register (16-bit)                                             |

| mREG         | Multi-byte register (e.g. message buffer)                                 |

| rsvd         | The respective bit or register is reserved for future use                 |

| /            | Inverter. Attached pin or bit uses inverted logic (low or 0 active)       |

| х            | Don't care                                                                |

| <b>1</b>     | Rising edge                                                               |

| $\downarrow$ | Falling edge                                                              |

# **Revision History**

| Revision | Date       | Description        |

|----------|------------|--------------------|

| 1.1      |            | Initial Data Sheet |

| 2        | Sept. 2000 | Fully revised.     |

## **TABLE OF CONTENTS**

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12                                                          |

| 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                          |

| 2 GENERAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                          |

| 2.1 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                          |

| 2.2 Network Interface & Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

| 2.3 On-Chip Network Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |

| 2.3.1 Channel Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19                                                          |

| 2.3.2 Physical Position Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19                                                          |

| 2.3.3 Network Delay Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |

| 2.3.4 Node Alive Supervision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

| 2.4 On-Chip Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

| 2.4.1 Low-Power Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

| 2.4.2 Zero Power Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

| 2.5 Data Transfer Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 2.5.1.1 Control Messaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 2.5.1.2 Synchronous (Stream) Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |

| 2.5.1.3 Asynchronous (Packet) Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

| 2.6 MOSTNetServices API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                                                          |

| 3 MAIN FUNCTIONAL BLOCKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| 4 OS8104 CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| 5 CONTROL PORT IN SERIAL MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                          |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29                                                          |

| 5.1 I <sup>2</sup> C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29<br>31<br>31                                              |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 5.1 I <sup>2</sup> C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29<br>30<br>31<br>32<br>32<br>32                            |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 5.1 I <sup>2</sup> C Mode 5.1.1 Writing To Control Port 5.1.2 Reading From Control Port 5.2 SPI Mode 5.2.1 Writing To Control Port 5.2.2 Reading From Control Port 6 NETWORK INTERFACE 6.1 MOST Frame Structure 6.2 Network Configuration                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 30 31 32 32 33 33 34 35 36                               |

| 5.1 I <sup>2</sup> C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register 2) 6.2.4 Capturing Error Events                                                                                                                                                                                                                                                              | 29 30 31 32 32 32 33 33 33 34 35 36 36                      |

| 5.1 I <sup>2</sup> C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE. 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register 2) 6.2.4 Capturing Error Events 6.2.5 bSBC (Synchronous Bandwidth Control register)                                                                                                                                                                                                         | 29 30 31 32 32 32 33 33 33 34 35 36 36 37                   |

| 5.1 I <sup>2</sup> C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE. 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register 2) 6.2.4 Capturing Error Events. 6.2.5 bSBC (Synchronous Bandwidth Control register) 6.2.6 bNDR (Node Delay Register).                                                                                                                                                                      | 29 30 31 32 32 32 33 33 33 34 35 36 36 37 37                |

| 5.1 I <sup>2</sup> C Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 30 31 32 32 32 33 33 34 35 36 36 37 37 39                |

| 5.1 I²C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE. 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register 2) 6.2.4 Capturing Error Events 6.2.5 bSBC (Synchronous Bandwidth Control register) 6.2.6 bNDR (Node Delay Register). 6.2.7 bNPR (Node Position Register) 6.2.8 bMPR (Maximum Position Register).                                                                                                        | 29 30 31 32 32 32 33 33 34 34 35 36 36 37 37 39             |

| 5.1 I²C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE. 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register 2) 6.2.4 Capturing Error Events 6.2.5 bSBC (Synchronous Bandwidth Control register) 6.2.6 bNDR (Node Delay Register) 6.2.7 bNPR (Node Position Register) 6.2.8 bMPR (Maximum Position Register) 6.2.9 bMDR (Maximum Delay Register)                                                                      | 29 30 31 32 32 32 33 33 34 35 36 36 37 37 39 39             |

| 5.1 I²C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE. 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register 2) 6.2.4 Capturing Error Events. 6.2.5 bSBC (Synchronous Bandwidth Control register) 6.2.6 bNDR (Node Delay Register). 6.2.7 bNPR (Node Position Register). 6.2.8 bMPR (Maximum Position Register). 6.2.9 bMDR (Maximum Delay Register). 6.2.10 Network Registers After Lock                             | 29 30 31 32 32 32 33 33 34 35 36 36 37 37 39 39 40          |

| 5.1 I²C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register) 6.2.4 Capturing Error Events 6.2.5 bSBC (Synchronous Bandwidth Control register) 6.2.6 bNDR (Node Delay Register) 6.2.7 bNPR (Node Position Register) 6.2.8 bMPR (Maximum Position Register) 6.2.9 bMDR (Maximum Delay Register) 6.2.10 Network Registers After Lock 7 SOURCE DATA PORTS IN SERIAL MODE  | 29 30 31 32 32 32 33 33 33 34 35 36 36 37 37 39 39 40 40 41 |

| 5.1 I²C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE. 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register) 6.2.4 Capturing Error Events 6.2.5 bSBC (Synchronous Bandwidth Control register) 6.2.6 bNDR (Node Delay Register) 6.2.7 bNPR (Node Position Register) 6.2.8 bMPR (Maximum Position Register) 6.2.9 bMDR (Maximum Delay Register) 6.2.10 Network Registers After Lock 7 SOURCE DATA PORTS IN SERIAL MODE | 29 30 31 32 32 32 33 33 33 34 35 36 36 37 37 39 39 40 40 41 |

| 5.1 I²C Mode 5.1.1 Writing To Control Port. 5.1.2 Reading From Control Port. 5.2 SPI Mode 5.2.1 Writing To Control Port. 5.2.2 Reading From Control Port. 6 NETWORK INTERFACE 6.1 MOST Frame Structure 6.2 Network Configuration 6.2.1 bXCR (Transceiver Control Register) 6.2.2 bXSR (Transceiver Status Register) 6.2.3 bXSR2 (Transceiver Status Register) 6.2.4 Capturing Error Events 6.2.5 bSBC (Synchronous Bandwidth Control register) 6.2.6 bNDR (Node Delay Register) 6.2.7 bNPR (Node Position Register) 6.2.8 bMPR (Maximum Position Register) 6.2.9 bMDR (Maximum Delay Register) 6.2.10 Network Registers After Lock 7 SOURCE DATA PORTS IN SERIAL MODE  | 29 30 31 32 32 32 33 33 33 34 35 36 36 37 37 39 39 40 40 41 |

Preliminary Product Data Sheet

© Copyright 1997-2000 Oasis SiliconSystems AG

DS8104PP2 Page 5

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.