# **Chapter 20: Card Services**

Note that the AcknowledgeInterrupt function is called by the status change interrupt service routine. Interrupts must not be re-enabled while processing a status change interrupt. This could cause nesting of status change interrupts while processing the socket service's AcknowledgeInterrupt, a situation that socket services is unprepared to manage (because the routine is non-reentrant).

#### The Client Call-Back

Numerous events can occur that require a call-back to client drivers. These events are listed in table 20-11. The events in the shaded boxes were added with the PC Card 95 release.

Table 20-11. Call-Back Events Defined by Card Services

| Event              | Code | Source           | Client(s) | Registered By     |

|--------------------|------|------------------|-----------|-------------------|

| BATTERY_DEAD       | 01h  | Hardware         | Socket    | RequestSocketMask |

| BATTERY_LOW        | 02h  | Hardware         | Socket    | RequestSocketMask |

| CARD_INSERTION     | 40h  | Hardware         | All       | RegisterClient    |

| CARD_INSERTION [A] | 40h  | DeregisterMTD    | MTDs      | RegisterClient    |

| CARD_INSERTION [A] | 40h  | RegisterClient   | Requester | RegisterClient    |

| CARD_INSERTION [A] | 40h  | ReleaseExclusive | All       | RegisterClient    |

| CARD_INSERTION [A] | 40h  | RequestExclusive | Requester | RequestExclusive  |

| CARD_INSERTION [A] | 40h  | RequestExclusive | All       | RegisterClient    |

| CARD_LOCK          | 03h  | Hardware         | Socket    | RequestSocketMask |

| CARD_READY         | 04h  | Hardware         | Socket    | RequestSocketMask |

| CARD_REMOVAL       | 05h  | Hardware         | Socket    | RequestSocketMask |

| CARD_REMOVAL [A]   | 05h  | ReleaseExclusive | Socket    | RequestSocketMask |

| CARD_REMOVAL [A]   | 05h  | RequestExclusive | All       | RegisterClient    |

| CARD_RESET         | 11h  | ResetFunction    | Socket    | RequestSocketMask |

| CARD_UNLOCK        | 06h  | Hardware         | Socket    | RequestSocketMask |

| CLIENT_INFO        | 14h  | GetClientInfo    | Provider  | RegisterClient    |

| EJECTION_COMPLETE  | 07h  | Hardware         | Socket    | RequestSocketMask |

| EJECTION_REQUEST   | 08h  | Hardware         | Socket    | RequestSocketMask |

| ERASE_COMPLETE     | 81h  | Queued Erase     | Requester | RequestEraseQueue |

| EXCLUSIVE_COMPLETE | 0Dh  | RequestExclusive | Requester | RequestExclusive  |

| EXCLUSIVE_REQUEST  | 0Eh  | RequestExclusive | Socket    | RequestSocketMask |

| INSERTION_COMPLETE | 09h  | Hardware         | Socket    | RequestSocketMask |

| INSERTION_REQUEST  | 0Ah  | Hardware         | Socket    | RequestSocketMask |

| MTD_REQUEST        | 12h  | Card Services    | MTD       | RegisterClient    |

| PM_RESUME          | 0Bh  | Card Services    | Socket    | RequestSocketMask |

Table 20-11. Call-Back Events Defined by Card Services

| Event ·               | Code  | Source         | Client(s) | Registered By     |

|-----------------------|-------|----------------|-----------|-------------------|

| PM_SUSPEND            | 0Ch   | Card Services  | Socket    | RequestSocketMask |

| REGISTRATION_COMPLETE | 82h   | RegisterClient | Requester | RegisterClient    |

| REQUEST_ATTENTION     | 18h   | Hardware       | All       | RegisterClient    |

| RESET_COMPLETE        | 80h   | ResetFunction  | Requester | ResetFunction     |

| RESET_PHYSICAL        | 0Fh   | ResetFunction  | Socket    | RegisterClient    |

| RESET_REQUEST         | 10h . | ResetFunction  | Socket    | RegisterClient    |

| SS_UPDATED            | 16h   | Card Services  | All       | RegisterClient    |

| TIMER_EXPIRED         | 15h   | Hardware       | Requester | RegisterTimer     |

| WRITE_PROTECT         | 17h   | Hardware       | All       | RegisterClient    |

# Configuring PC Cards During POST

The previous discussions of PC Card configuration have presumed that the cards will be installed when the operating system loads or when the PC Card is inserted sometime after the operating system has loaded and the system is running. If however, the need to load the operating system from the PC Card exists, the previously discussed approaches for configuring the cards don't work.

To perform initial program load (IPL) from a PC Card, ROM-based PCMCIA initialization code must be included with the system. This code must be able to program the HBA and parse the CIS to determine if a given card should be configured during POST (Power-On Self Test). Once the HBA has been programmed, memory cards containing a boot sector can be recognized as bootable since they will contain a BIOS Parameter Block (BPB) that permits the booting from the PC Card in the same fashion as a floppy drive.

Similarly, ATA drives can be recognized by ROM code by reading the initialization byte within the Function Identification tuple. The initialization byte specifies that the device should be configured during POST. Once the ATA drive is configured, IPL can occur from the PCMCIA ATA drive like any other ATA drive.

Note that this initialization process occurs prior to card services being installed. As a result, the a client driver will not have registered to receive status change events from the PC Card. When the operating system boots, a driver for the PC Card that is performing IPL can register with card services.

# Chapter 21

## The Previous Chapter

The previous chapter focused on the role of card services in the PCMCIA environment. It also reviewed each of the functions defined by the PC Card specification that apply to 16-bit PC Cards, and defined the related return codes. The call back mechanism was also described and the event and call back codes were defined.

## **This Chapter**

This chapter discusses the three basic types of enablers: point enablers, device-specific enablers, and super enablers. The chapter also discusses the jobs performed by generic memory enablers (and MTDs) and I/O device enablers.

## The Next Chapter

The next chapter discusses the problems associated with loading the operating system from a PC Card. It also defines mechanisms used to determine whether a given PC Card is a bootable device, and the firmware support required to support PC Card booting.

### Overview

This chapter discusses PC Card enablers. The chapter focuses primarily on client driver enablers, but also includes a brief discussion of point enablers at the end of the chapter. Note that the terms PC Card enabler, client, client driver, and device driver are all used to describe the software that is responsible for configuring a PC Card. This chapter uses the terms enabler and client driver.

Specific types of client drivers (enablers) discussed in this chapter include:

- SRAM client drivers

- Flash client drivers and Memory Technology Drivers (MTDs)

- Generic I/O client drivers

In order to configure a PC Card, enablers must first register with card services. The primary function of an enabler is to detect and configure PC Cards that it supports. As such, the enabler must be prepared to configure its card no matter when it is installed. In order to configure cards installed after power up, the enabler registers with card services to receive a call back (i.e., a card insertion call-back) each time card services detects that a PC Cards has been installed. During registration, the enabler can also request that card services generate a call-back for each PC Card already installed, thereby calling the enabler's configuration routine.

## The Card Insertion Call-Back

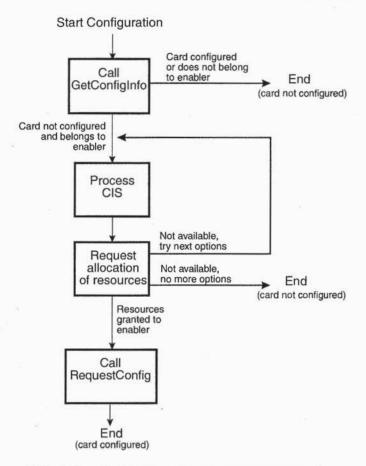

When card services makes a card insertion call-back it specifies the type of call-back initiated, along with the logical socket that the card was inserted into. The call-back routine then attempts to configure the card. Figure 21-1 illustrates the typical process used by an enabler to configure a card. The CIS may have to be accessed several times to obtain a combination of card-required resources that can be successfully allocated to the card (i.e., resources that are not already assigned to other devices).

The configuration process begins when card services makes the card insertion call-back to the enabler. The enabler detects which event caused the call-back and obtains information supplied by card services (e.g., which logical socket the card was inserted into).

The method of configuring a card varies depending of the type of card to be configured. The next section discusses generic memory enablers, and the following section describes the operation of a generic I/O enabler.

As discussed in the previous chapter, a variety of services are available for the PC Card enablers (i.e., card services client drivers) to configure a PC Card.

# **Chapter 21: Client Drivers**

Figure 21-1. A Sample Configuration Process Used By a Card Services Client

# **Memory Drivers and Memory Technology Drivers**

Memory client drivers provide virual disk drive support. In short, these drivers are responsible for storing and retrieving files within the memory card. The method required to access the memory card varies depending on the type of memory devices (i.e., memory technology) implemented in the card. Since memory devices (such as flash) require various programming algorithms, each memory type must have an associated memory technology driver (MTD).

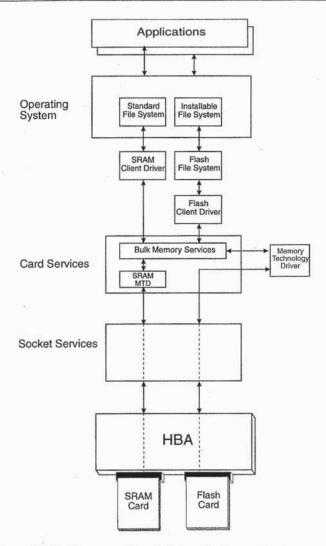

Figure 21-2 illustrates the overall software architecture specified for accessing memory cards as virtual disk drives. Notice that memory client drivers receive file access requests from the file system and must access the memory card to fullfill each request. The file system might be the standard file system used by the operating system (e.g., the DOS FAT system) or an installable system required when accessing flash memory. Card services provides bulk memory services that simplifies the memory client driver's job of accessing a specific block of memory within the memory card.

SRAM memory client drivers typically interface directly to the operating system's file manager, since there are no restrictions related to writing and reading data to or from SRAM. These client drivers are designed to access memory via the bulk memory services provided by card services. Since accessing SRAM is uniform and quite simple (byte read/write capability), the memory technology driver is incorporated into card services.

Flash memory client drivers interface directly to a flash file system. A special file system is required for flash devices due to the special requirements associated with writing to flash memory. Two major factors are:

- Write operations require first erasing a specified block of memory followed by the block write, and may take several seconds to complete.

- Flash memory also has a limited write-cycle life. That is, repetitive erasures and writes to the same memory block destroys the chips ability to retain data within that block. The maximum number of erasures and writes are specified by the manufacturer (e.g., a flash device may specify as life of as few as 10,000 writes).

Knowing the restrictions associated with accessing flash memory, the flash file system is designed specifically to provide compatible access to flash memory. For example, the flash file system distributes writes to flash memory to minimize the effects of repetitive write ware and accommodates the slow erase time.

Memory enablers (client drivers) have a formidable task to perform since a wide variety of memory card implementations exist. The enabler must also acquire a drive letter from the operating system to allocate to each card slots that a memory card might be inserted into. The following sections describe the jobs performed by SRAM and flash client drivers.

Figure 21-2. Memory Client Driver Software Environment

## **SRAM Client Drivers**

SRAM client drivers typically load as installable device drivers via the config.sys file or equivalent mechanism. One of the tasks performed by the device driver is to detect the presence of card services by calling the GetCSInfo service. If the call returns the ASCII string "CS," then SRAM client driver recognizes that card services are installed. Note that if card services is not installed, the SRAM driver typically reports the error condition and terminates

without remaining resident in memory. When card services is detected, the driver then registers with card services.

The driver must also obtain logical drive letters needed to perform the disk emulation. Note that the drive letter is acquired when the device driver installs even though a memory card may not be installed in the system. In this case, an attempt to access files associated with the drive letter assigned to the socket will result in a drive not ready error.

## SRAM Client Driver Registers with Card Services

The client driver performs the registration process by calling the RegisterClient service. The SRAM client identifies itself as a memory client, registers to receive relevant call-back events, and passes a pointer to its call-back routine. The client may also request that card services generate a card insertion call-back for each PC Card already installed in the system. The memory client receives a handle value from card services when it returns from the call. Once registered, the memory client awaits call-backs from card servcies, notifying it when a PC card is inserted or removed.

#### The SRAM Client Driver Call-Back

When card services generates the card insertion call-back, it also passes the logical socket number that the PC Card was inserted into. The memory client then attempts to configure the PC Card.

The memory client must first determine if it should attempt to configure the PC Card by determining the card type. Memory clients can use the bulk memory services to access a specific region within the PC card. To access memory, the client first calls the OpenMemory service by specifying an offset within the card's attribute or common memory address space. Card services then returns a memory handle to the client that it can use when accessing memory relative to the offset specified in the OpenMemory service. Note that if card services does not support bulk memory services, the memory client must use the RequestWindow service to specify the host system address space that it wishes to use to access PC Card memory.

Reading from or writing to PC Card memory is accomplished by calling the ReadMemory or WriteMemory services. The memory client passes the memory handle it received from the OpenMemory service and specifies the memory offset and range of addresses it wishes to access. The call will likely

# **Chapter 21: Client Drivers**

specify location zero within the attribute memory address space. When the data is returned to the memory client it evaluates the DEVICE tuple to determine if the card contains SRAM.

Note that determining the card type can be a complicated process for memory clients. Some memory cards implement the CIS in attribute memory (required by the PC Card standard), some implement the CIS in common memory, while others do not implement a CIS at all. To complicate matters, some CIS implementations are invalid, requiring the enabler to attempt interpretation of the faulty CIS. If the card does not contain a CIS, the enabler attempts to detect the presence of the BPB (BIOS parameter block), which contains information that specifies the logical size of the disk. The BPB if present should reside at either location 0 or 512 in common memory.

If an SRAM card is detected, the call-back routine return to card services, indicating that the card was successfully configured. If the PC Card was not an SRAM card, the client returns to card services, indicating the card was not configured by the SRAM enabler.

#### Flash Client Drivers

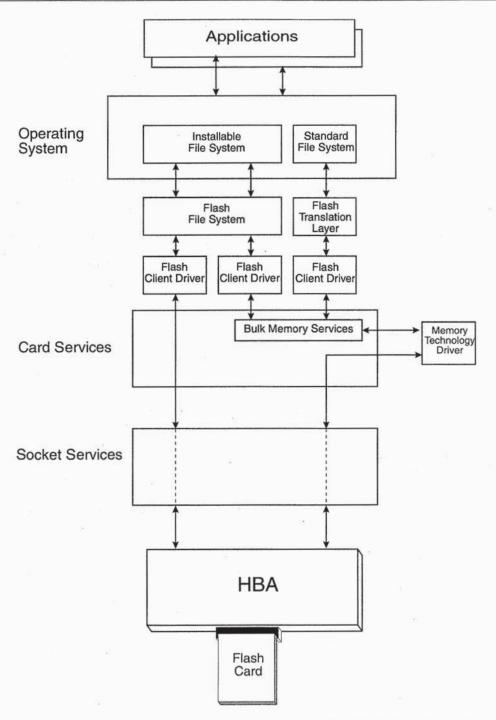

Figure 21-3 illustrates the flash client driver software environment. Three types of flash client drivers are illustrated in figure 21-3. Two of the client drivers are shown interfacing to a flash file system and the other via a file translation layer. (Each file system is discussed later in this chapter.)

The flash client drivers typically load as installable device drivers via the config.sys file or equivalent mechanism. The first task performed by the device driver is to detect the presence of card services. If card services are not installed, the flash driver typically reports the error condition and terminates without remaining resident in memory. When card services is detected, the driver then registers with card services.

Flash client drivers differ from SRAM drivers in two important ways:

- Flash client drivers interface to the flash file system

- MTD client drivers must be installed to handle calls made to bulk memory services

The MTD must register prior to the flash client driver. This is necessary because the flash client driver uses the MTD to access the flash card.

Figure 21-3. Software Environment Required for Flash Card Support

# **Chapter 21: Client Drivers**

Like SRAM client drivers, flash client drivers must also obtain logical drive letters needed to perform the disk emulation. The drive letter is acquired when the device driver installs even though a memory card may not be installed in the system. In this case, an attempt to access files associated with the drive letter assigned to the socket will result in a drive not ready error.

## The Flash File System

Two primary types of flash file system solution are provided by software vendors today. These systems are generally referred to as the flash file system (FFS) and flash translation layer (FTL) as illustrated in figure 21-3. The FFS provides file management based on variable size data blocks, while the FTL interfaces directly to the DOS file system which allocates data based on standard block sizes. The FTL system is compatible with disk utility programs such as Norton and PC Tools, whereas, the FFS-based systems are not.

## MTD Registers with Card Services

The MTD registers with card services by calling the RegisterClient service. When registering the MTD specifies that it is a MTD client during, specifies relevant call-back events it want to be notified of, and passes a pointer to its call-back routine. The MTD client may also request that card services generate a card insertion call-back for each PC Card already installed in the system. The MTD client receives a handle value from card services when it returns from the call. Once registered, the MTD awaits call-backs from card servcies, notifying it when a PC card is inserted or removed.

#### The MTD Call-Back

When card services generates the card insertion call-back, it also passes the logical socket number that the PC Card was inserted into. The MTD client then determines if the PC Card contains any flash memory that it is designed to access. This can be accomplished by calling the GetFirstRegion and GetNextRegion services. These services return information (obtained from the CIS) about the card type, size, location, access time, and block erase details of the regions. If the MTD recognizes a regions of memory that it knows how to access, it then registers with card services to control access to that specific region of memory.

## **MTD Registers Memory Regions**

To register a memory region with card services the MTD calls the RegisterMTD service. This notifies card services that the MTD has agreed to handle access to the memory regions specified. When a flash client driver requests access to this region via bulk memory services, card services will make an MTDRequest call-back to the MTD. The information specified in the call-back packet specifies the operation be requested.

## Flash Client Driver Registers with Card Services

The client driver performs the registration process by calling the RegisterClient service. The flash client identifies itself as a memory client, during registration and specifies which call-back events it wishes to be notified of, and passes a pointer to its call-back routine. The client may also request that card services generate a card insertion call-back for each PC Card already installed in the system. The memory client receives a handle value from card services when it returns from the call. Once registered, the memory client awaits call-backs from card services, notifying it when a PC card is inserted or removed.

#### The Flash Client Driver Call-Back

When card services generates the card insertion call-back, it also passes the logical socket number that the PC Card was inserted into. The memory client then attempts to configure the PC Card.

The memory client must first determine if the card is the type that it is designed to enable. Memory clients can use the bulk memory services to access a specific region within the PC card. To access memory, the client first calls the OpenMemory service by specifying an offset within the card's attribute or common memory address space. Card services then returns a memory handle to the client for use when accessing memory starting at the offset specified in the OpenMemory service. Also when the OpenMemory service is called, card services recognized the region being opened is registered by the MTD. Note that if card services does not support bulk memory services, the memory client must use the RequestWindow service to specify the host system address space that it wishes to use to access PC Card memory.

# **Chapter 21: Client Drivers**

Reading from or writing to PC Card memory is accomplished by calling the ReadMemory or WriteMemory services. In this instance, the memory client passes the memory handle it received from the OpenMemory service and specifies the memory offset and range of addresses it wishes to access. The call will likely specify location zero within the attribute memory address space. When the data is returned to the memory client it evaluates the DE-VICE tuple to determine if the card contains flash memory.

If a flash card is detected the call-back routine returns to card services, indicating that the card was successfully configured. If the PC Card was not a flash card, the client returns to card services, indicating the card was not enabled by the flash client driver.

## **Accessing Flash Memory**

Once the flash card has been enabled, access made to the flash card virtual drive will be fulfilled. The flash client driver receives the request from the flash file system and calls the appropriate bulk memory service. Card services recognizes that the call is to a region controlled by an MTD that previously register to access the specified memory region. Card services responds by making MTD call-backs to specify the operation being requested.

## I/O Card Client Drivers

Two basic types of I/O client drivers are popular.

- Device-specific client drivers drivers designed to detect and configure a specific PC Card. The client drivers are typically shipped by the manufacturer of a PC Card and are designed to configure this specific PC Card.

- Generic (Super) client drivers drivers designed to detect and configure a wide range of I/O cards based on generic types, regardless of manufacturer.

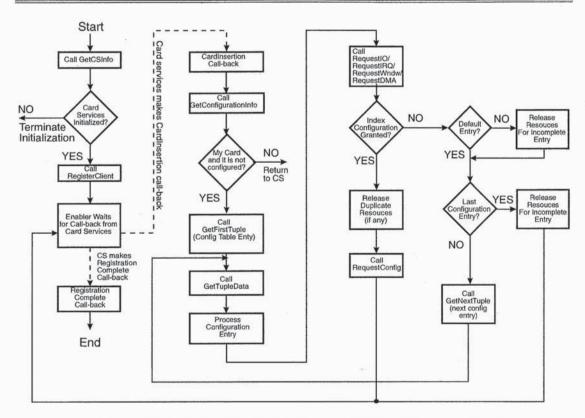

Each type of I/O client driver install as device drivers when the config.sys file is executed during the system boot process. Figure 21-4 illustrates the primary actions taken by an generic I/O client driver when it initializes, registers with card services and attempts to configure PC Cards.

Figure 21-4. I/O Enabler Registration and PC Card Configuration Process

## I/O Client Driver Registers with Card Services

The registration process begins after the client driver detects that card services has initialized. This is accomplished with the GetCardServicesInfo call. Card services returns information about card services and verifies its presence by also returning the ASCII string "CS." If card services is not initialized, the I/O client driver reports the error condition and terminates without remaining resident in memory. If card services are present the client driver calls the RegisterClient service. When the I/O client driver makes the call it:

- · identifies itself as an I/O client,

- specifies which events it wants to be notified of,

- requests a card insertion call-back for each PC Card currently installed in sockets, and

- passes the entry point of it call-back routine when making the call.

# **Chapter 21: Client Drivers**

Card services returns a client handle to the I/O client driver upon return from the RegisterClient service. The client driver then awaits card insertion callbacks. Card services generates a CardInsertion call-back for each PC Card already installed in a card socket (as requested by the client driver during registration). If all sockets are empty, card services generates a ConfigurationComplete call-back to signal the end of the configuration process. This example presumes that an I/O PC Card was installed when the system was powered on.

#### The I/O Client Driver Call-Back

Card services generates a CardInsertion call-back to the I/O client driver. The driver detects the call-back and evaluates the call-back packet to determine the socket into which the PC Card was inserted.

#### Identifying the PC Card

Next the GetConfigurationInfo service is called to determine if the PC Card has already been configured by another enabler. If already configured, the client driver returns to card services without configuring the PC Card. If the PC Card has not been configured, the client driver evaluates other data returned by the GetConfigurationInfo service to determine the type of function that is associated with the PC Card. If the function is one that the generic I/O enabler is designed to handle, the configuration process continues.

#### **Determining Resources Requirements**

Next, the client driver checks the first entry within the configuration table to determine the resources required by the card. This can be accomplished by and calling the GetFirstTuple service and specifying a tuple code of 1Bh (the configuration table entry tuple code). Card services scans the CIS until if finds the first instance of tuple 1Bh and returns to the client driver. The I/O driver checks the completion status and detects that card services has located the first configuration table entry. Next, the client driver calls GetTupleData and card services returns the contents of the first configuration table entry. The tuple data is evaluated to determine the resources required by the PC Card.

#### Requesting the Resources

As the client driver detects a configurable resource within the configuration table entry (e.g., a range of I/O address locations), it checks with card services to determine if the resource is available for the I/O card to use. The client requests a resource by calling the respective resource request service (e.g., RequestIO). When RequestIO is called Card services receives the base I/O address and range of address locations requested. It uses these values to performs a look-up within the resource management table to determine if the resource is available. Card services indicates whether or not the resource was available in the return code.

The client driver makes requests for all resources listed within the configuration table entry and determines their availability. The configurable resources that can be acquired from the system include:

- Memory address locations via the RequestWindow service

- I/O address locations via the RequestIO service

- Interrupt request lines via the RequestIRQ service

- DMA channels via the RequestDMA service

The specific actions taken when a resource is not available depends of whether the entry is a default entry of not, as discussed in the following paragraph.

If the client driver detects that the entry is tagged as a default entry, it knows that it should attempt to acquire all resources that are specified within this entry. It should retain all resource acquired from card services even if one or more of the resources requested are not available. If the entry is not a default entry, the client driver knows that the entire set of resources specified within entry must be obtained to satisfy the configuration. If any one resource is not available, then the client driver should release any individual resources that were acquired from card services by calling the respective release resource service (e.g., ReleaseIO).

If a given entry fails to satisfy the PC Card's configuration, the client driver then proceeds to the next entry by calling the GetNextTuple service. Card services finds the next configuration table entry (tuple 1B) and the client driver calls GetTupleData and starts the resource acquisition process again.

# **Chapter 21: Client Drivers**

#### Configuring the PC Card

When all resources needed for the PC Card's configuration have been acquired from the system, the client driver configures the HBA and PC Card by calling the RequestConfiguration service. In response, card services configures the HBA and PC Card. The HBA is configured by loading the appropriate HBA registers (via socket services) that satisfy the configuration being requested. This includes reconfiguring the socket interface to memory or I/O, programming the I/O window registers, and programming the IREQ# steering logic to direct the IRQ to the appropriate system IRQ line. The PC Card is configured by writing the index number of the configuration table entry (the entry that satisfied the configuration) into the configuration option register (COR) within the card's attribute memory address space.

### **Point Enablers**

Point enablers are dedicated enablers that bypass card and socket services. These enablers are popular in environments such as DOS where limited memory address space is available for application programs. Card and socket services take a considerable amount of memory when they install. Added to this is the space required by the enabler(s) and any TSR (terminate and stay resident programs) that might be used. As a result, too little memory is left for many application programs to run.

One solution used to relieve this memory shortage, is to remove card and socket services from the system, thereby freeing up memory that is needed to run the application program. Eliminating the card and socket services prevents PC Card client drivers from performing their functions, thus PC Card are never enabled and cannot be used. In order to use PC Cards point enablers are needed to configure the PC Cards.

In the absence of card and socket services, point enablers must communicate directly with the HBA to load the appropriate registers necessary to gain access to the PC Card. The card's CIS must be read and interpreted to identify the PC Card. If the point enabler recognizes the PC Card, it attempts to configure the card by loading the appropriate registers within the HBA to satisfy the configuration, and by writing to the configuration registers to configure the PC Card. Note that the resources used to configure the PC Card must be specified manually by the user (typically via software switches).

# Chapter 22

## The Previous Chapter

The previous chapter discussed the three basic types of enablers: point enablers, device-specific enablers, and generic (super) enablers. The chapter also discussed the jobs performed by generic memory enablers (and MTDs) and I/O device enablers.

## This Chapter

This chapter discusses the problems associated with loading the operating system from a PC Card. It also defines mechanisms used to determine whether a given PC Card is a bootable device, and the firmware support required to support PC Card booting.

## The Next Chapter

The next chapter introduces execute-in-place (XIP) support defined by the PC Card standard. The major components of an XIP environments are specified and the XIP mechanism is described.

# Configuring PC Cards During POST

The previous discussions of PC Card configuration have presumed that PC Cards will be initialized either as the operating system loads or when the PC Card is inserted into a socket sometime after the operating system has loaded and the system is running. If however, the need to load the operating system from a PC Card exists, the previously discussed approaches for configuring the cards don't work.

### The Problem

The normal method used in the PC environment to configure and initialize bootable devices (i.e., hard drive, video controller, and LAN adapters that support remote boot from the network) requires that the bootable device contain initialization code in a device-specific ROM. The system initialization code contained within system ROM scans the region of memory address space from location C0000h-DFFFFh to detect the presence of a device ROMs (i.e., a bootable devices). If a device ROM is detected, the system calls the initialization routine within the device ROM which is responsible for configuring the device. In this way, the bootable device is configured and can participate in loading the operating system.

To perform initial program load (IPL) from a PC Card, it too must be configured prior to beginning the boot operation. The standard method of configuring PC Cards requires the use of socket services, card services, and the PC Card's client driver. This software doesn't initialize until the operating system loads, making it unavailable for configuring a PC Card that must be used to load the operation system. Even if the PC Card contains a device ROM it cannot be detected by the system firmware during the ROM scan (because a memory window must first be programmed within the HBA to gain access to PC Card memory).

#### The Solution

ROM-based PCMCIA initialization code must be included with the system to support IPL from PC Cards. This firmware code must be able to program the HBA to open an attribute memory window to permit access to the CIS. Then the CIS can be evaluated to determine if the PC card is bootable, and therefore, should be configured during the POST (Power-On Self Test) sequence.

## **Bootable Memory Cards**

The PCMCIA initialization firmware detects the presence of memory cards and configure them by opening a common memory window to provide access to the PC Cards memory array (i.e., virtual drive). The boot code being PC Card aware attempts to load the operating system from the memory card. If the memory card has been formatted and the system files reside within the

# **Chapter 22: Booting from PC Cards**

memory card, the firmware will recognize the boot sector and load the operating system from the memory card.

Note that once the operating system loads, the memory cards will no longer be accessible unless the memory card contains a config.sys file that lists all of the PCMCIA relevant drivers. In this case, the socket services, card services, and the associated client drivers are loaded, thereby, providing access to the PC Cards after the operating system has loaded.

#### **Bootable ATA Devices**

PCMCIA initialization firmware recognizes ATA PC Cards by evaluating the function identification tuple within the CIS (table 22-1). The function identification tuple indicates the device type as shown in table 22-2. The shaded area identifies the value used by the ATA PC Card.

| Byte | Function Identification Tuple Format |                                 |  |

|------|--------------------------------------|---------------------------------|--|

| 0    | TPL_CODE                             | CISTPL_FUNCID (21H)             |  |

| 1    | TPL_LINK                             | Link to next tuple (at least 2) |  |

| 2    | TPLFID_FUNCTION                      | PC Card function code           |  |

| 3    | TPLFID_SYSINIT                       | System initialization bit mask  |  |

Table 22-1. Format of the Function Identification Tuple

Note that function extension tuple will follow the function identification tuple that identify specific features associated with the ATA card (Refer to the chapter entitled, "An ATA PC Card Example"). The function identification tuple also includes an initialization byte that specifies whether the device should be configured during POST and whether the ATA card contains a device ROM. (See table 22-3.)

If the initialization byte indicates that the ATA card should be configured during POST but that it does not contain a device ROM, then the firmware is responsible for configuring the ATA card. Once the ATA card is configured, the operating system can boot directly from the drive.

Table 22-2. Contents of the Function Identification Byte

| Code | Name                   | Meaning                                                                                                                    |  |

|------|------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| 0h   | Multi-Function         | PC Card has multiple functions. Examine the following function identification tuples that follow for individual functions. |  |

| 1h   | Memory                 | Memory Card (RAM, ROM, EPROM, flash, etc.).                                                                                |  |

| 2h   | Serial Port            | Serial I/O port, includes modem cards.                                                                                     |  |

| 3h   | Parallel Port          | Parallel printer port, may be bi-directional.                                                                              |  |

| 4h   | Fixed Disk             | Fixed drive, may be silicon may be removable.                                                                              |  |

| 5h   | Video Adapter          | Video interface, extension tuples (type and resolutions supported).                                                        |  |

| 6h   | Network LAN<br>Adapter | Local Area Network adapter.                                                                                                |  |

| 7h   | AIMS                   | Auto-Incrementing Mass Storage card.                                                                                       |  |

| 8FFh | Reserved               | Unused in this release. Reserved by PCMCIA for future use.                                                                 |  |

Table 22-3. Contents of the Initialization Byte

| 7  | 6           | 5          | 4           | 3            | 2  | 1   | 0    |

|----|-------------|------------|-------------|--------------|----|-----|------|

| Re | eserved for | future use | , must be s | et to zero ( | 0) | ROM | POST |

If the ATA drive also contains a device ROM, then firmware can map the ROM into the ROM scan region (C0000h-DFFFFh) and the standard initialization process will detect the device ROM. The ATA device ROM containing the ATA enabler and driver will be called by PCMCIA firmware. The ATA's device ROM performs the configuration process and returns to the system firmware. Once the drive is configured, IPL can occur from the PCMCIA ATA drive like any other ATA drive.

# Chapter 23

# The Previous Chapter

The last chapter discussed the problems associated with loading the operating system from a PC Card. It also defined mechanisms used to determine whether a given PC Card is a bootable device, and the firmware support required to support booting from PC Cards.

# This Chapter

This chapter discusses the Execute-In-Place mechanism defined by PCMCIA that allows code to be executed directly from the card rather than copying files to and executing from system memory.

# The Next Chapter

The next chapter introduces the ExCA (QuickSwap) specification that defines a required set of hardware and software support that is intended to improve PC Card interoperability across platforms based on the Intel X86 architecture.

## The XIP Goals

Execute-In-Place (XIP) provides a mechanism for application programs to execute directly from PC Card memory. This eliminates the need to copy code from the PC Card into host memory before being executed, reducing the amount of system memory address space needed to load and execute a large application program. This is a particular concern in the DOS operating environment where memory address space is at a premium. Application programs written to support XIP could be supplied on a ROM-based PC Card or could be loaded from disk to a memory card (such as flash) and be executed directly from the PC Card.

Similar techniques, including the popular expanded memory specification (EMS), allow an application to reside in memory outside the memory address range that is addressable by DOS. Small portions (16KB pages) of these remote memory ranges are mapped into areas addressable by DOS, permitting them to be accessed. The EMS protocol defined in the Lotus/Intel/Microsoft (LIM) specification is supported by XIP and is called LXIP. Additionally, XIP defines support for applications designed to use extended memory (address space beyond 1MB) using Intel 80386 compatible addressing modes. This form of XIP is termed EXIP. A new type of XIP called SXIP (Simple XIP) is defined for systems with very limited paging mechanisms and small address space. The execution and read-only data images require no more than 64KB of address space.

# The XIP Software Hierarchy

The functions performed by XIP software includes:

- Setting up XIP partitions in PC Card memory.

- Establishing directories within PC Card memory.

- Copying XIP applications into the XIP partitions.

- Mapping the application within the processor's addressable space.

- Starting the XIP application execution.

- Providing services for the XIP application so that it can manage program execution.

## **XIP File Management**

XIP applications do not use the normal DOS File Allocation Table (FAT) or Flash File System (FFS). Instead, XIP applications use a dedicated software interface consisting of XIP utilities, XIP management software and socket services to map the PC Card memory into an XIP partition. The XIP software can only execute an XIP application from an XIP partition. An XIP partition can be set up in PC Card memory by utility programs. The PCMCIA specification details the organization and data structures required for partitions and directory entries.

### The XIP Loader

Once the dedicated XIP partition exists then an XIP application can be loaded into the PC Card's common memory address space within an XIP partition. The XIP directory also contained within PC Card memory is then updated to reflect the application's presence. An XIP application from the user perspective begins execution in the same way that a DOS application does (by typing the name of the executable file). In this case, however, an XIP loader is invoked when an executable XIP file is called. The XIP loader's task is to find the XIP application that resides within an XIP partition in PC Card memory. The loader searches for the application within the XIP directory, maps the application into system address space and starts the application.

# The XIP Device Drivers (API and Hardware Manipulation)

Once started, the application manages program execution by making the necessary calls to the XIP driver. The PCMCIA specification defines all of the functions needed by the application. The XIP device-driver functionality is split between a high-level driver (XIP.SYS) and a low-level driver (PCMCIA.SYS). The high-level driver is implemented as an installable device driver and provides all the services needed by the XIP application. This provides the XIP application's API. The low-level driver provide services for the high-level driver when it needs to access the memory-mapping hardware within the HBA. It can be installed as an installable device driver or included in the system's BIOS routines.

The intent of the split driver approach is to remove the details of the hardware interface from the high-level driver, making it easy to implement a generic XIP driver that can be used with any XIP-capable system. The system manufacturer then need only concentrate on developing the low-level driver used to manipulate the hardware (the same as the related socket service functions).

### LXIP

LXIP is compatible with the LIM 4.0 specification. This protocol requires that four separate 16KB blocks of contiguous memory address space, called page frames, be mapped into the processor's memory address space. Each of these four page frames must permit access within the PC Card's XIP application, which is also organized into 16KB blocks, called pages. An LXIP application is aware of this organization and interacts with the LXIP manager to access PC Card memory via the page frames.

A PCMCIA host bus adapter designed to support the LXIP capability must have the ability to map these four 16KB address ranges independently. The LXIP manager accepts requests from the XIP application and sets up access to PC Card memory via the socket services interface and the HBA.

#### **EXIP**

EXIP specifies the ability of applications to execute directly from PC Card memory when the memory card is mapped into the processor's extended address space (above 1MB). The EXIP manager determines where PC Card memory will be allocated in extended memory and programs the HBA to map the card into extended memory.

## SXIP

SXIP applications are quite small and cannot exceed more than 64KB of address space. In this respect they are similar to .com programs that execute in a single x86 memory segment. The entire program image is directly mapped into the processor's address space and no remapping or paging is performed.

# Part Five

ExCA(QuickSwap)

# Chapter 24

## The Previous Chapter

The previous chapter described the Execute-In-Place (XIP) functionality provided by PCMCIA that allows code to be executed directly from files stored on PC Cards. Three types of XIP were defined: one for small applications (SXIP), one based on expanded memory concepts (LXIP) and the other for applications using extended memory (EXIP).

# **This Chapter**

This chapter introduces the ExCA (QuickSwap) specification that defines a required set of hardware and software support, intended to improve PC Card interoperability across platforms based on Intel x86 architecture.

# The Next Chapter

The next chapter provides a sample PCMCIA host bus adapter. The adapter documented is the Cirrus Logic PD6722 designed for use in x86 PC-based systems.

## The ExCA Goal

The Intel ExCA (Exchangeable Card Architecture) specification provides specific HBA, PC Card, and software requirements for systems implementing DOS-based Intel x86 compatible systems. By defining minimum hardware and software requirements for these systems, Intel hopes to ensure PC Card compatibility across x86 systems implementing the ExCA standard.

The need for such a standard stems from the flexibility incorporated into the PCMCIA specification. The standard was designed to provide latitude for designers who are developing PCMCIA solutions over a wide range of PC and

non-PC platforms. However, this latitude, while achieving its goal, also creates a greater possibility of compatibility problems.

# **ExCA Scope**

In most respects, the ExCA specification defines a subset of the features within the PCMCIA standards, narrowing down the implementation possibilities and reducing the risk of PC Cards and systems being developed that are incompatible with one another. Additionally, ExCA defines some system characteristics not specified in the PCMCIA standard. The ExCA specification describes the minimum capabilities of the following items:

- The ExCA Host Bus Adapter

- Socket Services

- Card Services

- PC Cards (both memory-only and memory and I/O)

ExCA also encompasses a three phase compliance test, including socket hardware functional testing, system software functional testing and system integration testing.

This chapter highlights the ExCA specification's features. Refer to the ExCA specification for complete details.

# **ExCA Host Bus Adapter Requirements**

Host bus adapter requirements fall into the following categories:

- Address Mapping (memory and I/O)

- Interrupt Support

- System Power

- PC Card Insertion and Removal

- Event WakeUp (i.e. ring indicate when system is in sleep mode)

# Address Mapping (memory and I/O)

Specific requirements exist for ExCA compliant host bus adapters to ensure that address windowing capability provides the features needed in DOS-based operating environments. Address mapping features are described for

# Chapter 24: ExCA (QuickSwap)

ExCA compliant sockets for both memory sockets and Memory or I/O sockets.

## **Memory Address Mapping**

Each socket must include a minimum of four memory windows that can be acquired and used by a socket. This requirement provides support for expanded memory (L-XIP) in which four separate 16KB address ranges must be acquired from system memory and mapped to the PC Card. Support must also exist for each socket to provide a fifth window, thereby allowing access to attribute memory when necessary.

Each memory window must support system address capabilities for both real mode (within the first 1MB of memory address space) and protected mode (above 1MB of memory address space) operation. Furthermore each ExCA memory address window must have the following capabilities and characteristics:

- windows are mappable anywhere between 256KB to 16MB (in host space)

- minimum window size of 4KB

- maximum window size of 256KB (real mode)

- maximum window size of 8MB (protected mode)

- window size can be any 4KB increment (4, 8, 12, 16, 20 KB .....) or may be a power of two size (4, 8, 16, 32, 64 KB ......)

Consistent with the PCMCIA specification, memory windows are not allowed to overlap in system address space, unless use of the address range is time multiplexed.

# I/O Address Mapping

ExCA requires that at least two I/O windows be implemented per socket. Characteristics of ExCA I/O windows include:

- minimum window size of 1 byte

- maximum windows size of 256 bytes

- window size must be power of two (1, 2, 4, 8, 16, 32 .... bytes)

Note that no remapping of the system I/O address is required. Addresses are directly mapped from system address locations to the same locations on the PC Card.

ExCA does not support overlapping I/O windows without time multiplexing them, as is required for overlapping memory windows. This means that no support need exist for the INPACK# signal on ExCA compliant adapters.

## Interrupt Support

ExCA adapters generate a status change interrupt for all card status change events defined in the PCMCIA specification and they redirect or steer PC Card interrupts to system IRQ lines as required.

## Status Change Interrupt

ExCA adapters generate a single status change interrupt for card events from all adapter sockets. Software must have the ability to globally select which type of card events generate a status change interrupt. Additionally, individual events can be masked at the socket, providing selection of specific events that generate a status change interrupt on a per socket basis. Support must also exist for enabling and disabling the status change interrupt under software control.

The adapter captures all status change events reported by each socket so that software can determine which socket encountered the status change event. The actual state of the status change signals from each socket can also be read directly from the adapter.

Status change events from I/O cards are reported when an I/O card asserts its status change pin. Status change information must be read directly from the I/O card's configuration register (pin replacement register).

# **PC Card Interrupts**

A PC Card interrupt must be steerable to any available system interrupt. Availability depends on the host system implementation as listed in table 24-1.

ExCA compliant systems must ensure that at least one interrupt is available for standard communications and local area networks (LANs). In other words, the system must supply at least one interrupt request line from each bullet list that follows.

# Chapter 24: ExCA (QuickSwap)

Table 24-1. Interrupts Potentially Available For Use By PC Cards

| Systems with One Inter-<br>rupt Controller | Systems with Two Interrupt Control |        |

|--------------------------------------------|------------------------------------|--------|

| IRQ 2                                      | IRQ 2/9                            | IRQ 10 |

| IRQ 3                                      | IRQ 3                              | IRQ 11 |

| IRQ 4                                      | IRQ 4                              | IRQ 12 |

| IRQ 5                                      | IRQ 5                              | IRQ 14 |

| ,IRQ7                                      | IRQ 7                              | IRQ 15 |

Standard Communications Interrupts (Serial Port)

- IRQ 3

- IRQ 4

### Standard LAN Interrupts

- IRQ 5

- IRQ 7

- IRQ 10

- IRQ 11

- IRQ 15

Note that ExCA recommends that all interrupts listed in table 24-1 be supported by the adapter. However, a given implementation may choose to use only a subset since the system design likely uses some of the interrupts.

Interrupt sharing support is system dependent. Systems based on ISA host buses do not support interrupt sharing, while systems based on Micro Channel and EISA can share interrupts. Micro Channel and EISA devices use level sensitive interrupt triggering to support sharing, thus cards that support only the PCMCIA specified pulse-mode interrupts will not behave according to the level sensitive triggering protocol. ExCA compliant adapters must support level-mode interrupts from the PC Card, while pulse-mode support is optional.

# **System Power Requirements**

ExCA systems must supply minimum power requirements as indicated in the ExCA specification. PCMCIA compliant PC Cards requiring more power than specified by the ExCA specification may not operate correctly when installed in sockets that are ExCA compliant. Additionally, ExCA compliant systems need not provide separate programmable voltages for Vpp1 and Vpp2. Refer to the ExCA specification for actual power requirements. The voltage supply combinations that must be provided at the socket include those listed in table 24-2.

Vcc Vpp1 Vpp2 required 0v 0v0v5v 5v 5v required 5v 12v 12v required optional 5v 0v

Table 24-2. ExCA Voltage Requirements

## PC Card Insertion/Removal

The ExCA specification defines the sequence of events, interface signal status, Vcc and Vpp levels and critical timing delays for PC Card insertion and removal. The ExCA specification supports both cold socket insertion (recommended) and warm insertion (not recommended). Hot socket insertion of PC Cards is not supported by the ExCA. Table 24-3 defines the difference between cold, warm and hot PCMCIA sockets.

| Socket State | Vcc and Vpp | Address State<br>at Signal<br>Contact | Data State at<br>Signal Contact | Control Signal<br>State at Signal<br>Contact |

|--------------|-------------|---------------------------------------|---------------------------------|----------------------------------------------|

| Cold Socket  | Off         | High Z or 0v                          | High Z or 0v                    | High Z or 0v                                 |

| Warm Socket  | On          | High Z or 0v                          | High Z or 0v                    | High Z or 0v                                 |

| Hot Socket   | On          | Driven Active                         | Driven Active                   | Driven Active                                |

Table 24-3. State of Socket When PC Card is Inserted

# Chapter 24: ExCA (QuickSwap)

#### **Card Insertion**

The ExCA specification defines the sequence of events and minimum time duration for these events when a card is inserted into a socket. The sequence of events is listed below.

- Card inserted into socket (both CD1# and CD2# asserted)

- 2. Adapter applies Vcc

- Adapter asserts reset to PC Card

- 4. Adapter removes reset and PC Card begins initialization

- 5. Initialization completes within 20 ms or else deasserts READY

- Client driver polls READY to detect when PC Card is ready to be accessed.

#### **Card Removal**

The ExCA specification also defines the sequence of events that are recommended when the PC Card is removed from the socket as listed below. Note that when a PC Card is removed from the system, the socket interface may be active.

- Adapter detects card removal (CD1# and/or CD2# deasserted)

- 2. Adapter ceases to drive active signals to the interface (address, data and control signals go to high impedance state or 0v)

- Vcc removed from the socket (not required if warm socket insertion is supported)

Note that the adapter detects that a card is being removed before any of the other interface or power pins lose contact with the socket (because the Card Detect pins are shortest). Next, the adapter releases the interface by tri-stating the address, data and control lines, (which are the intermediate length signal pins), and finally removes power to the Vcc pins (which are the longest pins). As the PC Card is removed it is still in contact with the signals pins and power pins long after they are disabled by the adapter.

### **ExCA Socket Services**

The ExCA specification defines a minimum subset of socket services functions that are required for ExCA compliance. Table 24-4 lists the socket services functions and notes those that are required versus optional.

Table 24-4. Socket Services Functions Required/Optional for ExCA Compliant Systems

| Function        | Required ? |

|-----------------|------------|

| GET_ADP_CNT     | Yes.       |

| GET_SS_INFO     | Yes        |

| INQ_ADAPTER     | Yes        |

| GET_ADAPTER     | Yes        |

| SET_ADAPTER     | Yes        |

| INQ_WINDOW      | Yes        |

| GET_WINDOW      | Yes        |

| SET_WINDOW      | Yes        |

| GET_PAGE        | Yes        |

| SET_PAGE        | Yes        |

| INQ_SOCKET      | Yes        |

| GET_SOCKET      | Yes        |

| SET_SOCKET      | Yes        |

| GET_STATUS      | Yes        |

| RESET_SOCKET    | Yes        |

| INQ_EDC         | No         |

| GET_EDC         | No         |

| SET_EDC         | No         |

| START_EDC       | No         |

| PAUSE_EDC       | No         |

| RESUME_EDC      | No         |

| STOP_EDC        | No         |

| READ_EDC        | No         |

| GET_VENDOR_INFO | No         |

| ACK_INTERRUPT   | Yes        |

| PRIOR_HANDLER   | No         |

| SS_ADDR         | No         |

| ACCESS_OFFSETS  | No         |

| VEND_SPECIFIC   | No         |

| CARD_SERVICES   | Yes        |

Note that the EDC and vendor specific functions are optional for ExCA compliant socket services. The implementation and definition of the required socket services functions are compliant with the PCMCIA socket services standard.

# Chapter 24: ExCA (QuickSwap)

## **ExCA Card Services**

ExCA compliant systems must support card services; but, like socket services not every card services function is required. Table 24-5 lists the card services functions that are required.

Table 24-5. Card Services Functions Required/Optional For ExCA Compliance

| Function                  | Required ? |

|---------------------------|------------|

| Client Services Functions |            |

| GetCardServicesInfo       | Partial    |

| RegisterClient            | Yes        |

| DeregisterClient          | Yes        |

| GetStatus                 | Yes        |

| ResetCard                 | Yes        |

| SetEvenMask               | Yes        |

| GetEvenMask               | Yes        |

| Resource Management Func  | tions      |

| RequestIO                 | Yes        |

| ReleaseIO                 | Yes        |

| RequestIRQ                | Yes        |

| ReleaseIRQ                | Yes        |

| RequestWindow             | Yes        |

| ReleaseWindow             | Yes        |

| ModifyWindow              | Yes        |

| MapMemPage                | Yes        |

| RequestSocketMask         | Yes        |

| ReleaseSocketMask         | Yes        |

| RequestConfiguration      | Yes        |

| GetConfigurationInfo      | Yes        |

| ModifyConfiguration       | . Yes      |

| ReleaseConfiguration      | Yes        |

| Bulk Memory Services Func | tions      |

| OpenMemory                | No         |

| ReadMemory                | No         |

| WriteMemory               | No         |

| CopyMemory                | No         |

| RegisterEraseQueue        | No         |

| CheckEraseQueue           | No         |

| Function                       | Required ? |

|--------------------------------|------------|

| DeregisterEraseQueue           | No         |

| CloseMemory                    | No         |

| Client Utilities Functions     |            |

| GetFirstTuple                  | Yes        |

| GetNextTuple                   | Yes        |

| GetTupleData                   | Yes        |

| GetFirstRegion                 | No         |

| GetNextRegion                  | No         |

| GetFirstPartition              | No         |

| GetNextPartition               | No         |

| Advanced Client Services Funct | ions       |

| ReturnSSEntry                  | Yes        |

| MapLogSocket                   | Yes        |

| MapPhySocket                   | Yes        |

| MapLogWindow                   | Yes        |

| MapPhyWindow                   | Yes        |

| RegisterMTD                    | No         |

| RegisterTimer                  | Yes        |

| SetRegion                      | No         |

| ValidateCIS                    | Yes        |

| RequestExclusive               | Yes        |

| ReleaseExclusive               | Yes        |

| GetFirstClient                 | Yes        |

| GetNextClient                  | Yes        |

| GetClientInfo                  | Yes        |

| AddSocketServices              | Ņo         |

| ReplaceSocket Services         | No         |

| VendorSpecific                 | No         |

| AdjustResourceInfo             | Yes        |

| AccessConfigurationRegister    | No         |

### **ExCA PC Cards**

ExCA recommends which tuples an ExCA compliant PC Card should implement. Table 24-6 below lists the recommended tuples for memory and I/O PC Cards. The lower portion of the table lists three tuples that might contain information needed by system initialization code or peripheral installation software for determining if a PC Card should be installed and configured during POST (Power-On Self Test) prior to loading the operating system. This capability is needed primarily for those devices that must be used to load and install the operating system.

Memory Cards? I/O Cards? Tuples Recommended by ExCA **Device Information** Yes Yes Yes Yes Level 1 Version/Product Information Yes Yes Configuration Yes Yes Configuration Table Entry JEDEC Device ID Yes No Device Geometry Information (flash) Yes No Recommended for bootable PC Cards Card Manufacturer ID Yes Yes Function ID Yes **Function Extension** Yes Yes

Table 24-6. Tuples Recommended by the ExCA Specification

# PC Card Event WakeUp

Systems implementing power conservation modes, such as suspend or sleep, may want to wake the system up if some critical event occurs at the PC Card. Events, such as a call to a modem, could be used to wake the system up and return to normal full power operation so that the event can be processed. Currently the PCMCIA specification (release 2.1) does not define an event wakeup procedure, and in its absence, ExCA defines the following optional definition for event wakeup.

Two events can cause event wakeup in an ExCA compliant system:

- · Ring Indication from a modem or fax

- remote power up from a LAN card

# Chapter 24: ExCA (QuickSwap)

ExCA compliant HBAs and PC Cards use socket pin 63 (Status Change) for event wakeup, replacing either the READY, Write Protect or Battery Voltage Change status change indication on the PC Card. The PC Card indicates its support of event wakeup via the CIS.

The Configuration Table Entry tuple identifies the card's capability for using event wakeup via pin 63. The configuration entry tuple contains a miscellaneous features field that can be used to specify which status change indicators are supported by the card and is used to indicated which status change event that the event wakeup mechanism uses. The host bus adapter is programmed to direct the status change indication to the power management interrupt, which requests that the system return to full power operation.

# Part Six

# An Example HBA

# Chapter 25

#### The Previous Chapter

The previous chapter introduces the ExCA (QuickSwap) specification that defines a required set of hardware and software support, intended to improve PC Card interoperability across platforms based on Intel x86 architecture.

#### **This Chapter**

This chapter provides an overview of a sample PCMCIA host bus adapter (The Cirrus Logic CL-PD6722) used in Intel x86 implementations for either an original PC or ISA compatible host bus.

#### Introduction to the CL-PD6722

This chapter is intended as a brief look at an actual PCMCIA host bus adapter. The Cirrus Logic CL-PD6722 was chosen as the example adapter for several reasons. First, the Intel 82365 PCMCIA adapter chip is currently implemented in more systems that any other, and the CL-PD6722 is register compatible with the Intel chip, with a few minor exceptions. The second reason is that it includes considerably more functionality than the Intel chip.

The CL-PD6722 controls two PCMCIA sockets via a single 208-pin PQFP. Features of the CL-PD6722 include the following:

- PCMCIA 2.1 and JEIDA 4.1 Compliant

- Intel 82365SL (Step A) compatible register set, ExCA compliant

- ISA host bus interface

- Dual socket interface

- Automatic Low-Power Dynamic Mode

- Programmable Suspend Mode for power conservation

- Five programmable memory windows per socket

- Two programmable I/O windows per socket

- 8-bit or 16-bit host bus interface

- ATA disk interface support for small form-factor drives

- DMA support

- Mixed-Voltage operation (3.3v or 5v) operation

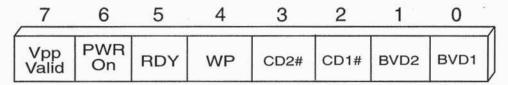

#### Socket Power Control

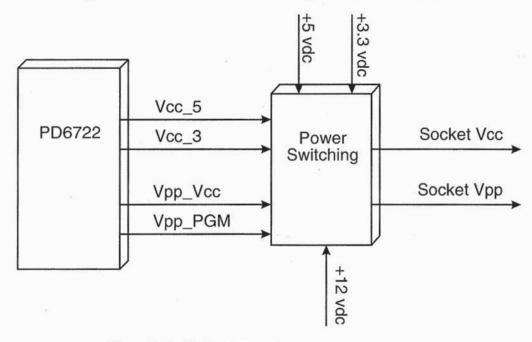

The CL-PD6722 uses the PowerGood signal from the system's power supply as its reset. When PowerGood transitions from low to high the CL-PD6722 leaves the reset state and begins operation. Power to the socket is controlled by chip outputs that go to power switching devices. As shown in figure 25-1, the CL-PC6722 has four output signals per socket that control power to the socket as follows:

- Vcc\_5 when asserted 5v is applied to socket Vcc

- Vcc\_3 when asserted 3.3v is applied to socket Vcc

- Vpp\_Vcc when asserted Vcc is applied to socket Vpp1.

- Vpp\_PGM when asserted the programming voltage (12v) is applied to socket Vpp1.

Internal registers determine which of these signals will be asserted and when.

Figure 25-1. CL-PD6722 Socket Power Control Signals

## Chapter 25: An Example HBA —The CL-PD6722

#### Vcc Control

In PCMCIA 2.1 compliant systems, Vcc to the socket must always be 5v, but can be switched to 3.3v if the PC Card indicates the ability to operate at 3.3v via the CIS. If 3.3v operation is supported, software will write to Miscellaneous Control 1 register, specifying that Vcc should be switched to 3.3v. (Note that the CL-PD6722 provides limited support for Vcc sensing and can be used in new designs that incorporate the low voltage connectors. Contact Cirrus Logic for details.)

The CL-PD6722 supports two methods of applying Vcc to the socket:

- Vcc control via the client driver, card service and socket services software chain when a card is detected.

- Automatic Vcc control via the CL-PD6722 controller

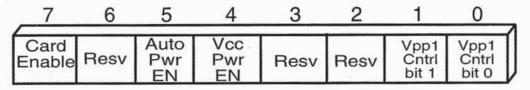

When a card is inserted into the socket, the -CD pins are asserted and the adapter detects the card's presence. When autopower mode is not selected, the adapter waits to be commanded by the software before applying Vcc to the socket. Software must set bit four in the Power Control register (Refer to figure 25-2) to enable power to the socket. The adapter responds by asserting the Vcc\_5 signal.

If bit five is set during system initialization, the adapter automatically supplies Vcc to the adapter (asserts Vcc\_5) when it detects the presence of a card. Vcc is automatically removed from the card when the card is removed. Note that power is removed based on timing parameters specified in the ExCA specification.

Figure 25-2. The Power Control Register

#### Vpp1 Control

Bits zero and one of the Power Control register determine whether Vcc (5v or 3.3 v), 12v, or zero volts is applied to the Vpp1 pin. (Refer to table 25-1)

| Bit 1 | Bit 0 | VPP_PGM    | VPP_VCC    | Socket Vpp1               |

|-------|-------|------------|------------|---------------------------|

| 0     | 0     | Deasserted | Deasserted | zero volts                |

| 0     | 1     | Deasserted | Asserted   | selected Vcc (3.3v or 5v) |

| 1     | 0     | Asserted   | Deasserted | +12v                      |

| 1     | 1     | Deasserted | Deasserted | zero volts                |

Table 25-1. Socket Vpp Control

#### **PC Card Data Transfers**

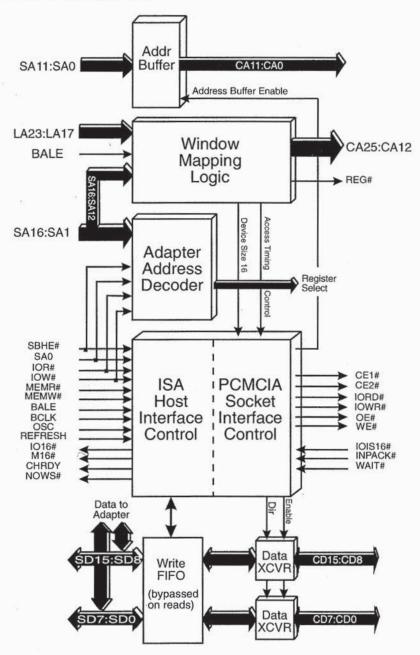

The adapter monitors ISA host bus activity to see if the bus cycle is intended for it or a PC Card installed in one of its sockets. Figure 25-3 shows the signals and functional blocks involved in transferring bus cycles to the target PC Card. Note that figure 25-3 shows a single socket interface to simplify the illustration. In reality, the socket signals shown are duplicated for the second socket.

The adapter must decode the address when an ISA bus cycle is run to determine if either a local access is being made to one of its registers or whether the access is to a PC Card. PC Card accesses are determined via the window address registers. If an ISA access is made to an address location that falls within the address window programmed for a the PC Card, then the adapter knows that the PC Card is being accessed and starts a data transfer either to or from the card depending on the state of the ISA read/write command lines. In essence, the HBA decodes addresses like other ISA adapters. The HBA performs the decode to determine if the transaction is for it (an HBA register) or one of its sockets.

The CL-PD6722 uses a First In First Out serial memory (FIFO) to store up to four write operations. When a write occurs from the host ISA bus, the CL-PD6722 stores the write in the FIFO and completes the operation in zero ISA wait states. The adapter then runs the socket access to the target PC Card to complete the write transfer. In this way, write operations to PC Cards al-

# Chapter 25: An Example HBA —The CL-PD6722

ways complete at zero waits states until the FIFO fills up. Note that the FIFO is bypassed on read transfers.

Figure 25-3. Basic Functional Blocks Used During Data Transfers

The CL-PD6722 contains two timing register sets each consisting of three registers that control transfer timing:

- · Setup Timing register

- · Command Timing register

- Recovery Timing register

These registers provide very flexible transaction timing when accessing PC Cards. Refer to the CL-PD6722 data book for details regarding these registers.

#### **Address Window Mapping**

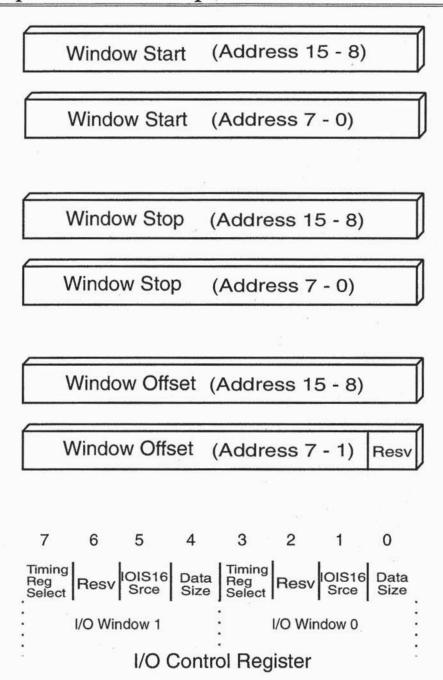

The CL-PD6722 has seven window address registers for each socket: Five memory window registers and two I/O window register. Associated with each register is the transfer speed of the devices that respond within the window.

#### **Memory Interface**

The memory window register is comprised of six 8-bit registers containing the following information (refer to figure 25-4):

- Lower byte of window start address (LA19:LA17; SA16:SA12). Note that

address line 12 is the smallest address used to define a memory address

window. This supports the ExCA's requirement that windows start on

4KB boundaries. The lower 12-bits of the address (SA11:SA0) go directly

to the socket via a buffer.

- Upper portion of window start address (LA23:LA20). The window start address reflects the maximum address capability of the ISA host bus (16MB).

- Lower byte of window stop (end) address (LA19:LA17; SA16:SA12).

Note that memory windows must also end on even 4KB boundaries, making the smallest memory window 4KB.

- Upper portion of window stop (end) address (LA23:LA20)

- Lower byte of window offset (CA19:CA12). Note that the offset is comprised of the Card Address value that is added to the ISA address, permitting the card address to appear anywhere within the PC Card's 64MB of address space.

- Upper portion of window offset (CA25:CA20).

# Chapter 25: An Example HBA —The CL-PD6722

The address register also contains bits that determine characteristics about the specified range of addresses. These characteristics include:

- Data Size Specifies whether access should be made to devices based on 8-bit or 16-bit addressing mode (depends on host bus size).

- Access Time (Timer Select) The CL-PD6722 incorporates two timing register sets that determine the cycle time of the devices that are mapped into the address window.

- Type of Window (-REG) Determines whether the window is used to access attribute memory or common memory.

- Write Protect (WP) specifies whether the memory within the window address range should be write protected. Writes to address within the window are inhibited if WP is set.

Figure 25-4. Registers Comprising a Single Memory Address Window

#### I/O Interface

I/O devices are mapped through the I/O window address registers. Each socket contains two I/O window registers each comprised of seven one byte registers as follows (refer to figure 25-5):

- Upper byte of window start address (SA15:SA8)

- Lower byte of window start address (SA7:SA0)

- Upper byte of window stop (end) address (SA15:SA8)

- Lower byte of window start address (SA7:SA0)

- Upper byte of window offset register (CA15:CA8)

- Lower byte of window offset register (CA7:CA1)

- Control bits for both I/O windows

Note that the I/O start address can begin and end on any byte boundary and can be any length. ExCA specifies constraints regarding I/O address window size and start addresses that compliant software should observe. Since the ISA host bus supports a maximum of 64KB of I/O address space, only 15 address bit are used. The offset capability allows software to map two devices at the same system address space and offset or remap the system addresses to separate locations with the PC Cards I/O address space.

Note that the characteristics of both I/O windows is controlled via the I/O window control register. The characteristics include:

- Data Size (data size and -IOIS16) An I/O device can be either an 8-bit or 16-bit device. The size can be programmed via the data size bit or can be dynamically determined by the PC Card via the -IOIS16 signal.

- Cycle Timing (Timing Select) the access timing of the devices responding within the window is determined by the value of a timing register set. The timing select bit determines which timer set should be used.

# Chapter 25: An Example HBA —The CL-PD6722

Figure 25-5. Register Comprising a Single I/O Address Window

#### **Status Change Reporting**

Status change interrupts are typically reported via a system interrupt whenever a status change event occurs. A single status change interrupt is used to report status changes for all sockets. Status change events that can result in a status change interrupt include:

#### For Memory Cards:

- Battery Dead Detection

- Battery Low Warning

- Change in Ready/Busy status

- Card Detect Change

#### For I/O Cards:

Status Change Pin is asserted - The I/O card's configuration registers must be read to determine which of the previously mentioned status changes have occurred.

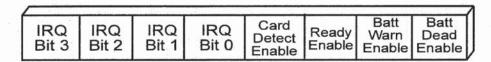

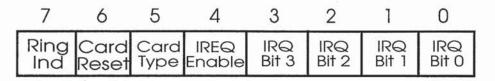

The CL-PD6722 reports a status change (also called management) interrupt over the one of the system IRQ lines specified in the Management Interrupt Configuration register (refer to figure 25-6). The upper four bits of the register determine which IRQ line the status change should be reported over, while the lower four bits determine which of the status change events should result in an interrupt being reported. These lower four bits act as a global mask to eliminate one or more of the status change events from being reported by the adapter.

Figure 25-6. Management Interrupt Configuration Register

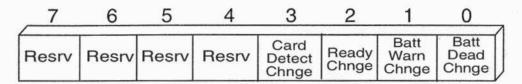

System software having been notified of a status change must determine which status change caused the interrupt. The Card Status Change register indicates the source of the status change. (Refer to figure 25-7.)

# Chapter 25: An Example HBA —The CL-PD6722

Figure 25-7. Card Status Change Register