"The 'must-have' PC architecture reference set." —PC Magazine's "Read Only" column

# PCMCIA SYSTEM ARCHITECTURE

**16-BIT PC CARDS**

## SECOND EDITION

MINDSHARE, INC. Don Anderson

PC SYSTEM ARCHITECTURE S E R I E S

# PCMCIA System Architecture 16-Bit PC Cards

Second Edition

MindShare, Inc. Don Anderson

## ADDISON-WESLEY

Boston • San Francisco • New York • Toronto • Montreal London • Munich • Paris • Madrid Capetown • Sydney • Tokyo • Singapore • Mexico City

> Toshiba\_Apricorn 1006-0002 IPR2018-01067

i

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial capital letters or all capital letters.

The author and publisher have taken care in preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

#### Library of Congress Cataloging-in-Publication Data

```

Anderson, Don, 1953–

PCMCIA system architecture : 16-bit cards / MindShare, Inc., Don

Anderson.

p. cm.

Includes index.

ISBN 0-201-40991-7 (alk. paper)

1. PCMCIA cards (Microcomputers) 2. Computer architecture.

I. MindShare, Inc. II. Title.

TK7895.P38A63 1995

004.6'4--dc20 95-44074

CIP

```

Copyright © 1995 by MindShare, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

Sponsoring Editor: Keith Wollman Production Coordinator: Deborah McKenna Cover design: Barbara T. Atkinson Set in 10 point Palatino by MindShare, Inc.

Text printed on recycled and acid-free paper. ISBN 0201409917

7 8 9 101112 MA 06 05 04 03

7th Printing May 2003

The publisher offers discounts on this book when ordered in quantity for special sales. For more information, please contact: Pearson Education Corporate Sales Division, One Lake Street, Upper Saddle River, NJ 07458, (800) 382-3419, corpsales@pearsontechgroup.com For Doris and Darrel Anderson, my mother and father.

.

iii

## The PC System Architecture Series

#### MindShare, Inc.

Please see our web site (http://www.awprofessional.com/series/mindshare) for more information on these titles.

AGP System Architecture: Second Edition 0-201-70069-7

CardBus System Architecture 0-201-40997-6

FireWire® System Architecture: Second Edition 0-201-48535-4

InfiniBand System Architecture 0-321-11765-4

ISA System Architecture: Third Edition 0-201-40996-8

PCI System Architecture: Fourth Edition 0-201-30974-2

PCI-X System Architecture 0-201-72682-3

PCMCIA System Architecture: Second Edition 0-201-40991-7

Pentium<sup>®</sup> Pro and Pentium<sup>®</sup> II System Architecture: Second Edition 0-201-30973-4

Pentium<sup>®</sup> Processor System Architecture: Second Edition 0-201-40992-5

Plug and Play System Architecture 0-201-41013-3

Protected Mode Software Architecture 0-201-55447-X

Universal Serial Bus System Architecture: Second Edition 0-201-30975-0

HyperTransport<sup>™</sup> System Architecture 0-321-16845-3

## Contents

| About This Book                                                  |   |

|------------------------------------------------------------------|---|

| The MindShare Architecture Series                                | 1 |

| Organization of This Book                                        | 2 |

| Part One: Introduction to PCMCIA                                 | 2 |

| Part Two: Socket and Host Bus Adapter Design                     | 2 |

| Part Three: PC Card Design                                       | 3 |

| Part Four: PCMCIA Software                                       | 4 |

| Part Five: ExCA (QuickSwap)                                      | 5 |

| Part Six: An Example HBA                                         | 5 |

| Appendices                                                       | 6 |

| Who Should Read This Book                                        |   |

| Prerequisite Knowledge                                           | 6 |

| Documentation Conventions                                        | 6 |

| Hex Notation                                                     |   |

| Binary Notation                                                  |   |

| Decimal Notation                                                 |   |

| Signal Name Representation                                       | 7 |

| Identification of Bit Fields (logical groups of bits or signals) | 7 |

| CarBus                                                           | 8 |

| We Want Your Feedback                                            | 8 |

| E-Mail/Phone/FAX                                                 | 8 |

| Mailing Address                                                  |   |

## Part One Introduction to PCMCIA

## **Chapter 1: The Problem**

| The Mobile Computing Environment        | .11 |

|-----------------------------------------|-----|

| Small Form-Factor I/O Expansion Devices | .12 |

## **Chapter 2: The PCMCIA Solution**

| The Virtual Floppy Drive Subsystem        | 13 |

|-------------------------------------------|----|

| The Lack of a Standard Memory Card Design |    |

| Emergence of PCMCIA                       | 14 |

| Support for I/O-based PC Cards Added | .15 |

|--------------------------------------|-----|

| The PC Card Standard                 | .15 |

| Summary of PCMCIA Releases           | .17 |

## **Chapter 3: Tying the Pieces Together**

| Overview                                                         | 21 |

|------------------------------------------------------------------|----|

| The PC Card                                                      | 22 |

| Interoperability: PCMCIA Sockets and The PCMCIA Host Bus Adapter | 25 |

| Initializing the Host Bus Adapter: Socket Services               | 27 |

| Configuring the Card: Card Services & Enablers                   |    |

| Accessing PC Cards After Configuration                           | 29 |

| The Metaformat                                                   |    |

| Card Types and Dimensions                                        | 35 |

|                                                                  |    |

## Part Two

## Socket and Host Bus Adapter Design

## **Chapter 4: The Physical Specifications**

| Card Types I, II, and III         |    |

|-----------------------------------|----|

| Extended Card Types I and II      |    |

| The Card and Socket Connectors    |    |

| Card and Socket Keying            | 40 |

| Pin Length                        |    |

| Environmental Characteristics     |    |

| Connector Environmental Standards |    |

| PC Card Environmental Standards   | 44 |

| Overview                          | 47 |

|                                   |    |

## **Chapter 5: The Memory-Only Socket Interface**

| The Memory Interface                         |  |

|----------------------------------------------|--|

| Card Power                                   |  |

| Release 2.x Socket                           |  |

| Low-Voltage Socket                           |  |

| Voltage Sense Pins (not used in 2.x systems) |  |

| The Power-Up Sequence                        |  |

| Vpp1 and Vpp2                                |  |

| Address Signals                              |  |

| Data Lines                                   |  |

|                                              |  |

## Contents

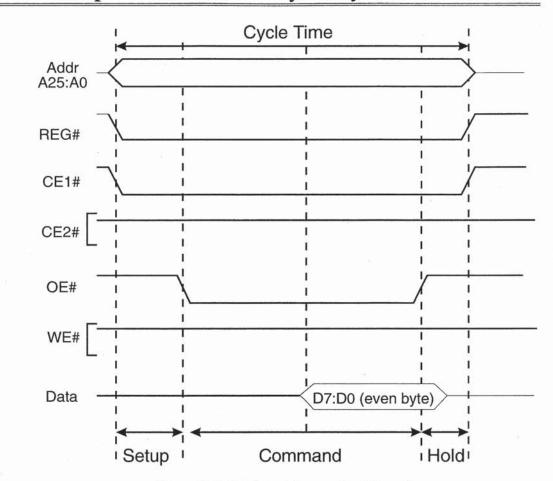

| PC Memory Card Transaction Definition               | 59 |

|-----------------------------------------------------|----|

| PC Memory Card Status Signals                       |    |

| Card Detection                                      | 61 |

| Ready Status                                        | 62 |

| Write-Protect Status                                | 62 |

| Low Battery Detection                               | 63 |

| Bus Cycle Control                                   | 64 |

| Card Reset                                          | 64 |

| PC Card Memory Transfers                            |    |

| Attribute Memory Read Transfers                     |    |

| Attribute Memory Write Transfers                    |    |

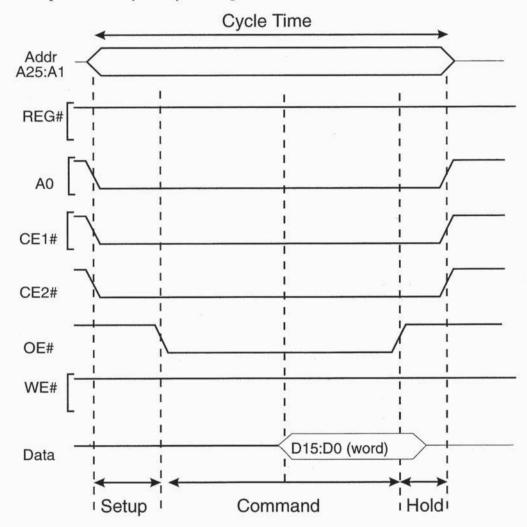

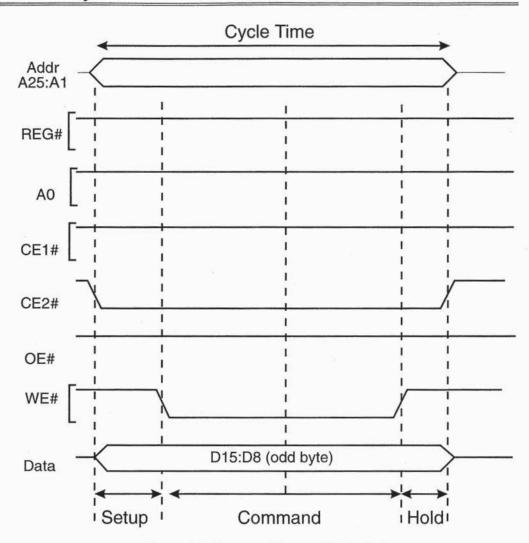

| Common Memory Read/Write Transfers                  | 68 |

| Common Memory Read or Write Transfer (16-Bit Hosts) | 68 |

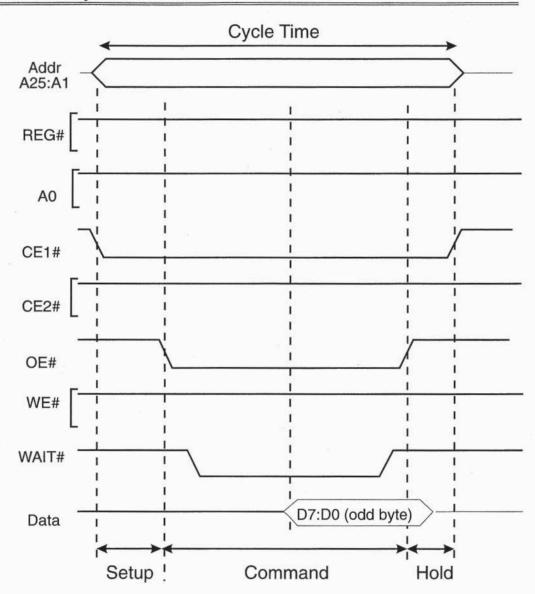

| Common Memory Read or Write Transfer (8-Bit Hosts)  | 70 |

| Common Memory Read/Write Timing with Wait           |    |

## Chapter 6: The Memory or I/O Interface

| Overview                                     | 74 |

|----------------------------------------------|----|

| The I/O Socket Interface                     | 74 |

| PC Memory or I/O Card Transaction Definition | 77 |

| The IOIS16# Pin                              | 78 |

| The IREQ# Pin                                | 78 |

| The INPACK# Pin                              | 78 |

| The STSCHG# Pin                              | 78 |

| The SPKR# Pin                                | 79 |

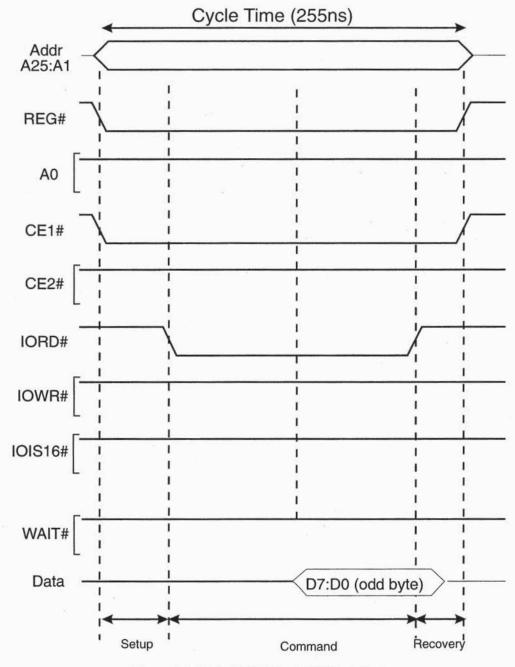

| I/O Transfers                                | 79 |

| Single Byte Access to/from 8-Bit I/O Devices | 80 |

| Word Access to/from 8-Bit I/O Devices        |    |

| Byte Accesses to/from 16-Bit Register        | 82 |

| Word Accesses to/from 16-Bit I/O Registers   |    |

## Chapter 7: The DMA Interface

| Background                            |  |

|---------------------------------------|--|

| Review of PC Compatible DMA Transfers |  |

| A DMA Example                         |  |

| DMA Channels Supported by ISA         |  |

| The DMA Socket Interface              |  |

| The DREQ# Pin                         |  |

| The DACK/REG# Pin                     |  |

| The TC Pin                            |  |

|                                       |  |

vii

| DMA with PC Card                    |  |

|-------------------------------------|--|

| DMA Transfer Timing (PC Compatible) |  |

| DMA Bus Cycle                       |  |

| Changes to Socket Services          |  |

| Changes to Card Services            |  |

## **Chapter 8: The ATA Interface**

| The ATA Interface                               |  |

|-------------------------------------------------|--|

| The ATA Interface                               |  |

| Differences Between Standard ATA and PCMCIA ATA |  |

| ATA System Resource Requirements                |  |

| Supporting Two Drives                           |  |

## **Chapter 9: The AIMS Interface**

| The AIMS Interface           |  |

|------------------------------|--|

| The AIMS Register Set        |  |

| The Block Transfer           |  |

| The AIMS Commands            |  |

| Accessing the AIMS Registers |  |

## Chapter 10: The PC Card Host Bus Adapter

| Introduction                                                |     |

|-------------------------------------------------------------|-----|

| Host Bus Adapter Functions                                  | 115 |

| The Socket Interface                                        |     |

| Maximum Number of HBAs                                      |     |

| Maximum Number of Socket Per HBA                            |     |

| Data Buffers / Transceivers                                 |     |

| Card Detection                                              |     |

| Power Switching                                             |     |

| Vcc Power Controls                                          |     |

| Vcc and 2.1 Compliant HBAs                                  |     |

| Vcc and Low Voltage Sockets                                 |     |

| Vpp1 and Vpp2 Control                                       |     |

| Address Translation                                         |     |

| Memory Address Mapping                                      |     |

| Direct Mapping                                              |     |

| Remapping the Host Address to PC Cards with Fixed Addresses |     |

| System Address Space Smaller Than Socket Address Space      |     |

| System Address Space Larger Than Socket Address Space       |     |

• •

## Contents

| Memory Address Windows                                |  |

|-------------------------------------------------------|--|

| Overlapping Memory Windows                            |  |

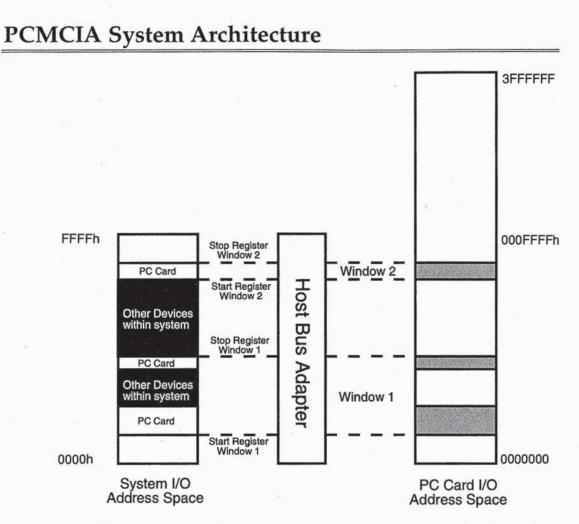

| I/O Address Mapping                                   |  |

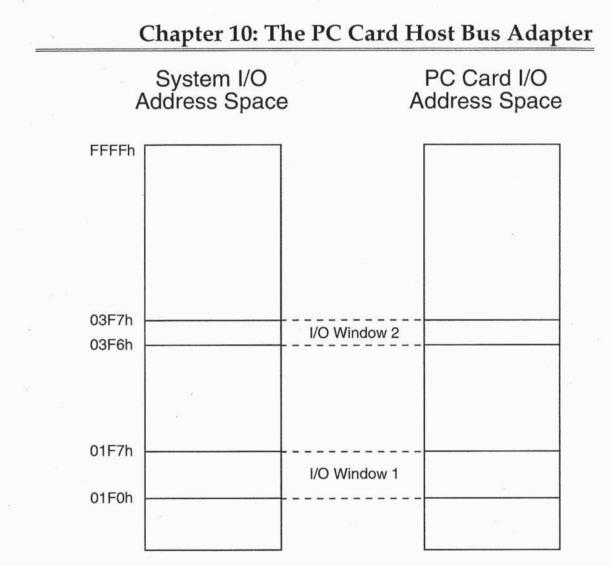

| Direct Mapped I/O Addresses                           |  |

| Overlapping I/O Windows                               |  |

| Other Information Associated with Address Windows     |  |

| Socket Transfer Timing and Control                    |  |

| Interface Control                                     |  |

| Socket Access Timing                                  |  |

| Stretching Socket Access Timing                       |  |

| Word or Byte Access                                   |  |

| PC Card I/O Device Size (IOIS16#)                     |  |

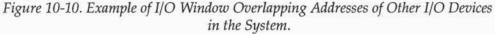

| Card Interrupt Steering and Handling                  |  |

| Level Mode Interrupts                                 |  |

| Pulse Mode Interrupts                                 |  |

| Card Event Notification (The Status Change Interrupt) |  |

| DMA Support                                           |  |

| Power Conservation Modes                              |  |

| Card Lock Mechanism                                   |  |

| Error Detection and Correction (EDC)                  |  |

## Part Three PC Card Design

## Chapter 11: The Card Information Structure (CIS)

| Overview                             |  |

|--------------------------------------|--|

| The Card Information Structure (CIS) |  |

| Tuples                               |  |

| Tuple Format                         |  |

| A Sample Tuple                       |  |

| The Configuration Table              |  |

| The Configuration Entry Tuple        |  |

| Interpreting the Configuration Table |  |

| Multiple Function PC Cards           |  |

| Devices Commonly Used for the CIS    |  |

| CIS Access Timing                    |  |

| Summary of Layer 1 Tuples            |  |

ix

## **Chapter 12: Function Configuration Registers**

| Configuration Registers                |  |

|----------------------------------------|--|

| Configuration Option Register          |  |

| Card Configuration and Status Register |  |

| Status Change                          |  |

| Size of Host Expansion Bus             |  |

| Audio Enable                           |  |

| Power Conservation Mode                |  |

| Interrupt Pending                      |  |

| Pin Replacement Register               |  |

| Socket and Copy Register               |  |

| Extended Status Register               |  |

| I/O Base Registers                     |  |

| I/O Limit Register                     |  |

## Chapter 13: An SRAM Card Example

| An SRAM Card Example                        |  |

|---------------------------------------------|--|

| The SRAM CIS                                |  |

| Device Information Tuple                    |  |

| Level 1 Version / Product Information Tuple |  |

| Checksum Tuple                              |  |

| Termination Tuple                           |  |

## Chapter 14: A Flash Card Example

| An Example Flash Card Implementation        |  |

|---------------------------------------------|--|

| A Flash Memory CIS Example                  |  |

| Device Information Tuple                    |  |

| Device Geometry Tuple                       |  |

| JEDEC Device Identifier (ID) Tuple          |  |

| Level 1 Version / Product Information Tuple |  |

| Configuration Tuple                         |  |

| Termination Tuple                           |  |

| Flash Card Configuration Registers          |  |

| Configuration Option Register               |  |

| Configuration Status Register               |  |

## Chapter 15: A FAX/Modem Example

| An Example FAX/Modem Card                   |  |

|---------------------------------------------|--|

| FAX/Modem Resource Requirements             |  |

| A FAX/Modem CIS Example                     |  |

| Device Information Tuple                    |  |

| Level 1 Version / Product Information Tuple |  |

| Card Manufacturer Identification (ID) Tuple |  |

| Function Identification Tuple               |  |

| Function Extension Tuples                   |  |

| Configuration Tuple                         |  |

| Configuration Table                         |  |

| No-Link Tuple                               |  |

| Termination Tuple                           |  |

| FAX/Modem Configuration Registers           |  |

| Configuration Option Register               |  |

| Configuration Status Register               |  |

| Pin Replacement Register                    |  |

## Chapter 16: An ATA PC Card Example

| An ATA PC Card Example                      |  |

|---------------------------------------------|--|

| ATA System Resource Requirements            |  |

| Supporting Two Drives                       |  |

| The ATA Card's CIS                          |  |

| Disk Device Function Extensions             |  |

| IPL from a PCMCIA ATA Drive                 |  |

| An Example ATA Card CIS                     |  |

| Device Information Tuple                    |  |

| Level 1 Version / Product Information Tuple |  |

| Configuration Tuple                         |  |

| Configuration Table                         |  |

| Function Identification Tuple               |  |

| Function Extension Tuples                   |  |

| No-Link Tuple                               |  |

| Termination Tuple                           |  |

| Configuration Registers                     |  |

## **Chapter 17: A Multiple Function PC Card Example**

| Overview                                           |     |

|----------------------------------------------------|-----|

| An Example Multiple Function PC Card               |     |

| An Example CIS                                     | 210 |

| Configuration Registers                            | 214 |

| Configuration Option Register                      |     |

| Card Configuration and Status Register             |     |

| I/O Base Registers                                 |     |

| I/O Limit Register                                 |     |

| Shared Interrupt Handling                          | 219 |

| Review of Single Function Interrupt Handling       | 219 |

| IRQ Initialization                                 |     |

| Handling the Interrupt Request                     |     |

| Multiple Function Interrupt Handling               | 221 |

| IRQ Initialization                                 |     |

| Function Zero                                      |     |

| Function One                                       |     |

| Handling the Interrupt Request                     |     |

| Applications Unaware of Multiple Function Protocol | 224 |

| The Problem                                        | 224 |

| An Example Solution                                |     |

| Changes to Card Services Functions                 |     |

## Part Four PCMCIA Software

## **Chapter 18: The Configuration Process**

| Overview of the Configuration Process    |     |

|------------------------------------------|-----|

| The Role of the CIS                      |     |

| The Role of the Socket Service Functions |     |

| The Role of Card Services                |     |

| The Role of the PC Card Enabler          |     |

| Dedicated Enablers                       |     |

| Generic Enablers                         |     |

| Point Enablers                           |     |

| PCMCIA Software Solutions                | 234 |

## Chapter 19: Socket Services

| The Role of Socket Services—Making Life Easier                                                    | 235                      |

|---------------------------------------------------------------------------------------------------|--------------------------|

| Installation and Initialization                                                                   | 237                      |

| Socket Services Functions                                                                         | 237                      |

| Socket Services Calling Convention                                                                | 239                      |

| Adapter Functions                                                                                 | 243                      |

| Verifying SS is installed (GetAdapterCount)                                                       | 243                      |

| Getting Information from Socket Services (GetSSInfo)                                              |                          |

| When Two or More Socket Services Are Needed (GetSetPriorHandle)                                   |                          |

| Controlling HBA Parameters                                                                        | 245                      |

| Vendor Functions (GetVendorInfo, VendorSpecific)                                                  |                          |

| Indirect Access to PC Card Memory (GetAccessOffsets )                                             |                          |

| Determining What Card Caused a Status Change Interrupt                                            |                          |

| (AcknowledgeInterrupt)                                                                            | 248                      |

| Socket Functions                                                                                  |                          |

| Controlling Individual Sockets (InquireSocket, SetSocket, GetSocket)                              | 249                      |

| Determining the Current Status of the Socket and PC Card (GetStatus)                              |                          |

| D III C I III I C III III I C III C III C IIII C IIII C IIII                                      |                          |

| Kesetting the Socket Under Software Control (ResetSocket)                                         | 252                      |

| Resetting the Socket Under Software Control (ResetSocket)<br>Window Functions                     | 252                      |

| Window Functions                                                                                  | 253                      |

| Window Functions<br>Controlling Windows (InquireWindow, GetWindow and SetWindow)                  | 253<br>253               |

| Window Functions                                                                                  | 253<br>253<br>259        |

| Window Functions<br>Controlling Windows (InquireWindow, GetWindow and SetWindow)<br>EDC Functions | 253<br>253<br>259<br>259 |

## **Chapter 20: Card Services**

| Overview                                     |  |

|----------------------------------------------|--|

| Enabling PC Cards Before Card Services       |  |

| The Role of Card Services                    |  |

| Initialization of Card Services              |  |

| Verifying the Presence of Socket Services    |  |

| Verifying that Card Services Installed       |  |

| Determining Availability of System Resources |  |

| Power Management Support                     |  |

| Card Services Calling Conventions            |  |

| Specifying the Service                       |  |

| The Handle                                   |  |

| The Argument Packet                          |  |

| Return Codes                                 |  |

| The Pointer Argument                         |  |

xiii

| Client Services (Client Registration and Support)               |     |

|-----------------------------------------------------------------|-----|

| Determining If Card Services Is Installed (GetCardServicesInfo) |     |

| Signing Up with Card Services (RegisterClient)                  |     |

| Receiving Notification of Status Change Events                  |     |

| Determining the Order of Call-Backs: Client Driver Type         |     |

| Artificial Card Insertion Events                                |     |

| Telling Card Services You're Leaving (DeregisterClient)         |     |

| Client Utility Services (Detecting a PC Card)                   |     |

| Evaluating the PC Card and Socket (GetConfigurationInfo)        |     |

| Scanning the CIS (GetFirstTuple, GetNextTuple, GetTuple Data)   |     |

| Simplifying CIS Processing for Memory and MTD Clients           |     |

| Resource Management Services (Assigning Resources)              |     |

| Requesting a Resource                                           |     |

| Requesting Resource Combinations                                |     |

| Configuring the HBA and PC Card (RequestConfiguration)          |     |

| Bulk Memory Services                                            |     |

| Advanced Client Functions                                       |     |

| The Call-Back Process                                           |     |

| Identifying a Status Change Event                               |     |

| The Client Call-Back                                            |     |

| Configuring PC Cards During POST                                | 294 |

## **Chapter 21: Client Drivers**

| Overview                                         |  |

|--------------------------------------------------|--|

| The Card Insertion Call-Back                     |  |

| Memory Drivers and Memory Technology Drivers     |  |

| SRAM Client Drivers                              |  |

| SRAM Client Driver Registers with Card Services  |  |

| The SRAM Client Driver Call-Back                 |  |

| Flash Client Drivers                             |  |

| The Flash File System                            |  |

| MTD Registers with Card Services                 |  |

| The MTD Call-Back                                |  |

| MTD Registers Memory Regions                     |  |

| Flash Client Driver Registers with Card Services |  |

| The Flash Client Driver Call-Back                |  |

| Accessing Flash Memory                           |  |

| I/O Card Client Drivers                          |  |

| I/O Client Driver Registers with Card Services   |  |

| The I/O Client Driver Call-Back                  |  |

xiv

## Contents

| Identifying the l | PC Card              |  |

|-------------------|----------------------|--|

|                   | sources Requirements |  |

| 0                 | Resources            |  |

|                   | PC Card              |  |

|                   |                      |  |

## Chapter 22: Booting from PC Cards

| Configuring PC Cards During POST |  |

|----------------------------------|--|

| The Problem                      |  |

| The Solution                     |  |

| Bootable Memory Cards            |  |

| Bootable ATA Devices             |  |

## Chapter 23: Execute In Place (XIP)

| The XIP Goals                                          |  |

|--------------------------------------------------------|--|

| The XIP Software Hierarchy                             |  |

| XIP File Management                                    |  |

| The XIP Loader                                         |  |

| The XIP Device Drivers (API and Hardware Manipulation) |  |

| LXIP                                                   |  |

| EXIP                                                   |  |

| SXIP                                                   |  |

|                                                        |  |

## Part Five ExCA (QuickSwap)

## Chapter 24: ExCA (QuickSwap)

| The ExCA Goal                      |  |

|------------------------------------|--|

| ExCA Scope                         |  |

| ExCA Host Bus Adapter Requirements |  |

| Address Mapping (memory and I/O)   |  |

| Memory Address Mapping             |  |

| I/O Address Mapping                |  |

| Interrupt Support                  |  |

| Status Change Interrupt            |  |

| PC Card Interrupts                 |  |

| System Power Requirements          |  |

| PC Card Insertion/Removal          |  |

|                                    |  |

xv

| Card Insertion       |  |

|----------------------|--|

| Card Removal         |  |

| ExCA Socket Services |  |

| ExCA Card Services   |  |

| ExCA PC Cards        |  |

| PC Card Event WakeUp |  |

## Part Six An Example HBA

## Chapter 25: An Example HBA—The CL-PD6722

| Introduction to the CL-PD6722 |  |

|-------------------------------|--|

| Socket Power Control          |  |

| Vcc Control                   |  |

| Vpp1 Control                  |  |

| PC Card Data Transfers        |  |

| Address Window Mapping        |  |

| Memory Interface              |  |

| I/O Interface                 |  |

| Status Change Reporting       |  |

| Interrupt Steering            |  |

| The ATA Socket Interface      |  |

| ATA Registers                 |  |

| DMA Support                   |  |

|                               |  |

## Appendices

| Appendix A: SRAM CIS Example              |  |

|-------------------------------------------|--|

| Appendix B: Flash Memory CIS Example      |  |

| Appendix C: FAX/Modem Tuple Example       |  |

| Appendix D: ATA Disk CIS Example          |  |

| Appendix E: Metaformat Layers 2, 3, and 4 |  |

| Appendix F: References                    |  |

| Glossary                                  |  |

| Index                                     |  |

## Figures

| Figure 3-1. Relationship of PCMCIA Software and Hardware                             |

|--------------------------------------------------------------------------------------|

| Figure 3-2. The Card Information Structure Contains Configuration Options for the PC |

| Card                                                                                 |

| Figure 3-3. PCMCIA Sockets Can Be Incorporated in a Wide Variety of Systems26        |

| Figure 3-4. Configuration and Status Reporting Software Flow Versus Run Time         |

| Software Flow                                                                        |

| Figure 4-1. The Interconnect Area is the Same Thickness for all PC Cards             |

| Figure 4-2. Type I Card with Battery and Write Protect Switch                        |

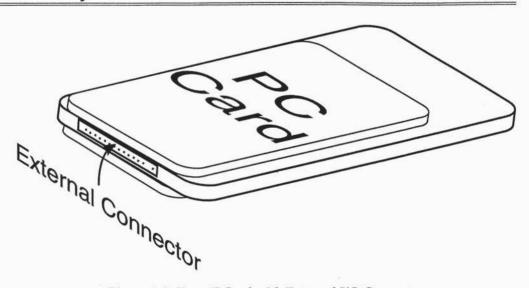

| Figure 4-3. Type II Card with External I/O Connector                                 |

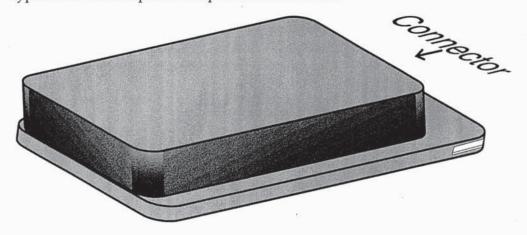

| Figure 4-4. Type III Card Outline                                                    |

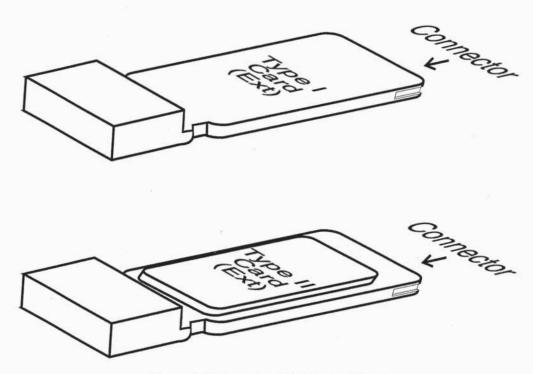

| Figure 4-5. Type I and II Extended Cards                                             |

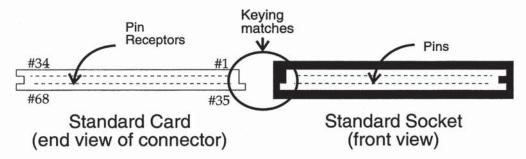

| Figure 4-6. Card and Socket Keying-Standard Interface                                |

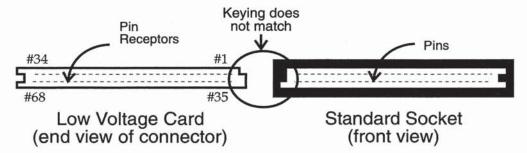

| Figure 4-7. Low-Voltage Cards Cannot Be Inserted into Standard Sockets               |

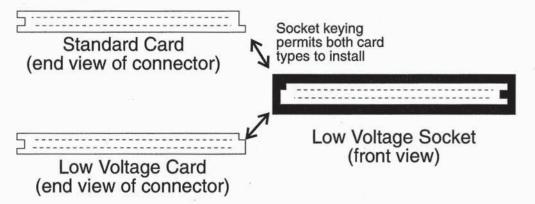

| Figure 4-8. Keying Used with Low Voltage Socket                                      |

| Figure 5-1. PCMCIA Memory Socket Interface to Host Bus Adapter                       |

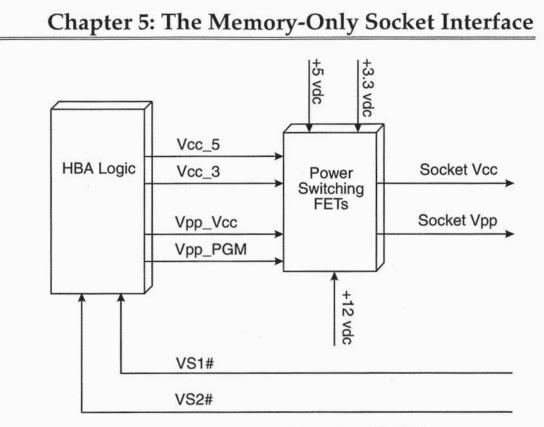

| Figure 5-2. Voltage Switching Performed by HBA                                       |

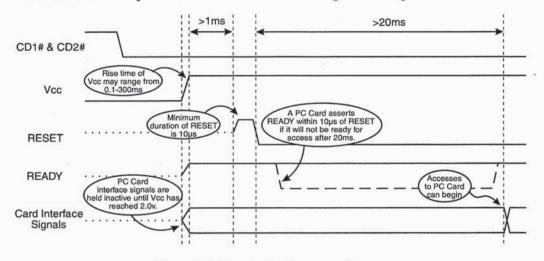

| Figure 5-3. The Socket Power-up Sequence                                             |

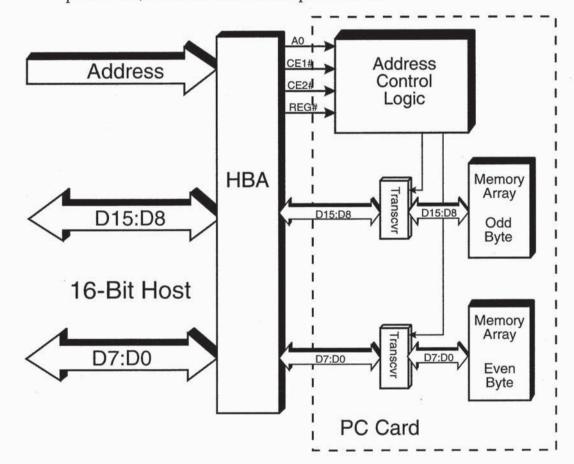

| Figure 5-4. Addressing Mode Used by Memory Card with 16-Bit Host56                   |

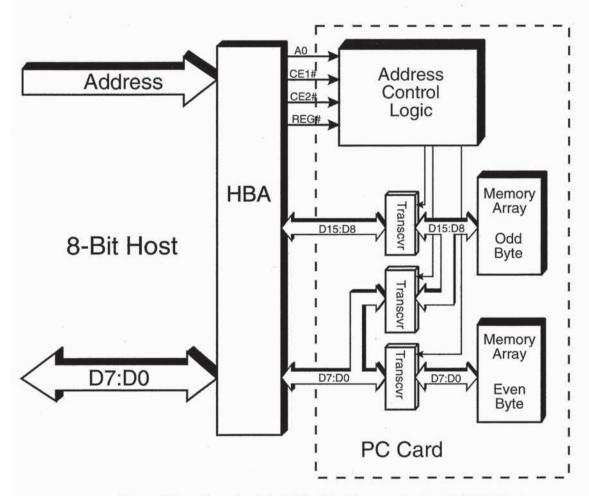

| Figure 5-5. Addressing Mode Used by Memory Card with 8-Bit Host57                    |

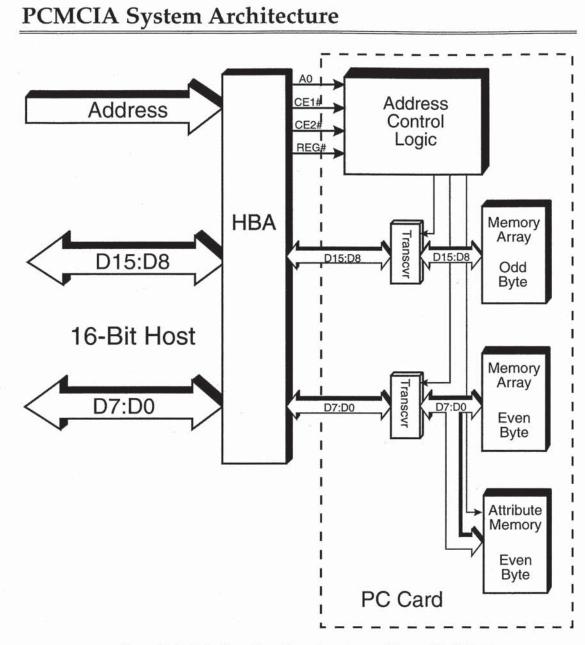

| Figure 5-6. Only Even Locations Are Accessed from Attribute Memory over the Lower    |

| Data Path                                                                            |

| Figure 6-1. PCMCIA Memory or I/O Socket                                              |

| Figure 7-1. Example DMA Transfer Mechanism                                           |

| Figure 7-2. DMA Signal Interface                                                     |

| Figure 7-3. Block Diagram of PC Card implementing DMA Transfers94                    |

| Figure 8-1. Typical ATA Interface to IDE Drive                                       |

| Figure 8-2. PC Card ATA Disk and Memory Devices                                      |

| Figure 8-3. Minimum Signals Required for ATA Socket Interface                        |

| Figure 9-1. AIMS Socket Interface Signals                                            |

| Figure 10-1. The PCMCIA Environment                                                  |

| Figure 10-2. Host Bus Adapter Functional Block with Two Sockets                      |

| Figure 10-3. PC Card with Memory That Can Be Direct Mapped into the System Ad-       |

| dress Space122                                                                       |

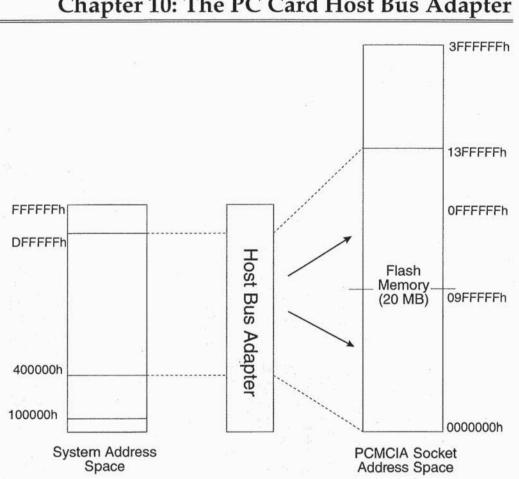

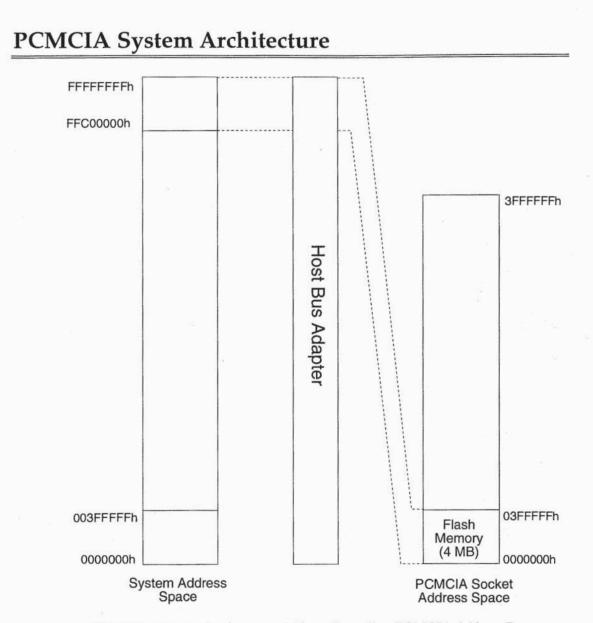

| Figure 10-4. Example of Address Translation Logic Remapping the System Address to    |

| the Bottom of the Common Memory Address Space123                                     |

| Figure 10-5. Example of Small System Address Range Being Remapped to a Larger        |

| PCMCIA Memory Device125                                                              |

| Figure 10-6. Example of System Address Exceeding PCMCIA Address Range 126            |

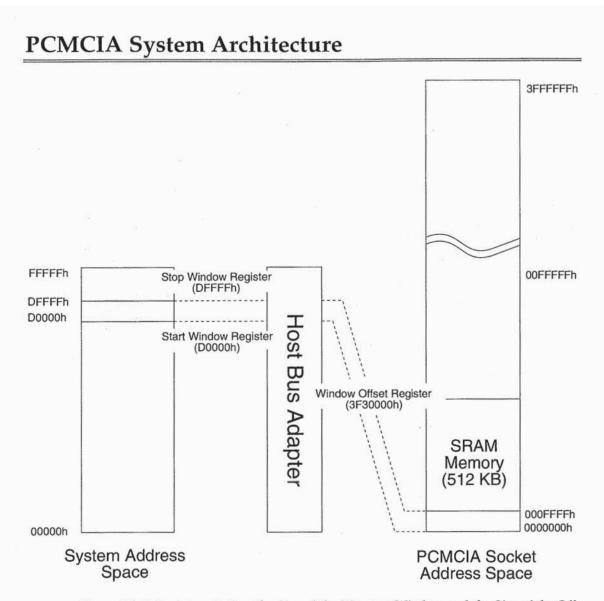

| Figure 10-7. Registers Define the Size of the Memory Window and the Size of the Off- |

| set for Remapping the System Address128                                              |

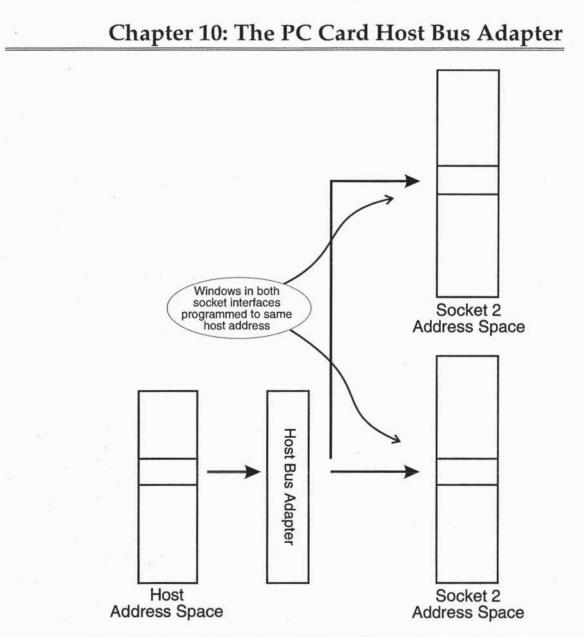

| Figure 10-8. Example of Overlapping Memory Windows Causing Contention129             |

xvii

| Figure 10-9. PC Card I/O Addresses Mapped Directly to System I/O Addresses1         | 131 |

|-------------------------------------------------------------------------------------|-----|

| Figure 10-10. Example of I/O Window Overlapping Addresses of Other I/O Device       | es  |

| in the System                                                                       |     |

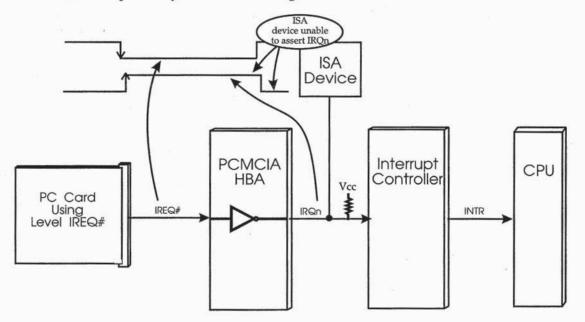

| Figure 10-11. HBA Interrupt Steering in an ISA System                               | 136 |

| Figure 10-12. ISA Interrupt Sharing Not Permitted with Level Mode IREQ#             | 137 |

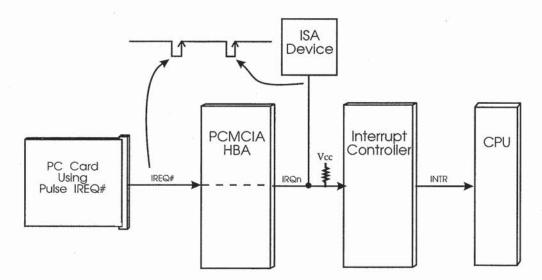

| Figure 10-13. Pulse Mode Interrupts Permit Interrupt Sharing in an ISA System       |     |

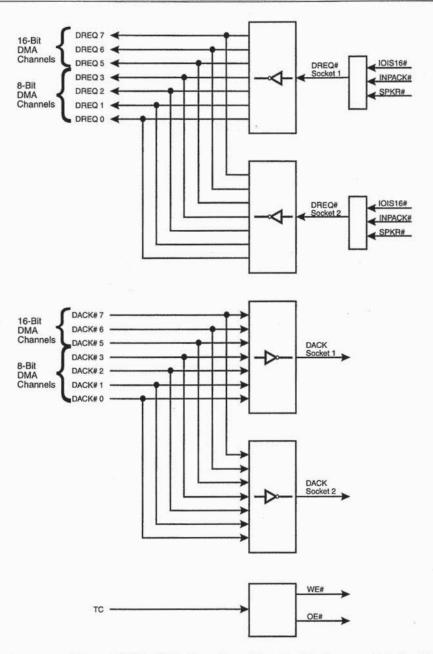

| Figure 10-14. HBA Functions Required to Support PC Card DMA                         |     |

| Figure 11-1. PCMCIA Software Flow                                                   |     |

| Figure 11-2. Example CIS Layout Consisting of a Linked List of Four Tuples          | 147 |

| Figure 11-3. The Configuration Table Consists of a Number of Entries, Describing th |     |

| Configuration Options Supported by the PC Card.                                     |     |

| Figure 11-4. Example Configuration Table with One Default and Four Non-Default      |     |

| Entries                                                                             |     |

| Figure 11-5. Configuration Table Structure Used by a Triple-Function PC Card        | 157 |

| Figure 13-1. Block Diagram of 2MB SRAM PC Card                                      |     |

| Figure 13-2. Map of Attribute Memory Addresses on Example SRAM Card                 |     |

| Figure 14-1. 20MB Flash Card Functional Diagram                                     |     |

| Figure 14-2. Example Contents of a Flash Card's Attribute Address Space             | 183 |

| Figure 15-1. Functional Block Diagram of FAX/Modem PC Card                          | 190 |

| Figure 15-2. Example of Attribute Memory Address Contents for FAX/Modem             | 193 |

| Figure 16-1. Functional Block Diagram of an ATA Disk Drive PC Card                  | 200 |

| Figure 17-1. Functional Diagram of a Multiple Function PC Card                      | 211 |

| Figure 17-2. An Example CIS Structure Supporting Two Functions.                     | 213 |

| Figure 17-3. Multiple Function IRQ Sharing Procedure.                               |     |

| Figure 18-1. PCMCIA Software Flow                                                   | 230 |

| Figure 19-1. Relationship of Socket Services to the Rest of the System.             | 236 |

| Figure 20-1. PCMCIA Software Flow                                                   |     |

| Figure 21-1. A Sample Configuration Process Used By a Card Services Client          | 297 |

| Figure 21-2. Memory Client Driver Software Environment                              |     |

| Figure 21-3. Software Environment Required for Flash Card Support                   | 302 |

| Figure 21-4. I/O Enabler Registration and PC Card Configuration Process             |     |

| Figure 25-1. CL-PD6722 Socket Power Control Signals                                 |     |

| Figure 25-2. The Power Control Register                                             |     |

| Figure 25-3. Basic Functional Blocks Used During Data Transfers                     | 339 |

| Figure 25-4. Registers Comprising a Single Memory Address Window                    |     |

| Figure 25-5. Register Comprising a Single I/O Address Window                        |     |

| Figure 25-6. Management Interrupt Configuration Register                            |     |

| Figure 25-7. Card Status Change Register                                            |     |

| Figure 25-8. Interface Status Register                                              |     |

| Figure 25-9. Interrupt and General Control Register                                 |     |

| Figure 25-10. ATA Socket Interface                                                  | 347 |

| THE AL DOMOTA FOR COMPANY                                                      | 16  |

|--------------------------------------------------------------------------------|-----|

| Table 2-1. PCMCIA Feature Summary                                              |     |

| Table 2-2. Evolution of the PCMCIA Specification                               | 1/  |

| Table 2-3. List of Individual Volumes Included in the PC Card Standard         |     |

| Table 3-1. PCMCIA Card Metaformat                                              |     |

| Table 4-1. Interpretation of Voltage Sense Signals                             |     |

| Table 4-2. Selected Connector Reliability Specifications                       |     |

| Table 4-3. Selected PC Card Environmental Specifications                       |     |

| Table 5-1. Card Voltage Pins                                                   |     |

| Table 5-2. Definition of Voltage Sense Pins                                    |     |

| Table 5-3. Interpretation of Voltage Sense Signals by a Low Voltage Socket     |     |

| Table 5-4. PCMCIA Address Lines—Memory Interface                               |     |

| Table 5-5. Addressing Even and Odd Bytes                                       |     |

| Table 5-6. Data Bus                                                            |     |

| Table 5-7. PC Card Command Lines for Memory Interface                          |     |

| Table 5-8. PCMCIA Memory Transaction Types                                     |     |

| Table 5-9. Card and Socket Status Signals                                      |     |

| Table 5-10. Interpretation of the Card Detect Signals                          |     |

| Table 5-11. Interpretation of Battery Voltage Detection Signals                |     |

| Table 6-1. Pins Added/Removed When Converting from Memory-Only to Men          |     |

| I/O Interface                                                                  |     |

| Table 6-2. PCMCIA Transaction Definition                                       |     |

| Table 7-1. Definition of the Miscellaneous Features Field that Defines DMA sup |     |

| Table 7-2. Interpretation of DMA Request Assignment Bits                       |     |

| Table 7-3. Typical DMA Clock Speeds in the PC Environment                      | 95  |

| Table 7-4. Socket Service Functions Modified to Support DMA                    |     |

| Table 7-5. Modifications Made to Card Services to Support DMA                  |     |

| Table 8-1. Signals Defined by ATA But Not Used By PCMCIA                       |     |

| Table 8-2. ATA Addressing Options Supported by PCMCIA                          |     |

| Table 9-1. Commands Supported by AIMS Cards                                    | 111 |

| Table 9-2. AIMS Registers                                                      | 112 |

| Table 10-1. Interpretation of Voltage Sense Lines.                             |     |

| Table 10-2. Address Sent to Socket                                             |     |

| Table 11-1. Basic Tuple Format                                                 | 148 |

| Table 11-2. Example Device Information Tuple for an SRAM Card                  | 149 |

| Table 11-3. Device Type Codes                                                  |     |

| Table 11-4. Device Speed Codes                                                 |     |

| Table 11-5. Unit Size Codes                                                    |     |

| Table 11-6. Format of the Configuration Table Entry Tuple                      |     |

| Table 11-7. Tuples defined for Compatibility Layer One (CIS)                   |     |

| Table 12-1. Format of the Function Configuration Registers                     |     |

| Table 12-3. Card Configuration and Status Register and Definition              |     |

|                                                                                |     |

xix

| Table 12.4 Din Dople company Provider                                                                     | 1(0 |

|-----------------------------------------------------------------------------------------------------------|-----|

| Table 12-4. Pin Replacement Register                                                                      |     |

| Table 12-5. Socket and Copy Register<br>Table 12-6. Format and definition of the Extended Status Register |     |

| Table 12-6. Format and definition of the Extended Status Register                                         |     |

|                                                                                                           |     |

| Table 17-1. Tuples Defined for the Primary CIS (Listed in the Order)                                      |     |

| Table 17-2. Tuples Defined for each Secondary CIS (Listed in the Order)                                   |     |

| Table 17-4. Configuration Option Register format and Definition                                           |     |

| Table 17-5. Card Configuration and Status Register and Definition                                         |     |

| Table 17-6. Address Limit Associated with Function Base Address Register                                  |     |

| Table 17-7. Card Services Modified for Multiple Function Support                                          |     |

| Table 18-1. Major Vendors of PCMCIA Software Solutions                                                    |     |

| Table 19-1. Socket Services Functions                                                                     |     |

| Table 19-2. Socket Services Function Code Listing                                                         |     |

| Table 19-3. Socket Services Return Codes                                                                  |     |

| Table 19-4. Adapter Information Structure Definition                                                      |     |

| Table 19-5. Socket Information Structure Definition                                                       |     |

| Table 19-6. Memory Window Characteristics Structure Definition                                            | 255 |

| Table 19-7. I/O Window Information Structure Definition                                                   |     |

| Table 19-7. I/O Window Information Structure Definition (Continued)                                       |     |

| Table 20-1. Card Services Listed in Alphabetical Order                                                    | 270 |

| Table 20-2. Card Services Function Codes Listed in Numerical Order                                        |     |

| Table 20-3. Card Services Return Codes Listed in Alphabetical Order                                       | 273 |

| Table 20-4. Card Services Return Codes Listed in Numerical Order                                          |     |

| Table 20-5. Client Services Functions                                                                     | 275 |

| Table 20-6. Client Utility Functions Used by the Client Driver to Access PC Card                          | in- |

| formation                                                                                                 |     |

| Table 20-7. Information Returned by the GetConfigurationInfo Service                                      |     |

| Table 20-8. Resource Management Functions                                                                 | 285 |

| Table 20-8. Resource Management Functions (Continued)                                                     | 286 |

| Table 20-9. Bulk Memory Functions                                                                         |     |

| Table 20-10. Advanced Card Services Functions                                                             |     |

| Table 20-10. Advanced Card Services Functions (Continued)                                                 | 291 |

| Table 20-11. Call-Back Events Defined by Card Services                                                    |     |

| Table 20-11. Call-Back Events Defined by Card Services                                                    | 294 |

| Table 22-1. Format of the Function Identification Tuple                                                   | 313 |

| Table 22-2. Contents of the Function Identification Byte                                                  | 314 |

| Table 22-3. Contents of the Initialization Byte                                                           | 314 |

| Table 24-1. Interrupts Potentially Available For Use By PC Cards                                          | 325 |

| Table 24-2. ExCA Voltage Requirements                                                                     | 326 |

| Table 24-3. State of Socket When PC Card is Inserted                                                      | 326 |

xx

Table 24-4. Socket Services Functions Required/Optional for ExCA Compliant Systems

328

Table 24-5. Card Services Functions Required/Optional For ExCA Compliance

329

Table 24-6. Tuples Recommended by the ExCA Specification

330

Table 25-1. Socket Vpp Control

338

Table 25-2. Example Addressing Scheme Used by ATA Cards

348

#### **Special Recognition**

Special thanks to Tom Shanley, my best friend, business partner and hiking companion, who keeps me on the right path.

#### Acknowledgments

I extend my appreciation and gratitude to the developers at IBM and Intel who provided valuable information and insight during the development of this book and training course. Special thanks to those at the IBM Toronto site who struggled with me during the early stages. Thanks also to those at Cirrus Logic who answered many questions and provided valuable information. Finally, I would like to thank Maxtor for providing information on their ATA drive.

Thanks to those at Norand in Cedar Rapids for their efforts in catching many errors in the manuscript and suggesting improvements to both text and illustrations.

#### The MindShare Architecture Series

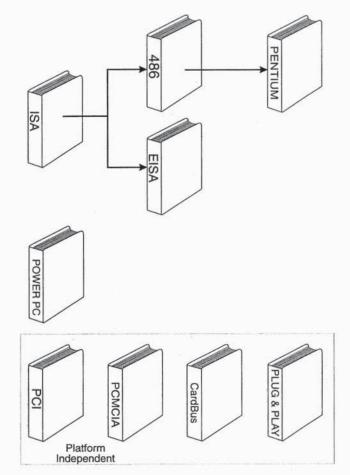

The series of books by MindShare on system architecture includes; *ISA System* Architecture, EISA System Architecture, 80486 System Architecture, PCI System Architecture, Pentium<sup>™</sup> Processor System Architecture, PCMCIA System Architecture, PowerPC<sup>™</sup> System Architecture, Plug and Play System Architecture, and CardBus System Architecture, all published by Addison-Wesley.

Rather than duplicating common information in each book, the series uses a building-block approach. *ISA System Architecture* is the core book upon which the others build. The figure below illustrates the relationship of the books to each other.

Architecture Series Organization

## **Organization of This Book**

*PCMCIA System Architecture* is organized into six parts consisting of twenty-five chapters. A brief description of each chapter follows:

#### Part One — Introduction to PCMCIA

**Chapter 1:** The Problem. This chapter focuses on the industry needs that led to the emergence of PCMCIA and the development of PC Card Standard.

**Chapter 2:** The PCMCIA Solution. This chapter discusses the emergence of PCMCIA, traces its evolution and introduces terminology and key concepts behind PCMCIA. Key features of the latest release of the 16-bit PCMCIA standard (called the PC Card Standard) are also introduced.

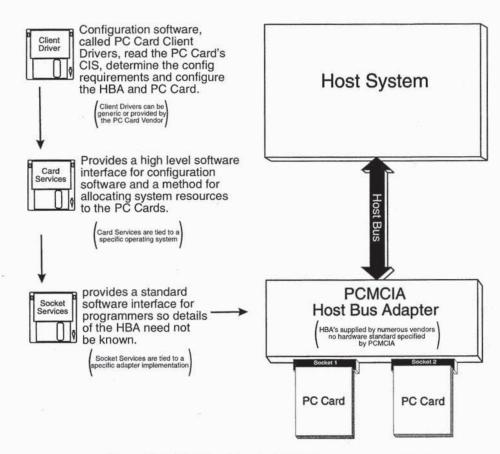

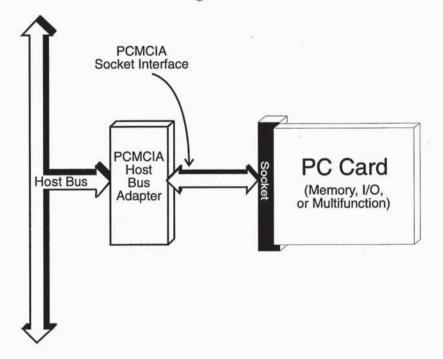

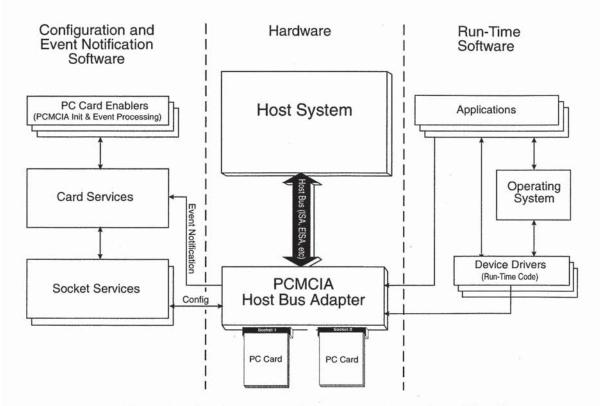

**Chapter 3: Tying the Pieces Together.** This chapter explains the relationships between the various hardware and software elements employed in a typical PC Card environment. The elements discussed include: the PCMCIA Host Bus Adapter (HBA); the PC Card socket; the PC Card; socket services; card services; and enablers.

#### Part Two — Socket and Host Bus Adapter Design

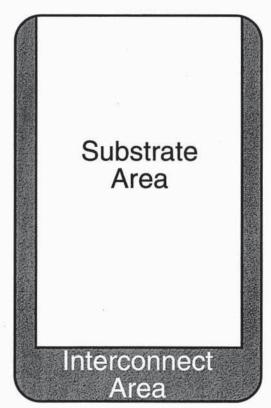

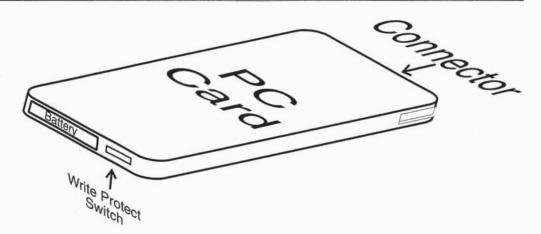

**Chapter 4:** The Physical Specifications. This chapter focuses on the various physical packages defined by PCMCIA for PC Cards and the related environmental specifications. The chapter also describes the standard socket and low-voltage socket types.

**Chapter 5:** The Memory-Only Socket Interface. This chapter details the memory-only electrical interface between the PC Card and socket. Each pin is defined and it relationship to the PC Card and the HBA is discussed. The memory-only interface is the interface initially seen by 16-bit PC Cards when they are first inserted into a socket. This permits the memory-mapped CIS to be accessed to determine the PC Card type and interface requirements. If the card is designed for an interface type other than memory-only, then the HBA and PC Card are configured to communicate via one of the other interfaces defined by the PC Card Standard (discussed in the following chapters). Also

discusses the timing of socket accesses to PC Cards of differing speeds, including transfers with attribute memory and common memory.

**Chapter 6:** The Memory or I/O Interface. This chapter details the memory or I/O socket interface. The memory-only interface is converted into a memory or I/O interface by software after it detects that an I/O PC Card has been installed into the socket interface. Pins that are added or redefined by the memory or I/O interface are discussed along with their relationship to the I/O card function. Some of the memory-only pins are replaced with I/O specific pins when the interface is redefined for I/O. This chapter describes how the functions associated with the replaced memory-only pins are handled.

**Chapter 7:** The DMA Interface. This chapter defines the DMA compliant electrical interface, permitting I/O Cards to use PC compatible DMA transfers. The DMA interface allows I/O devices that use DMA to take advantage of existing compatible software when performing data transfers.

**Chapter 8:** The ATA Interface. This chapter discusses the PC Card ATA interface. An PC Card ATA interface provides a PC compatible hardware and programming interface that simplifies the job of implemented hard drive solutions in the PCMCIA environment. This chapter defines the various ways that a PC Card ATA can be mapped in the system along with the electrical interfaces that are used. Differences between the PC compatible ATA implementation versus the PC Card ATA interface are also discussed.

**Chapter 9:** The AIMS Interface. This chapter focuses on the optional Auto-Indexing Mass Storage (AIMS) interface. The transfer mechanism is described, along with the registers that must be programmed to initiate the transfer.

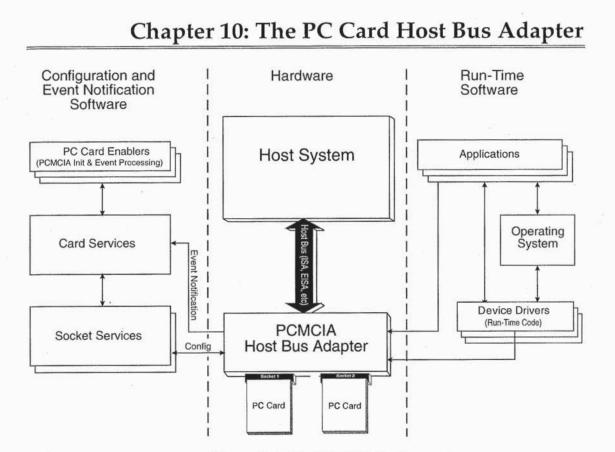

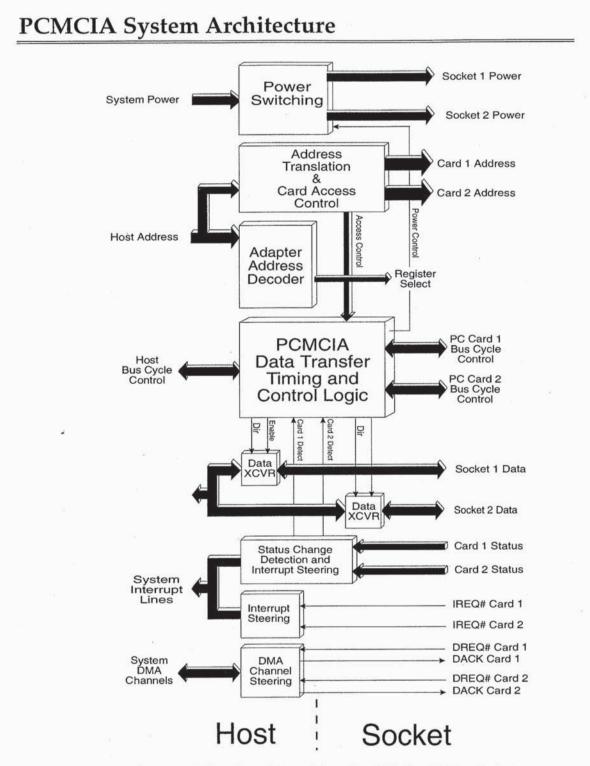

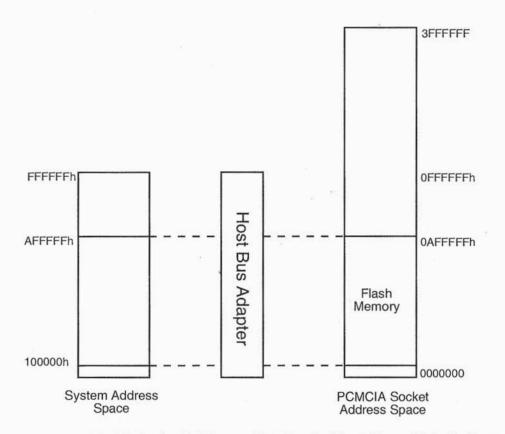

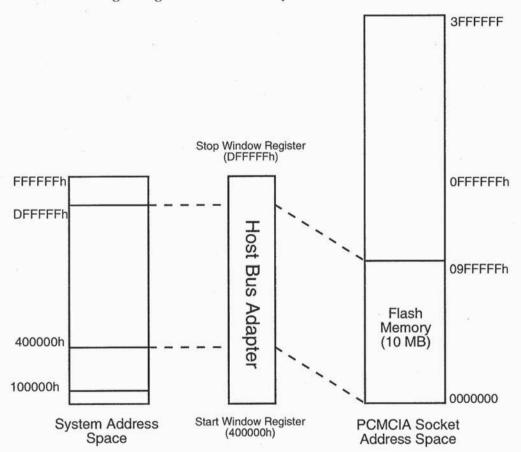

**Chapter 10:** The PC Card Host Bus Adapter. This chapter discusses the role of the PCMCIA Host Bus Adapter. Individual Host Bus Adapter functions are discussed. A functional block diagram of an HBA adapter is provided along with detailed explanations of each function.

#### Part Three — PC Card Design

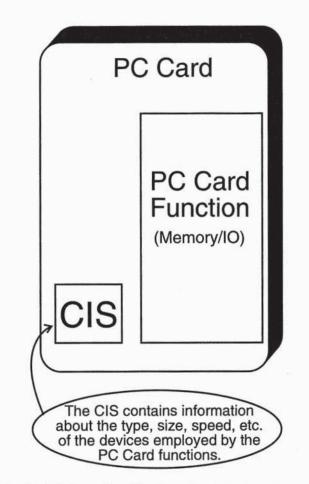

**Chapter 11:** The Card Information Structure (CIS). This chapter discusses layer one of the metaformat, commonly referred to as the card information structure, or CIS. The chapter details the role of the CIS in the PC Card configuration process. Tuples are also introduced and their format and structure

3

are described. The basic structure of the CIS's configuration table required by I/O cards is also described.

**Chapter 12: Function Configuration Registers.** This chapter discusses the configuration registers and provides a complete description of each register specified by the PC Card standard. Configuration register implementations for both single and multiple function cards are covered.

**Chapter 13:** An SRAM Card Example. This chapter describes a sample SRAM card implementation, including a functional block diagram of the SRAM card along with a sample CIS.

**Chapter 14:** A Flash Card Example. This chapter describes a flash card implementation, including a functional block diagram of the card, a sample CIS, and configuration registers implemented by the card.

**Chapter 15:** A FAX/Modem Example. This chapter describes an example FAX/Modem implementation, including a functional block diagram, sample CIS, and related configuration registers.

**Chapter 16: An ATA PC Card Example.** This chapter describes an example PC Card ATA drive implementation, including a functional block diagram, a sample CIS, and configuration registers implemented by the card.

**Chapter 17:** A Multiple Function PC Card Example. This chapter discusses the multiple function PC Card strategy and the mechanisms for achieving it. It also includes a functional block diagram of a multiple function PC Card, a sample multi-function CIS, related configuration registers, and multi-function interrupt handling.

#### Part Four — PCMCIA Software

**Chapter 18: The Configuration Process.** This chapter provides an overview of the PCMCIA software environment and the configuration process. The primary role and interaction between each piece of software is established. This chapter also introduces the common software solutions provided along with the most popular suppliers.

**Chapter 19:** Socket Services. This chapter discusses the role of socket services. It also describes the initialization of socket services and explains the basic purpose of the functions commonly supported in the PC environment.

**Chapter 20: Card Services.** This chapter focuses on the role of card services in the PCMCIA environment. This chapter review each of the functions defined by the PC Card specification that apply to 16-bit PC Cards, along with related return codes. The call back mechanism is also described and the event and call back codes are defined.

**Chapter 21: Client Drivers** This chapter discusses the three basic types of enablers: point enablers, device-specific enablers, and super enablers. The chapter also discusses the jobs performed by generic memory enablers (and MTDs) and I/O device enablers.

**Chapter 22:** Booting from PC Cards. This chapter discusses the problems associated with loading the operating system from a PC Card. It also defines mechanisms used to determine whether a given PC Card is a bootable device, and the firmware support required to support PC Card booting.

**Chapter 23:** Execute In Place (XIP). This chapter discusses the Execute-In-Place mechanism defined by PCMCIA that allows code to be executed directly from the card rather than copying files to and executing from system memory.

#### Part Five — ExCA (QuickSwap)

**Chapter 24: ExCA (QuickSwap).** This chapter introduces the ExCA (QuickSwap) specification that defines a required set of hardware and software support, intended to improve PC Card interoperability across platforms based on Intel x86 architecture.

#### Part Six — An Example HBA

**Chapter 25:** An Example HBA–The CL-PD6722. This chapter provides an overview of a sample PCMCIA host bus adapter (The Cirrus Logic CL-PD6722) used in Intel x86 implementations for either an original PC or ISA compatible host bus.

5

#### Appendices

SRAM CIS Example

Flash CIS Example

FAX/Modem CIS Example

ATA Disk CIS Example

Metaformat Layers 2, 3, and 4

References

### Who Should Read This Book

This book is intended for use by hardware and software designers and support personnel. Due to the clear and concise explanatory methods used to describe each subject, personnel outside of the design field may also find the text useful.

#### Prerequisite Knowledge

We highly recommend that you have a thorough knowledge of PCs, including hardware and software interaction prior to reading this book. Several Mind-Share publications provide all of the background necessary for a complete understanding of the subject matter covered in this book. Much of the background information can be obtained from the *ISA System Architecture* book.

#### **Documentation Conventions**

This section defines the typographical conventions used throughout this book.

#### **Hex Notation**

All hex numbers are followed by an "h". Examples:

9A4Eh

0100h

### **Binary Notation**

All binary numbers are followed by a "b". Examples:

0001 0101b

01b

#### **Decimal Notation**

When required for clarity, decimal numbers are followed by a "d". Examples:

256d

128d

#### Signal Name Representation

Each signal that assumes the logic low state when asserted is followed by a pound sign (#). As an example, a PC Card modem asserts the IREQ# signal to a logic low state when signaling an interrupt request to the system.

Signals that are not followed by a pound sign are asserted when they assume the logic high state. As an example, a PCMCIA Card asserts READY to logic high state, indicating that it is ready to be accessed.

## Identification of Bit Fields (logical groups of bits or signals)

7

All bit fields are designated as follows:

[X:Y],

where "X" is the most-significant bit and "Y" is the least-significant bit of the field. As an example, the PCMCIA socket supports address lines A[25:0], where A25 is the most-significant and A0 the least-significant bit of the address.

#### CardBus

An enhanced version of PCMCIA is also defined by the PC Card standard. The new high-speed CardBus cards incorporate 32-bit data transfers and bus mastering capability. See MindShare's *CardBus System Architecture* book published by Addison-Wesley for details regarding the CardBus implementation.

#### We Want Your Feedback

MindShare values your comments and suggestions. You can contact us via mail, phone, fax, or internet email.

#### E-Mail/Phone/FAX

Email: mindshar@interserv.com

Phone: (214) 231-2216

Fax: (214) 783-4715

#### Mailing Address

Our mailing address is:

MindShare, Inc.

2202 Buttercup Drive

Richardson, Texas 75082

# Part One

# Introduction to PCMCIA

# Chapter 1

#### This Chapter

This chapter focuses on the industry needs that led to the emergence of PCMCIA and the development of PC Card Standard.

#### **The Next Chapter**

The next chapter introduces the PCMCIA solution and reviews the evolution of the PCMCIA Standard.

#### The Mobile Computing Environment

The growth of the microcomputer industry in the 1980s and the popularity of the PC led to the proliferation of laptop, notebook and sub-notebook computers. Manufacturers strived to deliver desktop performance in smaller and lighter portable systems, powered by batteries. This fueled the need for lighter, smaller, and less power hungry peripheral devices. A major focus of this effort revolved around the relatively large, heavy, power hungry floppy drive subsystem.

In addition to being small, lighter, and more power efficient, the alternative system had to provide many of the same characteristics of the floppy disk; it had to include removable media that was transportable to other systems, and had to be immediately accessible when installed into the system for reading and writing files. Early interest revolved primarily around the use of batterybacked memory cards implemented as a virtual floppy drive subsystem. Memory cards were physically small, could store large amounts of data, and consumed relatively little system power when compared to the floppy drive. Furthermore, the emergence of Flash memory promised to provide an economical memory card solution that required no battery back-up.

11

#### Small Form-Factor I/O Expansion Devices

The mobile computer environment also had a need for small and power efficient I/O expansion devices. The small PCMCIA form-factor drew attention as a possible solution for I/O expansion devices. The initial PCMCIA designs supported only memory cards however, the need to expand PCMCIA to include I/O device support was clear.

· 1

# Chapter 2

## The Previous Chapter

The previous chapter focused on the industry needs that led to the emergence of PCMCIA and the development of PC Card Standard.

## This Chapter

This chapter discusses the emergence of PCMCIA, traces its evolution and introduces terminology and key concepts behind PCMCIA. Key features of the latest release of the 16-bit PCMCIA standard (called the PC Card Standard) are also introduced.

## The Next Chapter

The next chapter explains the relationships between the various hardware and software elements employed in a typical PC Card environment. The elements discussed include: the PCMCIA Host Bus Adapter (HBA); the PC Card socket; the PC Card; socket services; card services; and client drivers.

## The Virtual Floppy Drive Subsystem

Solid state memory cards can provide an alternative to the mechanical floppy and floppy drive. In other words, memory cards can be implemented as a virtual floppy drive subsystem. Such a solution must permit standard PC software to access the memory cards as if they were floppy disks. This necessitates translation of PC compatible software calls used to access an ordinary floppy disk into commands that access files stored within the memory card. To ensure compatibility with existing PC software a standardized software protocol was required to ensure compatible operation of the memory cards.

Memory cards implemented as virtual floppy disks must also have the ability to be inserted and removed from the system at any time as is done with

13

floppy disks. When a card is installed, software must be able to access the files stored on the memory card or write new files to it. How was this to be done? Several key questions come to mind: How would the insertion of a memory card be detected? Were memory cards to be accessed via an I/O port as done with the floppy drive interface, or mapped into the processor's memory address space? What system resources would be required? What software would be responsible for the various aspects of recognizing, configuring, and accessing the memory cards? These questions and others clearly pointed to the need for hardware and software standards that could be implemented by system manufacturers to ensure interoperability of memory cards between IBM compatible systems.

#### The Lack of a Standard Memory Card Design

Numerous memory card manufacturers produced cards with differing physical and electrical properties, making compatibility a major obstacle in fulfilling industry needs. A standard physical package, electrical interface and connector were needed to ensure compatibility of memory cards.

#### Emergence of PCMCIA

Several manufacturers met in the summer of 1988 to investigate the possibility of forming a standards organization to deal with memory card standards and interoperability issues. A year later the Personal Computer Memory Card International Association (PCMCIA) was founded, and the first PCMCIA Standard (Release 1.0) was introduced in September 1990. This standard specified the design of memory cards (commonly called PC Cards) and a socket interface to be implemented as virtual disk drives.

PCMCIA was formed to promote the standardization and interchangeability of PC Cards. Initially, its primary focus was defining PC Card standards for IBM PC-compatible (DOS-based) systems. The long-term goal is to allow a variety of computer types and non-computer products to freely interchange PC cards. With these goals in mind the PCMCIA defined standards for PC Cards.

The Japanese Electronics Industry Development Association (JEIDA) began working on memory card standardization issues in 1985. In 1989 PCMCIA adopted JEIDA's 68-pin connector as its socket interface. To serve the goals of compatibility and interoperability JEIDA and PCMCIA began working jointly to ensure compatibility between their standards. In 1990 PCMCIA announced its first standard (release 1.0) and JEIDA released its fourth standard (release 4.0). As newer versions of the standards are released, JEIDA and PCMCIA continue to work closely to support each other's standards.

## Support for I/O-based PC Cards Added

The mobile computing environment also needed standardized small formfactor I/O devices that could be added to mobile systems as expansion devices. PCMCIA's release 2.0 added support for I/O devices that could be inserted into a PCMCIA socket. Like memory cards, these devices are designed to be automatically detected by the system when installed and automatically configured. This gives PC Cards the ability to be inserted into a PCMCIA socket after the system has already been powered up and is operational.

# The PC Card Standard

The PCMCIA standard defines the following major items:

- Physical design of the PC Card

- Physical design of the connector (socket)

- Electrical interface to PC Cards

- Software architecture

The PC Card standard has been designed with flexibility in mind, allowing PC Card socket implementations to be adapted for a wide variety of systems. Major features of today's PCMCIA standard include items listed in table 2-1.

PC Cards come in a wide range of memory and I/O devices. Memory devices include RAM, FLASH memory and various types of ROM. I/O devices include voice, data and FAX modems; network interface cards; wireless communications (such as, Global Positioning Systems (GPS), pagers and networks); AT Attachment (ATA) Hard Drives (also called IDE drives); small computer system interface (SCSI) adapters; and many others.

Three sizes of PC Cards are specified by the physical standard. Each type of card has the same electrical interface and planar dimensions, but the thickness

varies to accommodate designs that require more physical space. Generally, type I cards (3.3mm thick) are used for memory devices of various kinds, type II cards (5.0mm thick) for modems, LANs, etc., and type III cards (10.5mm thick) for devices such as ATA hard drives.

| Feature                                                        | Description                                                                                                                                                                                                                        |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Small Form-Factor: Three<br>Physical Device Types De-<br>fined | PCMCIA cards have a standard length and width of 85.6mm (3.370") X 54.0mm (2.126"). The card type determines the card's thickness — Type 1 = 3.3mm (0.130"); Type 2 = 5.0mm (0.197"); Type 3 = 10.5mm (0.413").                    |

| Host Bus Independence                                          | PCMCIA sockets can be connected to a wide variety of host<br>buses. Sockets are connected to the host systems via host<br>bus adapters designed for a particular bus interface.                                                    |

| Three Address Spaces                                           | PCMCIA supports common memory address space (standard memory addresses), attribute memory space (for automatic configuration) and I/O address space.                                                                               |

| 64 MB of Address Space                                         | Twenty-six address lines provide address space up to 64 MB for each address space.                                                                                                                                                 |

| 16-bit Data Path*                                              | Sixteen data lines permit word transfers to/from PC Cards.                                                                                                                                                                         |

| I/O Device Support                                             | I/O devices as well as memory devices can be imple-<br>mented in the credit card form-factor.                                                                                                                                      |

| Direct Memory Access<br>(DMA) Support                          | The PC Card standard incorporated DMA support so that<br>standard PC expansion devices that use DMA can be sup-<br>ported in PC Card implementations and take advantage of<br>the existing software.                               |

| Multifunction PC Cards Support                                 | The PC Card standard directly supports PC Cards that in-<br>clude multiple memory or I/O functions or both.                                                                                                                        |

| Automatic Configuration                                        | When installed, PC Cards are configured automatically without the need for user intervention.                                                                                                                                      |

| Software Transparency                                          | Software written for standard host bus devices can be used<br>when accessing the same device that is implemented in a<br>PC Card. Once the PC Card is installed and configured it<br>typically behaves like any other host device. |

| Easy to Implement Configu-<br>ration Software                  | PCMCIA provides a standard software interface, simplify-<br>ing the design and implementation of device-drivers<br>required to configuration PC Cards.                                                                             |

| Low Voltage Support                                            | The PC Card standard supports 5 volt, 3.3 volt and what PCMCIA refers to as X.X voltage (an arbitrary low voltage to be specified sometime in the future).                                                                         |

| Table 2-1 | . PCMCIA | Feature | Summary |

|-----------|----------|---------|---------|

|-----------|----------|---------|---------|

# **Chapter 2: The PCMCIA Solution**

| Feature                                                             | Description                                                                                                                                                                                                          |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Support for Several Differ-<br>ent File Systems on a Single<br>Card | PC Cards provide a means for specifying support for a variety of different data-recording formats and data or-<br>ganizations.                                                                                       |

| Execution of Code Directly<br>from Memory Card                      | PCMCIA memory cards, typically implemented as virtual<br>disks, can be accessed directly for code, without copying it<br>to main memory. This support requires a software protocol<br>called XIP (execute-in-place). |

Table 2-1 PCMCIA Feature Summary (continued)

\* The PC Card standard also defines a 32-bit PC Card and socket interface called CardBus.

# Summary of PCMCIA Releases

Since the first PCMCIA standard was released, many revisions and enhancements have been made. Table 2-2 highlights the chronology of releases, providing a perspective of the pace of change that has occurred in a relatively short period of time. The most recent release (February 1995) is called the PC Card standard, consisting of a 12 volume set listed in table 2-3.

| Specification   | Version     | Release Dates   |

|-----------------|-------------|-----------------|

| Card Standard   | 1.0         | November, 1990  |

|                 | 1.01        | September, 1991 |

|                 | 2.0         | November, 1992  |

|                 | 2.1         | July, 1993      |

| Socket Services | A.0         | June, 1991      |

|                 | 1.00        | August, 1991    |

|                 | 1.01        | September, 1991 |

|                 | 2.0         | November, 1992  |

|                 | 2.1         | July, 1993      |

| Card Services   | 1.0 (draft) | December, 1991  |

|                 | 2.0         | November, 1992  |

|                 | 2.1         | July, 1993      |

| ATA Interface   | 1.0         | July, 1992      |

|                 | 1.01        | November, 1992  |

Table 2-2. Evolution of the PCMCIA Specification

| Specification                        | Version | Release Dates  |

|--------------------------------------|---------|----------------|

| Auto-Indexing Mass<br>Storage (AIMS) | 1.0     | July, 1992     |

| 0                                    | 1.01    | November, 1992 |

| Card Extensions                      | 1.0     | November, 1992 |

Table 2-2. Evolution of the PCMCIA Specification (continued)

| T-11-2 2 T'-1 -    | (T. J' 'J  | 17-1    | Tuludad  | i 11   | DC | Cand Claudand |

|--------------------|------------|---------|----------|--------|----|---------------|

| Table 2-3. List of | Inatotauat | volumes | incluaea | in the | PC | Cara Standara |

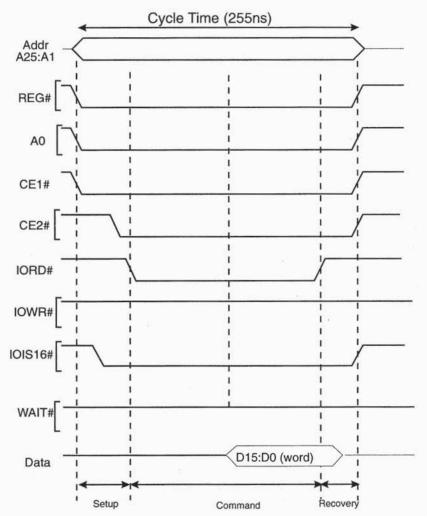

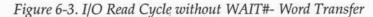

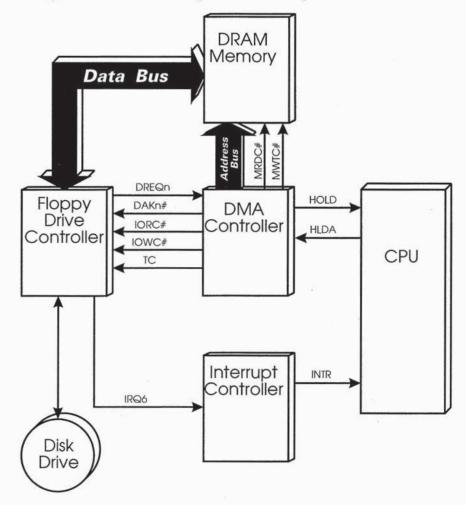

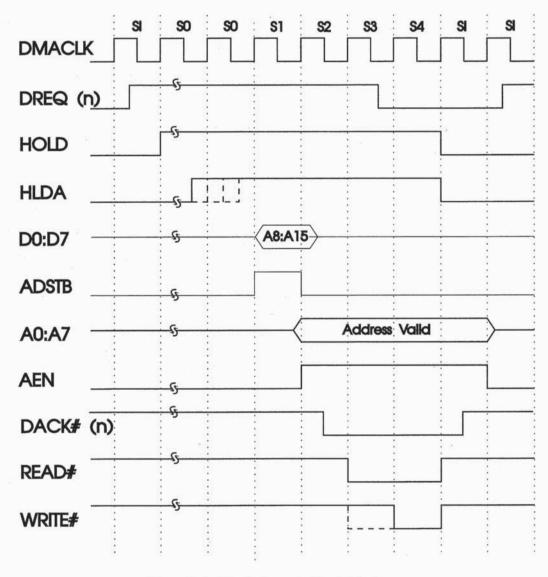

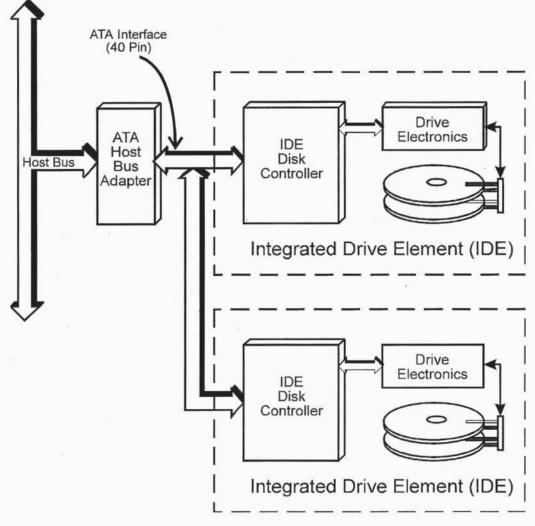

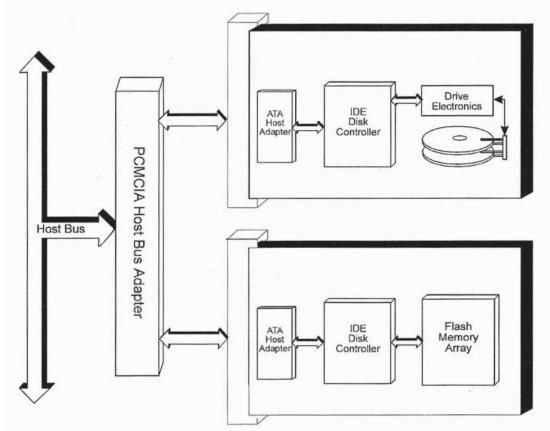

| Volume Name                   | Description of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |