| Please type a plus sign (+) in                                                                                                       | -                                                                                            | 11.5         | Approve                       | k Office: U.S. DEP             | PTO/SB/16 (8-00<br>0/31/2002. OMB 0651-0032<br>ARTMENT OF COMMERCI<br>a valid OMB control number |  |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------|-------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------|--|

|                                                                                                                                      | AL APPLICATION<br>filing a PROVISIONAL APP                                                   |              |                               |                                |                                                                                                  |  |

| P 7                                                                                                                                  | INVEN                                                                                        | TOR(S)       |                               |                                |                                                                                                  |  |

| Given Name (first and middle [if a                                                                                                   | ny]) Family Name or Sun                                                                      | name         | (City and                     | Residence<br>either State or F | <b>n</b>                                                                                         |  |

| Daniel M.                                                                                                                            | Fischer                                                                                      |              | 303-276 Eiw<br>Waterloo, O    |                                | NADA N2K 3M6                                                                                     |  |

| X Additional inventors are beir                                                                                                      | g named on the _1_ separately                                                                | numbere      | d sheets attached he          | preto                          |                                                                                                  |  |

| TITLE OF THE INVENTION (280 characters max)<br>SYSTEM AND METHOD FOR ADAPTING A USB TO PROVIDE<br>POWER FOR CHARGING A MOBILE DEVICE |                                                                                              |              |                               |                                |                                                                                                  |  |

| Direct all correspondence to:                                                                                                        | CORRESPONDE                                                                                  | NCE AD       | DRESS                         |                                |                                                                                                  |  |

| Customer Number                                                                                                                      |                                                                                              |              |                               | 1                              | mer Number                                                                                       |  |

| OR T                                                                                                                                 | pe Customer Number here                                                                      |              |                               | Bar Code La                    | ibel here                                                                                        |  |

| Firm or<br>Individual Name                                                                                                           | David B. Cochran,                                                                            | Esq.         |                               |                                |                                                                                                  |  |

| Address                                                                                                                              | Jones, Day, Reavis                                                                           |              | gue                           |                                |                                                                                                  |  |

| Address                                                                                                                              | North Point, 901 1                                                                           |              |                               |                                |                                                                                                  |  |

| City                                                                                                                                 |                                                                                              | ate          | OH                            | ZIP 4411                       | 4                                                                                                |  |

| Country                                                                                                                              | US Tele                                                                                      | phone 2      | 16/586-3939                   | Fax 216/5                      | 79-0212                                                                                          |  |

|                                                                                                                                      | ENCLOSED APPLICATION                                                                         | PARTS (      | check all that apply          | )                              |                                                                                                  |  |

| X Specification Number of Pa                                                                                                         | ages16                                                                                       | X            | COX(S)XINUXNDEX               | <u> </u>                       | A - 33 pgs.                                                                                      |  |

| X Drawing(s) Number of She                                                                                                           | ets 6                                                                                        | LXXX         | Assignment<br>Other (specify) |                                |                                                                                                  |  |

| Application Data Sheet. See                                                                                                          | 37 CFR 1.76                                                                                  | [X           | Oner (specify)                | Provisio                       | Attorney for<br>mal Appln. 2 p                                                                   |  |

| METHOD OF PAYMENT OF FILI                                                                                                            | NG FEES FOR THIS PROVISIO                                                                    | NAL APP      | LICATION FOR PAT              |                                |                                                                                                  |  |

|                                                                                                                                      | ity status. See 37 CFR 1.27.                                                                 |              |                               |                                | LING FEE                                                                                         |  |

|                                                                                                                                      | s enclosed to cover the filing fees                                                          | 3            |                               |                                | <u>10UNT (\$)</u>                                                                                |  |

| X fees or credit any overpay                                                                                                         | by authorized to charge filing<br>ment to Deposit Account Numbe<br>orm PTO-2038 is attached. | er: <u>5</u> | 01432                         | \$1                            | .90.00                                                                                           |  |

| The invention was made by an ag<br>United States Government.<br>No.<br>Yes, the name of the U.S. Govern                              | ency of the United States Government agency and the Government oc                            |              |                               | h an agency of t               | ne                                                                                               |  |

|                                                                                                                                      |                                                                                              |              |                               |                                |                                                                                                  |  |

| Respectfully submitted,                                                                                                              | 0                                                                                            |              | D-4- 2.                       | 2 10 1                         |                                                                                                  |  |

| SIGNATURE                                                                                                                            | B. Cochan                                                                                    |              |                               | 2101                           |                                                                                                  |  |

| TYPED or PRINTED NAMEDav                                                                                                             | id B. Cochran                                                                                |              | (if approp                    |                                | 39,142                                                                                           |  |

| TELEPHONE(216/586-3                                                                                                                  |                                                                                              |              | Docket Ni                     | imber:                         | 555255012132                                                                                     |  |

|                                                                                                                                      | FILING A PROVIS                                                                              |              |                               | ATIONE                         |                                                                                                  |  |

complete, including gathering, preparing, and submitting the complete provisional application to the PTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, Washington, D.C. 20231. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Box Provisional Application, Assistant Commissioner for Patents, Washington, D.C. 20231.

### PROVISIONAL APPLICATION COVER SHEET Additional Page

| Under the Paperwork Reduction Act of 1995, no                                                      | persons are requ | Docket Numb |                                               | Type                 | e a plus sign (+) e this box $\rightarrow$ | + |  |

|----------------------------------------------------------------------------------------------------|------------------|-------------|-----------------------------------------------|----------------------|--------------------------------------------|---|--|

| INVENTOR(S)/APPLICANT(S)                                                                           |                  |             |                                               |                      |                                            |   |  |

| Given Name (first and middle [if any]) Family or Sumame (City and either State or Foreign Country) |                  |             |                                               |                      |                                            |   |  |

| Dan G.                                                                                             | Radut            | 3<br>W      | 00 Regina St. N.,<br>aterloo, Ontario,        | , 1-1207<br>, CANADA | N2J 3B8                                    |   |  |

| Michael F.                                                                                         | Habicher         |             | 7 Ronald Road<br>ambridge, Ontario            | o, CANADA            | A N1S 4N2                                  |   |  |

| Quang                                                                                              | Luong            | U           | 4 Fairway Road<br>nit 10<br>itchener, Ontario | o, CANAD.            | A N2A 2N5                                  |   |  |

| Jonathan                                                                                           | Malton           | 1<br>K      | 00 Highland Cr.<br>itchener, Ontario          | o, CANAD             | A N2M 5C1                                  |   |  |

|                                                                                                    |                  |             |                                               |                      |                                            |   |  |

|                                                                                                    |                  |             |                                               |                      |                                            |   |  |

|                                                                                                    |                  |             |                                               |                      |                                            |   |  |

|                                                                                                    |                  |             |                                               |                      |                                            |   |  |

|                                                                                                    |                  |             |                                               |                      |                                            |   |  |

|                                                                                                    |                  |             |                                               |                      |                                            |   |  |

PTO/SB/16 (8-00) Approved for use through 10/31/2002. OMB 0651-0032 U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE he Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number.

Number 1 of 1

WARNING: Information on this form may become public. Credit card information should not be included on this form. Provide credit card information and authorization on PTO-2038.

Are and that have been and the trade of a struct that are that the

\*\*\*

+

# •

### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

Title of the Invention

System and Method for Adapting a USB to Provide Power for Charging a Mobile Device

Inventors

Daniel M. Fischer Dan G. Radut Mike Habicher Quang Luong Jonatahan Malton

555255-012-132

### TITLE OF INVENTION

٤

System and Method for Adapting a USB to Provide Power for Charging a Mobile Device

### FIELD OF INVENTION

This invention relates to rechargeable mobile devices having access to a Universal Serial Bus (USB). In particular, this invention relates to adapting power from the USB for use as a power source by the charging system of the mobile device to re-charge the portable power supply of the mobile device.

### BACKGROUND OF THE INVENTION

On one hand, the Universal Serial Bus (USB) is a communications bus for connecting a USB host controller such as a computer to peripheral devices. USB peripheral devices can be differentiated based on how they obtain their power in order to operate while connected. A self-powered peripheral has access to a power supply external to USB, whereas a bus-powered peripheral derives all of its power from the USB.

On the other hand, traditional mobile devices usually have a portable power supply that provides power to the mobile device while it is in service. Some portable power supplies are rechargeable so that when power is depleted and the portable power supply becomes discharged, a charging system can be used to restore the charge in the portable power supply. The charging system obtains power from an alternate power source, such as an AC outlet of a home or office electrical network, in order to recharge the portable power supply.

555255-012-132

Certain rechargeable mobile devices use a separate charging system such as a docking cradle. Other rechargeable mobile devices integrate a built-in charging system in order to facilitate recharging the portable power supply while it is still installed in the mobile device.

Recently the hitherto separate fields of USB and mobile devices have collided. Certain rechargeable mobile devices have evolved to access USB capabilities in order to become USB peripherals for the purpose of communicating with USB host controllers such as a computer. In some cases, USB capabilities have been incorporated into the docking cradle, whereas in other cases USB capabilities have been integrated into the rechargeable mobile device itself, in a manner analogous to the location of the traditional charging system.

Traditional rechargeable mobile devices having a USB already have access to two power supplies, specifically a portable power supply and an alternate power supply. Therefore USB capable rechargeable mobile devices traditionally operate as self-powered USB peripherals.

There is a need for a system and method of adapting the charging system of a USB capable rechargeable mobile device to use the power traditionally available on the USB as an alternate power source for recharging the portable power supply of the mobile device thereby eliminating the need for a separate charging and USB interfaces.

-3-

in

5

555255-012-132

### **BRIEF SUMMARY OF INVENTION**

\$

The sea and the sea of the sea and

Ē, da

dia tan ....

11

And Har

1. t.

It is an object of the invention to provide a system and method of adapting the charging system of a USB capable rechargeable mobile device to use the power traditionally available on the USB as an alternate power source for recharging the portable power supply of the mobile device.

Traditionally, the alternate power supply is of a much greater power capacity than the portable power supply, so that as much current as is needed can be drawn from the alternate power supply by the charging system in order to re-charge the portable power supply.

However, power traditionally available on the USB is 100mA to 500mA at 5V, which sometimes has to be shared amongst up to 127 self-powered peripherals. The exact amount of current available varies as peripherals are connected and disconnected from the USB.

In one embodiment of the invention, a charging circuit directly attached to the USB power lines draws current without regard to traditional USB functionality.

In another embodiment of the invention, a charging circuit uses a current analogous to the current being drawn from the USB on the Vbus rail. Several elements of the invention are provided by an ASIC thereby facilitating manufacture.

In yet another embodiment of the invention, the USB interface accessible to the mobile device isfurther adapted in order to favour two modes of operation: charging mode and communications mode.

Further features of the invention will be described or will become apparent in the course of the following detailed description.

#### 555255-012-132

-4-

# BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

In order that the invention may be more clearly understood, embodiments thereof will now be described in detail by way of example, with reference to the accompanying drawings, in which:

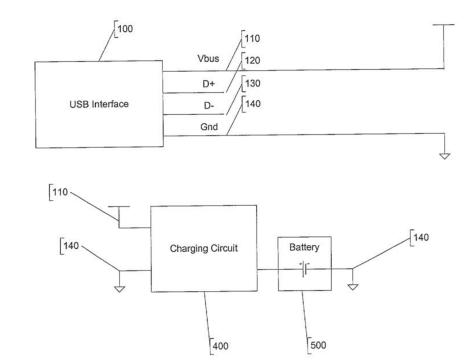

Figure 1 is a block diagram illustrating a non-enumerating embodiment;

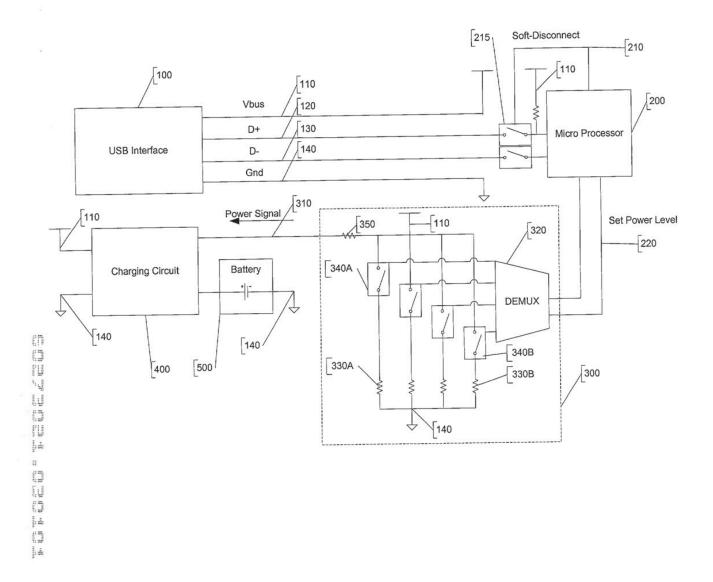

Figure 2 is a block diagram illustrating an enumerating embodiment;

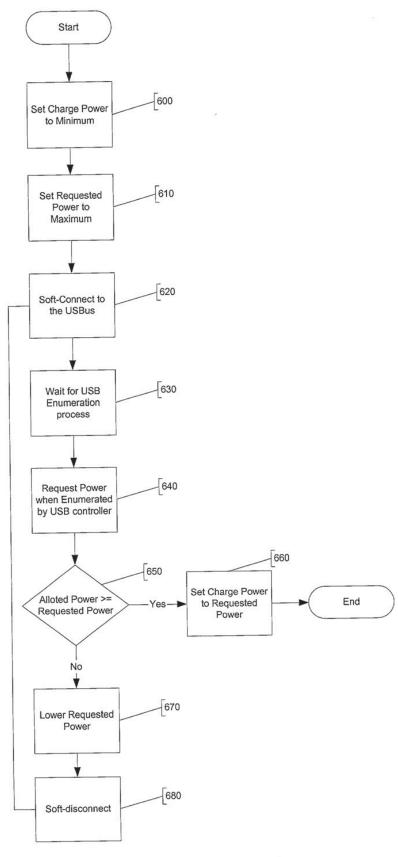

Figure 3 is a flowchart illustrating an enumerating method;

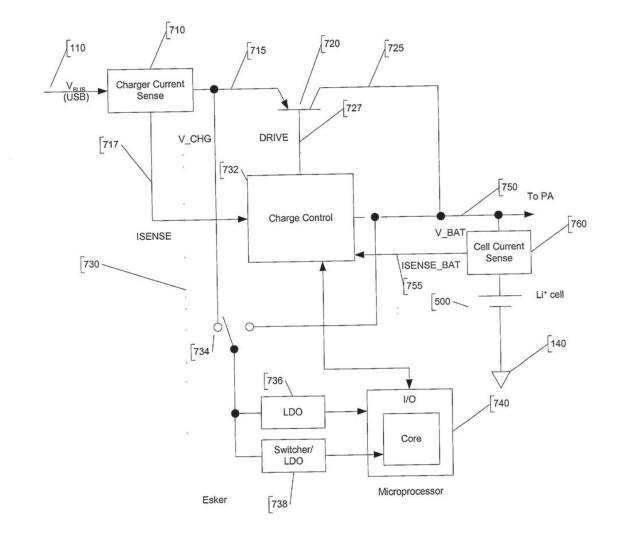

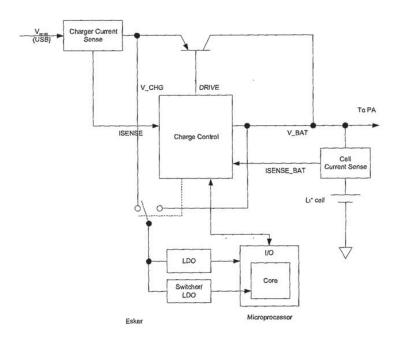

Figure 4 is a block diagram illustrating a current sensing embodiment, which can be used for both enumerating and nonenumerating purposes;

Figure 5 is a typical charge and voltage curve which illustrates a current-sensing method; and

Figure 6 is a flowchart which further illustrates a currentsensing method.

### DETAILED DESCRIPTION OF THE INVENTION

### NON-ENUMERATING EMBODIMENT

In one embodiment of the invention, a Li battery is charged by using the power available at a high-powered USB port, making no use of the D+ and D- data lines. A charger apparatus, such as a linear charger based on the LTC1734 charge controller, is used in this embodiment.

In reference to Figure 1, a USB interface 100 comprising a Vbus power line 100, D+ data line 120, D- data line 130 and GND

555255-012-132

í.n

ALL UND ALL ALL A

and the second

u un

turn ann

He first min

Huawei v. FISI Exhibit 1003 - 7/59

power line 140 is connected to a charging circuit 400 via the Vbus 110 and GND 140 power lines. A battery 500, to be charged, is connected at it's positive ent to the charging circuit 400, and at it's negative end to the GND power line 140.

It was determined experimentally that current can be drawn from several USB ports at a high rate, such as 500mA, without problem. As used in this description and in the appended claims, a high-power USB port is a USB port which can provide around 500mA to be drawn by the invention. Typical means of providing a highpower USB port are ensuring that the invention is the only USB device to attach to the USB port of a desktop computer, a laptop computer, or a self-powered hub.

First the charger is attached to the power lines of a highpowered USB port, such as that of a desktop computer. An open voltage value is measured on the USB prior to charging operation. This was about 5.16V in experiments.

Next, the battery is charged by drawing current at a rate of around 490mA.

The start of charge can be detected by observing that the Vbus voltage value settles to a charging voltage value. This was about 4.76V in experiments.

Finally, when the Vbus reaches its open value, the end of charge condition is detected. This was about 5.16V in experiments.

Additionally, when charging from the USB port of a portable computer, such as a laptop, after charging at the same rate (490mA) the Vbus voltage value settled to a charging voltage of about 4.65V. The difference between this laptop charging voltage value and the

555255-012-132

-6-

desktop charging voltage value can be used to sense what type of high-powered device the invention is attached to.

Furthermore, still in the case of a laptop, the USB voltage disappears when the internal laptop batteries were "completely" discharged. The voltage is present again immediately after the laptop is attached to its charger. Therefore, the invention adapts both the batteries of a laptop and the power adapter of the laptop to provide power to a rechargeable mobile device via the USB port.

Furthermore, it seems that certain high-power USB ports, such as a self-powered hub, appear to implement only an over-current protection, i.e. they turn off the voltage on the Vbus line for current values exceeding 700mA-800mA.

Thus a battery charger limiting its charge current value to 500mA can be powered from a high-power USB port without being necessary to be enumerated by the host, although such a device is not currently compatible with the current USB standard.

### ENUMERATING EMBODIMENT

In another embodiment of the invention, the USB interface accessible to the mobile device is further adapted in order to favour two modes of operation: a charging mode and the traditional communications mode. The traditional communications mode of operation of a USB peripheral is described in great detail in the current USB standard and is not discussed presently as it is obvious to a person skilled in the art. Both modes could be operated contemporaneously by a skilled person consulting both the standard and this specification, however this specification will positively set out and describe the charging mode.

-7-

Huawei v. FISI Exhibit 1003 - 9/59

In reference to Figures 2, one embodiment of a system used in the charging mode will be described presently in greater detail. In this embodiment, all lines of USB interface 100 are utilized. Specifically, the data D+ 120 and D- 130 lines are utilized to provide data communication between a USB controller (not shown) and a micro processor 200 of the present invention. The microporcessor 200 selectively controls soft-disconnect signal 120 to cause softdisconnect means means 210, such as a pair of electrically controlled switches to either connect or disconnect the microprocessor from the USB Interface 100. Microprocessor 200 also communicates with power level limiting means 300 via set power level signal 220. The power level limiting means 300, such as the switched current divider formed by a plurality of first resistor 330 and switch 340, and a single second resistor 350, provides a power signal 310, such as a reference current, to charging circuit 400. Charging circuit 400 is connected to power lines Vbus 110 and GND 140, and provides power to an attached battery 500 which is electrically connected at one end to the charging circuit 400, and at the other to the GND line 140 of the USB interface.

In charging mode, the mobile device USB interface operates as a bus-powered peripheral interface, with a temporary disregard to communications functionality in favour of obtaining the maximum amount of current from the USB host controller.

A method of use of the system illustrated in Figure 2 will be described presently, in reference to Figure 3. At step 600, the microporcessor 200 sets power level signal 220 to a minimum value, such as 0 mA. At step 610, the microprocessor sets a requested

#### 555255-012-132

-8-

power to a maximum value, such as 500mA. At step 620, the microprocessor 200 sends soft-disconnect signal 210 so that a connection to the USB interface is detected by a USB controller, which was not expressly shown in Figure 2.

At step 630, the microprocessor monitors data lines D+ 120 and D- 130 and waits for the enumeration process to begin. At step 640, When connecting, during the enumeration process, the USB host controller obtains a power request from the mobile device USB peripheral interface. However, the USB host controller might not allot the amount requested, and at Step 650 this is determined.

In order to maximize the likelihood of obtaining a large power allotment, the mobile device USB peripheral interface is capable of electrically disconnecting and reconnecting using switches in order to force a new enumeration process as if a user had unplugged and then plugged in the mobile device USB interface to the USB host controller. This is accomplished by steps 670 and 680 respectively, after which the method continues at step 620.

By comparing the amount of power requested and the amount of power allotted, the mobile device USB interface can determine whether or not to disconnect and attempt a request for less power. When the amount of power obtained corresponds with the amount of power allotted, the USB interface can proceed to operate in communications mode. This occurs at step 660, after which the method ends.

In communications mode, one additional element is taught by the invention over a traditional USB device taught by the standard. The mobile device USB interface operates as a traditional USB

555255-012-132

-9-

peripheral interface favouring traditional communications wherein the mobile device acts as either a self-powered or bus-powered peripheral, depending on the charge state of the portable power supply. If the portable power supply is sufficiently charged, the mobile device can act as a self-powered peripheral bypassing the charging mode. Conversely, if the portable power supply needs to be recharged, the mobile device can disconnect electrically and act as a bus-powered peripheral.

### CURRENT SENSING EMBODIMENT

In reference to Figures 4-5, a third embodiment of the present invention will be described. The Charger Current Sense block 710 provides a signal 717 to the Charge Control block 732 analogous to the current being drawn from the USB on the Vbus rail. The Charge Control block 732 uses this signal 717 to turn on the linear pass element 727, such as a bipolar transistor, to a greater or lesser degree by signal 727 as necessary in order that the total current does not exceed that required by the system. In the case of USB, this is for example either 100mA or 500mA. In addition and as a parallel control, the Charge Control block 732 monitors the battery voltage level via the V\_BAT 750 input, and controls the input current via the linear pass element 720 such that the battery voltage does not exceed the specified maximum, such as for example 4.20V. The Charge Control 732 block periodically inhibits delivery of current to the battery by switching off the linear pass element 720, and briefly monitoring the battery level at V\_BAT 750. This information is used to determine whether the linear pass element 720 should control solely the input current, such as monitored by the Charger Current

555255-012-132

-10-

Huawei v. FISI Exhibit 1003 - 12/59

c

Sense block 710, or the input current and the battery voltage during the following "charge on" cycle, which will be described in further detail in reference to Figure 5 below.

In the absence of input power at the Vbus 110, the Charge Control block 732 sets the switch 720 so that the first regulator 736 and second regulator 738 connect to and draw power from the battery 500 via the V\_BAT 750 input.

In order that the microprocessor 740 can monitor and control the charge system operation, the actual current delivered to the battery 500 is monitored by the Cell Current Sense block 760. This block produces a signal ISENSE\_BAT 755 that is analogous to the actual charge current, and which is converted by an analog-to-digital converter, which is not explicitly shown in the drawing but is comprised in Charge Control block 732, and which may be read serially by the microprocessor on a serial interface, which is also not shown explicitly in the drawings.

In order to favour manufacturing, a specification for an ASIC 730 to be known as Esker is provided in an appendix. The ASIC device performs charging, battery monitoring, low dropout voltage regulation, system reset control, and integration of a few other power consuming functions such as proximity sensor, vibrator, and buzzer.

LDOs 736,738 are Low Drop-Out regulators. An LDO is typically a linear regulator that can manage to keep its output within regulation tolerance, while the input falls to only a small amount above the output voltage. Note that regulator 738 may be a buck switching regulator external to Esker, as it might need to supply more current than a linear regulator could handle without overheating.

555255-012-132

-11-

ę.

In an embodiment using Esker, charge termination will be performed by the microprocessor, as the charge current will be monitored.

Note that the Charge Control block 732 also operates an electronic switch 727 when voltage is detected at the Vbus input 110. This switch diverts power as necessary from the source to operate the regulators 736.738 powering the microprocessor 740, in order to ensure that it is possible, even in the case of a severely discharged lithium battery 500, that the necessary communications and charge management functions may be performed.

One significant innovation in the configuration illustrated in Figure 4 is that the controlled parameter is system input current, rather than battery charge current. Varying of the battery charge current is used as the means for controlling (limiting) the system input current, thereby compensating for varying power drawn by the microprocessor.

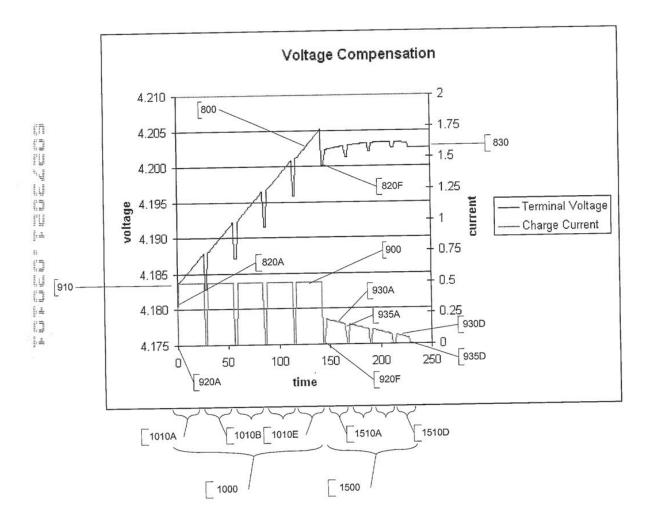

In reference to Figure 5, a "periodic charge" and "battery voltage compensation" method using the system of Figure 4 is illustrated in great detail. A battery voltage curve 800 and battery current curve 900 which illustrate the method of charging are depicted. A constant charge current 910, such as in this example 500mA, is delivered to the battery until during a constant charge current period 1000, for instance during the first five constant charge current cycles 1010A,B,C,D,E in the figure. Between each cycle, the current is stopped 920A,B,C,D,E,F and the battery voltage 820A,B,C,D,E,F (which climbs during charging) is measured. At the end of the constant charge current period 1000, the voltage

555255-012-132

-12-

ŵ.

820A,B,C,D,E is sampled to be at or above a critical threshold, such as 4.2V 820F. In the next cycles 1510A,B,C,D, the charge current is regulated such that the voltage 830 stays approximately constant during a constant voltage period 1500. When the sampled current 930A,B,C reaches a cirtical threshold, such as 50mA 930D, the charging method finishes. The current is still set to zero between constant current charging cycles 935A,B,C,D.

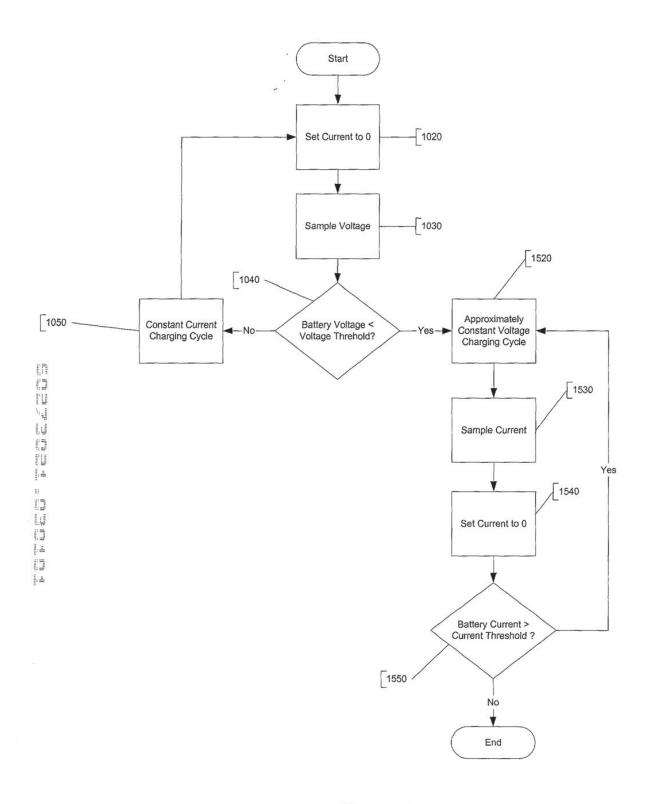

This method is illustrated further in Figure 6 with a flowchart. At step 1020, the charge current is set to zero. This corresponds to points 920 of Figure 5. At step 1030, the voltage is sampled 820. At step 1030, the sampled voltage is compared to a threshold, such as 4.20 V. In the event that the sampled voltage is below the threshold, at step 1050 a constant current charging cycle as described above in reference to Figure 5 ensues, aftewhich the method continues at step 1020. However, in the event that the sampled voltage is determined to be above or equal to the threhold at step 1030, the method continues at step 1520 in constant current charging mode 1500. At step 1520, a constant current charge cycle, as described above in reference to Figure 5 ensures. At step 1530, the current 930 is sampled. At step 1540, the current 935 is set to zero. At step 1550, the sampled current 930 is compared to a threshold. In the event that the current is greater than the threshold, the method continues at step 1520. In the event that the sampled current 930 is below the threshold, the method ends.

It will be appreciated that the above description relates to embodiments by way of example only. Many variations on the invention will be obvious to those knowledgeable in the field, and

555255-012-132

-13-

٩.

such obvious variations are within the scope of the invention as described and claimed, whether or not expressly described.

۹

.

555255-012-132

Huawei v. FISI Exhibit 1003 - 16/59

CLAIMS

555255-012-132

Huawei v. FISI Exhibit 1003 - 17/59

## ABSTRACT

then then and the then the set of the set of

555255-012-132

Huawei v. FISI Exhibit 1003 - 18/59

Figure 1

Figure 2

555255-012-132

Huawei v. FISI Exhibit 1003 - 20/59

555255-012-132

Figure 4

Figure 5

Figure 6

555255-012-132

#### Attorney Docket No. 555255012132

### PATENT

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Application of: Daniel M. Fischer Dan G. Radut Michael F. Habicher Quang Luong Jonathan Malton Application No.: Not Yet Assigned Filed: Herewith For: SYSTEM AND METHOD FOR ADA

:: SYSTEM AND METHOD FOR ADAPTING A USB TO PROVIDE POWER FOR CHARGING A MOBILE DEVICE

#### POWER OF ATTORNEY FOR PROVISIONAL APPLICATION

Each inventor, identified above and signing below, hereby appoints each of the following as my attorneys with full power of substitution and revocation, to prosecute this application and to transact all business in the Patent and Trademark Office connected therewith:

David B. Cochran, Registration No. 39,142; Kenneth R. Adamo, Registration No. 27,299; John V. Biernacki, Registration No. 40,511; Barbara Arndt, Registration No. 37,768; Regan J. Fay, Registration No. 26,878; F. Drexel Feeling; Registration No. 40,602; Calvin P. Griffith, Registration No. 34,831; Warren M. Haines II, Registration No. 40,632; Shawn A. McClintic, Registration No. 45,856; Timothy J. O'Hearn, Registration No. 31,552; Stephen D. Scanlon, Registration No. 32,755; Jenny L. Sheaffer, Registration No. 45,099; Duane Switzer, Registration No. 22,431; Michael W. Vary, Registration No. 30,811; and James L. Wamsley, III, Registration No. 31,578;

all of the firm of Jones, Day, Reavis & Pogue, North Point, 901 Lakeside Avenue, Cleveland, Ohio 44114; Krishna K. Pathiyal, Registration No. 44,435, Research In Motion Limited, 295 Phillip Street, Waterloo, Ontario, Canada N2L 3W8; and Charles B. Meyer, Registration No. 33,563, Research In Motion Limited, 25227 Grogan's Mill Road, Suite 125, The Woodlands, Texas 77380.

Page 1 of 2

In that the dark over the set of the the the the the the set of th

I hereby designate the following as my mailing address and telephone number:

David B. Cochran, Esq. Jones, Day, Reavis & Pogue North Point, 901 Lakeside Avenue Cleveland, Ohio 44114 (216) 586-3939

Each inventor, identified above and signing below, authorizes the above named attorney(s) and/or agents to accept and follow instructions from his/her representative(s).

Inventor(s)

Date: Feb 19/01 Daniel M. Fischer Date: 10/01 Dan G. Radut Date: Feb 19, 2001. Michael F. Habicher Date: February 19, 2001 Quang Luong Date: Fol 19 01 Jonathan Malton

Signature

New New "." - unit ALL AND £! Sum. 1 martin in the second second ١.a. 14

Page 2 of 2

**Confidential & Proprietary Information**

**Preliminary Information**

Project:Esker ASIC SpecificationASIC Part #:ANA-03126-002Author:Mike Habicher, mikeh@rim.net, x2207Date:16-Feb-2001Document:03126002, rev BVendor:Vendor Part #:

## **Esker ASIC Specification**

### Research in Motion, Ltd.

295 Phillip Street Waterloo, ON N1S 4N2 Canada

Tel.: +1 519 888-7465 Fax: +1 519 888-6906

i,

Copyright © 1999-2000, Research in Motion, Ltd. All Rights Reserved. 03126002 draft Page 1

Feber ASIC Specification

Huawei v. FISI Exhibit 1003 - 27/59

### 1 Table of Contents

>

e

| 1<br>2<br>3<br>4<br>5 | LIST<br>LIST<br>DOC | T OF TA<br>T OF FIC<br>CUMEN<br>RODUC | BLES.<br>GURES<br>T HIST<br>TION. | ORY                                | 5<br>5<br>6<br>7 |

|-----------------------|---------------------|---------------------------------------|-----------------------------------|------------------------------------|------------------|

|                       | 5.2                 |                                       |                                   | CONTACTS                           |                  |

|                       | 5.2                 |                                       |                                   | L DESCRIPTION                      |                  |

|                       |                     |                                       |                                   | S                                  |                  |

|                       | 5.4                 |                                       |                                   | 5                                  |                  |

| 6                     | REC<br>6.1          | UIREM<br>GEN                          | ERAL                              |                                    | 8                |

|                       |                     | 6.1.1                                 | Block                             | c Diagram                          | 8                |

|                       |                     | 6.1.2                                 | Pin L                             | Descriptions                       | 9                |

|                       |                     | 6.1.3                                 | Pack                              | aging1                             | 2                |

|                       |                     | 6.1.4                                 | ESD                               | and Latch-Up 1                     | 2                |

|                       |                     | 6.1.5                                 | Exter                             | nal Components 1                   | 2                |

|                       |                     | 6                                     | .1.5.1                            | Magnetics 1                        | 2                |

|                       |                     | 6                                     | .1.5.2                            | Capacitors 1                       | 2                |

|                       |                     | 6                                     | .1.5.3                            | Resistors 1                        | .2               |

|                       |                     | 6                                     | .1.5.4                            | Other Devices (Transistors, etc.)  | 2                |

|                       |                     | 6.1.6                                 | Inpu                              | t Power and Power Sequencing 1     | 2                |

|                       | 6.2                 | Moi                                   | DULES .                           |                                    | 3                |

|                       |                     | 6.2.1                                 | Batte                             | ery Monitoring and Charge Control1 | !3               |

|                       |                     | 6                                     | 5.2.1.1                           | PA_LOBAT_N1                        | 13               |

|                       |                     | 6                                     | 5.2.1.2                           | Charging 1                         | 14               |

|                       |                     | 6.2.2                                 | Rese                              | t Controller                       | 16               |

|                       |                     | 6.2.3                                 | Band                              | lgap Reference                     | 16               |

|                       |                     | 6.2.4                                 | Anal                              | og to Digital Converter with MUX   | 16               |

|                       |                     | 6.2.5                                 | Annı                              | unciator Drivers                   | 17               |

|                       |                     | e                                     | 5.2.5.1                           | Vibrator Motor                     | 17               |

|                       |                     | 6                                     | 5.2.5.2                           | Buzzer/Ringer                      | 17               |

|                       |                     | 6                                     | 5.2.5.3                           | Keyboard Backlighting LED Array    | 17               |

|                       |                     | (                                     | 5.2.5.4                           | Notification LED                   |                  |

| Co                    | ovrigh              | t © 199                               | 9-2000.                           | , Research in Motion, Ltd. Page    | 2                |

Copyright © 1999-2000, Research in Motion, Ltd. All Rights Reserved. 03126002 draft

Feker ASIC Specification

•

٠

| 6.2.6                   | Genera            | I-Purpose Outputs              |          |

|-------------------------|-------------------|--------------------------------|----------|

| 6.2.7                   | SIM In            | terface                        |          |

| 6.2.8                   | Serial            | Interface                      |          |

| 6.2.9                   | Registe           | r File                         |          |

| 6.2                     | 2.9.1             | ASIC_ID Register               | 19       |

| 6.2                     | 2.9.2             | CONTROL Register               |          |

| 6.2                     | 2.9.3             | IRQ_EN Register                |          |

| 6.2                     | 2.9.4             | IRQ_FLAG Register              |          |

| 6.2                     | 2.9.5             | ADC_CTRL Register              |          |

| 6.2                     | 2.9.6             | ADC_RES Register               |          |

| 6.2                     | 2.9.7             | INPUT Register                 |          |

| 6.2.10                  | Interra           | upt Controller                 |          |

| 6.2                     | 2.10.1            | O_TEMP Interrupt               |          |

| 6.2                     | 2.10.2            | O_VOLT Interrupt               |          |

| 6.2                     | 2.10.3            | U_VOLT Interrupt               |          |

| 6.2                     | 2.10.4            | SER_ERR Interrupt              |          |

| 6.2                     | 2.10.5            | BAT_DOOR Interrupt             | 24       |

| 6.                      | 2.10.6            | SIM_DET Interrupt              |          |

| 6.:                     | 2.10.7            | ADC Interrupt                  | 24       |

| 6.                      | 2.10.8            | PA_LOBAT Interrupt             | 24       |

| 6.                      | 2.10.9            | PROX_SW Interrupt              | 24       |

| 6.                      | 2.10.10           | CHG_DET Interrupt              | 24       |

| 6.2.11                  | Regul             | ators                          |          |

| 6.                      | 2.11.1            | REG1: Digital I/O              |          |

| 6.                      | 2.11.2            | REG2: Digital Core             |          |

| 6.                      | 2.11.3            | REG3: Radio Analog             | 25       |

| 6.                      | 2.11.4            | REG4: TCXO                     |          |

| 6.                      | .2.11.5           | REG5: PLL                      |          |

| 6.                      | .2.11.6           | REG6: Analog Baseband CODEC    |          |

| 6.                      | .2.11.7           | REG7: PLL Digital              |          |

| 6.                      | .2.11.8           | REG8: Voice-Band Analog        |          |

| 6.                      | .2.11.9           | Suspend Mode                   |          |

| 7 ELECTRICA<br>7.1 ABSO | AL SPE<br>OLUTE N | CIFICATIONS<br>MAXIMUM RATINGS | 27<br>27 |

|                         | -2000, 1          | Research in Motion, Ltd.       | Page 3   |

Feber ASIC Snerification

All Rights Reser

| Confidenti | al & Proprietary Information | <b>Preliminary Information</b> |

|------------|------------------------------|--------------------------------|

| 7.2        | ELECTRICAL CHARACTERISTICS   |                                |

5

¢

Copyright © 1999-2000, Research in Motion, Ltd. All Rights Reserved. 03126002 draft Page 4

Rekar ASIC Snacification

### 2 List of Tables

.

÷

| Fable 6-1: Key to Pin Types9                         |   |

|------------------------------------------------------|---|

| Fable 6-2: Pin Descriptions, Grouped by Function   9 |   |

| Fable 6-3: Charge Termination Thresholds             |   |

| Table 6-4: SIM Interface Operating Modes             |   |

| Table 6-5: SER_CS Bus Behaviour                      |   |

| Table 6-6: ASIC Register File                        |   |

| Γable 6-7: Bit Attribute Definitions                 | ŀ |

| Table 6-8: Charger Modes 20                          | 1 |

| Table 6-9: ADC MUX Channel Selection   22            |   |

| Table 6-10: Interrupts Generated by Esker    23      |   |

### 3 List of Figures

| Figure 6-1: Esker ASIC Functional Block Diagram | 8 |

|-------------------------------------------------|---|

| Figure 6-2: Power Sequencing                    | 3 |

Copyright © 1999-2000, Research in Motion, Ltd. All Rights Reserved. 03126002 draft

Page 5

Feker ASIC Specification

**Confidential & Proprietary Information**

**Preliminary Information**

### 4 Document History

.

٠

Copyright © 1999-2000, Research in Motion, Ltd. All Rights Reserved. 03126002 draft

Page 6

Feber ASIC Snecification

Huawei v. FISI Exhibit 1003 - 32/59

**Preliminary Information**

#### Introduction 5

### 5.1 Scope

This document defines the requirements for an ASIC that provides power management functionality for a low power two-way wireless PDA.

Any information and data contained in this document is subject to change by Research in Motion, Ltd. (RIM).

Deviations from the specifications contained in this document are subject to approval by RIM.

#### 5.2 Technical Contacts

Technical contacts at RIM for this specification are:

| Mike Habicher   | mikeh@rim.net   | 519-888-7465, x2207 |

|-----------------|-----------------|---------------------|

| Jonathan Malton | jmalton@rim.net | 519-888-7465, x2451 |

### 5.3 Functional Description

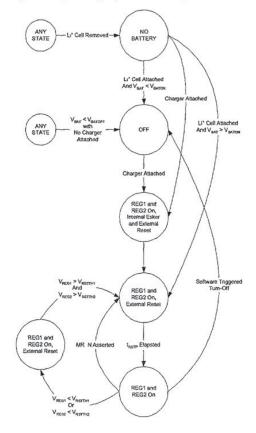

The power supply ASIC performs the following primary functions:

- 1. Monitor and control charging of the lithium-ion (Li<sup>+</sup>) cell;

- 2. Provide several regulated voltage outputs to the PDA systems;

- 3. Provide the necessary drive circuitry for the PDA annunciators;

- Provide voltage translation for the Subscriber Identity Module (SIM) interface. 4.

#### 5.4 References

The following documents form part of this specification to the extent specified herein:

- 1. EIA/JESD22-A114-A "Electrostatic Discharge (ESD) Sensitivity Testing/Human Body Model (HBM)", Electronic Industries Association.

- 2. EIA/JESD78 "IC Latch-Up Test", Electronic Industries Association.

- 3. GSM 11.11 "Specification of the Subscriber Identity Module-Mobile Equipment (SIM-ME) Interface", European Telecommunications Standards Institute, France.

- GSM 11.12 "Specification of the 3 Volt Subscriber Identity Module-Mobile Equipment (SIM-4. ME) Interface", European Telecommunications Standards Institute, France.

- JESD22-C101 "Field-Induced Charged-Device Model Test Method for Electrostatic Discharge 5. Withstand Thresholds of Microelectronic Components", Electronic Industries Association.

- 6. Universal Serial Bus Revision 2.0 Specification, USB Implementers Forum, Oregon.

Page 7

Feker ASIC Specification

22

in.

### 6 Requirements

### 6.1 General

x

.

### 6.1.1 Block Diagram

| BUZ_DR                                                                                                                     | 1             |                                       |       | PWM_BUZ                                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------|-------|----------------------------------------------|--|--|

| VIB_DR                                                                                                                     |               |                                       |       | PWM_VIB                                      |  |  |

| KBBL_DR                                                                                                                    |               | Annunciator Drivers                   |       | PWM_KBBL                                     |  |  |

| LED_DR                                                                                                                     |               |                                       | -     | PWM_LED                                      |  |  |

|                                                                                                                            |               |                                       |       |                                              |  |  |

| RESET_                                                                                                                     |               |                                       |       | MR_N                                         |  |  |

|                                                                                                                            |               | Reset Contoller                       |       |                                              |  |  |

|                                                                                                                            | '   }         |                                       |       | V_BAT                                        |  |  |

| PA_LOBAT_                                                                                                                  |               |                                       |       | V_CHG                                        |  |  |

|                                                                                                                            |               |                                       |       | ISENSE_H                                     |  |  |

| DRIV                                                                                                                       |               |                                       |       | ISENSE_L                                     |  |  |

|                                                                                                                            |               | Battery Montoring and Charge Control  |       | ISENSE_BAT                                   |  |  |

| GN                                                                                                                         |               | battery monitoring and onarge conitor |       |                                              |  |  |

| GN                                                                                                                         |               |                                       | 1     | HCHG_PROG                                    |  |  |

| GN                                                                                                                         |               |                                       |       |                                              |  |  |

|                                                                                                                            | וות           |                                       |       |                                              |  |  |

| VREF_BY                                                                                                                    | , 111         |                                       |       |                                              |  |  |

|                                                                                                                            | 111-1         | Bandgap Reference                     |       |                                              |  |  |

|                                                                                                                            |               | V_REF                                 |       |                                              |  |  |

|                                                                                                                            |               |                                       |       |                                              |  |  |

| R                                                                                                                          | 1111          | Interrupt Controller                  | 11 1  |                                              |  |  |

|                                                                                                                            |               |                                       |       | PROX_SW                                      |  |  |

|                                                                                                                            |               |                                       |       | SIM_DET                                      |  |  |

| BAT_DOO                                                                                                                    |               |                                       |       |                                              |  |  |

| BAT_CH                                                                                                                     |               | Senal Interface and Register File     |       | SER_CS                                       |  |  |

| LCD_BL_E                                                                                                                   |               |                                       |       | SER_CLK                                      |  |  |

| GPO                                                                                                                        |               |                                       |       | SER_DATA                                     |  |  |

| GPO                                                                                                                        |               |                                       |       | • • • • •                                    |  |  |

|                                                                                                                            | 1             |                                       |       |                                              |  |  |

|                                                                                                                            | ,             |                                       | 11111 |                                              |  |  |

| TEM                                                                                                                        | -             |                                       |       |                                              |  |  |

| PACK_TEM                                                                                                                   |               | ADC                                   |       |                                              |  |  |

| AU                                                                                                                         |               |                                       |       | PACK_ID                                      |  |  |

|                                                                                                                            |               | MUX                                   | ++++  |                                              |  |  |

| REG1 (VCC                                                                                                                  |               |                                       | 1111  |                                              |  |  |

|                                                                                                                            | $\rightarrow$ |                                       |       |                                              |  |  |

| REG2 (VCCC                                                                                                                 |               |                                       |       | 227094V                                      |  |  |

|                                                                                                                            |               |                                       |       | RF_ON                                        |  |  |

| REG3A (V_RF                                                                                                                |               |                                       |       | TX_ON                                        |  |  |

| REG38 (V_T)                                                                                                                |               |                                       |       | CLK_ON                                       |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC                                                                                                |               | LDO Regulators                        | PLLON |                                              |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLL                                                                                 |               | LDO Regulators                        |       | ANA_ON                                       |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLL<br>REG6 (VCCA                                                                   |               | LDO Regulators                        |       |                                              |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLL                                                                                 |               | LDO Regulators                        |       | PLLD_ON                                      |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLL<br>REG6 (VCCA                                                                   |               | LDO Regulators                        |       | PLLD_ON                                      |  |  |

| REG8 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PL<br>REG6 (VCC)<br>REG7 (V_PLLC<br>REG8 (V_VO)                                      |               | LDO Regulators                        |       |                                              |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLL<br>REG6 (VCCA<br>REG7 (V_PLL                                                    |               | LDO Regulators                        |       | PLLD_ON                                      |  |  |

| REG8 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PL<br>REG6 (VCC)<br>REG7 (V_PLLC<br>REG8 (V_VO)                                      |               | LDO Regulators                        |       | PLLD_ON<br>VOX_ON                            |  |  |

| REG8 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLL<br>REG6 (VC_PLL<br>REG6 (V_VPLL<br>REG8 (V_VO)<br>VCAP                           |               | LDO Regulators                        |       | PLLD_ON<br>VOX_ON<br>SIM_SUPPLY              |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLI<br>REG6 (VCC/<br>REG7 (V_PLIL<br>REG8 (V_VO)<br>VCAP                            |               | LDO Regulators                        |       | PLLD_ON                                      |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLI<br>REG5 (V_PLI<br>REG6 (V_CV)<br>REG6 (V_VO)<br>VCAP<br>VCAP<br>SIM_VO          |               |                                       |       | PLLD_ON<br>VOX_ON<br>SIM_SUPPLY<br>SIM_PROG  |  |  |

| REG38 (V_T)<br>REG4 (V_TCXC<br>REG5 (V_PLL<br>REG5 (V_PLL<br>REG5 (V_VO)<br>REG5 (V_VO)<br>VCAP<br>VCAP<br>SM_VC<br>RST258 |               |                                       |       | LD_ON<br>X_ON<br>A_SUPPLY<br>A_PROG<br>A_RST |  |  |

### Figure 6-1: Esker ASIC Functional Block Diagram

Page 8

Feber ASIC Snerification

Copyright © 1999-2000, Research in Motion, Ltd. All Rights Reserved. 03126002 draft

### 6.1.2 Pin Descriptions

The symbols listed in the Type column of Table 6-2 are defined in Table 6-1 below.

| Code | Description              |

|------|--------------------------|

| A    | Analog signal            |

| В    | Bidirectional            |

| D    | Digital signal. See 7.2. |

| I    | Input                    |

| 0    | Output                   |

| Р    | Power                    |

| -pu  | Pull-up                  |

| -pd  | Pull-down                |

Table 6-1: Key to Pin Types

All signals listed as digital ("D") in Table 6-2 will be CMOS-compatible and referenced to REG1. See the Electrical Characteristics section for details.

| Туре  | Pin Name        | Description                                                       |   |  |  |

|-------|-----------------|-------------------------------------------------------------------|---|--|--|

| LDO C | Control Signals |                                                                   |   |  |  |

| DI    | ANA_ON          | Active-high logic signal to enable REG6 (VCCA). See 6.2.11.6.     | 1 |  |  |

| DI    | CLK_ON          | Active-high control signal to enable REG4 (V_TCXO). See 6.2.11.4. | 1 |  |  |

| DI    | PLL_ON          | Active-high control signal to enable REG4 (V_TCXO). See 6.2.11.4. |   |  |  |

| DI    | PLLD_ON         | Active-high control signal to enable REG7 (V_PLLD). See 6.2.11.7. | - |  |  |

| DI    | RF_ON           | Active-high control signal to enable REG3A (V2_8RF). See 0.       |   |  |  |

| DI    | TX_ON           | Active-high control signal to enable REG3B (V_TX). See 0.         |   |  |  |

| DI    | VOX_ON          | Active-high control signal to enable REG8 (V_VOX). See 6.2.11.8.  |   |  |  |

| LDO C | Jutputs         |                                                                   |   |  |  |

| AO    | REG1            | Voltage regulator output 1, VCC. See 6.2.11.1.                    | 1 |  |  |

| AO    | REG2            | Voltage regulator output 2, VCCD. See 6.2.11.2.                   |   |  |  |

| AO    | REG3A           | Voltage regulator output 3A, V_RF. See 0.                         |   |  |  |

| AO    | REG3B           | High-side load switch from REG3A to supply V2_8TX. See 0.         |   |  |  |

| Table 6-2: Pin Descriptions, Grouped by Function | Table 6-2: Pin | Descriptions. | Grouped b | v Functio |

|--------------------------------------------------|----------------|---------------|-----------|-----------|

|--------------------------------------------------|----------------|---------------|-----------|-----------|

Copyright © 1999-2000, Research in Motion, Ltd.

Page 9

Feber ASIC Snorification

All Rights Reserved.

### **Confidential & Proprietary Information**

### **Preliminary Information**

| Туре     | Pin Name           | Description                                                              | #          |

|----------|--------------------|--------------------------------------------------------------------------|------------|

| AO       | REG4               | Voltage regulator output 4, V_TCXO. See 6.2.11.4.                        |            |

| AO       | REG5               | Voltage regulator output 5, V_PLL. See 6.2.11.5.                         | -          |

| AO       | REG6               | Voltage regulator output 6, V_VCCA. See 6.2.11.6.                        |            |

| AO       | REG7               | Voltage regulator output 7, V_PLLD. See 6.2.11.7.                        |            |

| AO       | REG8               | Voltage regulator output 8, V_VOX. See 6.2.11.8.                         | $\vdash$   |

| Annun    | ciator Driver Inpu | ts                                                                       |            |

| DI       | PWM_BUZ            | Buzzer/ringer driver PWM input from microprocessor. See 6.2.5.2.         | -          |

| DI       | PWM_KBBL           | Keyboard backlight driver PWM input from microprocessor. See 6.2.5.3.    |            |

| DI       | PWM_LED            | LED drive PWM input from microprocessor. See 6.2.5.4.                    | 1          |

| DI       | PWM_VIB            | Vibrator motor driver PWM input from microprocessor. See 6.2.5.1.        |            |

| Annun    | ciator Driver Outp | puts                                                                     |            |

| AO       | BUZ_DRV            | Buzzer/ringer driver output. See 6.2.5.2.                                | Γ          |

| AO       | KBBL_DRV           | Keyboard backlight driver output. See 6.2.5.3.                           | $\vdash$   |

| AO       | LED_DRV            | LED driver output. See 6.2.5.4.                                          | 1          |

| AO       | VIB_DRV            | Vibrator driver output, controlled through the serial port. See 6.2.5.1. | 1          |

| SIM In   | terface Signals    | 1                                                                        |            |

| DO       | CLK2SIM            | Level-shifted serial clock to the SIM. See 6.2.7.                        | Τ          |

| DB       | DATA2SIM           | Level-shifted serial data stream to/from SIM. See 6.2.7.                 | 1          |

| DO       | RST2SIM            | Level-shifted reset signal to SIM. See 6.2.7.                            | $\square$  |

| DI       | SIM_CLK            | SIM serial clock signal from microprocessor. See 6.2.7.                  | 1          |

| DB       | SIM_DATA           | SIM serial data stream to/from microprocessor. See 6.2.7.                | $\vdash$   |

| DI       | SIM_DET            | Detects the presence of a SIM card; connected to a switch. See 6.2.7.    | 1          |

| DI       | SIM_PROG           | Programs the level of the SIM output. See 6.2.7.                         | 1          |

| DI       | SIM_RST            | SIM reset signal from microprocessor. See 6.2.7.                         | 1          |

| DI       | SIM_SUPPLY         | Enables the SIM power supply and output to the SIM. See 6.2.7.           | 1          |

| Р        | SIM_VCC            | Power supply for SIM. See 6.2.7.                                         | 1-         |

| Serial I | nterface           | 1                                                                        | 1          |

| DL       | SER_CLK            | Serial clock signal. See 6.2.8.                                          | Γ          |

| DI       | SER_CS             | Active-high signal to frame serial communications. See 6.2.8.            | $\uparrow$ |

|          |                    | 1                                                                        | 1          |

Copyright © 1999-2000, Research in Motion, Ltd. All Rights Reserved. 03126002 draft

Page 10

Fekar ASIC Snarification

Huawei v. FISI Exhibit 1003 - 36/59

.

.

## **Preliminary Information**

| Туре    | Pin Name                                                                                                               | Description                                                                                                                                                                                                    | #       |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| A       | DRIVE                                                                                                                  | Output to control external pass element during charging. See 6.2.1.                                                                                                                                            |         |  |  |  |  |

| A       | HCHG_PROG                                                                                                              | Attache resistor from here to ground to program high current charging.<br>See 6.2.1 and 6.2.9.2.                                                                                                               |         |  |  |  |  |

| AI      | ISENSE_BAT                                                                                                             | ow side of battery current sensor.                                                                                                                                                                             |         |  |  |  |  |

| AI      | ISENSE_H                                                                                                               | High side of charge supply current sensor. See 6.2.1.                                                                                                                                                          |         |  |  |  |  |

| AI      | ISENSE_L                                                                                                               | Low side of charge supply current sensor. See 6.2.1.                                                                                                                                                           |         |  |  |  |  |

| DO      | PA_LOBAT_N Active-low, open-drain output to hard-disable the RF power amplifier when battery voltage drops. See 6.2.1. |                                                                                                                                                                                                                |         |  |  |  |  |

| P       | TEMP_CHK                                                                                                               | High-side load switch output that supplies power from $V_{BAT}$ to an external temperature sensor; also powers up an internal Li <sup>+</sup> cell voltage scaling network for the ADC. See 6.2.4 and 6.2.9.2. |         |  |  |  |  |

| Miscell | aneous Inputs and                                                                                                      | Outputs                                                                                                                                                                                                        |         |  |  |  |  |