Table 5-3 lists information about different-sized high-speed control transfers and the maximum number of transfers possible in a microframe. This table was generated assuming that there is one Data stage transaction and that the Data stage has a zero-length status stage. The table illustrates the possible power of two data payloads less than or equal to the allowable maximum data payload size. The table does not include the overhead associated with bit stuffing.

| 1.1 | Protocol Overhead<br>(173 bytes) |                                 | (Based on 480Mb/s and 8 bit interpacket gap, 88 bit min bus<br>turnaround, 32 bit sync, 8 bit EOP: (9x4 SYNC bytes,<br>9 PID bytes, 6 EP/ADDR+CRC,6 CRC16, 8 Setup data,<br>9x(1+11) byte interpacket delay (EOP, etc.)) |                  |                    |                                     |  |

|-----|----------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|-------------------------------------|--|

| Р   | Data<br>ayload                   | Max Bandwidth<br>(bytes/second) | Microframe<br>Bandwidth<br>per Transfer                                                                                                                                                                                  | Max<br>Transfers | Bytes<br>Remaining | Bytes/<br>Microframe<br>Useful Data |  |

|     | 1                                | 344000                          | 2%                                                                                                                                                                                                                       | 43               | 18                 | 43                                  |  |

|     | 2                                | 672000                          | 2%                                                                                                                                                                                                                       | 42               | 150                | 84                                  |  |

|     | 4                                | 1344000                         | 2%                                                                                                                                                                                                                       | 42               | 66                 | 168                                 |  |

|     | 8                                | 2624000                         | 2%                                                                                                                                                                                                                       | 41               | 79                 | 328                                 |  |

|     | 16                               | 4992000                         | 3%                                                                                                                                                                                                                       | 39               | 129                | 624                                 |  |

|     | 32                               | 9216000                         | 3%                                                                                                                                                                                                                       | 36               | 120                | 1152                                |  |

|     | 64                               | 15872000                        | 3%                                                                                                                                                                                                                       | 31               | 153                | 1984                                |  |

|     |                                  | 6000000                         |                                                                                                                                                                                                                          |                  |                    | 7500                                |  |

| Table 5-3. High-speed Co | ntrol Transfer Limits |

|--------------------------|-----------------------|

|--------------------------|-----------------------|

### 5.5.5 Control Transfer Data Sequences

Control transfers require that a Setup bus transaction be sent from the host to a device to describe the type of control access that the device should perform. The Setup transaction is followed by zero or more control Data transactions that carry the specific information for the requested access. Finally, a Status transaction completes the control transfer and allows the endpoint to return the status of the control transfer to the client software. After the Status transaction for a control transfer is completed, the host can advance to the next control transfer for the endpoint. As described in Section 5.5.4, each control transaction and the next control transfer will be moved over the bus at some Host Controller implementation-defined time.

The endpoint can be busy for a device-specific time during the Data and Status transactions of the control transfer. During these times when the endpoint indicates it is busy (refer to Chapter 8 and Chapter 9 for details), the host will retry the transaction at a later time.

If a Setup transaction is received by an endpoint before a previously initiated control transfer is completed, the device must abort the current transfer/operation and handle the new control Setup transaction. A Setup transaction should not normally be sent before the completion of a previous control transfer. However, if a transfer is aborted, for example, due to errors on the bus, the host can send the next Setup transaction prematurely from the endpoint's perspective.

After a halt condition is encountered or an error is detected by the host, a control endpoint is allowed to recover by accepting the next Setup PID; i.e., recovery actions via some other pipe are not required for control endpoints. For the Default Control Pipe, a device reset will ultimately be required to clear the halt or error condition if the next Setup PID is not accepted.

The USB provides robust error detection and recovery/retransmission for errors that occur during control transfers. Transmitters and receivers can remain synchronized with regard to where they are in a control transfer and recover with minimum effort. Retransmission of Data and Status packets can be detected by a receiver via data retry indicators in the packet. A transmitter can reliably determine that its corresponding receiver has successfully accepted a transmitted packet by information returned in a handshake to the packet. The protocol allows for distinguishing a retransmitted packet from its original packet except for a control Setup packet. Setup packets may be retransmitted due to a transmission error; however, Setup packets cannot indicate that a packet is an original or a retried transmission.

### 5.6 Isochronous Transfers

In non-USB environments, isochronous transfers have the general implication of constant-rate, errortolerant transfers. In the USB environment, requesting an isochronous transfer type provides the requester with the following:

- Guaranteed access to USB bandwidth with bounded latency

- Guaranteed constant data rate through the pipe as long as data is provided to the pipe

- In the case of a delivery failure due to error, no retrying of the attempt to deliver the data

While the USB isochronous transfer type is designed to support isochronous sources and destinations, it is not required that software using this transfer type actually be isochronous in order to use the transfer type. Section 5.12 presents more detail on special considerations for handling isochronous data on the USB.

### 5.6.1 Isochronous Transfer Data Format

The USB imposes no data content structure on communication flows for isochronous pipes.

### 5.6.2 Isochronous Transfer Direction

An isochronous pipe is a stream pipe and is, therefore, always uni-directional. An endpoint description identifies whether a given isochronous pipe's communication flow is into or out of the host. If a device requires bi-directional isochronous communication flow, two isochronous pipes must be used, one in each direction.

### 5.6.3 Isochronous Transfer Packet Size Constraints

An endpoint in a given configuration for an isochronous pipe specifies the maximum size data payload that it can transmit or receive. The USB System Software uses this information during configuration to ensure that there is sufficient bus time to accommodate this maximum data payload in each (micro)frame. If there is sufficient bus time for the maximum data payload, the configuration is established; if not, the configuration is not established.

The USB limits the maximum data payload size to 1,023 bytes for each full-speed isochronous endpoint. High-speed endpoints are allowed up to 1024-byte data payloads. A high speed, high bandwidth endpoint specifies whether it requires two or three transactions per microframe. Table 5-4 lists information about different-sized full-speed isochronous transactions and the maximum number of transactions possible in a frame. The table is shaded to indicate that a full-speed isochronous endpoint (with a non-zero *wMaxpacket* size) must not be part of a default interface setting. The table does not include the overhead associated with bit stuffing.

|                |     |                                    | 2 CRC bytes, and a 1-byte interpacket delay) |                  |                    |                            |  |

|----------------|-----|------------------------------------|----------------------------------------------|------------------|--------------------|----------------------------|--|

| Data<br>Payloa | d I | Max<br>Bandwidth(bytes/<br>second) | Frame<br>Bandwidth<br>per Transfer           | Max<br>Transfers | Bytes<br>Remaining | Bytes/Frame<br>Useful Data |  |

|                | 1   | 150000                             | 1%                                           | 150              | 0                  | 150                        |  |

|                | 2   | 272000                             | 1%                                           | 136              | 4                  | 272                        |  |

|                | 4   | 460000                             | 1%                                           | 115              | 5                  | 460                        |  |

|                | 8   | 704000                             | 1%                                           | 88               | 4                  | 704                        |  |

| 1              | 6   | 960000                             | 2%                                           | 60               | 0                  | 960                        |  |

| з              | 2   | 1152000                            | 3%                                           | 36               | 24                 | 1152                       |  |

| 6              | 4   | 1280000                            | 5%                                           | 20               | 40                 | 1280                       |  |

| 12             | 8   | 1280000                            | 9%                                           | 10               | 130                | 1280                       |  |

| 25             | 6   | 1280000                            | 18%                                          | 5                | 175                | 1280                       |  |

| 51             | 2   | 1024000                            | 35%                                          | 2                | 458                | 1024                       |  |

| 102            | 3   | 1023000                            | 69%                                          | 1                | 468                | 1023                       |  |

|                |     | 1500000                            |                                              |                  |                    | 1500                       |  |

### Table 5-4. Full-speed Isochronous Transaction Limits

45

Table 5-5 lists information about different-sized high-speed isochronous transactions and the maximum number of transactions possible in a microframe. The table is shaded to indicate that a high-speed isochronous endpoint must not be part of a default interface setting. The table does not include the overhead associated with bit stuffing.

Any given transaction for an isochronous pipe need not be exactly the maximum size specified for the endpoint. The size of a data payload is determined by the transmitter (client software or function) and can vary as required from transaction to transaction. The USB ensures that whatever size is presented to the Host Controller is delivered on the bus. The actual size of a data payload is determined by the data transmitter and may be less than the prenegotiated maximum size. Bus errors can change the actual packet size seen by the receiver. However, these errors can be detected by either CRC on the data or by knowledge the receiver has about the expected size for any transaction.

| Prot | Protocol Overhead |                                    | (Based on 480M<br>turnaround, 32 I<br>bytes, 2 EP/ADI<br>byte interpacket | bit sync, 8 bit E<br>DR+addr+CRC | OP: (2x4 SYNC<br>5, 2 CRC16, an | bytes, 2 PID                        |

|------|-------------------|------------------------------------|---------------------------------------------------------------------------|----------------------------------|---------------------------------|-------------------------------------|

| 1000 | ata<br>⁄load      | Max<br>Bandwidth<br>(bytes/second) | Microframe<br>Bandwidth<br>per Transfer                                   | Max<br>Transfers                 | Bytes<br>Remaining              | Bytes/<br>MicroFrame<br>Useful Data |

|      | 1                 | 1536000                            | 1%                                                                        | 192                              | 12                              | 192                                 |

|      | 2                 | 2992000                            | 1%                                                                        | 187                              | 20                              | 374                                 |

|      | 4                 | 5696000                            | 1%                                                                        | 178                              | 24                              | 712                                 |

|      | 8                 | 10432000                           | 1%                                                                        | 163                              | 2                               | 1304                                |

|      | 16                | 17664000                           | 1%                                                                        | 138                              | 48                              | 2208                                |

|      | 32                | 27392000                           | 1%                                                                        | 107                              | 10                              | 3424                                |

|      | 64                | 37376000                           | 1%                                                                        | 73                               | 54                              | 4672                                |

|      | 128               | 46080000                           | 2%                                                                        | 45                               | 30                              | 5760                                |

|      | 256               | 51200000                           | 4%                                                                        | 25                               | 150                             | 6400                                |

|      | 512               | 53248000                           | 7%                                                                        | 13                               | 350                             | 6656                                |

|      | 1024              | 57344000                           | 14%                                                                       | 7                                | 66                              | 7168                                |

|      | 2048              | 49152000                           | 28%                                                                       | 3                                | 1242                            | 6144                                |

|      | 3072              | 49152000                           | 41%                                                                       | 2                                | 1280                            | 6144                                |

|      |                   | 60000000                           |                                                                           |                                  |                                 | 7500                                |

| Table 5-5. | High-speed | Isochronous | Transaction | Limits |

|------------|------------|-------------|-------------|--------|

|            |            |             |             |        |

All device default interface settings must not include any isochronous endpoints with non-zero data payload sizes (specified via *wMaxPacketSize* in the endpoint descriptor). Alternate interface settings may specify non-zero data payload sizes for isochronous endpoints. If the isochronous endpoints have a large data payload size, it is recommended that additional alternate configurations or interface settings be used to specify a range of data payload sizes. This increases the chance that the device can be used successfully in combination with other USB devices.

## 5.6.4 Isochronous Transfer Bus Access Constraints

Isochronous transfers can only be used by full-speed and high-speed devices.

The USB requires that no more than 90% of any frame be allocated for periodic (isochronous and interrupt) transfers for full-speed endpoints. High-speed endpoints can allocate at most 80% of a microframe for periodic transfers.

An isochronous endpoint must specify its required bus access period. Full-/high-speed endpoints must specify a desired period as  $(2^{bhatcrul-1})$  x F, where bInterval is in the range one to (and including) 16 and F is 125 µs for high-speed and 1ms for full-speed. This allows full-/high-speed isochronous transfers to have rates slower than one transaction per (micro)frame. However, an isochronous endpoint must be prepared to handle poll rates faster than the one specified. A host must not issue more than 1 transaction in a (micro)frame for an isochronous endpoint unless the endpoint is high-speed, high-bandwidth (see below). An isochronous IN endpoint must return a zero-length packet whenever data is requested at a faster interval than the specified interval and data is not available.

A high-speed endpoint can move up to 3072 bytes per microframe (or 192 Mb/s). A high-speed isochronous endpoint that requires more than 1024 bytes per period is called a high-bandwidth endpoint. A high-bandwidth endpoint uses multiple transactions per microframe. A high-bandwidth endpoint must specify a period of  $1 \times 125 \,\mu s$  (i.e., a *bInterval* value of 1). See Section 5.9 for more information about the details of multiple transactions per microframe for high-bandwidth high-speed endpoints.

Errors on the bus or delays in operating system scheduling of client software can result in no packet being transferred for a (micro)frame. An error indication should be returned as status to the client software in such a case. A device can also detect this situation by tracking SOF tokens and noticing a disturbance in the specified bus access period pattern.

The bus frequency and (micro)frame timing limit the maximum number of successful isochronous transactions within a (micro)frame for any USB system to less than 151 full-speed one-byte data payloads and less than 193 high-speed one-byte data payloads. A Host Controller, for various implementation reasons, may not be able to provide the theoretical maximum number of isochronous transactions per (micro)frame.

## 5.6.5 Isochronous Transfer Data Sequences

Isochronous transfers do not support data retransmission in response to errors on the bus. A receiver can determine that a transmission error occurred. The low-level USB protocol does not allow handshakes to be returned to the transmitter of an isochronous pipe. Normally, handshakes would be returned to tell the transmitter whether a packet was successfully received or not. For isochronous transfers, timeliness is more important than correctness/retransmission, and, given the low error rates expected on the bus, the protocol is optimized by assuming transfers normally succeed. Isochronous receivers can determine whether they missed data during a (micro)frame. Also, a receiver can determine how much data was lost. Section 5.12 describes these USB mechanisms in more detail.

An endpoint for isochronous transfers never halts because there is no handshake to report a halt condition. Errors are reported as status associated with the IRP for an isochronous transfer, but the isochronous pipe is not halted in an error case. If an error is detected, the host continues to process the data associated with the next (micro)frame of the transfer. Only limited error detection is possible because the protocol for isochronous transactions does not allow per-transaction handshakes.

## 5.7 Interrupt Transfers

The interrupt transfer type is designed to support those devices that need to send or receive data infrequently but with bounded service periods. Requesting a pipe with an interrupt transfer type provides the requester with the following:

- Guaranteed maximum service period for the pipe

- Retry of transfer attempts at the next period, in the case of occasional delivery failure due to error on the bus

### 5.7.1 Interrupt Transfer Data Format

The USB imposes no data content structure on communication flows for interrupt pipes.

## 5.7.2 Interrupt Transfer Direction

An interrupt pipe is a stream pipe and is therefore always uni-directional. An endpoint description identifies whether a given interrupt pipe's communication flow is into or out of the host.

## 5.7.3 Interrupt Transfer Packet Size Constraints

An endpoint for an interrupt pipe specifies the maximum size data payload that it will transmit or receive. The maximum allowable interrupt data payload size is 64 bytes or less for full-speed. High-speed endpoints are allowed maximum data payload sizes up to 1024 bytes. A high speed, high bandwidth endpoint specifies whether it requires two or three transactions per microframe. Low-speed devices are limited to eight bytes or less maximum data payload size. This maximum applies to the data payloads of the data packets; i.e., the size specified is for the data field of the packet as defined in Chapter 8, not including other protocol-required information. The USB does not require that data packets be exactly the maximum size; i.e., if a data packet is less than the maximum, it does not need to be padded to the maximum size.

All Host Controllers are required to support maximum data payload sizes from 0 to 64 bytes for full-speed interrupt endpoints, from 0 to 8 bytes for low-speed interrupt endpoints, and from 0 to 1024 bytes for high-speed interrupt endpoints. See Section 5.9 for more information about the details of multiple transactions per microframe for high bandwidth high-speed endpoints. No Host Controller is required to support larger maximum data payload sizes.

The USB System Software determines the maximum data payload size that will be used for an interrupt pipe during device configuration. This size remains constant for the lifetime of a device's configuration. The USB System Software uses the maximum data payload size determined during configuration to ensure that there is sufficient bus time to accommodate this maximum data payload in its assigned period. If there is sufficient bus time, the pipe is established; if not, the pipe is not established. However, the actual size of a data payload is still determined by the data transmitter and may be less than the maximum size.

An endpoint must always transmit data payloads with a data field less than or equal to the endpoint's *wMaxPacketSize* value. A device can move data via an interrupt pipe that is larger than *wMaxPacketSize*. A software client can accept this data via an IRP for the interrupt transfer that requires multiple bus transactions without requiring an IRP-complete notification per transaction. This can be achieved by specifying a buffer that can hold the desired data size. The size of the buffer is a multiple of *wMaxPacketSize* with some remainder. The endpoint must transfer each transaction except the last as *wMaxPacketSize* and the last transaction is the remainder. The multiple data transactions are moved over the bus at the period established for the pipe.

When an interrupt transfer involves more data than can fit in one data payload of the currently established maximum size, all data payloads are required to be maximum-sized except for the last data payload, which will contain the remaining data. An interrupt transfer is complete when the endpoint does one of the following:

48

- · Has transferred exactly the amount of data expected

- Transfers a packet with a payload size less than wMaxPacketSize or transfers a zero-length packet

When an interrupt transfer is complete, the Host Controller retires the current IRP and advances to the next IRP. If a data payload is received that is larger than expected, the interrupt IRP will be aborted/retired and the pipe will stall future IRPs until the condition is corrected and acknowledged.

All high-speed device default interface settings must not include any interrupt endpoints with a data payload size (specified via *wMaxPacketSize* in the endpoint descriptor) greater than 64 bytes. Alternate interface settings may specify larger data payload sizes for interrupt endpoints. If the interrupt endpoints have a large data payload size, it is recommended that additional configurations or alternate interface settings be used to specify a range of data payload sizes. This increases the chances that the device can be used successfully in combination with other USB devices.

### 5.7.4 Interrupt Transfer Bus Access Constraints

Interrupt transfers can be used by low-speed, full-speed, and high-speed devices. High-speed endpoints can be allocated at most 80% of a microframe for periodic transfers. The USB requires that no more than 90% of any frame be allocated for periodic (isochronous and interrupt) full-/low-speed transfers.

The bus frequency and (micro)frame timing limit the maximum number of successful interrupt transactions within a (micro)frame for any USB system to less than 108 full-speed one-byte data payloads, or less than 10 low-speed one-byte data payloads. A Host Controller, for various implementation reasons, may not be able to provide the above maximum number of interrupt transactions per (micro)frame.

Table 5-6 lists information about different low-speed interrupt transactions and the maximum number of transactions possible in a frame. Table 5-7 lists similar information for full-speed interrupt transactions. Table 5-8 lists similar information for high-speed interrupt transactions. The shaded portion of Table 5-8 indicates the data payload sizes of a high-speed interrupt endpoint that must not be part of a default interface setting. The tables do not include the overhead associated with bit stuffing.

| 122 | Protocol Overhead<br>(19 bytes) |                                 | (5 SYNC bytes, 5 PID bytes, 2 Endpoint + CRC bytes, 2 CRC bytes, and a 5-byte interpacket delay) |                  |                    |                            |  |

|-----|---------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------|------------------|--------------------|----------------------------|--|

| F   | Data<br>Payload                 | Max Bandwidth<br>(bytes/second) | Frame<br>Bandwidth<br>per Transfer                                                               | Max<br>Transfers | Bytes<br>Remaining | Bytes/Frame<br>Useful Data |  |

|     | 1                               | 9000                            | 11%                                                                                              | 9                | 7                  | 9                          |  |

|     | 2                               | 16000                           | 11%                                                                                              | 8                | 19                 | 16                         |  |

|     | 4                               | 32000                           | 12%                                                                                              | 8                | 3                  | 32                         |  |

|     | 8                               | 48000                           | 14%                                                                                              | 6                | 25                 | 48                         |  |

| Г   |                                 | 187500                          |                                                                                                  |                  |                    | 187                        |  |

Table 5-6. Low-speed Interrupt Transaction Limits

| Protocol Overhead (13 bytes) |                                    | (3 SYNC bytes, 3 PID bytes, 2 Endpoint + CRC bytes, 2 CRC bytes, and a 3-byte interpacket delay) |                  |                    |                            |  |

|------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|------------------|--------------------|----------------------------|--|

| Data<br>Payload              | Max<br>Bandwidth<br>(bytes/second) | Frame<br>Bandwidth<br>per Transfer                                                               | Max<br>Transfers | Bytes<br>Remaining | Bytes/Frame<br>Useful Data |  |

| 1                            | 107000                             | 1%                                                                                               | 107              | 2                  | 107                        |  |

| 2                            | 200000                             | 1%                                                                                               | 100              | 0                  | 200                        |  |

| 4                            | 352000                             | 1%                                                                                               | 88               | 4                  | 352                        |  |

| 8                            | 568000                             | 1%                                                                                               | 71               | 9                  | 568                        |  |

| 16                           | 816000                             | 2%                                                                                               | 51               | 21                 | 816                        |  |

| 32                           | 1056000                            | 3%                                                                                               | 33               | 15                 | 1056                       |  |

| 64                           | 1216000                            | 5%                                                                                               | 19               | 37                 | 1216                       |  |

|                              | 1500000                            |                                                                                                  |                  |                    | 1500                       |  |

| Table 5-7. | Full-speed | Interrupt | Transaction | Limits |

|------------|------------|-----------|-------------|--------|

| Table 5-7. | run-speeu  | muerrupt  | Transaction | Limits |

| Protocol Overhead |   | btocol Overhead (Based on 480Mb/s and 8 bit i<br>bus turnaround, 32 bit sync, 8<br>3 PID bytes, 2 EP/ADDR+CR0<br>3x(1+11) byte interpacket dela |                                         |                  |                    | SYNC bytes,                         |

|-------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|--------------------|-------------------------------------|

| Data<br>Payload   | ļ | Max<br>Bandwidth<br>(bytes/second)                                                                                                              | Microframe<br>Bandwidth<br>per Transfer | Max<br>Transfers | Bytes<br>Remaining | Bytes/<br>Microframe<br>Useful Data |

| 3                 | 1 | 1064000                                                                                                                                         | 1%                                      | 133              | 52                 | 133                                 |

| 1                 | 2 | 2096000                                                                                                                                         | 1%                                      | 131              | 33                 | 262                                 |

|                   | 4 | 4064000                                                                                                                                         | 1%                                      | 127              | 7                  | 508                                 |

|                   | 8 | 7616000                                                                                                                                         | 1%                                      | 119              | 3                  | 952                                 |

| 1                 | 6 | 13440000                                                                                                                                        | 1%                                      | 105              | 45                 | 1680                                |

| 3                 | 2 | 22016000                                                                                                                                        | 1%                                      | 86               | 18                 | 2752                                |

| 6                 | 4 | 32256000                                                                                                                                        | 2%                                      | 63               | 3                  | 4032                                |

| 12                | 8 | 40960000                                                                                                                                        | 2%                                      | 40               | 180                | 5120                                |

| 25                | 6 | 49152000                                                                                                                                        | 4%                                      | 24               | 36                 | 6144                                |

| 51                | 2 | 53248000                                                                                                                                        | 8%                                      | 13               | 129                | 6656                                |

| 102               | 4 | 49152000                                                                                                                                        | 14%                                     | 6                | 1026               | 6144                                |

| 204               | 8 | 49152000                                                                                                                                        | 28%                                     | 3                | 1191               | 6144                                |

| 307               | 2 | 49152000                                                                                                                                        | 42%                                     | 2                | 1246               | 6144                                |

|                   |   | 6000000                                                                                                                                         |                                         |                  |                    | 7500                                |

| Table 5-8. High-speed Interrupt Transaction Limi | Table 5-8. | High-speed | Interrupt | Transaction | Limits |

|--------------------------------------------------|------------|------------|-----------|-------------|--------|

|--------------------------------------------------|------------|------------|-----------|-------------|--------|

An endpoint for an interrupt pipe specifies its desired bus access period. A full-speed endpoint can specify a desired period from 1 ms to 255 ms. Low-speed endpoints are limited to specifying only 10 ms to 255 ms. High-speed endpoints can specify a desired period  $(2^{bhacval-1})x125 \mu s$ , where *bInterval* is in the range 1 to (including) 16. The USB System Software will use this information during configuration to determine a period that can be sustained. The period provided by the system may be shorter than that desired by the device up to the shortest period defined by the USB (125  $\mu$ s microframe or 1 ms frame). The client software and device can depend only on the fact that the host will ensure that the time duration between two transaction attempts with the endpoint will be no longer than the desired period. Note that errors on the bus can prevent an interrupt transaction from being successfully delivered over the bus and consequently exceed the desired period. Also, the endpoint is only polled when the software client has an IRP for an interrupt transfer pending. If the bus time for performing an interrupt transfer arrives and there is no IRP pending, the endpoint will not be given an opportunity to transfer data at that time. Once an IRP is available, its data will be transferred at the next allocated period.

A high-speed endpoint can move up to 3072 bytes per microframe (or 192 Mb/s). A high-speed interrupt endpoint that requires more than 1024 bytes per period is called a high-bandwidth endpoint. A high-bandwidth endpoint uses multiple transactions per microframe. A high-bandwidth endpoint must specify a period of  $1 \times 125 \,\mu s$  (i.e., a *bInterval* value of 1). See Section 5.9 for more information about the details of multiple transactions per microframe for high-bandwidth high-speed endpoints.

Interrupt transfers are moved over the USB by accessing an interrupt endpoint every specified period. For input interrupt endpoints, the host has no way to determine whether an endpoint will source an interrupt without accessing the endpoint and requesting an interrupt transfer. If the endpoint has no interrupt data to transmit when accessed by the host, it responds with NAK. An endpoint should only provide interrupt data when it has an interrupt pending to avoid having a software client erroneously notified of IRP complete. A zero-length data payload is a valid transfer and may be useful for some implementations.

### 5.7.5 Interrupt Transfer Data Sequences

Interrupt transactions may use either alternating data toggle bits, such that the bits are toggled only upon successful transfer completion or a continuously toggling of data toggle bits. The host in any case must assume that the device is obeying full handshake/retry rules as defined in Chapter 8. A device may choose to always toggle DATA0/DATA1 PIDs so that it can ignore handshakes from the host. However, in this case, the client software can miss some data packets when an error occurs, because the Host Controller interprets the next packet as a retry of a missed packet.

If a halt condition is detected on an interrupt pipe due to transmission errors or a STALL handshake being returned from the endpoint, all pending IRPs are retired. Removal of the halt condition is achieved via software intervention through a separate control pipe. This recovery will reset the data toggle bit to DATA0 for the endpoint on both the host and the device. Interrupt transactions are retried due to errors detected on the bus that affect a given transfer.

### 5.8 Bulk Transfers

The bulk transfer type is designed to support devices that need to communicate relatively large amounts of data at highly variable times where the transfer can use any available bandwidth. Requesting a pipe with a bulk transfer type provides the requester with the following:

- Access to the USB on a bandwidth-available basis

- · Retry of transfers, in the case of occasional delivery failure due to errors on the bus

- · Guaranteed delivery of data but no guarantee of bandwidth or latency

Bulk transfers occur only on a bandwidth-available basis. For a USB with large amounts of free bandwidth, bulk transfers may happen relatively quickly; for a USB with little bandwidth available, bulk transfers may trickle out over a relatively long period of time.

### 5.8.1 Bulk Transfer Data Format

The USB imposes no data content structure on communication flows for bulk pipes.

## 5.8.2 Bulk Transfer Direction

A bulk pipe is a stream pipe and, therefore, always has communication flowing either into or out of the host for a given pipe. If a device requires bi-directional bulk communication flow, two bulk pipes must be used, one in each direction.

## 5.8.3 Bulk Transfer Packet Size Constraints

An endpoint for bulk transfers specifies the maximum data payload size that the endpoint can accept from or transmit to the bus. The USB defines the allowable maximum bulk data payload sizes to be only 8, 16, 32, or 64 bytes for full-speed endpoints and 512 bytes for high-speed endpoints. A low-speed device must not have bulk endpoints. This maximum applies to the data payloads of the data packets; i.e., the size specified is for the data field of the packet as defined in Chapter 8, not including other protocol-required information.

A bulk endpoint is designed to support a maximum data payload size. A bulk endpoint reports in its configuration information the value for its maximum data payload size. The USB does not require that data payloads transmitted be exactly the maximum size; i.e., if a data payload is less than the maximum, it does not need to be padded to the maximum size.

All Host Controllers are required to have support for 8-, 16-, 32-, and 64-byte maximum packet sizes for full-speed bulk endpoints and 512 bytes for high-speed bulk endpoints. No Host Controller is required to support larger or smaller maximum packet sizes.

During configuration, the USB System Software reads the endpoint's maximum data payload size and ensures that no data payload will be sent to the endpoint that is larger than the supported size.

An endpoint must always transmit data payloads with a data field less than or equal to the endpoint's reported *wMaxPacketSize* value. When a bulk IRP involves more data than can fit in one maximum-sized data payload, all data payloads are required to be maximum size except for the last data payload, which will contain the remaining data. A bulk transfer is complete when the endpoint does one of the following:

- · Has transferred exactly the amount of data expected

- Transfers a packet with a payload size less than wMaxPacketSize or transfers a zero-length packet

When a bulk transfer is complete, the Host Controller retires the current IRP and advances to the next IRP. If a data payload is received that is larger than expected, all pending bulk IRPs for that endpoint will be aborted/retired.

## 5.8.4 Bulk Transfer Bus Access Constraints

Only full-speed and high-speed devices can use bulk transfers.

An endpoint has no way to indicate a desired bus access frequency for a bulk pipe. The USB balances the bus access requirements of all bulk pipes and the specific IRPs that are pending to provide "good effort" delivery of data between client software and functions. Moving control transfers over the bus has priority over moving bulk transfers.

There is no time guaranteed to be available for bulk transfers as there is for control transfers. Bulk transfers are moved over the bus only on a bandwidth-available basis. If there is bus time that is not being used for other purposes, bulk transfers will be moved over the bus. If there are bulk transfers pending for multiple endpoints, bulk transfers for the different endpoints are selected according to a fair access policy that is Host Controller implementation-dependent.

All bulk transfers pending in a system contend for the same available bus time. Because of this, the USB System Software at its discretion can vary the bus time made available for bulk transfers to a particular endpoint. An endpoint and its client software cannot assume a specific rate of service for bulk transfers. Bus time made available to a software client and its endpoint can be changed as other devices are inserted into and removed from the system or also as bulk transfers are requested for other device endpoints. Client software cannot assume ordering between bulk and control transfers; i.e., in some situations, bulk transfers can be delivered ahead of control transfers.

High-speed bulk OUT endpoints must support the PING flow control protocol. The details of this protocol are described in Section 8.5.1.

The bus frequency and (micro)frame timing limit the maximum number of successful bulk transactions within a (micro)frame for any USB system to less than 72 full-speed eight-byte data payloads or less than 14 high-speed 512-byte data payloads. Table 5-9 lists information about different-sized full-speed bulk transactions and the maximum number of transactions possible in a frame. The table does not include the overhead associated with bit stuffing. Table 5-10 lists similar information for high-speed bulk transactions.

|   | Protocol Overhead (13 bytes) |                                 | (3 SYNC bytes, 3 PID bytes, 2 Endpoint + CRC bytes, 2 CRC bytes, and a 3-byte interpacket delay) |                  |                    |                            |  |

|---|------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------|------------------|--------------------|----------------------------|--|

|   | Data<br>Payload              | Max Bandwidth<br>(bytes/second) | Frame<br>Bandwidth<br>per Transfer                                                               | Max<br>Transfers | Bytes<br>Remaining | Bytes/Frame<br>Useful Data |  |

| Γ | 1                            | 107000                          | 1%                                                                                               | 107              | 2                  | 107                        |  |

|   | 2                            | 200000                          | 1%                                                                                               | 100              | 0                  | 200                        |  |

|   | 4                            | 352000                          | 1%                                                                                               | 88               | 4                  | 352                        |  |

|   | 8                            | 568000                          | 1%                                                                                               | 71               | 9                  | 568                        |  |

|   | 16                           | 816000                          | 2%                                                                                               | 51               | 21                 | 816                        |  |

| Γ | 32                           | 1056000                         | 3%                                                                                               | 33               | 15                 | 1056                       |  |

|   | 64                           | 1216000                         | 5%                                                                                               | 19               | 37                 | 1216                       |  |

| Γ |                              | 1500000                         |                                                                                                  |                  |                    | 1500                       |  |

| Table 5-9. Full-speed Bu | lk Transaction Limits |

|--------------------------|-----------------------|

|--------------------------|-----------------------|

|    | Protocol Overhead (55 bytes) |                                 | (3x4 SYNC bytes, 3 PID bytes, 2 EP/ADDR+CRC bytes, 2 CRC16, and a 3x(1+11) byte interpacket delay (EOP, etc.)) |                  |                    |                                     |

|----|------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|------------------|--------------------|-------------------------------------|

|    | Data<br>Payload              | Max Bandwidth<br>(bytes/second) | Microframe<br>Bandwidth<br>per Transfer                                                                        | Max<br>Transfers | Bytes<br>Remaining | Bytes/<br>Microframe<br>Useful Data |

|    | 1                            | 1064000                         | 1%                                                                                                             | 133              | 52                 | 133                                 |

|    | 2                            | 2096000                         | 1%                                                                                                             | 131              | 33                 | 262                                 |

|    | 4                            | 4064000                         | 1%                                                                                                             | 127              | 7                  | 508                                 |

|    | 8                            | 7616000                         | 1%                                                                                                             | 119              | 3                  | 952                                 |

|    | 16                           | 13440000                        | 1%                                                                                                             | 105              | 45                 | 1680                                |

|    | 32                           | 22016000                        | 1%                                                                                                             | 86               | 18                 | 2752                                |

|    | 64                           | 32256000                        | 2%                                                                                                             | 63               | 3                  | 4032                                |

|    | 128                          | 40960000                        | 2%                                                                                                             | 40               | 180                | 5120                                |

|    | 256                          | 49152000                        | 4%                                                                                                             | 24               | 36                 | 6144                                |

|    | 512                          | 53248000                        | 8%                                                                                                             | 13               | 129                | 6656                                |

| ax |                              | 6000000                         |                                                                                                                |                  |                    | 7500                                |

Host Controllers are free to determine how the individual bus transactions for specific bulk transfers are moved over the bus within and across (micro)frames. An endpoint could see all bus transactions for a bulk transfer within the same (micro)frame or spread across several (micro)frames. A Host Controller, for various implementation reasons, may not be able to provide the above maximum number of transactions per (micro)frame.

### 5.8.5 Bulk Transfer Data Sequences

Bulk transactions use data toggle bits that are toggled only upon successful transaction completion to preserve synchronization between transmitter and receiver when transactions are retried due to errors. Bulk transactions are initialized to DATA0 when the endpoint is configured by an appropriate control transfer. The host will also start the first bulk transaction with DATA0. If a halt condition is detected on a bulk pipe due to transmission errors or a STALL handshake being returned from the endpoint, all pending IRPs are retired. Removal of the halt condition is achieved via software intervention through a separate control pipe. This recovery will reset the data toggle bit to DATA0 for the endpoint on both the host and the device.

Bulk transactions are retried due to errors detected on the bus that affect a given transaction.

## 5.9 High-Speed, High Bandwidth Endpoints

USB supports individual high-speed interrupt or isochronous endpoints that require data rates up to 192 Mb/s (i.e., 3072 data bytes per microframe). One, two, or three high-speed transactions are allowed in a single microframe to support high-bandwidth endpoints.

A high-speed interrupt or isochronous endpoint indicates that it requires more than 1024 bytes per microframe when bits 12..11 of the *wMaxPacketSize* field of the endpoint descriptor (see Table 5-11) are non-zero. The lower 11 bits of *wMaxPacketSize* indicate the size of the data payload for each individual transaction while bits 12..11 indicate the maximum number of required transactions possible. See Section 9.6.6 for restrictions on the allowed combinations of values for bits 12..11 and bits 10..0.

Table 5-11. wMaxPacketSize Field of Endpoint Descriptor

| Bits  | 1513                                | 1211                                  | 100                                      |  |

|-------|-------------------------------------|---------------------------------------|------------------------------------------|--|

| Field | Reserved,<br>must be<br>set to zero | Number of transactions per microframe | Maximum size of data<br>payload in bytes |  |

Note: This representation means that endpoints requesting two transactions per microframe will specify a total data payload size in the microframe that is a multiple of two bytes. Also endpoints requesting three transactions per microframe will specify a total data payload size that is a multiple of three bytes. In any case, any number of bytes can actually be transferred in a microframe.

The host controller must issue an appropriate number of high-speed transactions per microframe. Errors in the host or on the bus can result in the host controller issuing fewer transactions than requested for the endpoint. The first transaction(s) must have a data payload(s) as specified by the lower 11 bits of *wMaxPacketSize* if enough data is available, while the last transaction has any remaining data less than or equal to the maximum size specified. The host controller may issue transactions for the same endpoint one immediately after the other (as required for the actual data provided) or may issue transactions for other endpoints in between the transactions for a high bandwidth endpoint.

### 5.9.1 High Bandwidth Interrupt Endpoints

For interrupt transactions, if the endpoint NAKs a transaction during a microframe, the host controller must not issue further transactions for that endpoint until the next period.

If the endpoint times-out a transaction, the host controller must retry the transaction. The endpoint specifies the maximum number of desired transactions per microframe. If the maximum number of transactions per microframe has not been reached, the host controller may immediately retry the transaction during the current microframe. Host controllers are recommended to do an immediate retry since this minimizes impact on devices that are bandwidth sensitive. If the maximum number of transactions per microframe has been reached, the host controller must retry the transaction at the next period for the endpoint.

A host controller is allowed to issue less than the maximum number of transactions to an endpoint per microframe only if more than a single memory buffer is required for the transactions within the microframe.

Normal DATA0/DATA1 data toggle sequencing is used for each interrupt transaction during a microframe.

### 5.9.2 High Bandwidth Isochronous Endpoints

For isochronous transactions, if an IN endpoint provides less than a maximum data payload as specified by its endpoint descriptor, the host must not issue further transactions for that endpoint for that microframe.

For an isochronous OUT endpoint, the host controller must issue the number of transactions as required for the actual data provided, not exceeding the maximum number specified by the endpoint descriptor. The transactions issued must adhere to the maximum payload sizes as specified in the endpoint descriptor.

No retries are ever done for isochronous endpoints.

High bandwidth isochronous endpoints (IN and OUT) must support data PID sequencing. Data PID sequencing provides the required support for the data receiver to detect one or more lost/damaged packets per microframe.

Data PID sequencing for a high-speed, high bandwidth isochronous IN endpoint uses a repeating sequence of DATA2, DATA1, DATA0 PIDs for the data packet of each transaction in a microframe. If there is only a single transaction in the microframe, only a DATA0 data packet PID is used. If there are two transactions per microframe, DATA1 is used for the first transaction data packet and DATA0 is used for the second transaction data packet. If there are three transactions per microframe, DATA2 is used for the eare three transactions per microframe, DATA2 is used for the first transaction data packet, DATA1 is used for the second, and DATA0 is used for the third. In all cases, the data PID sequence starts over again the next microframe. Figure 5-11 shows the order of data packet PIDs that are used in subsequent transactions within a microframe for high-bandwidth isochronous IN endpoints.

| 1 transaction, <1024 bytes:         | DATA0 |       |       |

|-------------------------------------|-------|-------|-------|

| 2 transactions, 513-1024 bytes ea.: | DATA1 | DATA0 |       |

| 3 transactions, 683-1024 bytes ea.: | DATA2 | DATA1 | DATA0 |

Figure 5-11. Data Phase PID Sequence for Isochronous IN High Bandwidth Endpoints

An endpoint must respond to an IN token for the first transaction with a DATA2 when it requires three transactions of data to be moved. It must respond with a DATA1 for the first transaction when it requires two transactions and with a DATA0 when it requires only a single transaction. After the first transaction, the endpoint follows the data PID sequence as described above.

The host knows the maximum number of allowed transactions per microframe for the IN endpoint. The host expects the response to the first transaction to encode (via the data packet PID) how many transactions are required by the endpoint for this microframe. If the host doesn't receive an error-free, appropriate response to any transaction, the host must not issue any further transactions to the endpoint for that microframe. When the host receives a DATA0 data packet from the endpoint, it must not issue any further transactions to the endpoint for that microframe.

Data PID sequencing for a high-speed, high bandwidth isochronous OUT endpoint uses a different sequence than that used for an IN endpoint. The host must issue a DATA0 data packet when there is a single transaction. The host must issue an MDATA for the first transaction and a DATA1 for the second transaction when there are two transactions per microframe. The host must issue two MDATA transactions and a DATA2 for the third transaction when there are three transactions per microframe. These sequences allow the endpoint to detect if there was a lost/damaged transaction during a microframe. Figure 5-12 shows the order of data packet PIDs that are used in subsequent transactions within a microframe for highbandwidth isochronous OUT.

### Figure 5-12. Data Phase PID Sequence for Isochronous OUT High Bandwidth Endpoints

If the wrong OUT transactions are detected by the endpoint, all of the data transferred during the microframe must be treated as if it had encountered an error. Note that for the three transactions per microframe case with a missing MDATA transaction, USB provides no way for the endpoint to determine which of the two MDATA transactions was lost. There may be application specific methods to more precisely determine which data was lost, but USB provides no method to do so at the bus level.

### 5.10 Split Transactions

Host controllers and hubs support one additional transaction type called split transactions. This transaction type allows full- and low-speed devices to be attached to hubs operating at high-speed. These transactions involve only host controllers and hubs and are not visible to devices. High-speed split transactions for interrupt and isochronous transfers must be allocated by the host from the 80% periodic portion of a microframe. More information on split transactions can be found in Chapter 8 and Chapter 11.

### 5.11 Bus Access for Transfers

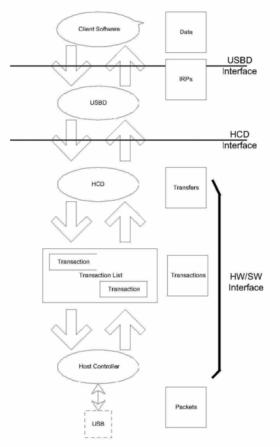

Accomplishing any data transfer between the host and a USB device requires some use of the USB bandwidth. Supporting a wide variety of isochronous and asynchronous devices requires that each device's transfer requirements are accommodated. The process of assigning bus bandwidth to devices is called transfer management. There are several entities on the host that coordinate the information flowing over the USB: client software, the USB Driver (USBD), and the Host Controller Driver (HCD). Implementers of these entities need to know the key concepts related to bus access:

- Transfer Management: The entities and the objects that support communication flow over the USB

- Transaction Tracking: The USB mechanisms that are used to track transactions as they move through the USB system

- · Bus Time: The time it takes to move a packet of information over the bus

- Device/Software Buffer Size: The space required to support a bus transaction

- Bus Bandwidth Reclamation: Conditions where bandwidth that was allocated to other transfers but was

not used and can now be possibly reused by control and bulk transfers

The previous sections focused on how client software relates to a function and what the logical flows are over a pipe between the two entities. This section focuses on the different parts of the host and how they must interact to support moving data over the USB. This information may also be of interest to device implementers so they understand aspects of what the host is doing when a client requests a transfer and how that transfer is presented to the device.

58

### 5.11.1 Transfer Management

Transfer management involves several entities that operate on different objects in order to move transactions over the bus:

- Client Software: Consumes/generates function-specific data to/from a function endpoint via calls and callbacks requesting IRPs with the USBD interface.

- USB Driver (USBD): Converts data in client IRPs to/from device endpoint via calls/callbacks with the

appropriate HCD. A single client IRP may involve one or more transfers.

- Host Controller Driver (HCD): Converts IRPs to/from transactions (as required by a Host Controller implementation) and organizes them for manipulation by the Host Controller. Interactions between the HCD and its hardware is implementation-dependent and is outside the scope of the USB Specification.

- Host Controller: Takes transactions and generates bus activity via packets to move function-specific data across the bus for each transaction.

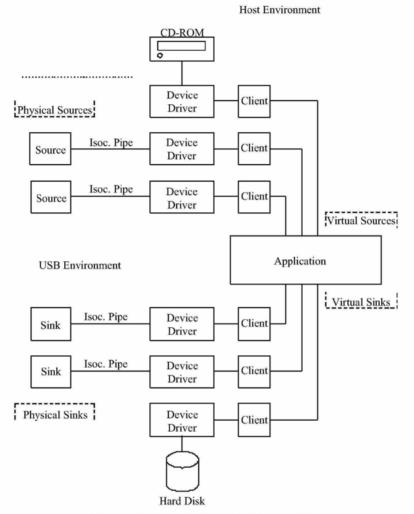

Figure 5-13 shows how the entities are organized as information flows between client software and the USB. The objects of primary interest to each entity are shown at the interfaces between entities.

Figure 5-13. USB Information Conversion From Client Software to Bus

## 5.11.1.1 Client Software

Client software determines what transfers need to be made with a function. It uses appropriate operating system-specific interfaces to request IRPs. Client software is aware only of the set of pipes (i.e., the interface) it needs to manipulate its function. The client is aware of and adheres to all bus access and bandwidth constraints as described previously for each transfer type. The requests made by the client software are presented via the USBD interface.

Some clients may manipulate USB functions via other device class interfaces defined by the operating system and may themselves not make direct USBD calls. However, there is always some lowest level client that makes USBD calls to pass IRPs to the USBD. All IRPs presented are required to adhere to the prenegotiated bandwidth constraints set when the pipe was established. If a function is moved from a non-USB environment to the USB, the driver that would have directly manipulated the function hardware via memory or I/O accesses is the lowest client software in the USB environment that now interacts with the USBD to manipulate the driver's USB function.

After client software has requested a transfer of its function and the request has been serviced, the client software receives notification of the completion status of the IRP. If the transfer involved function-to-host data transfer, the client software can access the data in the data buffer associated with the completed IRP.

The USBD interface is defined in Chapter 10.

## 5.11.1.2 USB Driver

The Universal Serial Bus Driver (USBD) is involved in mediating bus access at two general times:

- While a device is attached to the bus during configuration

- During normal transfers

When a device is attached and configured, the USBD is involved to ensure that the desired device configuration can be accommodated on the bus. The USBD receives configuration requests from the configuring software that describe the desired device configuration: endpoint(s), transfer type(s), transfer period(s), data size(s), etc. The USBD either accepts or rejects a configuration request based on bandwidth availability and the ability to accommodate that request type on the bus. If it accepts the request, the USBD creates a pipe for the requester of the desired type and with appropriate constraints as defined for the transfer type. Bandwidth allocation for periodic endpoints does not have to be made when the device is configured and, once made, a bandwidth allocation can be released without changing the device configuration.

The configuration aspects of the USBD are typically operating system-specific and heavily leverage the configuration features of the operating system to avoid defining additional (redundant) interfaces.

Once a device is configured, the software client can request IRPs to move data between it and its function endpoints.

## 5.11.1.3 Host Controller Driver

The Host Controller Driver (HCD) is responsible for tracking the IRPs in progress and ensuring that USB bandwidth and (micro)frame time maximums are never exceeded. When IRPs are made for a pipe, the HCD adds them to the transaction list. When an IRP is complete, the HCD notifies the requesting software client of the completion status for the IRP. If the IRP involved data transfer from the function to the software client, the data was placed in the client-indicated data buffer.

IRPs are defined in an operating system-dependent manner.

## 5.11.1.4 Transaction List

The transaction list is a Host Controller implementation-dependent description of the current outstanding set of bus transactions that need to be run on the bus. Only the HCD and its Host Controller have access to the specific representation. Each description contains transaction descriptions in which parameters, such as data size in bytes, the device address and endpoint number, and the memory area to which data is to be sent or received, are identified.

A transaction list and the interface between the HCD and its Host Controller is typically represented in an implementation-dependent fashion and is not defined explicitly as part of the USB Specification.

### 5.11.1.5 Host Controller

The Host Controller has access to the transaction list and translates it into bus activity. In addition, the Host Controller provides a reporting mechanism whereby the status of a transaction (done, pending, halted, etc.) can be obtained. The Host Controller converts transactions into appropriate implementation-dependent activities that result in USB packets moving over the bus topology rooted in the root hub.

The Host Controller ensures that the bus access rules defined by the protocol are obeyed, such as inter-packet timings, timeouts, babble, etc. The HCD interface provides a way for the Host Controller to participate in deciding whether a new pipe is allowed access to the bus. This is done because Host Controller implementations can have restrictions/constraints on the minimum inter-transaction times they may support for combinations of bus transactions.

The interface between the transaction list and the Host Controller is hidden within an HCD and Host Controller implementation.

## 5.11.2 Transaction Tracking

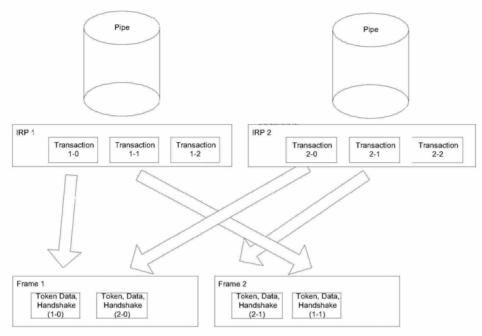

A USB function sees data flowing across the bus in packets as described in Chapter 8. The Host Controller uses some implementation-dependent representation to track what packets to transfer to/from what endpoints at what time or in what order. Most client software does not want to deal with packetized communication flows because this involves a degree of complexity and interconnect dependency that limits the implementation. The USB System Software (USBD and HCD) provides support for matching data movement requirements of a client to packets on the bus. The Host Controller hardware and software uses IRPs to track information about one or more transactions that combine to deliver a transfer of information between the client software and the function. Figure 5-14 summarizes how transactions are organized into IRPs for the four transfer types. Detailed protocol information for each transfer type can be found in Chapter 8. More information about client software views of IRPs can be found in Chapter 10 and in the operating system specific-information for a particular operating system.

| Data Flow Types                                                             | All transfers are                                                                           |  |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| IRP Transaction Transaction Transaction                                     | composed of one or more<br>transactions. An IRP<br>corresponds to one or<br>more transfers. |  |

| Control Transfer                                                            | A control transfer is an OUT<br>Setup transaction followed<br>by multiple IN or OUT Data    |  |

| IRP<br>Setup<br>Transaction Data<br>Transaction Status<br>Control Transfers | transactions followed by one<br>"opposite of data direction"<br>Status transaction.         |  |

| Interrupt Transfer                                                          | An interrupt transfer is one<br>or more IN / OUT Data                                       |  |

| IRP Transaction Transaction                                                 | transactions.                                                                               |  |

| Isochronous Transfer                                                        | An isochronous transfer                                                                     |  |

| IRP Transaction Transaction Transaction                                     | is one or more IN / OUT<br>Data transactions.                                               |  |

| Bulk Transfer                                                               | A bulk transfer is one                                                                      |  |

| IRP Transaction Transaction Transaction                                     | or more IN / OUT Data<br>transactions.                                                      |  |

Figure 5-14. Transfers for Communication Flows

Even though IRPs track the bus transactions that need to occur to move a specific data flow over the USB, Host Controllers are free to choose how the particular bus transactions are moved over the bus subject to the USB-defined constraints (e.g., exactly one transaction per (micro)frame for isochronous transfers). In any case, an endpoint will see transactions in the order they appear within an IRP unless errors occur. For example, Figure 5-15 shows two IRPs, one each for two pipes where each IRP contains three transactions. For any transfer type, a Host Controller is free to move the first transaction of the first IRP followed by the first transaction of the second IRP somewhere in (micro)Frame 1, while moving the second transaction of each IRP in opposite order somewhere in (micro)Frame 2. If these are isochronous transfer types, that is the only degree of freedom a Host Controller has. If these are control or bulk transfers, a Host Controller could further move more or less transactions from either IRP within either (micro)frame. Functions cannot depend on seeing transactions within an IRP back-to-back within a (micro)frame nor should they depend on not seeing transactions back-to-back within a (micro)frame.

62

Figure 5-15. Arrangement of IRPs to Transactions/(Micro)frames

## 5.11.3 Calculating Bus Transaction Times

When the USB System Software allows a new pipe to be created for the bus, it must calculate how much bus time is required for a given transaction. That bus time is based on the maximum packet size information reported for an endpoint, the protocol overhead for the specific transaction type request, the overhead due to signaling imposed bit stuffing, inter-packet timings required by the protocol, inter-transaction timings, etc. These calculations are required to ensure that the time available in a (micro)frame is not exceeded. The equations used to determine transaction bus time are:

## KEY:

| Data_bc      | The byte count of data payload                                                                                                                                                                                   |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host_Delay   | The time required for the host or transaction<br>translator to prepare for or recover from the<br>transmission; Host Controller implementation-specific                                                          |