| Test Description                                        | Test Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Performance Requirement                                                                                                                                                                                                       |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flammability                                            | UL 94 V-0<br>This procedure is to ensure<br>thermoplastic resin compliance to<br>UL flammability standards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The manufacturer will require its<br>thermoplastic resin vendor to<br>supply a detailed C of C with each<br>resin shipment. The C of C shall<br>clearly show the resin's UL listing<br>number, lot number, date code,<br>etc. |

| Flammability                                            | UL 94 V-0<br>This procedure is to ensure<br>thermoplastic resin compliance to<br>UL flammability standards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | The manufacturer will require its<br>thermoplastic resin vendor to<br>supply a detailed C of C with each<br>resin shipment. The C of C shall<br>clearly show the resin's UL listing<br>number, lot number, date code,<br>etc. |

| Cable Impedance<br>(Only required for high-/full-speed) | <ul> <li>The object of this test is to insure the signal conductors have the proper impedance.</li> <li>1. Connect the Time Domain Reflectometer (TDR) outputs to the impedance/delay/skew test fixture (Note 1). Use separate 50 Ω cables for the plus (or true) and minus (or complement) outputs. Set the TDR head to differential TDR mode.</li> <li>2. Connect the Series "A" plug of the cable to be tested to the text fixture, leaving the other end open-circuited.</li> <li>3. Define a waveform composed of the difference between the true and complement waveforms, to allow measurement of differential impedance.</li> <li>4. Measure the minimum and maximum impedances found between the connector and the open circuited far end of the cable.</li> </ul> | Impedance must be in the range specified in Table 7-9 (ZO).                                                                                                                                                                   |

| Table 6-7. USB Electrical, Mechanical, and Environmental Compliance Standards (Continued) |

|-------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------|

| Test Description                                                | Test Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Performance Requirement                                                      |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

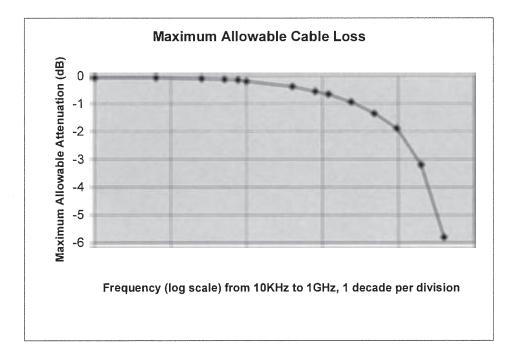

| Signal Pair Attenuation<br>(Only required for high-/full-speed) | <ol> <li>The object of this test is to insure that adequate signal strength is presented to the receiver to maintain a low error rate.</li> <li>Connect the Network Analyzer output port (port 1) to the input connector on the attenuation test fixture (Note 2).</li> <li>Connect the Series "A" plug of the cable to be tested to the test fixture, leaving the other end open-circuited.</li> <li>Calibrate the network analyzer and fixture using the appropriate calibration standards over the desired frequency range.</li> <li>Follow the method listed in Hewlett Packard Application Note 380-2 to measure the open-ended response of the cable.</li> <li>Short circuit the Series "B" end (or bare leads end, if a captive cable) and measure the short-circuit response.</li> <li>Using the software in H-P App. Note 380-2 or equivalent, calculate the cable attenuation accounting for resonance effects in the cable as needed.</li> </ol> | Refer to Section 7.1.17 for<br>frequency range and allowable<br>attenuation. |

| Table 6-7. L | JSB Electrical. | Mechanical. | and Environmental | <b>Compliance Standards</b> | (Continued) |

|--------------|-----------------|-------------|-------------------|-----------------------------|-------------|

| Test Description  | Test Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Performance Requirement                                                                                                                                                                 |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

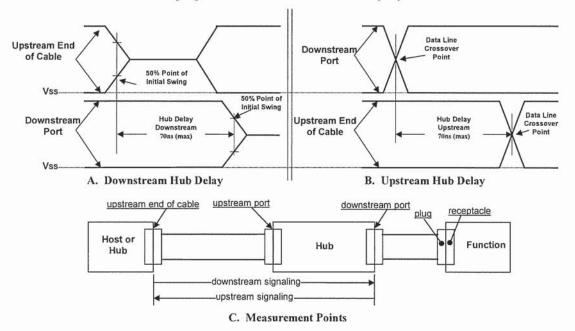

| Propagation Delay | <ul> <li>The purpose of the test is to verify the end to end propagation of the cable.</li> <li>1. Connect one output of the TDR sampling head to the D+ and D- inputs of the impedance/delay/skew test fixture (Note 1). Use one 50 Ω cable for each signal and set the TDR head to differential TDR mode.</li> <li>2. Connect the cable to be tested to the test fixture. If detachable, plug both connectors in to the matching fixture connectors. If captive, plug the series "A" plug into the matching fixture connector and solder the stripped leads on the other end to the test fixture.</li> <li>3. Measure the propagation delay of the test fixture from input to output and recording the delay.</li> <li>4. Remove the short piece of wire and remeasure the propagation delay. Subtract from it the delay of the test fixture the propagation delay of the test fixture the propagation delay.</li> </ul> | High-/full-speed.<br>See Section 7.1.1,<br>Section 7.1.4, Section 7.1.16, and<br>Table 7-9 (TFSCBL).<br>Low-speed.<br>See Section 7.1.12,<br>Section 7.1.16, and Table 7-9<br>(TLSCBL). |

| Table 6 7  | LISP Floatwight | Machanical   | and Environmental | Compliance Standard  | (Continued) |

|------------|-----------------|--------------|-------------------|----------------------|-------------|

| Table 0-7. | USD Electrical, | wiechamical, | and Environmental | Compliance Standards | (Continueu) |

| Test Description                               | Test Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Performance Requirement                                                       |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Propagation Delay Skew                         | <ol> <li>This test insures that the signal on<br/>both the D+ and D- lines arrive at<br/>the receiver at the same time.</li> <li>Connect the TDR to the fixture<br/>with test sample cable, as in<br/>the previous section.</li> <li>Measure the difference in<br/>delay for the two conductors in<br/>the test cable. Use the TDR<br/>cursors to find the open-<br/>circuited end of each<br/>conductor (where the<br/>impedance goes infinite) and<br/>subtract the time difference<br/>between the two values.</li> </ol>               | Propagation skew must meet the<br>requirements as listed in<br>Section 7.1.3. |

| Capacitive Load<br>Only required for low-speed | <ul> <li>The purpose of this test is to insure the distributed inter-wire capacitance is less than the lumped capacitance specified by the low-speed transmit driver.</li> <li>1. Connect the one lead of the Impedance Analyzer to the D+pin on the impedance/delay/skew fixture (Note 1) and the other lead to the D-pin.</li> <li>2. Connect the series "A" plug to the fixture, with the series "B" end leads open-circuited.</li> <li>3. Set the Impedance Analyzer to a frequency of 100 kHz, to measure the capacitance.</li> </ul> | See Section 7.1.1.2 and Table 7-7<br>(CLINUA).                                |

| TC 11 / 7    | TICD DI        | 34 1        | I Describe a second and       | C           | C4            | (C. I' I)   |

|--------------|----------------|-------------|-------------------------------|-------------|---------------|-------------|

| 1 9 DIC D_ / | INK Electrical | Viechanical | , and Environmental           | I ompliance | Standards     | ( ontinued) |

| I able v / · | COD LICCUICHI  | THECHNERRE  | , and and the one contraction | Company     | Seminaria des | Continueur  |

Note1: Impedance, propagation delay, and skew test fixture

This fixture will be used with the TDR for measuring the time domain performance of the cable under test. The fixture impedance should be matched to the equipment, typically 50  $\Omega$ . Coaxial connectors should be provided on the fixture for connection from the TDR.

Note 2: Attenuation text fixture

This fixture provides a means of connection from the network analyzer to the Series "A" plug. Since USB signals are differential in nature and operate over balanced cable, a transformer or balun (North Hills NH13734 or equivalent) is ideally used. The transformer converts the unbalanced (also known as single-ended) signal from the signal generator which is typically a 50  $\Omega$  output to the balanced (also known as differential) and likely different impedance loaded presented by the cable. A second transformer or balun should be used on the other end of the cable under test to convert the signal back to unbalanced form of the correct impedance to match the network analyzer.

# 6.7.1 Applicable Documents

American National Standard/Electronic Industries Association

| ANSI/EIA-364-C (12/94) | Electrical Connector/Socket Test Procedures<br>Including Environmental Classifications |

|------------------------|----------------------------------------------------------------------------------------|

|                        |                                                                                        |

American Standard Test Materials

| ASTM-D-4565                    | Physical and Environmental Performance Properties<br>of Insulation and Jacket for Telecommunication<br>Wire and Cable, Test Standard Method |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| ASTM-D-4566                    | Electrical Performance Properties of Insulation and<br>Jacket for Telecommunication Wire and Cable, Test<br>Standard Method                 |

| Underwriters' Laboratory, Inc. |                                                                                                                                             |

| UL STD-94                      | Test for Flammability of Plastic materials for Parts<br>in Devices and Appliances                                                           |

| UL Subject-444 | Communication Cables |

|----------------|----------------------|

## 6.8 USB Grounding

The shield must be terminated to the connector plug for completed assemblies. The shield and chassis are bonded together. The user selected grounding scheme for USB devices, and cables must be consistent with accepted industry practices and regulatory agency standards for safety and EMI/ESD/RFI.

## 6.9 PCB Reference Drawings

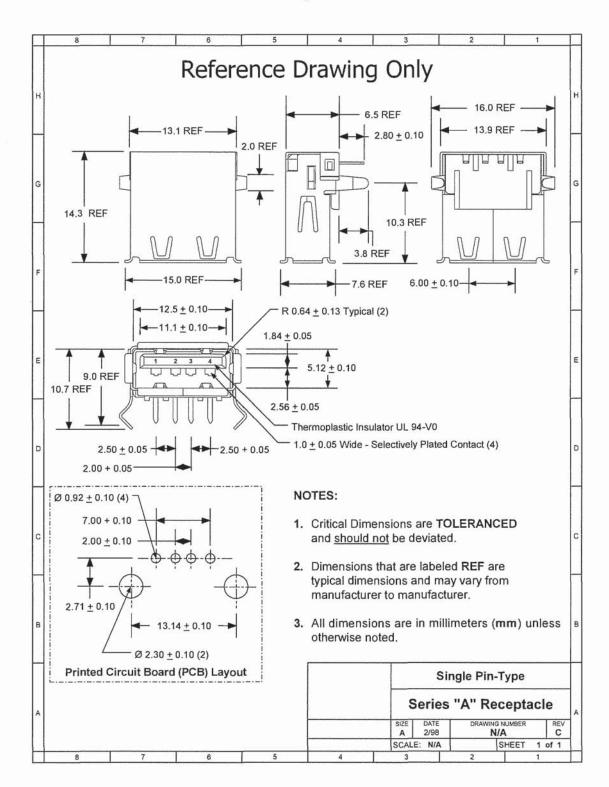

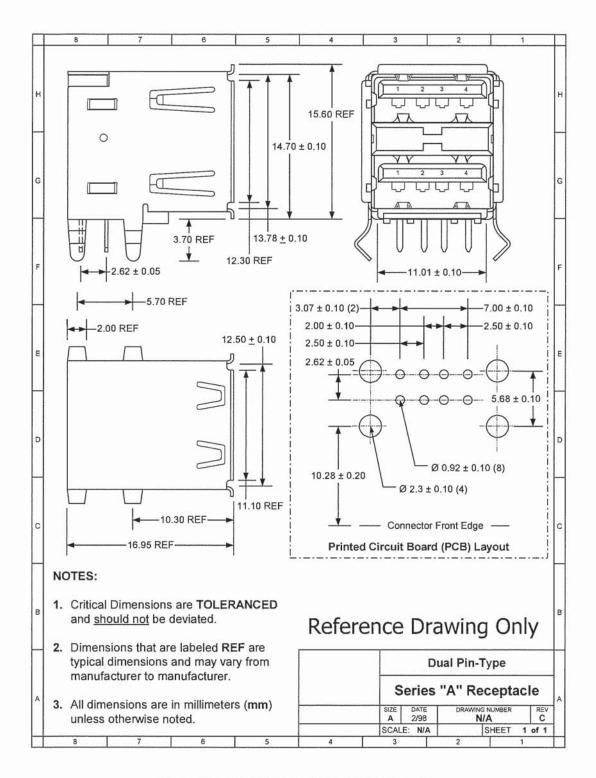

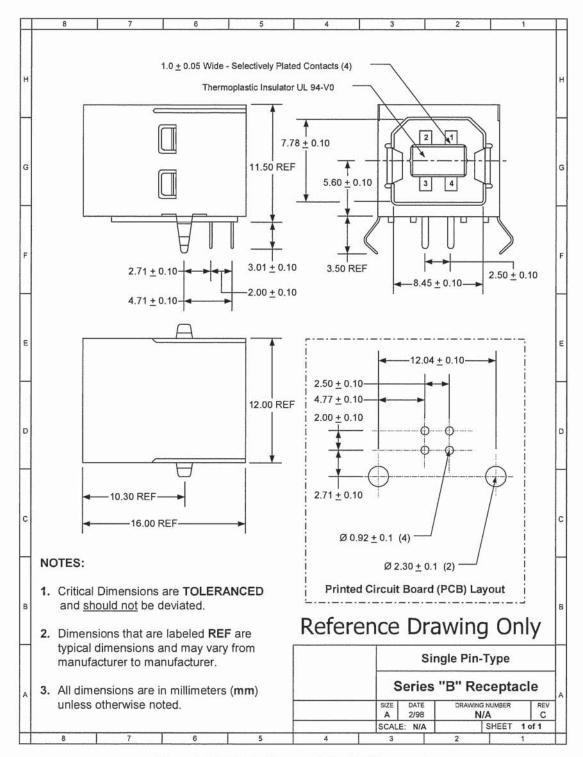

The drawings in Figure 6-12, Figure 6-13, and Figure 6-14 describe typical receptacle PCB interfaces. These drawings are included for informational purposes only.

Figure 6-12. Single Pin-type Series "A" Receptacle

Figure 6-13. Dual Pin-type Series "A" Receptacle

#### **Universal Serial Bus Specification Revision 2.0**

Figure 6-14. Single Pin-type Series "B" Receptacle

Universal Serial Bus Specification Revision 2.0

I

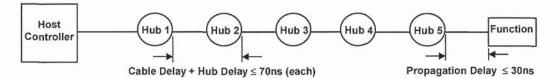

# Chapter 7 Electrical

This chapter describes the electrical specification for the USB. It contains signaling, power distribution, and physical layer specifications. This specification does not address regulatory compliance. It is the responsibility of product designers to make sure that their designs comply with all applicable regulatory requirements.

The USB 2.0 specification requires hubs to support high-speed mode. USB 2.0 devices are not required to support high-speed mode. A high-speed capable upstream facing transceiver must not support low-speed signaling mode. A USB 2.0 downstream facing transceiver must support high-speed, full-speed, and low-speed modes.

To assure reliable operation at high-speed data rates, this specification requires the use of cables that conform to all current cable specifications.

In this chapter, there are numerous references to strings of J's and K's, or to strings of 1's and 0's. In each of these instances, the leftmost symbol is transmitted/received first, and the rightmost is transmitted/received last.

# 7.1 Signaling

The signaling specification for the USB is described in the following subsections.

#### **Overview of High-speed Signaling**

A high-speed USB connection is made through a shielded, twisted pair cable that conforms to all current USB cable specifications.

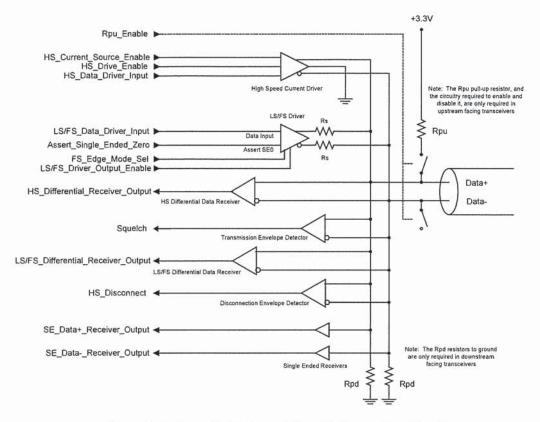

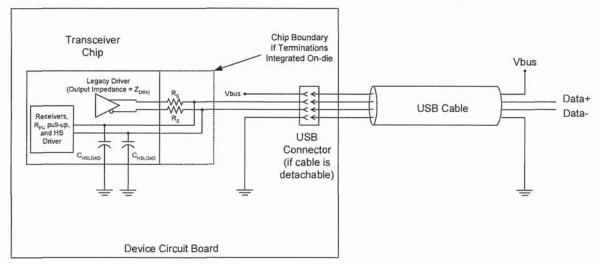

Figure 7-1. Example High-speed Capable Transceiver Circuit

Figure 7-1 depicts an example implementation which largely utilizes USB 1.1 transceiver elements and adds the new elements required for high-speed operation.

High-speed operation supports signaling at 480 Mb/s. To achieve reliable signaling at this rate, the cable is terminated at each end with a resistance from each wire to ground. The value of this resistance (on each wire) is nominally set to 1/2 the specified differential impedance of the cable, or 45  $\Omega$ . This presents a differential termination of 90  $\Omega$ .

For a link operating in high-speed mode, the high-speed idle state occurs when the transceivers at both ends of the cable present high-speed terminations to ground, and when neither transceiver drives signaling current into the D+ or D- lines. This state is achieved by using the low-/full-speed driver to assert a single ended zero, and to closely control the combined total of the intrinsic driver output impedance and the Rs resistance (to 45  $\Omega$ , nominal). The recommended practice is to make the intrinsic driver impedance as low as possible, and to let Rs contribute as much of the 45  $\Omega$  as possible. This will generally lead to the best termination accuracy with the least parasitic loading.

In order to transmit in high-speed mode, a transceiver activates an internal current source which is derived from its positive supply voltage and directs this current into one of the two data lines via a high speed current steering switch. In this way, the transceiver generates the high-speed J or K state on the cable.

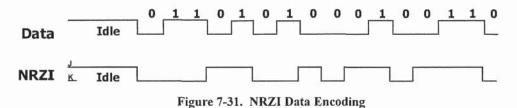

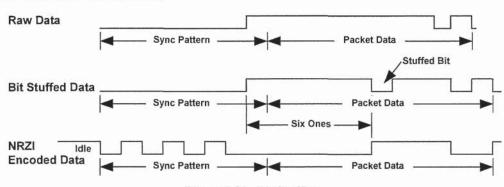

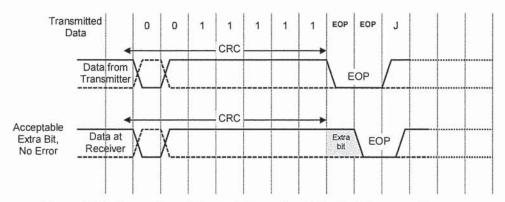

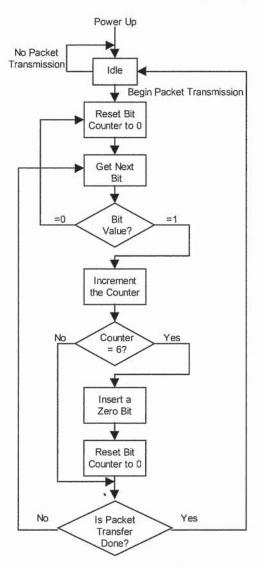

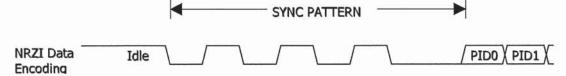

The dynamic switching of this current into the D+ or D- line follows the same NRZI data encoding scheme used in low-speed or full-speed operation and also in the bit stuffing behavior. To signal a J, the current is directed into the D+ line, and to signal a K, the current is directed into the D- line. The SYNC field and the EOP delimiters have been modified for high-speed mode. The magnitude of the current source and the value of the termination resistors are controlled to specified tolerances, and together they determine the actual voltage drive levels. The DC resistance from D+ or D- to the device ground is required to be 45  $\Omega \pm 10\%$  when measured without a load, and the differential output voltage measured across the lines (in either the J or K state) must be  $\pm 400 \text{ mV} \pm 10\%$  when D+ and D- are terminated with precision 45  $\Omega$  resistors to ground.

The differential voltage developed across the lines is used for three purposes:

- A differential receiver at the receiving end of the cable receives the differential data signal.

- A differential envelope detector at the receiving end of the cable determines when the link is in the Squelch state. A receiver uses squelch detection as indication that the signal at its connector is not valid.

- In the case of a downstream facing hub transceiver, a differential envelope detector monitors whether the signal at its connector is in the high-speed state. A downstream facing transceiver operating in high-speed mode is required to test for this state at a particular point in time when it is transmitting a SOF packet, as described in Section 7.1.7.3. This is used to detect device disconnection. In the absence of the far end terminations, the differential voltage will nominally double (as compared to when a high-speed device is present) when a high-speed J or K are continuously driven for a period exceeding the round-trip delay for the cable and board-traces between the two transceivers.

USB 2.0 requires that a downstream facing transceiver must be able to operate in low-speed, full-speed, and high-speed signaling modes. An upstream facing high-speed capable transceiver must not operate in low-speed signaling mode, but must be able to operate in full-speed signaling mode. Therefore, a 1.5 k $\Omega$  pull-up on the D-line is not allowed for a high-speed capable device, since a high-speed capable transceiver must never signal low-speed operation to the hub port to which it is attached.

Table 7-1 describes the required functional elements of a high-speed capable transceiver, using the diagram shown in Figure 7-1 as an example.

| Element                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-/full-speed Driver                   | The low-/full-speed driver is used for low-speed and full-speed transmission. It is required to meet all specifications called out in USB 1.1 for low-speed and full-speed operation, with one exception. The exception is that in high-speed capable transceivers, the impedance of each output, including the contribution of Rs, must be 45 $\Omega \pm 10\%$ .                                                                                                                                                                                                                                                                                                                                                 |

|                                          | The line terminations for high-speed operation are created by having this driver drive D+ and D- to ground. (This is equivalent to driving SE0 in the full-speed or low-speed mode.) Because of the output impedance requirement described above, this provides a well-controlled high-speed termination on each data line to ground. This is equivalent to a 90 $\Omega$ differential termination.                                                                                                                                                                                                                                                                                                                |

| Low-/full-speed Differential<br>Receiver | The low-/full-speed differential receiver is used for receiving low-speed and full-<br>speed data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Single Ended Receivers                   | The single ended receivers are used for low-speed and full-speed signaling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| High-speed Current Driver                | The high-speed current driver is used for high-speed data transmission. A current source derived from a positive supply is switched into either the D+ or D-lines to signal a J or a K, respectively. The nominal value of the current source is 17.78 mA. When this current is applied to a data line with a 45 $\Omega$ termination to ground at each end, the nominal high level voltage (VHSOH) is +400 mV. The nominal differential high-speed voltage (D+ - D-) is thus 400 mV for a J and -400 mV for a K.                                                                                                                                                                                                  |

|                                          | The current source must comply with the Transmit Eye Pattern Templates specified in Section 7.1.2.2, starting with the first symbol of a packet. One means of achieving this is to leave the current source on continuously when a transceiver is operating in high-speed mode. If this approach is used, the current can be directed to the port ground when the transceiver is not transmitting (the example design in Figure 7-1 shows a control line called HS_Current_Source_Enable to turn the current on, and another called HS_Drive_Enable to direct the current into the data lines.) The penalty of this approach is the 17.78 mA of standing current for every such enabled transceiver in the system. |

|                                          | The preferred design is to fully turn the current source off when the transceiver is not transmitting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| High-speed Differential Data<br>Receiver | The high-speed differential data receiver is used to receive high-speed data. It is left to transceiver designers to choose between incorporating separate high-speed and low-/full-speed receivers, as shown in Figure 7-1, or combining both functions into a single receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## Table 7-1. Description of Functional Elements in the Example Shown in Figure 7-1

| Transmission Envelope<br>Detector  | This envelope detector is used to indicate that data is invalid when the amplitude of the differential signal at a receiver's inputs falls below the squelch threshold (VHSSQ). It must indicate Squelch when the signal drops below 100 mV differential amplitude, and it must indicate that the line is not in the Squelch state when the signal exceeds 150 mV differential amplitude. The response time of the detector must be fast enough to allow a receiver to detect data transmission, to achieve DLL lock, and to detect the end of the SYNC field within 12 bit times, the minimum number of SYNC bits that a receiver is guaranteed to see. This envelope detector must incorporate a filtering mechanism that prevents indication of squelch during the longest differential data transitions allowed by the receiver eye pattern specifications. |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Disconnection Envelope<br>Detector | This envelope detector is required in downstream facing ports to detect the high-<br>speed Disconnect state on the line (VHSDSC). Disconnection must be indicated<br>when the amplitude of the differential signal at the downstream facing driver's<br>connector $\geq$ 625 mV, and it must not be indicated when the signal amplitude is<br>$\leq$ 525 mV. The output of this detector is sampled at a specific time during the<br>transmission of the high-speed SOF EOP, as described in Section 7.1.7.3.                                                                                                                                                                                                                                                                                                                                                   |  |

| Pull-up Resistor (Rpu)             | This resistor is required only in upstream facing transceivers and is used to indicate signaling speed capability. A high-speed capable device is required to initially attach as a full-speed device and must transition to high-speed as described in this specification. Once operating in high-speed, the 1.5 k $\Omega$ resistor must be electrically removed from the circuit. In Figure 7-1, a control line called RPU_Enable is indicated for this purpose. The preferred embodiment is to attach matched switching devices to both the D+ and D- lines so as to keep the lines' parasitic loading balanced, even though a pull-up resistor must never be used on the D- line of an upstream facing high-speed capable transceiver. When connected, this pull-up must meet all the specifications called out for full-speed operation.                  |  |

| Pull-down Resistors (RPD)          | -down Resistors (RPD) These resistors are required only in downstream facing transceivers and r<br>conform to the same specifications called out for low-speed and full-speed<br>operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

Table 7-1. Description of Functional Elements in the Example Shown in Figure 7-1 (Continued)

## 7.1.1 USB Driver Characteristics

The USB uses a differential output driver to drive the USB data signal onto the USB cable.

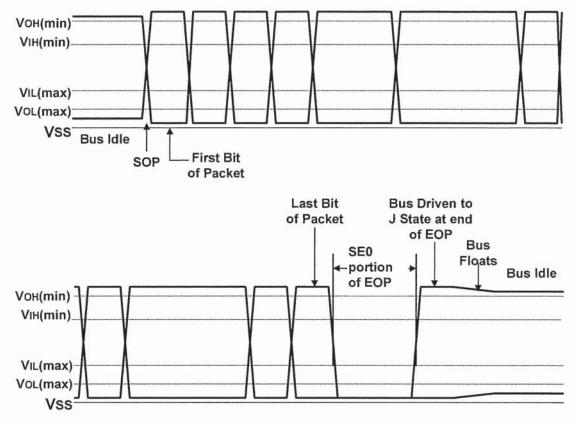

For low-speed and full-speed operation, the static output swing of the driver in its low state must be below VoL (max) of 0.3 V with a 1.5 k $\Omega$  load to 3.6 V, and in its high state must be above the VoH (min) of 2.8 V with a 15 k $\Omega$  load to ground as listed in Table 7-7. Full-speed drivers have more stringent requirements, as described in Section 7.1.1.1. The output swings between the differential high and low state must be well-balanced to minimize signal skew. Slew rate control on the driver is required to minimize the radiated noise and cross talk. The driver's outputs must support three-state operation to achieve bi-directional half-duplex operation.

Low-speed and full-speed USB drivers must never "intentionally" generate an SE1 on the bus. SE1 is a state in which both the D+ and D- lines are at a voltage above Vose1 (min), which is 0.8 V.

High-speed drivers use substantially different signaling levels, as described in Section 7.1.1.3.

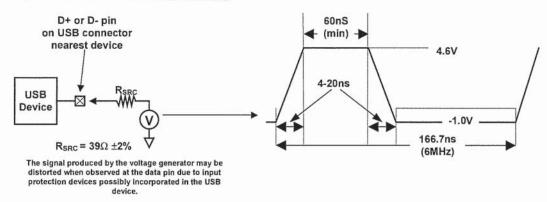

USB ports must be capable of withstanding continuous exposure to the waveforms shown in Figure 7-2 while in any drive state. These waveforms are applied directly into each USB data pin from a voltage source with an

output impedance of 39  $\Omega$ . The open-circuit voltage of the source shown in Figure 7-2 is based on the expected worst-case overshoot and undershoot.

## AC Stress Evaluation Setup

Figure 7-2. Maximum Input Waveforms for USB Signaling

#### Short Circuit Withstand

A USB transceiver is required to withstand a continuous short circuit of D+ and/or D- to VBUS, GND, other data line, or the cable shield at the connector, for a minimum of 24 hours without degradation. It is recommended that transceivers be designed so as to withstand such short circuits indefinitely. The device must not be damaged under this short circuit condition when transmitting 50% of the time and receiving 50% of the time (in all supported speeds). The transmit phase consists of a symmetrical signal that toggles between drive high and drive low. This requirement must be met for max value of VBUS (5.25 V).

It is recommended that these AC and short circuit stresses be used as qualification criteria against which the long-term reliability of each device is evaluated.

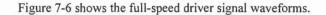

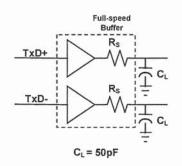

#### 7.1.1.1 Full-speed (12 Mb/s) Driver Characteristics

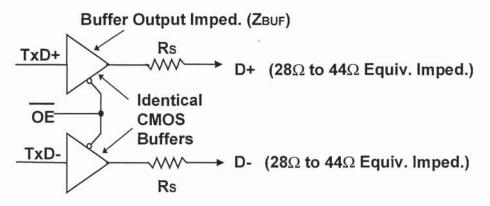

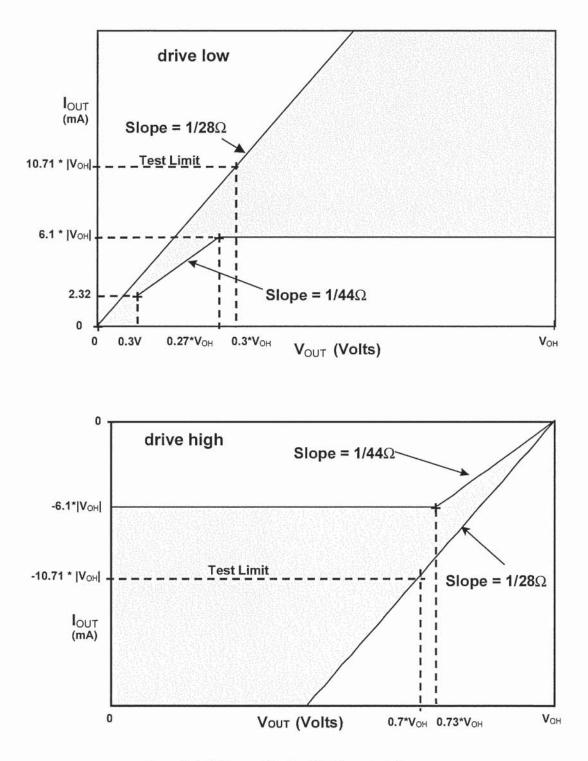

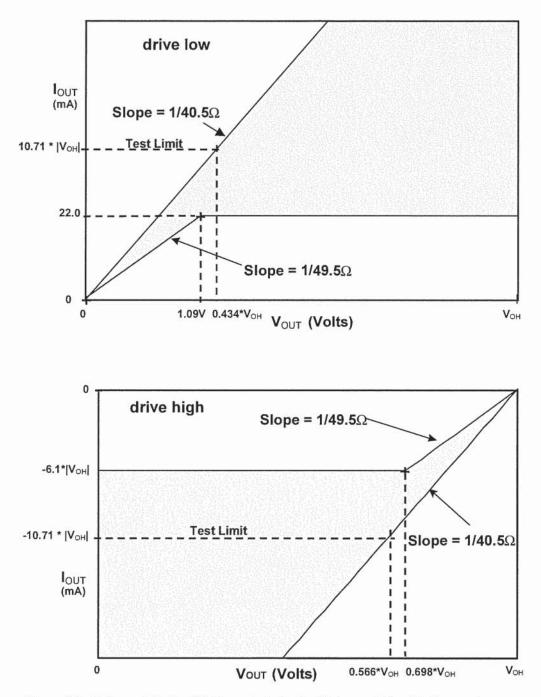

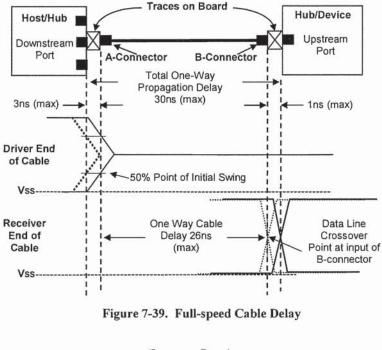

A full-speed USB connection is made through a shielded, twisted pair cable with a differential characteristic impedance (Z<sub>0</sub>) of 90  $\Omega \pm 15\%$ , a common mode impedance (Z<sub>CM</sub>) of 30  $\Omega \pm 30\%$ , and a maximum one-way delay (TFSCBL) of 26 ns. When the full-speed driver is not part of a high-speed capable transceiver, the impedance of each of the drivers (ZDRV) must be between 28  $\Omega$  and 44  $\Omega$ , i.e., within the gray area in Figure 7-4. When the full-speed driver is part of a high-speed capable transceiver, the impedance of each of the drivers (ZHSDRV) must be between 40.5  $\Omega$  and 49.5  $\Omega$ , i.e., within the gray area in Figure 7-5.

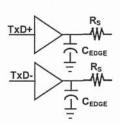

For a CMOS implementation, the driver impedance will typically be realized by a CMOS driver with an impedance significantly less than this resistance with a discrete series resistor making up the balance as shown in Figure 7-3. The series resistor Rs is included in the buffer impedance requirement shown in Figure 7-4 and Figure 7-5. In the rest of the chapter, references to the buffer assume a buffer with the series impedance unless stated otherwise.

Figure 7-3. Example Full-speed CMOS Driver Circuit (non High-speed capable)

#### Full-speed Buffers in Transceivers Which are Not High-speed Capable

The buffer impedance must be measured for driving high as well as driving low. Figure 7-4 shows the composite V/I characteristics for the full-speed drivers with included series damping resistor (RS). The characteristics are normalized to the steady-state, unloaded output swing of the driver. The normalized driver characteristics are found by dividing the measured voltages and currents by the actual swing of the driver under test. The normalized V/I curve for the driver must fall entirely inside the shaded region. The V/I region is bounded by the minimum driver impedance above and the maximum driver impedance below. The minimum drive region is intersected by a constant current region of |6.1VOH| mA when driving low and -|6.1VOH| mA when driving high. In the special case of a full-speed driver which is driving low, and which is part of a high-speed capable transceiver, the low drive region is intersected by a constant current that the waveform at the receiver crosses the opposite single-ended switching level on the first reflection.

When testing, the current into or out of the device need not exceed  $\pm 10.71$ \*VOH mA and the voltage applied to D+/D- need not exceed 0.3\*VOH for the drive low case and need not drop below 0.7\*VOH for the drive high case.

#### Full-speed Buffers in High-speed Capable Transceivers

Figure 7-5 shows the V/I characteristics for a Full-speed buffer which is part of a high-speed capable transceiver. The output impedance, ZHSDRV (including the contribution of RS), is required to be between 40.5  $\Omega$  and 49.5  $\Omega$ . Additionally, the output voltage must be within 10mV of ground when no current is flowing in or out of the pin (VHSTERM).

Figure 7-4. Full-speed Buffer V/I Characteristics

Figure 7-5. Full-speed Buffer V/I Characteristics for High-speed Capable Transceiver

ZTE/SAMSUNG 1008-0155 IPR2018-00111

Figure 7-6. Full-speed Signal Waveforms

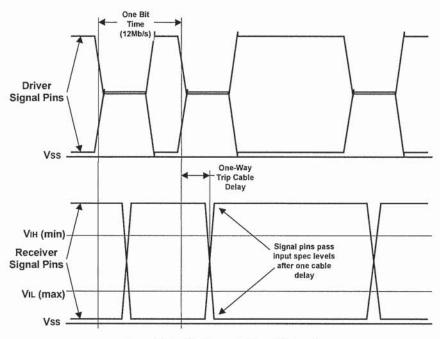

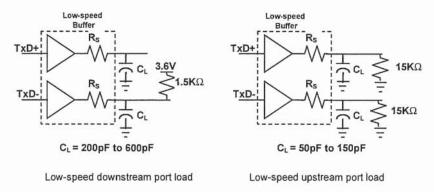

## 7.1.1.2 Low-speed (1.5 Mb/s) Driver Characteristics

A low-speed device must have a captive cable with the Series A connector on the plug end. The combination of the cable and the device must have a single-ended capacitance of no less than 200 pF and no more than 450 pF on the D+ or D- lines.

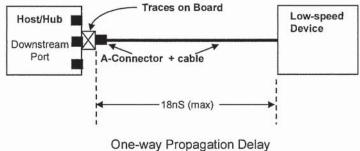

The propagation delay (TLSCBL) of a low-speed cable must be less than 18 ns. This is to ensure that the reflection occurs during the first half of the signal rise/fall, which allows the cable to be approximated by a lumped capacitance.

Figure 7-7 shows the low-speed driver signal waveforms.

Figure 7-7. Low-speed Driver Signal Waveforms

# 7.1.1.3 High-speed (480 Mb/s) Driver Characteristics

A high-speed USB connection is made through a shielded, twisted pair cable with a differential characteristic impedance (Z<sub>0</sub>) of 90  $\Omega \pm 15\%$ , a common mode impedance (Z<sub>CM</sub>) of 30  $\Omega \pm 30\%$ , and a maximum one-way delay of 26 ns (TFSCBL). The D+ and D- circuit board traces which run between a transceiver and its associated connector should also have a nominal differential impedance of 90  $\Omega$ , and together they may add an additional 4 ns of delay between the transceivers. (See Section 7.1.6 for details on impedance specifications of boards and transceivers.) The differential output impedance of a high-speed capable driver is required to be 90  $\Omega \pm 10\%$ . When either the D+ or D- lines are driven high, VHSOH (the high-speed mode high-level output voltage driven on a data line with a precision 45  $\Omega$  load to GND) must be 400 mV  $\pm 10\%$ . On a line which is not driven, either because the transceiver is not transmitting or because the opposite line is being driven high, VHSOL (the high-speed mode low-level output voltage driven on a data line with a 45  $\Omega$  load to GND) must be 0 V  $\pm 10$  mV.

Note: Unless indicated otherwise, all voltage measurements are to be made with respect to the local circuit ground.

Note: This specification requires that a high-speed capable transceiver operating in full-speed or low-speed mode must have a driver impedance (ZHSDRV) of 45  $\Omega \pm 10\%$ . It is recommended that the driver impedances be matched to within 5  $\Omega$  within a transceiver. For upstream facing transceivers which do not support high-speed mode, the driver output impedance (ZDRV) must fall within the range of 28  $\Omega$  to 44  $\Omega$ .

On downstream facing ports, RPD resistors (15 k $\Omega$  ±5%) must be connected from D+ and D- to ground.

When a high-speed capable transceiver transitions to high-speed mode, the high-speed idle state is achieved by driving SE0 with the low-/full-speed drivers at each end of the link (so as to provide the required terminations), and by disconnecting the D+ pull-up resistor in the upstream facing transceiver.

In the preferred embodiment, a transceiver activates its high-speed current driver only when transmitting highspeed signals. This is a potential design challenge, however, since the signal amplitude and timing specifications must be met even on the first symbol within a packet. As a less efficient alternative, a transceiver may cause its high-speed current source to be continually active while in high-speed mode. When the transceiver is not transmitting, the current may be directed into the device ground rather than through the current steering switch which is used for data signaling. In the example circuit, steering the current to ground is accomplished by setting HS Drive Enable low.

In CMOS implementations, the driver impedance will typically be realized by the combination of the driver's intrinsic output impedance and Rs. To optimally control ZHSDRV and to minimize parasitics, it is preferred the driver impedance be minimized (under 5  $\Omega$ ) and the balance of the 45  $\Omega$  should be contributed by the Rs component.

When a transceiver operating in high-speed mode transmits, the transmit current is directed into either the D+ or D- data line. A J is asserted by directing the current to the D+ line, a K by directing it to the D- line.

When each of the data lines is terminated with a 45  $\Omega$  resistor to the device ground, the effective load resistance on each side is 22.5  $\Omega$ . Therefore, the line into which the drive current is being directed rises to 17.78 ma \* 22.5  $\Omega$  or 400 mV (nominal). The other line remains at the device ground voltage. When the current is directed to the opposite line, these voltages are reversed.

# 7.1.2 Data Signal Rise and Fall, Eye Patterns

The following sections specify the data signal rise and fall times for full-speed and low-speed signaling, and the rise time and eye patterns for high-speed signaling.

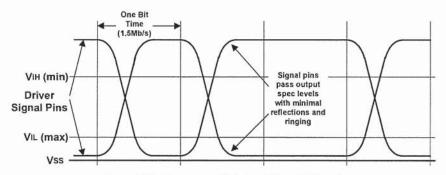

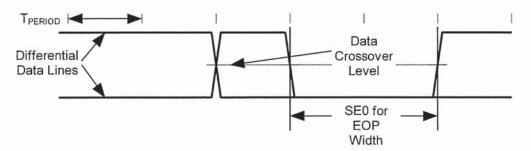

## 7.1.2.1 Low-speed and Full-speed Data Signal Rise and Fall

For low-speed and full-speed, the output rise time and fall times are measured between 10% and 90% of the signal (Figure 7-8). Rise and fall time requirements apply to differential transitions as well as to transitions between differential and single-ended signaling.

The rise and fall times for full-speed buffers are measured with the load shown in Figure 7-9. The rise and fall times must be between 4 ns and 20 ns and matched to within  $\pm 10\%$  to minimize RFI emissions and signal skew. The transitions must be monotonic.

The rise and fall times for low-speed buffers are measured with the load shown in Figure 7-10. The capacitive load shown in Figure 7-10 is representative of the worst-case load allowed by the specification. A downstream facing transceiver is allowed 150 pF of input/output capacitance (CIND). A low-speed device (including cable) may have a capacitance of as little as 200 pF and as much as 450 pF. This gives a range of 200 pF to 600 pF as the capacitive load that a downstream facing low-speed buffer might encounter. Upstream facing buffers on low-speed devices must be designed to drive the capacitance of the attached cable plus an additional 150 pF. If a low-speed buffer is designed for an application where the load capacitance is known to fall in a different range, the test load can be adjusted to match the actual application. Low-speed buffers on hosts and hubs that are attached to USB receptacles must be designed for the 200 pF to 600 pF range. The rise and fall time must be between 75 ns and 300 ns for any balanced, capacitive test load. In all cases, the edges must be matched to within  $\pm 20\%$  to minimize RFI emissions and signal skew. The transitions must be monotonic.

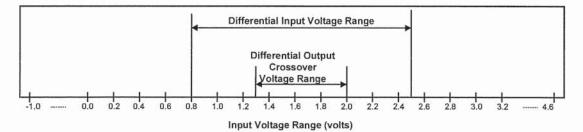

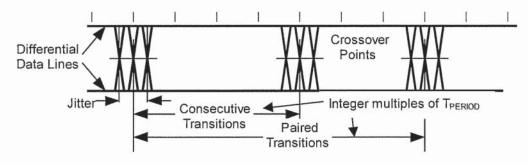

For both full-speed and low-speed signaling, the crossover voltage (VCRS) must be between 1.3 V and 2.0 V.

For low-speed and full-speed, this specification does not require matching signal swing matching to any greater degree than described above. However, when signaling, it is preferred that the average voltage on the D+ and D- lines should be constant. This means that the amplitude of the signal swing on both D+ and D- should be the same; the low and high going transition should begin at the same time and change at the same rate; and the crossover voltage should be the same when switching to a J or K. Deviations from signal matching will result in common-mode noise that will radiate and affect the ability of devices and systems to pass tests that are mandated by government agencies.

Figure 7-8. Data Signal Rise and Fall Time

Figure 7-9. Full-speed Load

#### **Universal Serial Bus Specification Revision 2.0**

Figure 7-10. Low-speed Port Loads

Note: The CL for low-speed port load only represents the range of loading that might be added when the lowspeed device is attached to a hub. The low-speed buffer must be designed to drive the load of its attached cable plus CL. A low-speed buffer design that can drive the downstream test load would be capable of driving any legitimate upstream load.

# 7.1.2.2 High-speed Signaling Eye Patterns and Rise and Fall Time

The following specifications apply to high-speed mode signaling. All bits, including the first and last bit of a packet, must meet the following eye pattern requirements for timing and amplitude.

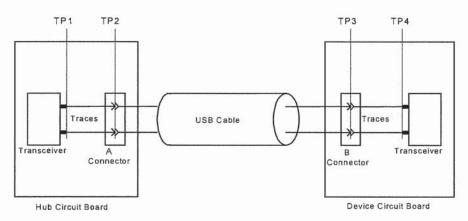

Figure 7-11 defines four test planes which will be referenced in this section. TP1 and TP4 are the points where the transceiver IC pins are soldered to the hub and device circuit boards, respectively. TP2 is at the mated pins of the A connector, and TP3 is at the mated pins of the B connector (or, in the case of a captive cable, where the cable is attached to the circuit board). The following differential eye pattern templates specify transmit waveform and receive sensitivity requirements at various points and under various conditions.

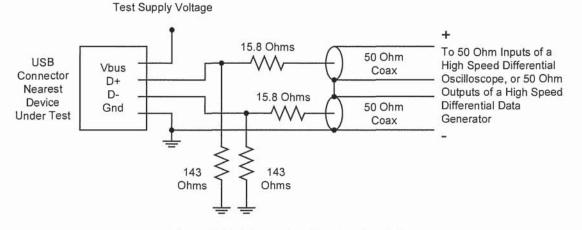

When testing high-speed transmitters and receivers, measurements are made with the Transmitter/Receiver Test Fixture shown in Figure 7-12. In either case, the fixture is attached to the USB connector closest to the transceiver being tested.

Transmitter Test Attenuation: Voltage at Scope Inputs = 0.760 \* Voltage at Transmitter Outputs Receiver Test Attenuation: Voltage at Receiver Inputs = 0.684 \* Voltage at Data Generator Outputs

Figure 7-12. Transmitter/Receiver Test Fixture

Note: When testing the upstream facing port of a device, VBUS must be provided from the time the device is placed in the appropriate test mode until the test is completed. This requirement will likely necessitate additional switching functionality in the test fixture (for example, to switch the D+ and D- lines between the host controller and the test instrument). Such additions must have minimal impact on the high frequency measurement results.

Transmit eye patterns specify the minimum and maximum limits, as well as limits on timing jitter, within which a driver must drive signals at each of the specified test planes. Receive eye patterns specify the minimum and maximum limits, as well as limits on timing jitter, within which a receiver must recover data.

Conformance to Templates 1, 2, 3, and 4 is required for USB 2.0 hubs and devices:

- Template 1: Transmit waveform requirements for hub measured at TP2, and for device (without a captive cable) measured at TP3

- Template 2: Transmit waveform requirements for device (with a captive cable) measured at TP2

- Template 3: Receiver sensitivity requirements for device (with a captive cable) when signal is applied at TP2

- Template 4: Receiver sensitivity requirements for device (without a captive cable) when signal is applied at TP3, and for hub when signal is applied at TP2

- Templates 5 and 6 are recommended guidelines for designers:

- Template 5: Transmit waveform requirements for hub transceiver measured at TP1, and for device transceiver measured at TP4

- Template 6: Receiver sensitivity requirements for device transceiver when signal is applied at TP4, and for hub transceiver at when signal is applied at TP1

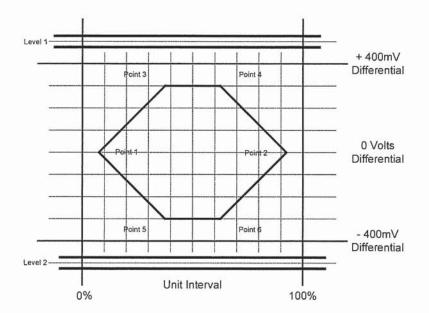

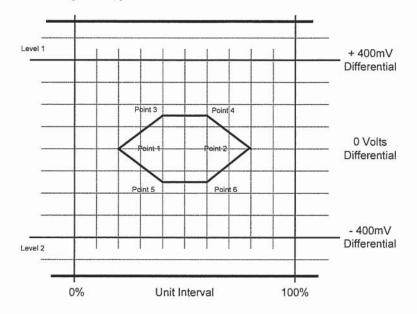

Figure 7-13 shows the transmit waveform requirements for a hub measured at TP2, and for a device (without a captive cable) measured at TP3.

|         | Voltage Level (D+ - D-)                                      | Time (% of Unit Interval) |

|---------|--------------------------------------------------------------|---------------------------|

| Level 1 | 525 mV in UI following a transition,<br>475 mV in all others | N/A                       |

| Level 2 | -525 mV in UI following a transition,<br>-475 in all others  | N/A                       |

| Point 1 | 0 V                                                          | 7.5% UI                   |

| Point 2 | 0 V                                                          | 92.5% UI                  |

| Point 3 | 300 mV                                                       | 37.5% UI                  |

| Point 4 | 300 mV                                                       | 62.5% UI                  |

| Point 5 | -300 mV                                                      | 37.5% UI                  |

| Point 6 | -300 mV                                                      | 62.5% UI                  |

Figure 7-13. Template 1

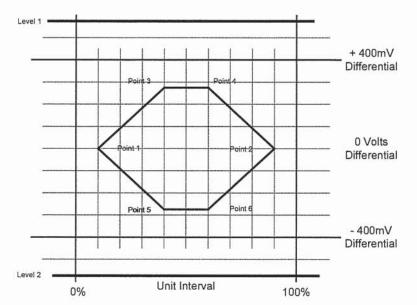

Figure 7-14 shows transmit waveform requirements for a device (with a captive cable) measured at TP2.

### **Template 2**

Level 1 + 400mV Differential Point 3 Point 4 Point 2 Point 4 Point 2 Point 5 Point 6 Unit Interval 0%

Voltage Level (D+ - D-) Time (% of Unit Interval) Level 1 525 mV in UI following a transition, N/A 475 mV in all others Level 2 -525 mV in UI following a transition, N/A -475 in all others 0V Point 1 12.5% UI 0 V Point 2 87.5% UI Point 3 175 mV 35% UI Point 4 175 mV 65% UI Point 5 -175 mV 35% UI Point 6 -175 mV 65% UI

Figure 7-14. Template 2

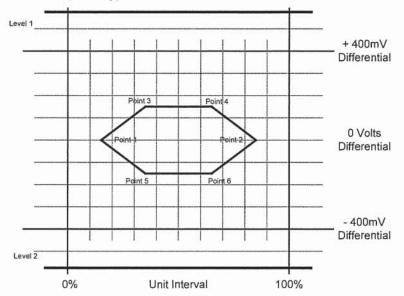

Figure 7-15 shows receiver sensitivity requirements for a device (with a captive cable) when a signal is applied at TP2.

|         | Voltage Level (D+ - D-) | Time (% of Unit Interval) |  |

|---------|-------------------------|---------------------------|--|

| Level 1 | 575 mV                  | N/A                       |  |

| Level 2 | -575 mV                 | N/A                       |  |

| Point 1 | 0 V                     | 10% UI                    |  |

| Point 2 | 0 V                     | 90% UI                    |  |

| Point 3 | 275 mV                  | 40% UI                    |  |

| Point 4 | 275 mV                  | 60% UI                    |  |

| Point 5 | -275 mV                 | 40% UI                    |  |

| Point 6 | -275 mV                 | 60% UI                    |  |

#### Figure 7-15. Template 3

Note: This eye is intended to specify differential data receiver sensitivity requirements. Levels 1 and 2 are outside the Disconnect Threshold values, but disconnection is detected at the source (after a minimum of 32 bit times without any transitions), not at the target receiver.

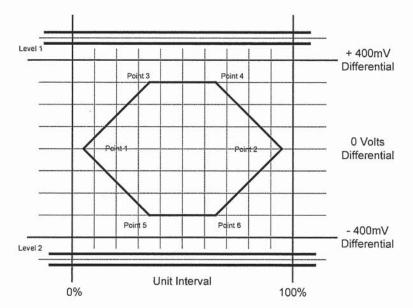

Figure 7-16 shows receiver sensitivity requirements for a device (without a captive cable) when signal is applied at TP3, and for a hub when a signal is applied at TP2.

|         | Voltage Level (D+ - D-) | Time (% of Unit Interval) |  |

|---------|-------------------------|---------------------------|--|

| Level 1 | 575 mV                  | N/A                       |  |

| Level 2 | -575 mV                 | N/A                       |  |

| Point 1 | 0 V                     | 15% UI                    |  |

| Point 2 | 0 V                     | 85% UI                    |  |

| Point 3 | 150 mV                  | 35% UI                    |  |

| Point 4 | 150 mV                  | 65% UI                    |  |

| Point 5 | -150 mV                 | 35% UI                    |  |

| Point 6 | -150 mV                 | 65% UI                    |  |

Figure 7-16. Template 4

Note: This eye is intended to specify differential data receiver sensitivity requirements. Levels 1 and 2 are outside the Disconnect Threshold values, but disconnection is detected at the source (after a minimum of 32 bit times without any transitions), not at the target receiver.

Figure 7-17 shows transmit waveform requirements for a hub transceiver measured at TP1 and for a device transceiver measured at TP4.

|         | Voltage Level (D+ - D-)                                      | Time (% of Unit Interval) |

|---------|--------------------------------------------------------------|---------------------------|

| Level 1 | 525 mV in UI following a transition,<br>475 mV in all others | N/A                       |

| Level 2 | -525 mV in UI following a transition,<br>-475 in all others  | N/A                       |

| Point 1 | 0 V                                                          | 5% UI                     |

| Point 2 | 0 V                                                          | 95% UI                    |

| Point 3 | 300 mV                                                       | 35% UI                    |

| Point 4 | 300 mV                                                       | 65% UI                    |

| Point 5 | -300 mV                                                      | 35% UI                    |

| Point 6 | -300 mV                                                      | 65% UI                    |

Figure 7-17. Template 5

Figure 7-18 shows receiver sensitivity requirements for a device transceiver when a signal is applied at TP4 and for a hub transceiver when a signal is applied at TP1.

|         | Voltage Level (D+ - D-) | Time (% of Unit Interval) |  |

|---------|-------------------------|---------------------------|--|

| Level 1 | 575 mV                  | N/A                       |  |

| Level 2 | -575 mV                 | N/A                       |  |

| Point 1 | 0 V                     | 20% UI                    |  |

| Point 2 | 0 V                     | 80% UI                    |  |

| Point 3 | 150 mV                  | 40% UI                    |  |

| Point 4 | 150 mV                  | 60% UI                    |  |

| Point 5 | -150 mV                 | 40% UI                    |  |

| Point 6 | -150 mV                 | 60% UI                    |  |

#### Figure 7-18. Template 6

Note: This eye is intended to specify differential data receiver sensitivity requirements. Levels 1 and 2 are outside the Disconnect Threshold values, but disconnection is detected at the source (after a minimum of 32 bit times without any transitions), not at the target receiver.

#### High-speed Signaling Rise and Fall Times

The transition time of a high-speed driver must not be less than the specified minimum allowable differential rise and fall time (THSR and THSF). Transition times are measured when driving a reference load of 45  $\Omega$  to ground on D+ and D-. Figure 7-12 shows a recommended "Transmitter Test Fixture" for performing these measurements.

For a hub, or for a device with detachable cable, the 10% to 90% high-speed differential rise and fall times must be 500 ps or longer when measured at the A or B receptacles (respectively).

For a device with a captive cable assembly, it is a recommended design guideline that the 10% to 90% highspeed differential rise and fall times must be 500 ps or longer when measured at the point where the cable is attached to the device circuit board.

It is required that high-speed data transitions be monotonic over the minimum vertical openings specified in the preceding eye pattern templates.

## 7.1.2.3 Driver Usage

The upstream facing ports of functions must use one and only one of the following three driver configurations:

- 1. Low-speed Low-speed drivers only

- 2. Full-speed Full-speed drivers only

- 3. Full-/high-speed Combination full-speed and high-speed drivers

Upstream facing USB 2.0 hub ports must use full-/high-speed drivers. Such ports must be capable of transmitting data at low-speed and full-speed rates with full-speed signaling, and at the high-speed rate using high-speed signaling. Downstream facing ports (including the host) must support low-speed, full-speed, and high-speed signaling, and must be able to transmit data at each of the three associated data rates.

In this section, there is reference to a situation in which high-speed operation is "disallowed." This topic is discussed in depth in Chapter 11 of this specification. In brief, a high-speed capable hub's downstream facing ports are "high-speed disallowed" if the hub is unable to establish a high-speed connection on its upstream facing port. For example, this would be the case for the downstream facing ports of a high-speed capable hub when the hub is connected to a USB 1.1 host controller.

When a full-/high-speed device is attached to a pre-USB 2.0 hub, or to a hub port which is high-speed disallowed, it is required to behave as a full-speed only device. When a full-/high-speed device is attached to a USB 2.0 hub which is not high-speed disallowed, it must operate with high-speed signaling and data rate.

#### 7.1.3 Cable Skew

The maximum skew introduced by the cable between the differential signaling pair (i.e., D+ and D- (TSKEW)) must be less than 100 ps and is measured as described in Section 6.7.

# 7.1.4 Receiver Characteristics

This section discusses the receiver characteristics for low-speed, full-speed, and full-/high-speed transceivers.

#### 7.1.4.1 Low-speed and Full-speed Receiver Characteristics

A differential input receiver must be used to accept the USB data signal. The receiver must feature an input sensitivity (VDI) of at least 200 mV when both differential data inputs are in the differential common mode range (VCM) of 0.8 V to 2.5 V, as shown in Figure 7-19.

In addition to the differential receiver, there must be a single-ended receiver for each of the two data lines. The receivers must have a switching threshold between 0.8 V (VIL) and 2.0 V (VIH). It is recommended that the single-ended receivers incorporate hysteresis to reduce their sensitivity to noise.

Both D+ and D- may temporarily be less than VIH (min) during differential signal transitions. This period can be up to 14 ns (TFST) for full-speed transitions and up to 210 ns (TLST) for low-speed transitions. Logic in the receiver must ensure that this is not interpreted as an SE0.

Figure 7-19. Differential Input Sensitivity Range for Low-/full-speed

# 7.1.4.2 High-speed Receiver Characteristics

A high-speed capable transceiver receiver must conform to the receiver characteristics specifications called out in Section 7.1.4.1 when receiving in low-speed or full-speed modes.

As shown in Figure 7-1, a high-speed capable transceiver which is operating in high-speed mode "listens" for an incoming serial data stream with the high-speed differential data receiver and the transmission envelope detector. Additionally, a downstream facing high-speed capable transceiver monitors the amplitude of the differential voltage on the lines with the disconnection envelope detector.

When receiving in high-speed mode, the differential receiver must be able to reliably receive signals that conform to the Receiver Eye Pattern templates shown in Section 7.1.2. Additionally, it is a strongly recommended guideline that a high-speed receiver should be able to reliably receive such signals in the presence of a common mode voltage component (VHSCM) over the range of -50 mV to 500 mV (the nominal common mode component of high-speed signaling is 200 mV). Low frequency chirp J and K signaling, which occurs during the Reset handshake, should be reliably received with a common mode voltage range of -50 mV to 600 mV.

Reception of data is qualified by the output of the transmission envelope detector. The receiver must disable data recovery when the signal falls below the high-speed squelch level (VHSSQ) defined in Table 7-3. (Detector must indicate squelch when the magnitude of the differential voltage envelope is  $\leq 100$  mV, and must not indicate squelch if the amplitude of differential voltage envelope is  $\geq 150$  mV.) Squelch detection must be done with a differential envelope detector, such as the one shown in Figure 7-1. The envelope detector used to detect the squelch state must incorporate a filtering mechanism that prevents indication of squelch during differential data crossovers.

The definition of a high-speed packet's SYNC pattern, together with the requirements for high-speed hub repeaters, guarantee that a receiver will see at least 12 bits of SYNC (KJKJKJKJKJKK) followed by the data portion of the packet. This means that the combination of squelch response time, DLL lock time, and end of SYNC detection must occur within 12 bit times. This is required to assure that the first bit of the packet payload will be received correctly.

In the case of a downstream facing port, a high-speed capable transceiver must include a differential envelope detector that indicates when the signal on the data exceeds the high-speed Disconnect level (VHSDSC) as defined in Table 7-3. (The detector must not indicate that the disconnection threshold has been exceeded if the differential signal amplitude is  $\leq$ 525 mV, and must indicate that the threshold has been exceeded if the differential signal amplitude is  $\geq$ 625 mV.)

When sampled at the appropriate time, this detector provides indication that the device has been disconnected. The details of how the disconnection envelope detector is used are described in Section 7.1.7.3.

## 7.1.5 Device Speed Identification

The following sections specify the speed identification mechanisms for low-speed, full-speed, and high-speed.

# 7.1.5.1 Low-/Full-speed Device Speed Identification

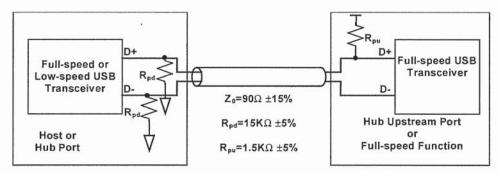

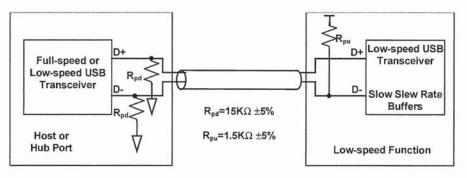

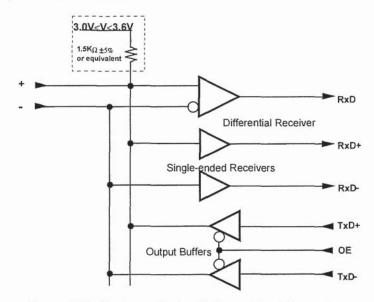

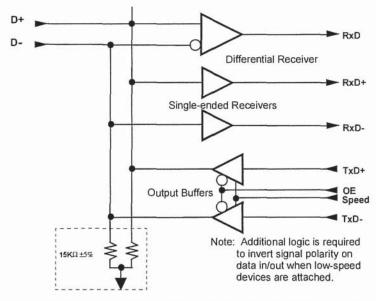

The USB is terminated at the hub and function ends as shown in Figure 7-20 and Figure 7-21. Full-speed and low-speed devices are differentiated by the position of the pull-up resistor on the downstream end of the cable:

- Full-speed devices are terminated as shown in Figure 7-20 with the pull-up resistor on the D+ line.

- Low-speed devices are terminated as shown in Figure 7-21 with the pull-up resistor on the D- line.

- The pull-down terminators on downstream facing ports are resistors of 15 kΩ ±5% connected to ground.

The design of the pull-up resistor must ensure that the signal levels satisfy the requirements specified in Table 7-2. In order to facilitate bus state evaluation that may be performed at the end of a reset, the design must be able to pull-up D+ or D- from 0 V to VIH (min) within the minimum reset relaxation time of 2.5  $\mu$ s. A device that has a detachable cable must use a 1.5 k $\Omega \pm 5\%$  resistor tied to a voltage source between 3.0 V and 3.6 V (VTERM) to satisfy these requirements. Devices with captive cables may use alternative termination means. However, the Thevenin resistance of any termination must be no less than 900  $\Omega$ .

Note: Thevenin resistance of termination does not include the 15 k $\Omega \pm 5\%$  resistor on host/hub.

The voltage source on the pull-up resistor must be derived from or controlled by the power supplied on the USB cable such that when VBUS is removed, the pull-up resistor does not supply current on the data line to which it is attached.

Figure 7-20. Full-speed Device Cable and Resistor Connections

Figure 7-21. Low-speed Device Cable and Resistor Connections

# 7.1.5.2 High-speed Device Speed Identification

The high-speed Reset and Detection mechanisms follow the behavioral model for low-/full-speed. When reset is complete, the link must be operating in its appropriate signaling mode (low-speed, full-speed, or high-speed as governed by the preceding usage rules), and the speed indication bits in the port status register will correctly report this mode. Software need only initiate the assertion of reset and read the port status register upon notification of reset completion.

High-speed capable devices initially attach as full-speed devices. This means that for high-speed capable upstream facing ports, RPU (1.5 k $\Omega \pm 5\%$ ) must be connected from D+ to the 3.3 V supply (as shown in Figure 7-1) through a switch which can be opened under SW control.

After the initial attachment, high-speed capable transceivers engage in a low level protocol during reset to establish a high-speed link and to indicate high-speed operation in the appropriate port status register. This protocol is described in Section 7.1.7.5.

## 7.1.6 Input Characteristics

The following sections describe the input characteristics for transceivers operating in low-speed, full-speed, and high-speed modes.

## 7.1.6.1 Low-speed and Full-speed Input Characteristics

The input impedance of D+ or D- without termination should be > 300 k $\Omega$  (ZINP). The input capacitance of a port is measured at the connector pins. Upstream facing and downstream facing ports are allowed different values of capacitance. The maximum capacitance (differential or single-ended) (CIND) allowed on a downstream facing port of a hub or host is 150 pF on D+ or D- when operating in low-speed or full-speed. This is comprised of up to 75 pF of lumped capacitance to ground on each line at the transceiver and in the connector, and an additional 75 pF capacitance on each conductor in the transmission line between the receptacle and the transceiver. The transmission line between the receptacle and RS must be 90  $\Omega \pm 15\%$ .

The maximum capacitance on an upstream facing port of a full-speed device with a detachable cable ( $C_{INUB}$ ) is 100 pF on D+ or D-. This is comprised of up to 75 pF of lumped capacitance to ground on each line at the transceiver and in the connector and an additional 25 pF capacitance on each conductor in the transmission line between the receptacle and the transceiver. The difference in capacitance between D+ and D- must be less than 10%.

For full-speed devices with captive cables, the device itself may have up to 75 pF of lumped capacitance to ground on D+ and D-. The cable accounts for the remainder of the input capacitance.

A low-speed device is required to have a captive cable. The input capacitance of the low-speed device will include the cable. The maximum single-ended or differential input capacitance of a low-speed device is 450 pF (CLINUA).

For devices with captive cables, the single-ended input capacitance must be consistent with the termination scheme used. The termination must be able to charge the D+ or D- line from 0 V to V<sub>IH</sub> (min) within 2.5  $\mu$ s. The capacitance on D+/D- includes the single-ended input-capacitance of the device (measured from the pins on the connector on the cable) and the 150 pF of input capacitance of the host/hub.

An implementation may use small capacitors at the transceiver for purposes of edge rate control. The sum of the capacitance of the added capacitor (CEDGE), the transceiver, and the trace connecting capacitor and transceiver to Rs must not exceed 75 pF (either single-ended or differential) and the capacitance must be balanced to within 10%. The added capacitor, if present, must be placed between the transceiver pins and Rs (see Figure 7-22).

Use of ferrite beads on the D+ or D- lines of full-speed devices is discouraged.

Figure 7-22. Placement of Optional Edge Rate Control Capacitors for Low-/full-speed

# 7.1.6.2 High-speed Input Characteristics

Figure 7-23 shows the simple equivalent loading circuit of a USB device operating in high-speed receive mode.

Figure 7-23. Diagram for High-speed Loading Equivalent Circuit

When operating in high-speed signaling mode, a transceiver must meet the following loading specifications:

- 1. DC output voltage and resistance specifications

- 2. TDR loading specification

Additionally, it is strongly recommended that a transceiver component operating in high-speed signaling mode should meet the following lumped capacitance guideline.

The use of ferrites on high-speed data lines is strongly discouraged.

**DC output voltage and resistance specifications** – A transceiver that is in high-speed mode must present a DC load on each of the data lines nominally equivalent to 45  $\Omega$  to ground. The actual resistance, ZHSDRV, must be 40.5  $\Omega \leq Z$ HSDRV  $\leq$  49.5  $\Omega$ . The output voltage in the high-speed idle state (VHSTERM) is specified in Table 7-3

**TDR loading specification** – The AC loading specifications of a transceiver in the high-speed idle state are specified in terms of differential TDR (Time Domain Reflectometer) measurements.

These measurements govern the maximum allowable transmission line discontinuities for the port connector, the interconnect leading from the connector to the transceiver, the transceiver package, and the transceiver IC itself. In the special case of a high-speed capable device with a captive cable, the transmission line discontinuities of the cable assembly are also governed.

143

The following specifications must be met with the incident rise time of the differential TDR set to 400 ps. It is important to note that all times are "as displayed" on the TDR and are hence "round trip times."

Termination Impedance (ZHSTERM) is measured on the TDR trace at a specific measurement time following the connector reference time. The connector reference time is determined by disconnecting the TDR connection from the port connector and noting the time of the open circuit step. For an A connector, the measurement time is 8 ns after the connector reference location. For a B connector, the measurement time is 4 ns after the connector reference location. The differential termination impedance must be:

#### 80 $\Omega \leq Z$ HSTERM $\leq 100 \Omega$

Through Impedance (ZHSTHRU) is the impedance measured from 500 ps before the connector reference location until the time governed by the Termination impedance specification.

#### $70 \ \Omega \le Z$ HSTHRU $\le 110 \ \Omega$

In the Exception Window (a sliding 1.4 ns window inside the Through Impedance time window), the differential impedance may exceed the Through limits. No single excursion, however, may exceed the Through limits for more than twice the TDR rise time (400 ps).

In the special case of a high-speed capable device with a captive cable, the same specifications must be met, but the TDR measurements must be made through the captive cable assembly. Determination of the connector reference time can be more difficult in this case, since the cable may not be readily removable from the port being tested. It is left to the tester of a specific device to determine the connector reference location by whatever means are available.

#### Lumped capacitance guideline for the transceiver component

When characterizing a transceiver chip as an isolated component, the measurement can be performed effectively at the chip boundary shown in Figure 7-23 without USB connectors or cables. Parasitic capacitance of the test fixture can be corrected by measuring the capacitance of the fixture itself and subtracting this reading from the reading taken with the transceiver inserted. If the terminations are off-chip, discrete Rs resistors should be in place during the measurements, and measurements should be taken on the "connector side" of the resistors. The transceiver should be in Test\_SE0\_NAK mode during testing.

Capacitance measurements are taken from each of the data lines to ground while the other line is left open. The instrument used to perform this measurement must be able to determine the effective capacitance to ground in the presence of the parallel effective resistance to ground.

Capacitance to Ground on each line:  $CHSLOAD \le 10 \text{ pF}$ Matching of Capacitances to Ground:  $\le 1.0 \text{ pF}$

The guideline is to allow no more than 5.0 pF for the transceiver die itself and no more than an additional 5 pF for the package. The differential capacitance across the transceiver inputs should be no more than 5.0 pF

#### 7.1.7 Signaling Levels

The following sections specify signaling levels for low-speed, full-speed, and high-speed operation.

#### 7.1.7.1 Low-/Full-speed Signaling Levels

Table 7-2 summarizes the USB signaling levels. The source is required to drive the levels specified in the second column, and the target is required to identify the correct bus state when it sees the levels in the third column. (Target receivers can be more sensitive as long as they are within limits specified in the fourth column.)

| Bus State                                | Signaling Levels                                                                              |                                                                                |                                                                                |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

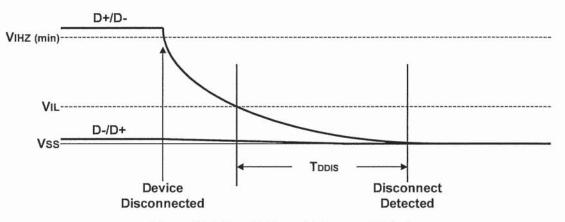

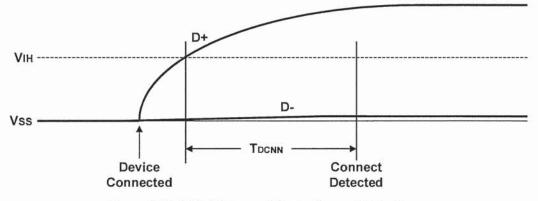

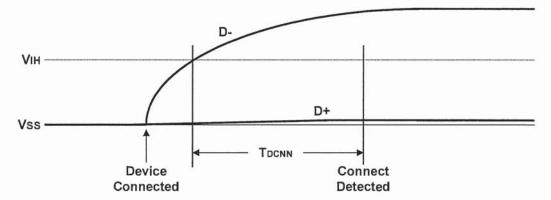

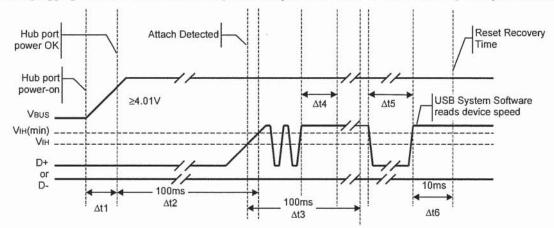

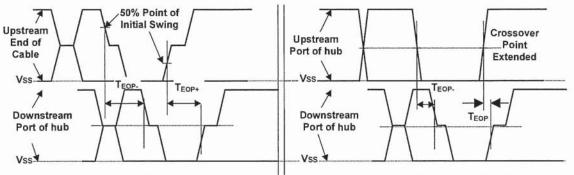

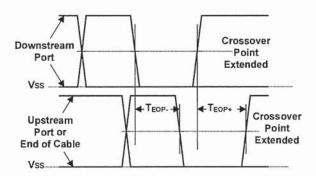

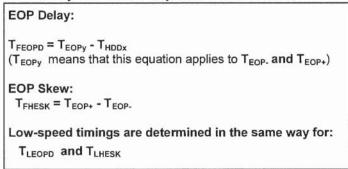

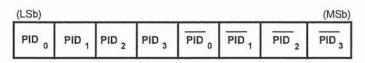

|                                          | At originating source                                                                         | At final target connector                                                      |                                                                                |  |