instruction set summaries in this chapter—focuses on the general principles of the architecture and on the portions of the architecture most relevant to understanding the measurements examined here. A list of the full VAX instruction set is included in Appendix B.

The VAX is a general-purpose register machine with a large orthogonal instruction set. Figure 4.2 shows the data types supported. The VAX uses the name "word" to refer to 16-bit quantities, while in this text we use the convention that a word is 32 bits. Be careful when reading the VAX instruction mnemonics, as they often refer to the names of the VAX data types. Figure 4.2 shows the conversion between the data type names used in this text and the VAX names. In addition to the data types in Figure 4.2, the VAX provides support for fixed- and variable-length bit strings, up to 32 bits in length.

The VAX provides 16 general-purpose registers, but four registers are effectively claimed by the instruction set architecture. For example, R14 is the stack pointer and R15 is the PC (program counter). Hence, R15 cannot be used

| Bits | Data type            | Our name         | DEC's name                                     |

|------|----------------------|------------------|------------------------------------------------|

| 8    | Integer              | Byte             | Byte                                           |

| 16   | Integer              | Halfword         | Word                                           |

| 32   | Integer              | Word             | Long word                                      |

| 32   | Floating point       | Single precision | F_floating                                     |

| 64   | Integer              | Doubleword       | Quad word                                      |

| 64   | Floating point       | Double precision | D_floating or G_floating                       |

| 128  | Integer              | Quadword         | Octa word                                      |

| 128  | Floating point       | Huge             | H_floating                                     |

| 8n   | Character string     | Character        | Character                                      |

| 4n   | Binary-coded decimal | Packed           | Packed                                         |

| 8n   | Numeric string       | Unpacked         | Numeric strings: Trailing and leading separate |

FIGURE 4.2 VAX data types, their lengths, and names. The first letter of the DEC type (B, W, L, F, Q, D, G, O, H, C, P, T, S) is often used to complete an opcode name. As examples, the move opcodes include MOVB, MOVB, MOVL, MOVF, MOVQ, MOVD, MOVD, MOVG, MOVO, MOVH, MOVC3, MOVP. Each move instruction transfers an operand of the data type indicated by the letter following MOV. (There is no difference between moves of character and numeric strings, so only move character operations are needed.) The length fields that appear as Xn indicate that the length may be any multiple of X in bits. The packed data type is special in that the length for operations on this type is always given in digits, each of which is four bits. The packed objects are still allocated and addressed in units of bytes. For any string data type the starting address is the low-order address of the string.

as a general-purpose register, and using R14 is very difficult because it interferes with instructions that manipulate the stack frame. Condition codes are used for branching and are set by all arithmetic and logical operations and by the move instruction. The move instruction transfers data between any two addressable locations and subsumes load, store, register—register moves, and memory—memory moves as special cases.

# **VAX Addressing Modes**

The addressing modes include most of those we discussed in Chapter 3: literal, register (operand is in a register), register deferred (register indirect), autodecrement, autoincrement, autoincrement deferred, byte/word/long displacement, byte/word/long displacement deferred, and scaled (called "indexed" in the VAX architecture). Scaled addressing mode may be applied to any general addressing mode except register or literal. Register is an addressing mode no different from any other in the VAX. Thus, a 3-operand VAX instruction may include from zero to three operand memory references, each of which may be any of the memory addressing modes. Since the memory indirect modes require an additional memory access, up to 6 memory accesses may be required for a 3-operand instruction. When the addressing modes are used with R15 (the PC), only a few are defined, and their meaning is special. The defined addressing modes with R15 are as follows:

- *Immediate*—an immediate value is in the instruction stream; this mode is encoded as autoincrement on PC.

- Absolute—a 32-bit absolute address is in the instruction stream; this mode is encoded as autoincrement deferred with PC as the register.

- Byte/word/long displacement—the same as the general mode, but the base is the PC, giving PC-relative addressing.

- Byte/word/long displacement deferred—the same as the general mode, but the base is the PC, giving addressing that is indirect through a memory location that is PC-relative.

A VAX instruction consists of an opcode followed by zero or more operand specifiers. The opcode is almost always a single byte that specifies the operation, the data type, and the operand count. Almost all operations are fully orthogonal with respect to addressing modes—any combination of addressing modes works with nearly every opcode, and many operations are supported for all possible data types.

Operand specifiers may vary in length from one byte to many, depending on the information to be conveyed. The first byte of each operand specifier consists of two 4-bit fields: the type of address specifier and a register that is part of the addressing mode. If the operand specifier requires additional bytes to specify a displacement, additional registers, or an immediate value, it is extended in 1-byte increments. The name, assembler syntax, and number of bytes for each operand specifier are shown in Figure 4.3. The total instruction length and format are easy to state: Simply add up the sizes of the operand specifiers and include one byte (or rarely two) for the opcode.

# **Example**

How long is the following instruction?

#### **Answer**

The opcode length is 1 byte, as is the first operand specifier (R1). The second operand specifier has two parts: the first part is a byte that specifies the addressing mode and base register; the second part is the 2-byte long displacement. The third operand specifier also has two parts: the first byte specifies immediate mode, and the second part contains the immediate. Because the data type is long (ADDL3), the immediate value takes 4 bytes.

Thus, the total length of the instruction is 1 + 1 + (1+2) + (1+4) = 10 bytes.

| Addressing mode                         | Syntax             | Length in bytes                    |

|-----------------------------------------|--------------------|------------------------------------|

| Literal                                 | #value             | 1 (6-bit signed value)             |

| Immediate                               | #value             | 1 + length of the immediate        |

| Register                                | Rn                 | 1                                  |

| Register deferred                       | (Rn)               | 1                                  |

| Byte/word/long<br>displacement          | Displacement (Rn)  | 1 + length of the displacement     |

| Byte/word/long<br>displacement deferred | @displacement (Rn) | 1 + length of the displacement     |

| Scaled (Indexed)                        | Base mode [Rx]     | 1 + length of base addressing mode |

| Autoincrement                           | (Rn)+              | 1                                  |

| Autodecrement                           | - (Rn)             | 1                                  |

| Autoincrement deferred                  | @(Rn)+             | 1                                  |

FIGURE 4.3 Length of the VAX operand specifiers. The length of each addressing mode is 1 byte plus the length of any displacement or immediate field that is in the mode. Literal mode uses a special 2-bit tag and the remaining 6 bits encode the constant value. The data we examined in Chapter 3 on constants showed the heavy use of small constants; the same observation motivated this optimization. The length of an immediate is dictated by the data type indicated in the opcode, not the value of the immediate.

| Туре                         | Example     | Instruction meaning                                                                                             |

|------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------|

| Data transfers               |             | Move data between byte, halfword, word, or doubleword operands; * is the data type                              |

|                              | MOV*        | Move between two operands                                                                                       |

|                              | MOVZB*      | Move a byte to a halfword or word, extending it with zeroes                                                     |

|                              | MOVA*       | Move address of operand; data type is last                                                                      |

| ·                            | PUSH*       | Push operand onto stack                                                                                         |

| Arithmetic,<br>logical       |             | Operations on integer or logical bytes, halfwords (16 bits), words (32 bits); * is the data type                |

|                              | ADD*_       | Add with 2 or 3 operands                                                                                        |

|                              | CMP*        | Compare and set condition codes                                                                                 |

|                              | TST*        | Compare to zero and set condition codes                                                                         |

|                              | ASH*        | Arithmetic shift                                                                                                |

|                              | CLR*        | Clear                                                                                                           |

|                              | CVTB*       | Sign extend byte to size of data type                                                                           |

| Control                      |             | Conditional and unconditional branches                                                                          |

|                              | BEQL, BNEQ  | Branch equal/not equal                                                                                          |

|                              | BCS, BCC    | Branch carry set, branch carry clear                                                                            |

|                              | BRB, BRW    | Unconditional branch with an 8-bit or 16-bit offset                                                             |

|                              | JMP         | Jump using any addressing mode to specify target                                                                |

|                              | AOBLEQ      | Add one to operand; branch if result ≤ second operand                                                           |

|                              | CASE        | Jump based on case selector                                                                                     |

| Procedure                    |             | Call/return from procedure                                                                                      |

|                              | CALLS       | Call procedure with arguments on stack (see Section 3.9)                                                        |

|                              | CALLG       | Call procedure with FORTRAN-style parameter list                                                                |

|                              | JSB         | Jump to subroutine, saving return address                                                                       |

|                              | RET         | Return from procedure call                                                                                      |

| Bit-field charact<br>decimal | er          | Operate on variable-length bit fields, character strings, and decimal strings, both in character and BCD format |

|                              | EXTV        | Extracts a variable-length bit field into a 32-bit word                                                         |

|                              | MOVC3       | Move a string of characters for given length                                                                    |

|                              | CMPC3       | Compare two strings of characters for given length                                                              |

|                              | MOVC5       | Move string of characters with truncation or filling                                                            |

|                              | ADDP4       | Add decimal string of the indicated length                                                                      |

|                              | CVTPT       | Convert packed-decimal string to character string                                                               |

| Floating point               |             | Floating-point operations on D, F, G, and H formats                                                             |

| - <del>-</del>               | ADDD_       | Add double-precision D-format floating numbers                                                                  |

|                              | SUBD        | Subtract double-precision D-format floating numbers                                                             |

|                              | MULF        | Multiply single-precision F-format floating point                                                               |

|                              | POLYF       | Evaluate a polynomial using table of coefficients in F format                                                   |

| System                       | <del></del> | Change to system mode, modify protected registers                                                               |

| -                            | CHMK, CHME  | Change mode to kernel/executive                                                                                 |

|                              | REI         | Return from exception or interrupt                                                                              |

| Other                        |             | Special operations                                                                                              |

|                              | CRC         | Calculate cyclic redundancy check                                                                               |

|                              | INSQUE      | Insert a queue entry into a queue                                                                               |

|                              |             |                                                                                                                 |

FIGURE 4.4 (Adjoining page) Classes of VAX instructions with examples. The asterisk stands for multiple data types—B, W, L, and usually D, F, G, H, and Q; remember how these VAX data types relate to the names used in the text (see Figure 4.2 on page 143). For example, a MOVW moves the VAX data-type word, which is 16 bits and is called a halfword in this text. The underline, as in ADDD\_, means there are 2-operand (ADDD2) and 3-operand (ADDD3) forms of this instruction. The operand count is explicit in the opcode.

# **Operations on the VAX**

What types of operators does the VAX provide? VAX operations can be divided into classes, as shown in Figure 4.4. (Detailed lists of the VAX instructions are included in Appendix B.) Figure 4.5 gives examples of typical VAX instructions and their meanings. Most instructions set the VAX condition codes according to their result; instructions without results, such as branches, do not. The condition codes are N (Negative), Z (Zero), V (oVerflow), and C (Carry).

| Example assembly instruction | Length | Meaning                                                                                                                                                                                                       |

|------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVL @40(R4),30(R2)          | . 5    | $M[M[40+R4]] \leftarrow_{32} M[30+R2]$                                                                                                                                                                        |

| MOVAW R2, (R3) [R4]          | 4      | R2← 32 R3+ (R4*2)                                                                                                                                                                                             |

| ADDL3 R5, (R6)+, (R6)+       | 4      | i←M[R6];R6←R6+4; R5←i+M[R6]; R6←R6+4                                                                                                                                                                          |

| CMPL -(R6),#100              | 7      | R6←R6-4; Set the condition code using: M[R6]-100                                                                                                                                                              |

| CVTBW R10, (R8)              | 3      | $R10_{1631} \leftarrow_{16} (M[R8]_0)^8 ## M[R8]$                                                                                                                                                             |

| BEQL name                    | . 2    | if equal(CC) {PC←name}<br>PC-128 ≤ name < PC+128                                                                                                                                                              |

| BRW name                     | 3      | PC←name<br>PC-32768 ≤ name < PC+32768                                                                                                                                                                         |

| EXTZV (R8),R5,R6,-564(R7)    | 7      | t $\leftarrow_{40}$ M[R7-564+(R5>>3)];<br>i $\leftarrow$ R5 & 7; j $\leftarrow$ if R6>=32 then 32 else if<br>R6<0 then 0 else R6;<br>M[R8] $\leftarrow_{32}$ 0 <sup>32-j</sup> ## t <sub>39-i-j+139-i</sub> ; |

| MOVC3 @36(R9),(R10),35(R11)  | 6      | R1 $\leftarrow$ 35+R11; R3 $\leftarrow$ M[36+R9];<br>for (R0 $\leftarrow$ M[R10];R0!=0;R0)<br>{M[R3] $\leftarrow$ 8M[R1]; R1++; R3++}<br>R2=0; R4=0; R5=0                                                     |

| ADDD3 R0,R2,R4               | 4      | $(R0#\#R1) \leftarrow_{64} (R2\#\#R3) + (R4\#\#R5)$<br>register contents are type D floating point.                                                                                                           |

FIGURE 4.5 Some examples of typical VAX instructions. VAX assembly language syntax puts the result operand last; we have put it first for consistency with other machines. Instruction length is given in bytes. The condition equal (CC) is true if the condition-code setting reflects equality after a compare. Remember that most instructions set the condition code; the only function of compare instructions is to set the condition code. The names t, i, j are used as a temporaries in the instruction descriptions; t is 40 bits in length, while i and j are 32 bits. The EXTZV instruction may appear mysterious. Its purpose is to extract a variable-length field (0 to 32 bits) and zero extend it to 32 bits. The source operands to the EXTZV are the starting bit position (which may be any distance from the starting byte address), the length of the field, and the starting address of the bit string to extract the field from. The VAX numbers its bits from low order to high order, but we number bits in the reverse order. Thus, the subscripts adjust the bit offsets accordingly (which makes EXTV look more mysterious!). Although the result of the variable bit string operations are always 32 bits, the MOVC3 changes the values of registers R0 through R5 as shown (although any of R0, R2, R4, and R5 could be used to hold the count). A discussion of why MOVC3 uses the GPRs as working registers appears in Section 5.6 of the next chapter.

# 4.3

# The 360/370 Architecture

The IBM 360 was introduced in 1964. Its official goals included the following:

- 1. Exploit storage—large main storage, storage hierarchies (ROM used for microcode).

- 2. Support concurrent I/O—up to 5 MB/second with a standard interface on all machines.

- 3. Create a general-purpose machine with new OS facilities and many data types.

- 4. Maintain strict upward and downward machine-language compatibility.

The System/370, first introduced in 1970, was a successor to System/360. System/370 is fully upward compatible with System/360, even in system mode. The major extensions over the 360 included

- Virtual memory and dynamic address translation (see Chapter 8, Section 8.5)

- A few new instructions: synchronization support, long string instructions (long move and long compare), additional instructions for manipulating bytes in registers, and some additional decimal instructions

- Removal of data alignment requirements

In addition, several important implementation differences were introduced in the 370 implementations, including MOS main memory rather than core, and writeable control store (see Chapter 5).

In 1983, IBM introduced 370-XA, the eXtended Architecture. Until this extension, first used in the 3080 series, the 360/370 architecture had a 24-bit address space. Additional bits were added to the program status word so that the program counter could be extended. Unfortunately, it was common programming practice on the 360 to use the high-order byte of an address for status. Thus, old 24-bit programs cannot be run in 32-bit mode (actually a 31-bit address), while new and recompiled programs can take advantage of the larger address space. The I/O structure was also changed to permit higher levels of multiprocessing.

The latest extension to the architecture was ESA/370, introduced with the 3090 model in 1986. ESA/370 added additional instruction formats, called the Extended formats, with 16-bit opcodes. ESA/370 includes support for a Vector Facility (including a set of vector registers) and an extended (128-bit) floating-point format. The address space was extended by adding segments on top of the 31-bit address space (see Chapter 8, Sections 8.5 and 8.6); a new and more powerful protection model was added as well.

The remainder of this section surveys the IBM 360 architecture and presents measurements for the workload. First, let's examine the basics of the 360 architecture, then look at the instruction set formats and some sample instructions.

## The 360/370 Instruction Set Architecture

The IBM System/360 is a 32-bit machine with byte addressability and support for a variety of data types: byte, halfword (16 bits), word (32 bits), doubleword (double-precision real), packed decimal, and unpacked character strings. The System/360 had alignment restrictions, which were removed in the System/370 architecture.

The internal state of the 360 has the following components:

- Sixteen 32-bit, general-purpose registers; register 0 is special when used in an addressing mode, where a zero is always substituted.

- Four double-precision (64-bit) floating-point registers.

- Program status word (PSW) holds the PC, some control flags, and the condition codes.

Later versions of the architecture extended this state with additional control registers.

## Addressing Modes and Instruction Formats

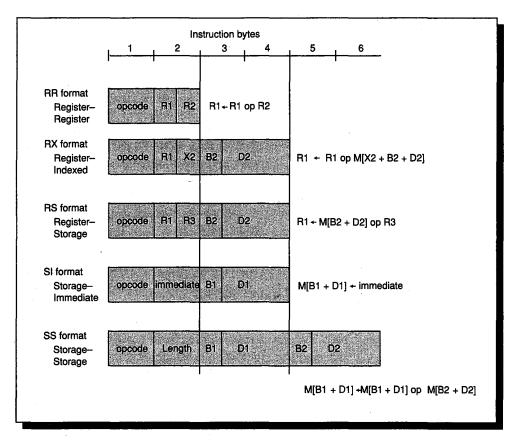

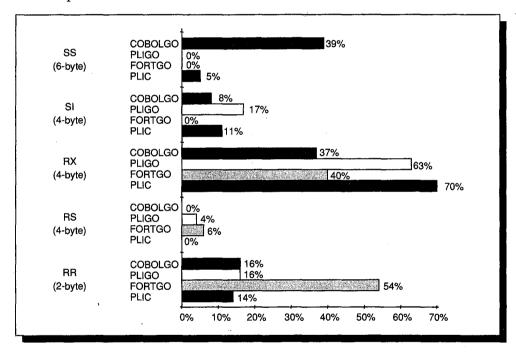

The 360/370 has five instruction formats. Each format is associated with a single addressing mode and has a set of operations defined for that format. While some operations are defined in multiple formats, most are not. The instruction formats are shown in Figure 4.6 (page 150). While many instructions follow the paradigm of operating on sources and putting the result in a destination, other instructions (such as the control instructions BAL, BALR, BC) do not follow this paradigm, but use the same fields for other purposes. The associated addressing modes are as follows.

**RR** (register-register)—Both operands are simply contents of registers. The first source operand is also the destination.

**RX** (register-indexed)—The first operand and destination are a register. The second operand is the contents of the memory location given by the sum of a 12-bit displacement field D2, the contents of the register B2, and the contents of the register X2. This format is used when an index register is needed (and for most loads and stores).

RS (register-storage)—The first operand is a register that is the destination. The third operand is a register that is used as the second source. The second operand is the contents of the memory location given by the sum of the 12-bit displacement field D2 and the contents of the register B2. RS mode differs from RX in that a 3-operand form is supported, but the index register is eliminated. This instruction format is used for only a small number of instructions.

SI (storage-immediate)—The destination is a memory operand given by the sum of the contents of register B1 and the value of displacement D1. The second operand, an 8-bit immediate field, is the source.

SS (storage-storage)—The addresses of the two memory operands are the sum of the contents of a base register Bi and a displacement Di. The first operand is the destination. This storage-to-storage operation is used for decimal operations and for character strings. The length field can specify a single length of 1 to 256, or two lengths, each from 1 to 16. A single length is used for string instructions, while decimal instructions specify a length for each operand.

The displacement in the RS, RX, SI, and SS formats is 12 bits and is unsigned.

FIGURE 4.6 The 360/370 instruction formats. The possible instruction operands are a register (R1, R2, or R3), an 8-bit immediate, or a memory location. The opcode specifies where the operands reside and the addressing mode. The effective addresses for memory operands are formed using the sum of one or two registers (called B1, B2, or X2) and a 12-bit unsigned displacement field (called D1 or D2). In addition, the storage—storage instructions, which are all string-oriented, specify an 8-bit length field. Other instruction formats have been added in later architectural extensions. These formats allowed the opcode space to be extended and new data types to be added. For loads, stores, and moves only one source operand is used and the operation only moves the data (see Figure 4.8 on page 152). For SS instructions, the length is one greater than the value in the instruction.

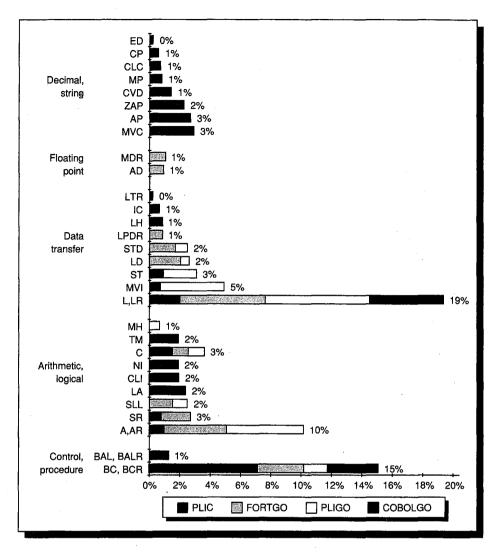

# **Operations on the 360/370**

Just as on the VAX, the instructions on the 360 can be divided into classes. Four basic types of operations on data are supported:

- 1. Logical operations on bits, character strings, and fixed words. These are mostly RR and RX formats with a few RS instructions.

- 2. Decimal or character operations on strings of characters or decimal digits. These are SS format instructions.

- 3. Fixed-point binary arithmetic. This is supported in both RR and RX formats.

- 4. Floating-point arithmetic. This is supported primarily with RR and RX instructions.

Branches use the RX instruction format with the effective address specifying the branch target. Since branches are not PC-relative, a base register may need to be loaded to specify the branch target. This has a rather substantial impact: in general, it means that there must be registers that point to every region containing a branch target. The condition codes are set by all arithmetic and logical operations. Conditional branches test the condition codes under a mask to determine whether or not to branch.

Some example instructions and their formats are shown in Figure 4.7. When an operation is defined for more than one format, separate opcodes are used to specify the instruction format. For example, the opcode AR (add register) says that the instruction type is RR; thus, the operands are in registers. The opcode A (add) says the format is RX; thus, one operand is in memory, accessed with the RX addressing mode. Figure 4.8 (page 152) has a longer listing of operations, including all the most common ones; a full table of instructions appears in Appendix B.

| Туре | Instruc | tion example     | Meaning                                                                    |

|------|---------|------------------|----------------------------------------------------------------------------|

| RR   | AR R4   | , R5 '           | R4← R4+R5                                                                  |

| RX   | A R4    | 1,10(R5,R6)      | R4← R4+M[R5+R6+10]                                                         |

| RX   | BC Ma   | ask, 20 (R5, R6) | if (CC & Mask)!=0 {PC← 20+R5+R6}                                           |

| RS   | STM 20  | (R14),R2,R8      | for(i=2;i<=8;i++)<br>{M[R14+20+(i-2)*4] ← 32 Ri}                           |

| SI   | MVI 20  | (R5),#40         | M[R5+20]← <sub>8</sub> 40                                                  |

| SS   | MVC 10  | (R2),Len,20(R6)  | for(i=0;i <len+1;i++)<br>{M[R2+10+i] \( \in \) M[R6+20+i]}</len+1;i++)<br> |

FIGURE 4.7 Typical IBM 360 instructions with their meanings. The MVC instruction is shown with the length as the second operand. The length field is a constant in the instruction; standard 360 assembly language syntax includes the length with the first operand. The variable i used in the MVC and STM is a temporary.

| Class or instruction | Format         | Instruction meaning                                                                                                  |

|----------------------|----------------|----------------------------------------------------------------------------------------------------------------------|

| Control              |                | Change the PC                                                                                                        |

| BC_<br>BAL_          | RX,RR<br>RX,RR | Test the condition and conditionally branch<br>Branch and link (address of next instruction is placed in<br>R15)     |

| Arithmetic, log      | jical          | Arithmetic and logical operations                                                                                    |

| A_                   | RX,RR          | Add                                                                                                                  |

| s_                   | RX,RR          | Subtract                                                                                                             |

| SLL                  | RS             | Shift left logical; shifts a register by an immediate amount                                                         |

| LA                   | RX             | Load address—put effective address into destination                                                                  |

| CLI                  | SI             | Compare storage byte against immediate                                                                               |

| NI                   | SI             | AND immediate into storage byte                                                                                      |

| C                    | RX,RR          | Compare and set condition codes                                                                                      |

| TM                   | RS             | Test under mask—perform a logical AND of the operand and an immediate field; set condition codes based on the result |

| MH                   | RX             | Multiply halfword                                                                                                    |

| Data transfer        |                | Moves between registers or register and memory                                                                       |

| L_                   | RX,RR          | Load a register from memory or another register                                                                      |

| MVI                  | SI             | Store an immediate byte in memory                                                                                    |

| ST                   | RX             | Store a register                                                                                                     |

| LD                   | RX             | Load a double-precision floating-point register                                                                      |

| STD                  | RX             | Store a double-precision floating-point register                                                                     |

| LPDR                 | RR             | Move a double-precision floating-point register to another                                                           |

| LH                   | RX             | Load a halfword from memory into a register                                                                          |

| IC                   | RX             | Insert a memory byte into low-order byte of a register                                                               |

| LTR                  | RR             | Load a register and set condition codes                                                                              |

| Floating point       |                | Floating-point operations                                                                                            |

| AD_                  | RX,RR          | Double-precision floating-point add                                                                                  |

| MD                   | RX,RR          | Double-precision FP multiply                                                                                         |

| Decimal, string      |                | Operations on decimal and character strings                                                                          |

| MVC                  | SS             | Move characters                                                                                                      |

| AP                   | SS             | Add packed-decimal strings, replacing first with sum                                                                 |

| ZAP                  | SS             | Zero and add packed—replace destination with source                                                                  |

| CVD                  | RX             | Convert a binary word to decimal doubleword                                                                          |

| MP                   | SS             | Multiply two packed-decimal strings                                                                                  |

| CLC                  | SS             | Compare two character strings                                                                                        |

| CP                   | SS             | Compare two packed-decimal strings                                                                                   |

| ED                   | SS             | Edit—convert packed-decimal to character string                                                                      |

**FIGURE 4.8** Most frequently used IBM 360 instructions. The underline means that the opcode is two distinct opcodes with an RX format and an RR format. For example  $\mathtt{A}$ \_ stands for  $\mathtt{AR}$  and  $\mathtt{A}$ . The full instruction set is shown in Appendix B.

# 4.4

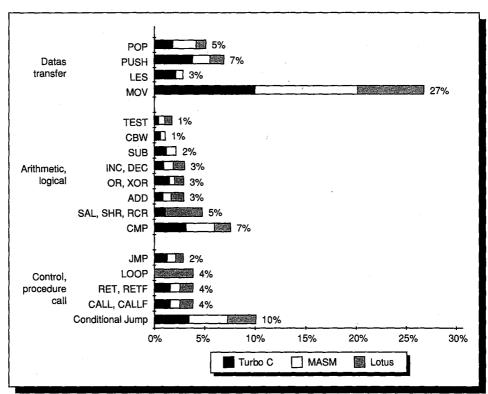

# **The 8086 Architecture**

The Intel 8086 architecture was announced in 1978 as an upward-compatible extension of the then-successful 8080. Whereas the 8080 was a straightforward accumulator machine, the 8086 extended the architecture with additional registers. The 8086 fails to be a truly general-purpose register machine, however, because nearly every register has a dedicated use. Thus, its architecture falls somewhere between an accumulator machine and a general-purpose register machine. The 8086 is a 16-bit architecture; all internal registers are 16 bits. To obtain addressability greater than 16 bits the designers added segments to the architecture. This allowed a 20-bit address space, broken into 64-KB fragments. Chapter 8 discusses segmentation in detail, while this chapter will focus only on the implications for a compiler.

The 80186, 80286, 80386, and 80486 are "compatible" extensions of the 8086 architecture and are collectively referred to as the 80x86 processors. They are compatible in the sense that they all belong to the same architectural family. There are more instances of this architectural family than of any other in the world. The 80186 added a small number of extensions (about 16) to the 8086 architecture in 1981. The 80286, introduced in 1982, extended the 80186 architecture by creating an elaborate memory-mapping and protection model and by extending the address space to 24 bits (see Chapter 8, Section 8.6). Because 8086 programs needed to be binary compatible, the 80286 offered a real addressing mode to make the machine look just like an 8086.

The 80386 was introduced in 1985. It is a true 32-bit machine when running in native mode. Like the 80286, a real addressing mode is provided for 8086 compatibility. There is also a virtual 8086 mode that provides for multiple 20-bit 8086 address partitions within the 80386's memory. In addition to a 32-bit architecture with 32-bit registers and a 32-bit address space, the 80386 has a new set of addressing modes and additional operations. The added instructions make the 80386 nearly a general-purpose register machine—for most operations any register can be used as an operand. The 80386 also provides paging support (see Chapter 8). The 80486 was introduced in 1989 and added only a few new instructions, while substantially increasing performance.

Since 8086 compatibility mode is the dominant use of all 80x86 processors, we will take a detailed look in this section at the 8086 architecture. We will begin by summarizing the architecture and then discuss its usage by typical programs.

# **8086 Instruction Set Summary**

The 8086 provides support for both 8-bit (byte) and 16-bit (called word) data types. The data type distinctions apply to register operations as well as memory accesses.

The address space on the 8086 is a total of 20 bits; however, it is broken into 64-KB segments addressable with 16-bit offsets. A 20-bit address is formed by taking a 16-bit effective address—as an offset within a segment—and adding it to a 16-bit segment base address. The segment base address is obtained by shifting the contents of a 16-bit segment register 4 bits to the left.

| Class   | Register | Purposes of class or register                                                                                                                      |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Data    |          | Used to hold and operate on data                                                                                                                   |

|         | AX       | Used for multiply, divide, and I/O; sometimes an implicit operand; AH and AL also have dedicated uses in byte multiply, divide, decimal arithmetic |

|         | BX       | Can also be used as address-base register                                                                                                          |

|         | CX       | Used for string operations and loop instructions; CL is the dynamic shift count                                                                    |

|         | DX       | Used for multiply, divide, and I/O                                                                                                                 |

| Address |          | Used to form 16-bit effective memory addresses (within segment)                                                                                    |

|         | SP       | Stack pointer                                                                                                                                      |

|         | BP       | Base register—used in based-addressing mode                                                                                                        |

|         | SI       | Index register, and also used as string source base register                                                                                       |

|         | DI       | Index register, and also used as string destination base register                                                                                  |

| Segment |          | Used to form 20-bit real memory addresses                                                                                                          |

|         | CS       | Code segment—used with instruction access                                                                                                          |

|         | SS       | Stack segment—used for stack references (SP) or when BP is base register                                                                           |

|         | DS       | Data segment—used when a reference is not for code (CS used), to the stack (SS used), or a string destination (ES used)                            |

|         | ES       | Extra segment—used when operand is string destination                                                                                              |

| Control |          | Used for status and program control                                                                                                                |

|         | IP       | Instruction pointer—provides the offset of the currently executing instruction (this is the lower 16-bits of the effective PC)                     |

|         | FLAGS    | Contains six condition code bits—carry, zero, sign, borrow, parity, and overflow—and three status control bits                                     |

**FIGURE 4.9** The 14 registers on the 8086. The table divides them into four classes that have restricted uses. In addition, many of the individual registers are required for certain instructions. The data registers have an upper and lower half: xL refers to lower byte and xH to upper byte of register x.

The 8086 provides a total of 14 registers broken into four groups—data registers, address registers, segment registers, and control registers—as shown in Figure 4.9. The segment register for a memory access is usually implied by the base register used to form the effective address within the segment.

The addressing modes for data on the 8086 use the segment registers implied by the addressing mode or specified in the instruction with an override of the default mode. We will discuss how branches and jumps deal with segmentation in the section on operations.

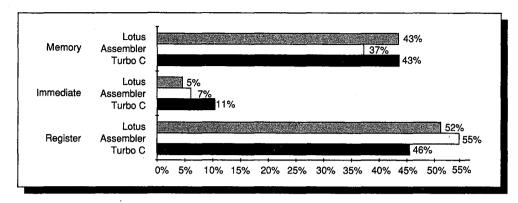

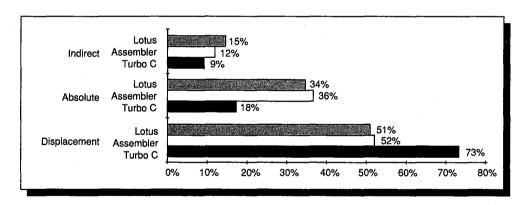

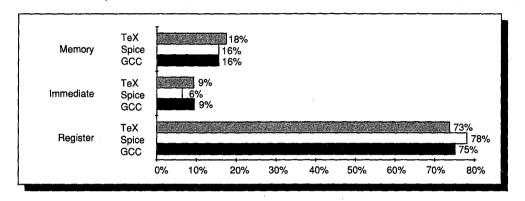

# **Addressing Modes**

Most of the addressing modes for forming the effective address of a data operand are among those discussed in Chapter 3. The arithmetic, logical, and data-transfer instructions are two-operand instructions that allow the combinations shown in Figure 4.10.

| Source/destination operand type | Second source operand |  |

|---------------------------------|-----------------------|--|

| Register                        | Register              |  |

| Register                        | Immediate             |  |

| Register                        | Memory                |  |

| Memory                          | Register              |  |

| Memory                          | Immediate             |  |

**FIGURE 4.10** Instruction types for the arithmetic, logical, and data-transfer instructions. The 8086 allows the combinations shown. Immediates may be 8 or 16 bits in length; a register is any one of the 12 major registers in Figure 4.9 (not one of the control registers). The only restriction is the absence of memory—memory mode.

The memory addressing modes supported are absolute (16-bit absolute address), register indirect, based, indexed, and based indexed with displacement (not mentioned in Chapter 3). Although a memory operand can use any addressing mode, there are restrictions on what registers can be used in a mode. The registers usable in specifying the effective address are as follows:

- Register indirect—BX, SI, DI.

- Based mode with 8-bit or 16-bit displacement—BP, BX, SI, DI. (Intel gives two names to this addressing mode, Based and Indexed, but they are essentially identical and we combine them.)

- Indexed—address is sum of two registers. The allowable combinations are BX+SI, BX+DI, BP+SI, and BP+DI. This mode is called Based Indexed on the 8086.

■ Based indexed with 8-bit or 16-bit displacement—the address is sum of displacement and contents of two registers. The same restrictions on registers apply as in indexed mode.

# **Operations on the 8086**

The 8086 operations can be divided into four major classes:

- 1. Data movement instructions, including move, push, and pop

- 2. Arithmetic and logic instructions, including logical operations, test, shifts, and integer and decimal arithmetic operations

- 3. Control flow, including conditional and unconditional branches, calls, and returns

- 4. String instructions, including string move and string compare

| Instruction     | Function                                                                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| JE name         | if equal(CC) {IP←name};<br>IP-128 ≤ name < IP+128                                                                                                  |

| JMP name        | IP←name                                                                                                                                            |

| CALLF name, seg | $SP \leftarrow SP-2$ ; $M[SS:SP] \leftarrow CS$ ; $SP \leftarrow SP-2$ ; $M[SS:SP] \leftarrow IP+5$ ; $IP \leftarrow name$ ; $CS \leftarrow seg$ ; |

| MOVW BX,[DI+45] | $BX \leftarrow_{16} M[DS:DI+45]$                                                                                                                   |

| PUSH SI         | SP←SP-2; M[SS:SP]←SI                                                                                                                               |

| POP DI          | DI←M[SS:SP]; SP←SP+2                                                                                                                               |

| ADD AX,#6765    | AX←AX+6765                                                                                                                                         |

| SHL BX,1        | BX←BX <sub>115</sub> ## 0                                                                                                                          |

| TEST DX,#42     | Set CC flags with DX & 42                                                                                                                          |

| MOVSB           | $M[ES:DI] \leftarrow_8 M[DS:SI];$                                                                                                                  |

|                 | DI←DI+1; SI←SI+1                                                                                                                                   |

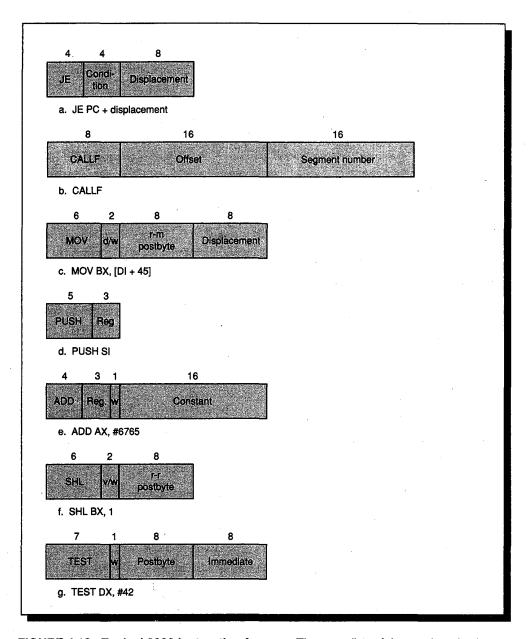

FIGURE 4.11 Some typical 8086 instructions and their functions. A list of the most frequent operations appears in Figure 4.12 (page 158). We use the abbreviation SR:X to indicate the formation of an address with segment register SR and offset X. This effective address corresponding to SR:X is (SR<<4)+X. The CALLF saves the IP of the next instruction and the current CS on the stack.

In addition, there is a repeat prefix that may precede any string instruction, which says that the instruction should be repeated using the value in the CX register for the number of repetitions. Figure 4.11 shows some typical 8086 instructions and their functions.

Control-flow instructions must be able to address destinations in another segment. This is handled by having two types of control-flow instructions: "near" for intrasegment (within a segment) and "far" for intersegment (between segments) transfers. In far jumps, which must be unconditional, two 16-bit quantities follow the opcode. One of these is used as the instruction pointer, while the other is loaded into CS and becomes the new code segment. Calls and returns work similarly—a far call pushes the return instruction pointer and return segment on the stack and loads both the instruction pointer and code segment. A far return pops both the instruction pointer and the code segment from the stack. Programmers or compiler writers must be sure to always use the same type of call and return for a procedure—a near return does not work with a far call, and vice versa.

Figure 4.12 (page 158) summarizes the most popular 8086 instructions. Many of the instructions are available in both byte and word formats. A full listing of instructions appears in Appendix B.

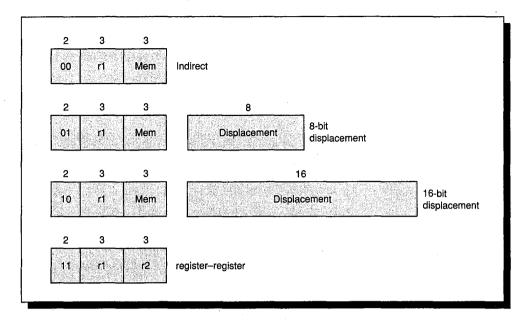

The encoding of instructions in the 8086 is complex, and there are many different instruction formats. Instructions may vary from one byte, when there are no operands, up to six bytes, when the instruction contains a 16-bit immediate and uses 16-bit displacement addressing. Figure 4.13 (page 159) shows the instruction format for several of the example instructions in Figure 4.11 (page 156). The opcode byte usually contains a bit saying whether the instruction is a word or byte instruction. For some instructions the opcode may include the addressing mode and the register; this is true in many instructions that have the form "register ← register op immediate." For other instructions a "postbyte" or extra opcode byte contains the addressing mode information. This postbyte is used for many of the instructions that address memory. The encoding of the postbyte is shown in Figure 4.14 (page 160). Finally, there is a byte prefix that is used for three different purposes. It can override the default-segment usage of instructions, and it can be used to repeat a string instruction by a count provided in CX. (This latter function is useful for string instructions that operate on a single byte or word at a time and use autoincrement addressing.) Third, it can be used to generate an atomic memory access for use in implementing synchronization.

| Instruction            | Meaning                                                                                        |

|------------------------|------------------------------------------------------------------------------------------------|

| Control                | Conditional and unconditional branches                                                         |

| JNZ, JZ                | Jump if condition to IP + 8-bit offset; JNE (for JNZ), JE (for JZ) are alternative names       |

| JMP, JMPF              | Unconditional jump—8-bit or 16-bit offset intrasegment (near), and intersegment (far) versions |

| CALL, CALLF            | Subroutine call—16-bit offset; return address pushed; near and far versions                    |

| RET, RETF              | Pops return address from stack and jumps to it; near and far versions                          |

| LOOP                   | Loop branch—decrement CX; jump to IP + 8-bit displacement if CX ≠0                             |

| Data transfer          | Move data between registers or between register and memory                                     |

| MOV                    | Move between two registers or between register and memory                                      |

| PUSH                   | Push source operand on stack                                                                   |

| POP                    | Pop operand from stack top to a register                                                       |

| LES                    | Load ES and one of the GPRs from memory                                                        |

| Arithmetic,<br>logical | Arithmetic and logical operations using the data registers and memory                          |

| ADD                    | Add source to destination; register-memory format                                              |

| SUB                    | Subtract source from destination; register-memory format                                       |

| CMP                    | Compare source and destination; register-memory format                                         |

| SHL                    | Shift left                                                                                     |

| SHR                    | Shift logical right                                                                            |

| RCR                    | Rotate right with Carry as fill                                                                |

| CBW                    | Convert byte in AL to word in AX                                                               |

| TEST                   | Logical AND of source and destination sets flags                                               |

| INC                    | Increment destination; register-memory format                                                  |

| DEC                    | Decrement destination; register-memory format                                                  |

| OR                     | Logical OR; register-memory format                                                             |

| XOR                    | Exclusive OR; register-memory format                                                           |

| String instructions    | Move between string operands; length given by a repeat prefix                                  |

| MOVS                   | Copies from string source to destination; may be repeated                                      |

| LODS                   | Loads a byte or word of a string into the A register                                           |

**FIGURE 4.12** Some typical operations on the 8086. Many operations use register—memory format, where either the source or the destination may be memory and the other may be a register or immediate operand.

FIGURE 4.13 Typical 8086 instruction formats. The encoding of the postbyte is shown in Figure 4.14. Many instructions contain the 1-bit field w, which says whether the operation is a byte or word. Fields of the form v/w or d/w are a d-field or v-field followed by the w-field. The d-field in MoV is used in instructions that may move to or from memory and shows the direction of the move. The field v in the SHL instruction indicates a variable-length shift; variable-length shifts use a register to hold the shift count. The ADD instruction shows a typical optimized short encoding usable only when the first operand is AX. Overall instructions may vary from one to six bytes in length.

**FIGURE 4.14** There are four postbyte encodings on the 8086 designated by a 2-bit tag. The first three indicate a register—memory instruction, where Mem is the base register. The fourth form is register—register.

# 4.5 The DLX Architecture

In many places throughout this book we will have occasion to refer to a computer's "machine language." The machine we use is a mythical computer called "MIX." MIX is very much like nearly every computer in existence, except that is, perhaps, nicer ... MIX is the world's first polyunsaturated computer. Like most machines, it has an identifying number—the 1009. This number was found by taking 16 actual computers which are very similar to MIX and on which MIX can be easily simulated, then averaging their number with equal weight:

$$\lfloor (360 + 650 + 709 + 7070 + U3 + SS80 + 1107 + 1604 + G20 + B220 + S2000 + 920 + 601 + H800 + PDP-4 + 11)/16 \rfloor = 1009.$$

The same number may be obtained in a simpler way by taking Roman numerals.

Donald Knuth, The Art of Computer Programming. Volume 1: Fundamental Algorithms

In this section we will describe a simple load/store architecture called DLX (pronounced "Deluxe"). The authors believe DLX to be the world's second polyunsaturated computer—the average of a number of recent experimental and commercial machines that are very similar in philosophy to DLX. Like Knuth, we derived the name of our machine from an average expressed in Roman numerals:

(AMD 29K, DECstation 3100, HP 850, IBM 801, Intel i860, MIPS M/120A, MIPS M/1000, Motorola 88K, RISC I, SGI 4D/60, SPARCstation-1, Sun-4/110, Sun-4/260) / 13 = 560 = DLX.

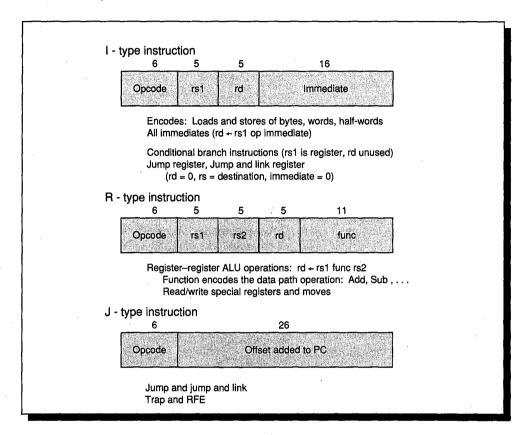

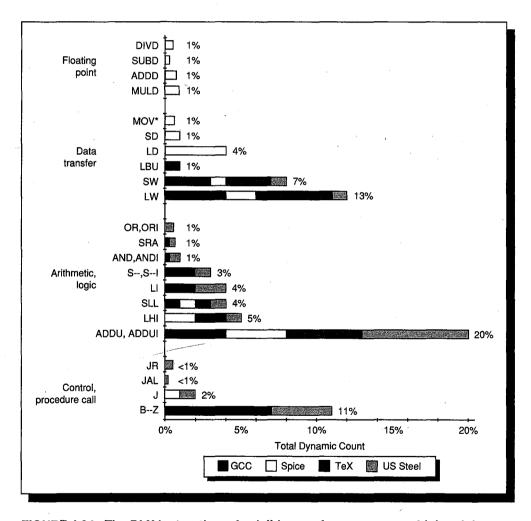

The architecture of DLX was chosen based on observations about the most frequently used primitives in programs. More sophisticated (and less performance-critical) functions are implemented in software with multiple instructions. In Section 4.9 we discuss how and why these architectures became popular.

Like most recent load/store machines, DLX emphasizes

- A simple load/store instruction set

- Design for pipelining efficiency (discussed in Chapter 6)

- An easily decoded instruction set

- Efficiency as a compiler target

DLX provides a good architectural model for study, not only because of the recent popularity of this type of machine, but also because it is an easy architecture to understand.

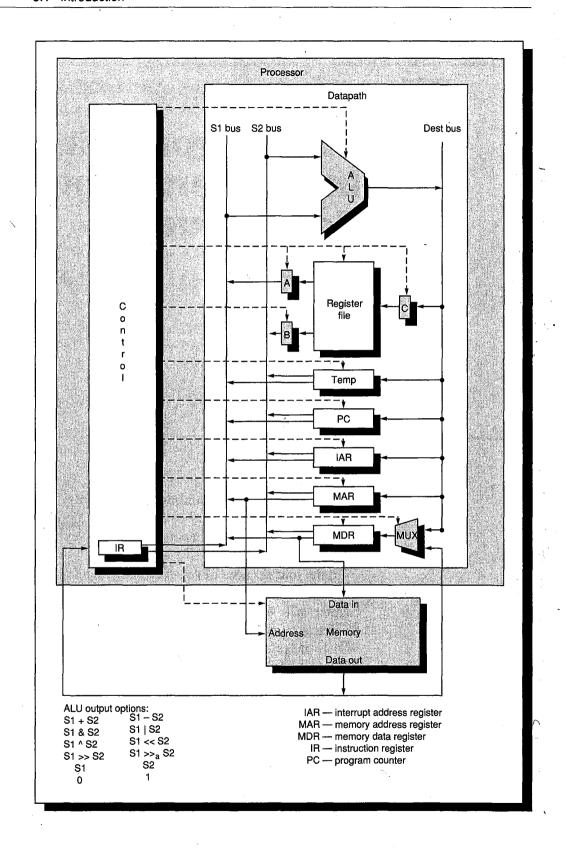

## **DLX—Our Generic Load/Store Architecture**

In this section, the DLX instruction set is defined. We will use this architecture again in Chapters 5 through 7, and it forms the basis for a number of exercises and programming projects.

■ The architecture has thirty-two 32-bit general-purpose registers (GPRs); the value of R0 is always 0. Additionally, there are a set of floating-point registers (FPRs), which can be used as 32 single-precision (32-bit) registers, or as even-odd pairs holding double-precision values. Thus, the 64-bit floating-point registers are named F0, F2, ..., F28, F30. Both single- and double-precision operations are provided. There are a set of special registers used for accessing status information. The FP status register is used for both compares and FP exceptions. All movement to/from the status register is through the GPRs; there is a branch that tests the comparison bit in the FP status register.

- Memory is byte addressable in Big Endian mode with a 32-bit address. All memory references are through loads or stores between memory and either the GPRs or the FPRs. Accesses involving the GPRs can be to a byte, to a halfword, or to a word. The FPRs may be loaded and stored with single-precision or double-precision words (using a pair of registers for DP). All memory accesses must be aligned. There are also instructions for moving between a FPR and a GPR.

- All instructions are 32 bits and must be aligned.

- There are also a few special registers that can be transferred to and from the integer registers. An example is the floating-point status register, used to hold information about the results of floating-point operations.

# **Operations**

There are four classes of instructions: loads and stores, ALU operations, branches and jumps, and floating-point operations.

| Exar | nple instruction | Instruction name       | Meaning                                                      |  |

|------|------------------|------------------------|--------------------------------------------------------------|--|

| LW   | R1,30(R2)        | Load word              | R1← <sub>32</sub> M[30+R2]                                   |  |

| LW   | R1,1000(R0)      | Load word              | R1← <sub>32</sub> M[1000+0]                                  |  |

| LB   | R1,40(R3)        | Load byte              | $R1 \leftarrow_{32} (M[40+R3]_0)^{24} \# M[40+R3]$           |  |

| LBU  | R1,40(R3)        | Load byte unsigned     | R1← <sub>32</sub> 0 <sup>24</sup> ## M[40+R3]                |  |

| LH   | R1,40(R3)        | Load halfword .        | $R1 \leftarrow_{32} (M[40+R3]_0)^{16} \#M[40+R3] \#M[41+R3]$ |  |

| LHU  | R1,40(R3)        | Load halfword unsigned | R1← <sub>32</sub> 0 <sup>16</sup> ##M[40+R3]##M[41+R3]       |  |

| LF   | F0,50(R3)        | Load float             | F0← <sub>32</sub> M[50+R3]                                   |  |

| LD   | F0,50(R2)        | Load double            | F0##F1← <sub>64</sub> M[50+R2]                               |  |

| SW   | 500 (R4),R3      | Store word             | M[500+R4]← <sub>32</sub> R3                                  |  |

| SF   | 40 (R3),F0       | Store float            | M[40+R3]← <sub>32</sub> F0                                   |  |

| SD   | 40 (R3),F0       | Store double           | $M[40+R3] \leftarrow_{32} F0; M[44+R3] \leftarrow_{32} F1$   |  |

| SH   | 502 (R2),R3      | Store half             | M[502+R2]← <sub>16</sub> R3 <sub>1631</sub>                  |  |

| SB   | 41 (R3),R2       | Store byte             | M[41+R3]← <sub>8</sub> R2 <sub>2431</sub>                    |  |

**FIGURE 4.15** The load and store instructions in DLX. All use a single addressing mode and require that the memory value be aligned. Of course, both loads and stores are available for all the data types shown.

Any of the general-purpose or floating-point registers may be loaded or stored, except that loading R0 has no effect. There is a single addressing mode, base register + 16-bit signed offset. Halfword and byte loads place the loaded object in the lower portion of the register. The upper portion of the register is filled with either the sign extension of the loaded value or zeros, depending on the opcode. Single-precision floating-point numbers occupy a single floating-point register, while double-precision values occupy a pair. Conversions between single and double precision must be done explicitly. The floating-point format is IEEE 754 (see Appendix A). Figure 4.15 gives an example of the load and store instructions. A complete list of the instructions appears in Figure 4.18 (page 165).

All ALU instructions are register-register instructions. The operations include simple arithmetic and logical operations: add, subtract, AND, OR, XOR, and shifts. Immediate forms of all these instructions, with a 16-bit sign-extended immediate, are provided. The operation LHI (load high immediate) loads the top half of a register, while setting the lower half to 0. This allows a full 32-bit constant to be built in two instructions. (We sometimes use the mnemonic LI, standing for Load Immediate, as an abbreviation for an add immediate where one of the source operands is R0; likewise, the mnemonic MOV is sometimes used for an ADD where one of the sources is R0.)

There are also compare instructions, which compare two registers  $(=,\neq,<,>,\leq,\geq)$ . If the condition is true, these instructions place a 1 in the destination register (to represent true); otherwise they place the value 0. Because these operations "set" a register they are called set-equal, set-not-equal, set-less-than, and so on. There are also immediate forms of these compares. Figure 4.16 gives some examples of the arithmetic/logical instructions.

Control is handled through a set of jumps and a set of branches. The four jump instructions are differentiated by the two ways to specify the destination address and by whether or not a link is made. Two jumps use a 26-bit signed offset added to the program counter (of the instruction sequentially following the jump) to determine the destination address; the other two jump instructions specify a register that contains the destination address. There are two flavors of jumps: plain jump, and jump and link (used for procedure calls). The latter places the return address in R31.

| Example instruction | Instruction name    | Meaning                               |  |

|---------------------|---------------------|---------------------------------------|--|

| ADD R1,R2,R3        | Add                 | R1←R2+R3                              |  |

| ADDI R1,R2,#3       | Add immediate       | R1←R2+3                               |  |

| LHI R1,#42          | Load high immediate | R1←42##0 <sup>16</sup>                |  |

| SLLI R1,R2,#5       | Shift left logical  | R1←R2<<5                              |  |

| SLT R1,R2,R3        | Set less than       | if (R2 <r3) r1←1<br="">elseR1←0</r3)> |  |

FIGURE 4.16 Examples of arithmetic/logical instructions on DLX, both with and without immediates.

| Example instruction I |          | Instruction name       | Meaning                                                                                                             |  |

|-----------------------|----------|------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| J                     | name     | Jump                   | $PC\leftarrow name; ((PC+4)-2^{25}) \le name < ((PC+4)+2^{25})$                                                     |  |

| JAL                   | name ·   | Jump and link          | R31 $\leftarrow$ PC+4; PC $\leftarrow$ name;<br>((PC+4)-2 <sup>25</sup> ) $\leq$ name $<$ ((PC+4)+2 <sup>25</sup> ) |  |

| JALR                  | R2       | Jump and link register | R31←PC+4; PC←R2                                                                                                     |  |

| JR                    | R3       | Jump register          | PC←R3                                                                                                               |  |

| BEQZ                  | R4, name | Branch equal zero      | if (R4==0) PC $\leftarrow$ name;<br>((PC+4)-2 <sup>15</sup> ) $\leq$ name $<$ ((PC+4)+2 <sup>15</sup> )             |  |

| BNEZ                  | R4, name | Branch not equal zero  | if $(R4!=0)$ PC $\leftarrow$ name;<br>$((PC+4)-2^{15}) \le name < ((PC+4)+2^{15})$                                  |  |

**FIGURE 4.17** Typical control-flow instructions in DLX. All control instructions, except jumps to an address in a register, are PC-relative. If the register operand is R0, the branch is unconditional, but the compiler will usually prefer to use a jump with a longer offset over this "unconditional branch."

All branches are conditional. The branch condition is specified by the instruction, which may test the register source for zero or nonzero; this may be a data value or the result of a compare. The branch target address is specified with a 16-bit signed offset that is added to the program counter. Figure 4.17 gives some typical branch and jump instructions.

Floating-point instructions manipulate the floating-point registers and indicate whether the operation to be performed is single or double precision. Single-precision operations can be applied to any of the registers, while double-precision operations apply only to an even-odd pair (e.g., F4, F5), which is designated by the even register number. Load and store instructions for the floating-point registers move data between the floating-point registers and memory both in single and double precision. The operations MOVF and MOVD copy a single-precision (MOVF) or double-precision (MOVD) floating-point register to another register of the same type. The operations MOVFP2I and MOVI2FP move data between a single floating-point register and an integer register; moving a double-precision value to two integer registers require two instructions. Integer multiply and divide that work on 32-bit floating-point registers are also provided, as are conversions from integer to floating point and vice versa.

The floating-point operations are add, subtract, multiply, and divide; a suffix D is used for double precision and a suffix F is used for single precision (e.g., ADDD, ADDF, SUBD, SUBF, MULTD, MULTF, DIVD, DIVF). Floating-point compares set a bit in the special floating-point status register that can be tested with a pair of branches: BFPT and BFPF, branch floating point true and branch floating point false.

Figure 4.18 contains a list of all operations and their meaning.

| Instruction type / opcode                         | Instruction meaning                                                                                                                                                                                 |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data transfers                                    | Move data between registers and memory, or between the integer and FP or special registers; only memory address mode is 16-bit displacement + contents of a GPR                                     |  |

| LB, LBU, SB                                       | Load byte, load byte unsigned, store byte                                                                                                                                                           |  |

| LH, LHU, SH                                       | Load halfword, load halfword unsigned, store halfword                                                                                                                                               |  |

| LW, SW                                            | Load word, store word (to/from integer registers)                                                                                                                                                   |  |

| LF, LD, SF, SD                                    | Load SP float, load DP float, store SP float, store DP float                                                                                                                                        |  |

| MOVI2S, MOVS2I                                    | Move from/to GPR to/from a special register                                                                                                                                                         |  |

| MOVF, MOVD                                        | Copy one floating-point register or a DP pair to another register or pair                                                                                                                           |  |

| MOVFP2I, MOVI2FP                                  | Move 32 bits from/to FP registers to/from integer registers                                                                                                                                         |  |

| Arithmetic / Logical                              | Operations on integer or logical data in GPRs; signed arithmetics trap on overflow                                                                                                                  |  |

| ADD, ADDI, ADDU, ADDUI                            | Add, add immediate (all immediates are 16 bits); signed and unsigned                                                                                                                                |  |

| SUB, SUBI, SUBU, SUBUI                            | Subtract, subtract immediate; signed and unsigned                                                                                                                                                   |  |

| MULT, MULTU, DIV, DIVU                            | Multiply and divide, signed and unsigned; operands must be floating-point registers; all operations take and yield 32-bit values                                                                    |  |

| AND, ANDI                                         | And, and immediate                                                                                                                                                                                  |  |

| OR,ORI,XOR,XORI                                   | Or, or immediate, exclusive or, exclusive or immediate                                                                                                                                              |  |

| LHI                                               | Load high immediate—loads upper half of register with immediate                                                                                                                                     |  |

| SLL, SRL, SRA, SLLI, SRLI, SRAI                   | Shifts: both immediate (SI) and variable form (S); shifts are shift left logical, right logical, right arithmetic                                                                                   |  |

| s,sI                                              | Set conditional: "" may be LT, GT, LE, GE, EQ, NE                                                                                                                                                   |  |

| Control                                           | Conditional branches and jumps; PC-relative or through register                                                                                                                                     |  |

| BEQZ, BNEZ                                        | Branch GPR equal/not equal to zero; 16-bit offset from PC+4                                                                                                                                         |  |

| BFPT, BFPF                                        | Test comparison bit in the FP status register and branch; 16-bit offset from PC+4                                                                                                                   |  |

| J, JR                                             | Jumps: 26-bit offset from PC (J) or target in register (JR)                                                                                                                                         |  |

| JAL, JALR                                         | Jump and link: save PC+4 to R31, target is PC-relative (JAL) or a register (JALR)                                                                                                                   |  |

| TRAP                                              | Transfer to operating system at a vectored address; see Chapter 5                                                                                                                                   |  |

| RFE                                               | Return to user code from an exception; restore user mode; see Chapter 5                                                                                                                             |  |

| Floating point                                    | Floating-point operations on DP and SP formats                                                                                                                                                      |  |

| ADDD, ADDF                                        | Add DP, SP numbers                                                                                                                                                                                  |  |

| SUBD, SUBF                                        | Subtract DP, SP numbers                                                                                                                                                                             |  |

| MULTD, MULTF                                      | Multiply DP, SP floating point                                                                                                                                                                      |  |

| DIVD, DIVF                                        | Divide DP, SP floating point                                                                                                                                                                        |  |

| CVTF2D, CVTF2I, CVTD2F,<br>CVTD2I, CVTI2F, CVTI2D | Convert instructions: CVT $x2y$ converts from type $x$ to type $y$ , where $x$ and $y$ are one of I (Integer), D (Double precision), or F (Single precision). Both operands are in the FP registers |  |