#### 5.1.3 Register Usage

There will be 512 registers available. The first 256 will be used for process contexts. The remaining 256 will be split between the 3 sequencers as follows: 257 – 320: 64 for RCV general processing / main loop. 321 - 384: 64 for XMT general processing / main loop. 385 – 512: 128 for  $3^{rd}$  sequencer use.

## 5.2 Receive Processing

5.2.1 Main Loop

The following is a summary of the main loop of Receive:

### forever {

while there are any Receive events { if (a new event) { if (no new context available)

ignore the event;

} call appropriate event handler to service the event; this may make a waiting process runnable or set up a new process to be run (get free context, hddr buffer, TCB buffer, set the context up).

}

while any process contexts are runable {

run them by jumping to the start/resume address;

if (process complete)

free the context;

}

}

## 5.2.2 Receive Events

The events that will be processed on a given context are:

- accept a context

- release a context command (from the host via Transmit)

- release a context request (from Transmit)

- receive a valid frame; this will actually become 2 events based on the received frame

receive an ACK, receive a segment

- receive an "invalid" frame i.e. one that causes the TCB to be flushed to the host

- · a valid ACK needs to be sent (delayed ACK timer expiry).

- There are expected to be the following sources of events:

- 1. Receive input queue: it is expected that hardware will automatically DMA arriving frames into frame buffers and queue an event into a RCV-event queue.

- 2. Timer event queue: expiration of a timer will queue an event into this queue.

- 3. Transmit sequencer queue: for requests from the transmit processor.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US 52

.. ..

For the sake of brevity the following only discusses receive-frame processing .

#### 5.2.3 Receive Details - Valid Context

The base for the receive processing done by the INIC on an existing context is the fastpath or "header prediction" code in the FreeBSD release. Thus the processing is divided into 3 parts: header validation and checksumming, TCP processing and subsequent SMB processing.

#### 5.2.3.1 Header Validation

There is considerable hardware assist here. The first step in receive processing is to dma the frame header into an SRAM header buffer. It is useful for header validation to be implemented in conjunction with this dma by scanning the data as it flies by. The following tests need to be "passed":

MAC header: destination address is our MAC address (not MC or BC too), the Ethertype is IP.

• IP header: header checksum is valid, header length = 5, IP length > header length, protocol = TCP, no fragmentation, destination IP is our IP address.

• TCP header: checksum is valid (incl. pseudo-header), header length = 5 or 8 (timestamp option), length is valid, dest port = SMB or FTP data, no

FIN/SYN/URG/PSH/RST bits set, timestamp option is valid if present, segment is in sequence, the window size did not change, this is not a retransmission, it is a pure ACK or a pure receive segment, and most important, a valid context exists. The valid-context test is non-trivial in the amount of work involved to determine it. Also note that for pure ACKs, the window-size test will be relaxed. This is because initially the output PERSIST state is to be handled on the INIC.

Many but perhaps not all of these tests will be performed in hardware - depending upon the embodiment

## 5.2.3.2 TCP Processing

Once a frame has passed the header validation tests, processing splits based on whether the frame is a pure ACK or a pure received segment.

#### 5.2.3.2.1 Pure RCV Packet

The design is to split off headers into a small header buffer and pass the aligned data in separate large buffers. Since a frame has been received, eventually some receiver process on the host will need to be informed. In the case of FTP, the frame is pure data and it is passed to the host immediately. This involves getting large buffers and dmaing the data into them, then setting the appropriate details in a small buffer that is used to notify the host. However for SMB, the INIC is performing reassembly of data when the frame consists of headers and data. So there may not yet be a complete SMB to pass to the host. In this case, a small buffer will be acquired and the header moved into it. If the received segment completes an SMB, then the procedures are pretty much as for FTP. If it does not, then the scheme is to at least move the received data (not the headers) to the host to free the INIC buffers and to save latency. The list of in-progress host buffers is maintained in the TCB and moved to the header buffer when the SMB is complete.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

The final part of pure-receive processing is to fire off the delayed ACK timer for this segment.

5.2.3.2.2 Pure ACK

Pure ACK processing implies this TCB is the sender, so there may be transmit buffers that can be returned to the host. If so, send an event to the Transmit processor (or do the processing here). If there is more output available, send an event to the transmit processor. Then appropriate actions need to be taken with the retransmission timer.

5.2.3.3 SMB Processing

The following is the format of the SMB header of an SMB frame:

0 31 NetBIOS header TYPE 4 LENGTH + FLAGS SMB header "M" "S" "B" **0xFF** COM RCLS REH ERR .... ....ERR REB / FLG Reserved Reserved Reserved Reserved TID PID UID MID VWV[] WCT . BCC Data ..... Notes (interesting fields): LENGTH 17 bit Length of SMB message (0-128K) SMB command COM WCT Count (16 bit) of parameter words in VWV[] VWV Variable number of parameter words BCC Bytes of data following Provisional Pat. App. of Alacritech, Inc. 54

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

DDG1809 .101497

ij7i

The LENGTH field of the NetBIOS header will be used to determine when a complete SMB has been received and the header buffer with appropriate details can be posted to the host.

The interesting commands are the write commands: SMBwrite (0xB), SMBwriteBraw (0x1D), SMBwriteBmpx (0x1E), SMBwriteBs (0x1F), SMBwriteclose (0x2C), SMBwriteX (0x2F), SMBwriteunlock (0x14). These are interesting because they will have data to be aligned in host memory. The point to note about these commands is that they each have a different WCT field, so that the start offset of the data depends on the command type. SMB processing will thus need to be cognizant of these types.

5.2.4 Receive Details - No Valid Context

The design here is to provide as much assist as possible. Frames will be checksummed and the TCPIP headers may be split off.

#### 5.2.5 Receive Notes

- PRU\_RCVD or the equivalent in Microsoft language: the host application has to tell the INIC when he has accepted the received data that has been queued. This is so that the INIC can update the receive window. It is an advantage for this mechanism to be efficient. This may be accomplished by piggybacking these on transmit requests (not necessarily for the same TCB).

- Keepalive Timer: for a INIC-controlled TCB, the INIC will not maintain this timer. This leaves the host with the job of determining that the TCB is still active.

- Timestamp option: it is useful to support this option in the fast path because the BSD implementation does. Also, it can be very helpful in getting a much better estimate of the round-trip time (RTT) which TCP needs to use.

- 4. Idle timer: the INIC will not maintain this timer (see Note 2 above).

- 5. Frame with no valid context: The INIC may split TCP/IP headers into a separate header buffer.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

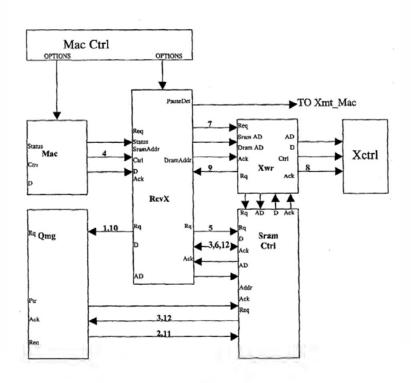

### 5.3 Transmit Processing

5.3.1 Main Loop.

The following is a summary of the main loop of Transmit:

forever {

3

| while ther | e are any Transmit events {                           |

|------------|-------------------------------------------------------|

| if         | (a new event) {                                       |

|            | if (no new context available)                         |

|            | ignore the event;                                     |

| }          | -                                                     |

| ca         | ll appropriate event handler to service the event;    |

|            | is may make a waiting process runnable or set up      |

|            | new process to be run (get free context, hddr buffer, |

|            | CB buffer, set the context up).                       |

| }          |                                                       |

| while any  | process contexts are runable {                        |

| ru         | n them by jumping to the start/resume address;        |

| if         | (process complete)                                    |

|            | free the context;                                     |

| }          |                                                       |

5.3.2 Transmit Events

The events that will be processed on a given context and their sources are:

- accept a context (from the Host).

- release a context command (from the Host).

- release a context command (from Receive).

- valid send request and window > 0 (from host or RCV sequencer).

- valid send request and window = 0 (from host or RCV sequencer).

- send a window update (host has accepted data).

- persist timer expiration (persist timer).

- context-release event e.g. window shrank (XMT processing or retransmission timer).

- receive-release request ACK( from RCV sequencer).

5.3.3 Transmit Details - Valid Context

The following is an overview of the transmit flow:

The host posts a transmit request to the INIC by filling in a command buffer with appropriate data pointers etc and posting it to the INIC via the Command Buffer Address register. Note that there is one host command buffer queue, but there are 4 physical transmit lines. So each request needs to include an interface number as well as the context number. The INIC microcode will dma the command in and place it in 1 of 4 internal command queues which the transmit sequencer will work on. This is so that transmit processing can round-robin service these 4 queues to keep all 4 interfaces busy, and not

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

let a highly-active interface lock out the others (which would happen with a single queue).

The transmit request may be a segment that is less than the MSS, or it may be as much as a full 64K SMB READ. Obviously the former request will go out as one segment, the latter as a number of MSS-sized segments. The transmitting TCB must hold on to the request until all data in it has been transmitted and acked. Appropriate pointers to do this will be kept in the TCB. A large buffer is acquired from the free buffer fifo, and the MAC and TCP/IP headers are created in it. It may be quicker/simpler to keep a basic frame header set up in the TCB and either dma directly this into the frame each time. Then data is dmad from host memory into the frame to create an MSS-sized segment. This dma also checksums the data. Then the checksum is adjusted for the pseudo-header and placed into the TCP header, and the frame is queued to the MAC transmit interface which may be controlled by the third sequencer. The final step is to update various window fields etc in the TCB. Eventually either the entire request will have been sent and acked, or a retransmission timer will expire in which case the context is flushed to the host. In either case, the INIC will place a command response in the Response queue containing the command buffer handle from the original transmit command and appropriate status. The above discussion has dealt how an actual transmit occurs. However the real challenge in the transmit processor is to determine whether it is appropriate to transmit at the time a transmit request arrives. There are many reasons not to transmit: the receiver's window size is <= 0, the Persist timer has expired, the amount to send is less than a full segment and an ACK is expected / outstanding, the receiver's window is not half-open etc. Much of the transmit processing will be in determining these conditions.

#### 5.3.4 Transmit Details - No Valid Context

The main difference between this and a context-based transmit is that the queued request here will already have the appropriate MAC and TCP/IP (or whatever) headers in the frame to be output. Also the request is guaranteed not to be greater than MSS-sized in length. So the processing is fairly simple. A large buffer is acquired and the frame is dmad into it, at which time the checksum is also calculated. If the frame is TCP/IP, the checksum will be appropriately adjusted if necessary (pseudo-header etc) and placed in the TCP header. The frame is then queued to the appropriate MAC transmit interface. Then the command is immediately responded to with appropriate status through the Response queue.

#### 5.3.5 Transmit Notes

Slow-start: the INIC will handle the slow-start algorithm that is now a part of the TCP standard. This obviates waiting until the connection is sending a full-rate before passing it to the INIC.

2. Window Probe vs Window Update: an explanation for posterity ....

A Window Probe is sent from the sending TCB to the receiving TCB, and it means the sender has the receiver in PERSIST state. Persist state is entered when the receiver advertises a zero window. It is thus the state of the transmitting TCB. In this state, he sends periodic window probes to the receiver in case an ACK from the receiver has been lost. The receiver will return his latest window size in the ACK.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

A Window Update is sent from the receiving TCB to the sending TCB, usually to tell him that the receiving window has altered. It is mostly triggered by the upper layer when it accepts some data. This probably means the sending TCB is viewing the receiving TCB as being in PERSIST state.

- 3. Persist state: it is designed to handle Persist state on the INIC. It seems unreasonable to throw a TCB back to the host just because its receiver advertised a zero window. This would normally be a transient situation, and would tend to happen mostly with clients that do not support slow-start. Alternatively, the code can easily be changed to throw the TCB back to the host as soon as a receiver advertises a zero window.

- MSS-sized frames: the INIC code will expect all transmit requests for which it has no TCB to not be greater than the MSS. If any request is, it will be dropped and an appropriate response status posted.

- 5. Silly Window avoidance: as a receiver, the INIC will do the right thing here and not advertise small windows this is easy. However it is necessary to also do things to avoid this as a sender, for the cases where a stupid client does advertise small windows. Without getting into too much detail here, the mechanism requires the INIC code to calculate the largest window advertisement ever advertised by the other end. It is an attempt to guess the size of the other end's receive buffer and assumes the other end never reduces the size of its receive buffer. See Stevens Vol. 1 pp. 325-326.

## 6 The Utility Processor

#### 6.1 Summary

The following is a summary of the main functions of the utility sequencer of the microprocessor:

look at the event queues: Event13Type & Event23Type (we assume there will be an event status bit for this - USE\_EV13 and USE\_EV23) in the events register; these are events from sequencers 1 and 2; they will mainly be XMIT requests from the XMT sequencer. Dequeue request and place the frame on the appropriate interface.

• RCV-frame support: in the model, RCV is done through VinicReceive() which is registered by the lower-edge driver, and is called at dispatch-level. This routine calls VinicTransferDataComplete() to check if the xfer (possibly DMA) of the frame into host buffers is complete. The latter rtne is also called at dispatch level on a DMA-completion interrupt. It queues complete buffers to the RCV sequencer via the normal queue mechanism.

- Other processes may also be employed here for supporting the RCV sequencer.

- service the following registers: (this will probably involve micro-interrupts) Header Buffer Address register:

buffers are 256 bytes long on 256-byte boundaries.

31-8 - physical addr in host of a set of

contiguous hddr buffers

7-0 - number of hddr buffers passed.

Use contents to add to SmallHType queue

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

261209 .101497

Data Buffer Handle & Data Buffer Address registers: buffers are 4K long aligned on 4K boundaries... Use contents to add to the FreeType queue.

Command Buffer Address register:

buffers are multiple of 32 bytes up to 1K long (2\*\*5 \* 32) 31-5 - physical addr in host of cmd buffer

4-0 - length of cmd in bytes/32

(i.e. multiples of 32 bytes)

Points to host cmd; get FreeSType buffer and move command into it; queue to Xmit0-Xmit3Type queues.

Response Buffer Address register:

buffers are 32 bytes long on 32-byte boundaries

31-8 - physical addr in host of a set of

contiguous resp buffers

7-0 - number of resp buffers passed.

Use contents to add to the ResponseType queue.

• low buffer threshold support: set approp bits in the ISR when the available-buffers count in the various queues filled by the host falls below a threshold.

#### 6.2 Further Operations of the Utility Processor

The utility processor of the microprocessor housed on the INIC is responsible for setting up and implementing all configuration space and memory mapped operations, and also as described below, for managing the debug interface.

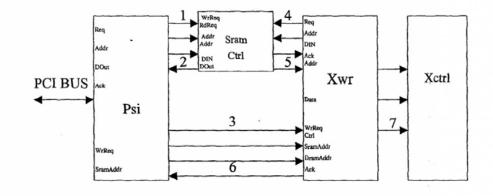

All data transfers, and other INIC initiated transfers will be done via DMA. Configuration space for both the network processor function and the utility processor function will define a single memory space for each. This memory space will define the basic communication structure for the host. In general, writing to one of these memory locations will perform a request for service from the INIC. This is detailed in the memory description for each function. This section defines much of the operation of the Host interface, but should be read in conjunction with the Host Interface Strategy for the Alacritech INIC to fully define the Host/INIC interface.

Two registers, DMA hardware and an interrupt function comprise the INIC interface to the Host through PCI. The interrupt function is implemented via a four bit register (PCI\_INT) tied to the PCI interrupt lines. This register is directly accessed by the microprocessor.

THE MICROPROCESSOR uses two registers, the PCI\_Data\_Reg and the PCI\_Address\_Reg, to enable the Host to access Configuration Space and the memory space allocated to the INIC. These registers are not available to the Host, but are used by THE MICROPROCESSOR to enable Host reads and writes. The function of these two registers is as follows.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

# PCI\_Data\_Reg

This register can be both read and written by THE MICROPROCESSOR. On write operations from the host, this register contains the data being sent from the host. On read operations, this register contains the data to be sent to the host.

#### PCI\_Address\_Reg

This is the control register for memory reads and writes from the host. The structure of the register is as follows:

| Bit 31 – | 24 Byte enable 7 – 0. Only the low order four bits are<br>valid for 32 bit addressing mode. |            |

|----------|---------------------------------------------------------------------------------------------|------------|

| Bit 23 - | 0 Memory access                                                                             |            |

|          | 1 Configuration access                                                                      |            |

| Bit 22 - | 0 Read (to Host)                                                                            |            |

|          | 1 Write (from Host)                                                                         | 42         |

| 1        | Bit 21 – 1                                                                                  | Data Valid |

| Bit 20 - | 16 Reserved                                                                                 |            |

| Bit 15 - | 0 Address                                                                                   |            |

During a write operation from the Host the PCI\_Data\_Reg contains valid data after Data Valid is set in the PCI\_Address\_Reg. Both registers are locked until THE MICROPROCESSOR writes the PCI\_Data\_Reg, which resets Data Valid.

All read operations will be direct from SRAM. Memory space based reads will return 00. Configuration space reads will be mapped as follows:

| Configuration Space 1 | SRAM Address Offset |

|-----------------------|---------------------|

| 00                    | 00                  |

| 04                    | 04                  |

| 08                    | 08                  |

| 0C                    | 0C                  |

| 10                    | 10                  |

| 3C                    | 14                  |

| Configuration Space 2 |                     |

| 00                    | 00                  |

| 04                    | 18                  |

| 3C                                                     |  |

|--------------------------------------------------------|--|

| All other reads to configuration space will return 00. |  |

08 0C

10

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US 60

08

1C 20

24

÷

## 6.2.1 CONFIGURATION SPACE

The INIC is implemented as a multi-function device. The first device is the network controller, and the second device is the debug interface. An alternative production embodiment may implement only the network controller function. Both configuration space headers will be the same, except for the differences noted in the following description.

Vendor ID – This field will contain the Alacritech Vendor ID. One field will be used for both functions. The Alacritech Vendor ID is hex 139A.

Device ID – Chosen at Alacritech on a device specific basis. One field will be used for both functions.

Command – Initialized to 00. All bits defined below as not enabled (0) will remain 0. Those that are enabled will be set to 0 or 1 depending on the state of the system. Each function (network and debug) will have its own command field.

|   | Bit $0-0$    | I/O accesses are not enabled                       |

|---|--------------|----------------------------------------------------|

|   | Bit 1 – 1    | Memory accesses are enabled                        |

|   | Bit 2 – 1    | Bus master is enabled                              |

|   | Bit 3 – 0    | Special Cycle is not enabled                       |

|   | Bit 4 – 1    | Memory Write and Invalidate is enabled             |

|   | Bit 5 – 0    | VGA palette snooping is not enabled                |

|   | Bit 6 – 1    | Parity checking is enabled                         |

|   | Bit 7 – 0    | Address data stepping is not enabled               |

|   | Bit 8 - SE   | RR# is enabled                                     |

|   | Bit 9 – 0    | Fast back to back is not enabled                   |

|   |              |                                                    |

| S | - This is no | t initialized to zero. Each function will have its |

|   |              |                                                    |

Status – This is not initialized to zero. Each function will have its own field. The configuration is as follows:

| Bit $5-1$ | 66 MHz capable is e | nabled. This bit | t will be set if the INIC |

|-----------|---------------------|------------------|---------------------------|

|-----------|---------------------|------------------|---------------------------|

Detects the system running at 66 MHz on reset

Bit 6-0 User Definable Features is not enabled

Bit 7-1 Fast Back-to-Back slave transfers enabled

Bit 8-1 Parity Error enabled - This bit is initialized to 0

Bit 9,10 - 00 - Fast device select will be set if we are at 33 MHz

01 – Medium device select will be set if we are at 66 MHz

Bit 11 - 1 Target Abort is implemented. Initialized to 0.

Bit 12-1 Target Abort is implemented. Initialized to 0.

Bit 13-1 Master Abort is implemented. Initialized to 0.

Bit 14 - 1 SERR# is implemented. Initialized to 0.

Bit 15-1 Parity error is implemented. Initialized to 0.

Revision ID - The revision field will be shared by both functions.

Class Code - This is 02 00 00 for the network controller, and for the debug interface. The field will be shared.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US 61

m

C0061809 . 101497

Cache Line Size – This is initialized to zero. Supported sizes are 16, 32, 64 and 128 bytes. This hardware register is replicated in SRAM and supported separately for each function, but THE MICROPROCESSOR will implement the value set in Configuration Space 1 (the network processor).

Latency Timer – This is initialized to zero. The function is supported. This hardware register is replicated in SRAM. Each function is supported separately, but THE MICROPROCESSOR will implement the value set in Configuration Space 1 (the network processor).

Header Type - This is set to 80 for both functions, but will be supported separately.

BIST – Is implemented. In addition to responding to a request to run self test, if test after reset fails, a code will be set in the BIST register. This will be implemented separately for each function.

Base Address Register -A single base address register is implemented for each function. It is 64 bits in length, and the bottom four bits are configured as follows:

| Bit $0 - 0$  | Indicates memory base address                       |

|--------------|-----------------------------------------------------|

| Bit 1,2 – 00 | Locate base address anywhere in 32 bit memory space |

| Bit 3 – 1    | Memory is prefetchable                              |

CardBus CIS Pointer - Not implemented-initialized to 0.

Subsystem Vendor ID - Not implemented-initialized to 0.

Subsystem ID - Not implemented-initialized to 0.

Expansion ROM Base Address - Not implemented-initialized to 0.

Interrupt Line – Implemented—initialized to 0. This is implemented separately for each function.

Interrupt Pin - This is set to 01, corresponding to INTA# for the network controller, and 02, corresponding to INTB# for the debug interface. This is implemented separately for each function.

Min\_Gnt – This can be set at a value in the range of 10, to allow reasonably long bursts on the bus. This is implemented separately for each function.

Max\_Lat – This can be set to 0 to indicate no particular requirement for frequency of access to PCI. This is implemented separately for each function.

6.2.2 MEMORY SPACE

Because each of the following functions may or may not reside in a single location, and may or may not need to be in SRAM at all, the address for each is really only used as an identifier (label). There is, therefore, no control block anywhere in memory that represents this memory space. When the host writes one of these registers, the utility

> Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

62

·· ·:

processor will construct the data required and transfer it. Reads to this memory will generate 00 for data.

6.2.2.1 Network Processor

The following four byte registers, beginning at location h00 of the network processor's allocated memory, are defined.

- 00 Interrupt Status Pointer -- Initialized by the host to point to a four byte area where status is stored

- 04 Interrupt Status Returned status from host. Sent after one or more status conditions have been reset. Also an interlock for storing any new status. Once status has been stored at the Interrupt Status Pointer location, no new status will be stored until the host writes the Interrupt Status Register. New status will be ored with any remaining uncleared status (as defined by the contents of the returned status) and stored again at the Interrupt Status Pointer location. Bits are as follows:

- Bit 31 ERR -- Error bits are set

- Bit 30 RCV Receive has occurred

- Bit 29 XMT Transmit command complete

- Bit 25 RMISS Receive drop occurred due to no buffers

- 08 Interrupt Mask Written by the host. Interrupts are masked for each of the bits in the interrupt status when the same bit in the mask register is set. When the Interrupt Mask register is written and as a result a status bit is unmasked, an interrupt is generated. Also, when the Interrupt Status Register is written, enabling new status to be stored, when it is stored if a bit is stored that is not masked by the Interrupt Mask, an interrupt is generated.

- 0C Header Buffer Address Written by host to pass a set of header buffers to the INIC.

- 10 Data Buffer Handle First register to be written by the Host to transfer a receive data buffer to the INIC. This data is Host reference data. It is not used by the INIC, it is returned with the data buffer. However, to insure integrity of the buffer, this register must be interlocked with the Data Buffer Address register. Once the Data Buffer Address register has been written, neither register can be written until after the Data Buffer Handle register has been read by THE MICROPROCESSOR.

- 14 Data Buffer Address Pointer to the data buffer being sent to the INIC by the Host. Must be interlocked with the Data Buffer Handle register.

- 18 Command Buffer Address XMT0 Pointer to a set of command buffers sent by the Host. THE MICROPROCESSOR will DMA the buffers to local DRAM found on the FreeSType queue and queue the Command

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US 63

÷

Buffer Address XMT0 with the local address replacing the host Address.

- 1C Command Buffer Address SMT1

- 20 Command Buffer Address SMT2

- 24 Command Buffer Address SMT3

- 28 Response Buffer Address -- Pointer to a set of response buffers sent by the Host. These will be treated in the same fashion as the Command Buffer Address registers.

6.2.2.2 Utility Processor

Ending status will be handled by the utility processor in the same fashion as it is handled by the network processor. At present two ending status conditions are defined B31 - command complete, and B30 - error. When end status is stored an interrupt is generated.

Two additional registers are defined, Command Pointer and Data Pointer. The Host is responsible for insuring that the Data Pointer is valid and points to sufficient memory before storing a command pointer. Storing a command pointer initiates command decode and execution by the debug processor. The Host must not modify either command or Data Pointer until ending status has been received, at which point a new command may be initiated. Memory space is write only by the Host, reads will receive 00. The format is as follows:

- 00 Interrupt Status Pointer -- Initialized by the host to point to a four byte area where status is stored

- 04 Interrupt Status Returned status from host. Sent after one or more status conditions have been reset. Also an interlock for storing any new status. Once status has been stored at the Interrupt Status Pointer location, no new status will be stored until the host writes the Interrupt Status Register. New status will be ored with any remaining uncleared status (as defined by the contents of the returned status) and stored again at the Interrupt Status Pointer location. Bits are as follows:

- Bit 31 CC Command Complete

Bit 30 - ERR -- Error

- Bit29 Transmit Processor Halted

- Bit28 Receive Processor Halted

- Bit27 Utility Processor Halted

- 08 Interrupt Mask Written by the host. Interrupts are masked for each of the bits in the interrupt status when the same bit in the mask register is set. When the Interrupt Mask register is written and as a result a status bit is unmasked, an interrupt is generated. Also,

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

when the Interrupt Status Register is written, enabling new status to be stored, when it is stored if a bit is stored that is not masked by the Interrupt Mask, an interrupt is generated.

- 0C Command Pointer Points to command to be executed. Storing this pointer initiates command decode and execution.

- 10 Data Pointer Points to the data buffer. This is used for both read and write data, determined by the command function.

## 7 Debug Interface

In order to provide a mechanism to debug the microcode running on the microprocessor sequencers, a debug process has been defined which will run on the utility sequencer. This processor will interface with a control program on the host processor over PCI.

#### 7.1 PCI Interface

This interface is defined in the combination of the Utility Processor and the Host Interface Strategy sections, above.

## 7.2 Command Format

The first byte of the command, the command byte, defines the structure of the remainder of the command. The first five bits of the command byte are the command itself. The next bit is used to specify an alternate processor, and the last two bits specify which processors are intended for the command.

#### 7.2.1 Command Byte

| 7 - 3   | 2          | 1 - 0     |

|---------|------------|-----------|

| Command | Alt. Proc. | Processor |

7.2.2 Processor Bits

00 – Any Processor

01 - Transmit Processor

10 - Receive Processor

11 - Utility Processor

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

#### 7.2.3 Alternate Processor

This bit defines which processor should handle debug processing if the utility processor is defined as the processor in debug.

0 – Transmit Processor 1 – Receive Processor

7.2.4 Single Byte Commands

00 - Halt

This command asynchronously halts the processor.

08 - Run

This command starts the processor.

10-Step

This command steps the processor.

7.2.5 Eight Byte Commands

18 - Break

0 1 2-3 4-7 Command Reserved Count Address

This command sets a stop at the specified address. A count of 1 causes the specified processor to halt the first time it executes the instruction. A count of 2 or more causes the processor to halt after that number of executions. The processor is halted just before executing the instruction. A count of 0 does not halt the processor, but causes a sync signal to be generated. If a second processor is set to the same break address, the count data from the first break request is used, and each time either processor executes the instruction the count is decremented.

20 - Reset Break

0 Command

1 - 3 Reserved 4-7 Address

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

This command resets a previously set break point at the specified address. Reset break fully resets that address. If multiple processors were set to that break point, all will be reset.

| 28 | _ | Dump   |  |

|----|---|--------|--|

|    |   | 2 unip |  |

|         |            |       |         | - 8 |

|---------|------------|-------|---------|-----|

| 0       | 1          | 2 - 3 | 4 – 7   |     |

| Command | Descriptor | Count | Address |     |

This command transfers to the host the contents of the descriptor. For descriptors larger than four bytes, a count, in four byte increments is specified. For descriptors utilizing an address the address field is specified.

7.2.6 Descriptor

00 - Register

This descriptor uses both count and address fields. Both fields are four byte based (a count of 1 transfers four bytes).

01 - Sram

This descriptor uses both count and address fields. Count is in four byte blocks. Address is in bytes, but if it is not four byte aligned, it is forced to the lower four byte aligned address.

02 – Dram

This descriptor uses both count and address fields. Count is in four byte blocks. Address is in bytes, but if it is not four byte aligned, it is forced to the lower four byte aligned address

03-Cstore

This descriptor uses both count and address fields. Count is in four byte blocks. Address is in bytes, but if it is not four byte aligned, it is forced to the lower four byte aligned address

Stand-alone descriptors:

The following descriptors do not use either the count or address fields. They transfer the contents of the referenced register.

04 - CPU\_STATUS

05 - PC

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

.

06 – ADDR\_REGA

$07 - ADDR_REGB$

08-RAM\_BASE

09-FILE\_BASE

0A-INSTR REG L

0B-INSTR\_REG\_H

0C-MAC\_DATA

0D-DMA\_EVENT

0E-MISC\_EVENT

OF-Q\_IN\_RDY

10-Q\_OUT\_RDY

11-LOCK STATUS

12-STACK - This returns 12 bytes

13 - Sense Reg

This register contains four bytes of data. If error status is posted for a command, if the next command that is issued reads this register, a code describing the error in more detail may be obtained. If any command other than a dump of this register is issued after error status, sense information will be reset.

30-Load

| 0       | 1          | 2 - 3 | 4-7     |

|---------|------------|-------|---------|

| Command | Descriptor | Count | Address |

This command transfers from the host the contents of the descriptor. For descriptors larger than four bytes, a count, in four byte increments is specified. For descriptors utilizing an address the address field is specified.

### 7.2.7 Descriptor

00 - Register

This descriptor uses both count and address fields. Both fields are four byte based.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

#### 01 - Sram

This descriptor uses both count and address fields. Count is in four byte blocks. Address is in bytes, but if it is not four byte aligned, it is forced to the lower four byte aligned address.

02 – Dram

This descriptor uses both count and address fields. Count is in four byte blocks. Address is in bytes, but if it is not four byte aligned, it is forced to the lower four byte aligned address

03 - Cstore

This descriptor uses both count and address fields. Count is in four byte blocks. Address is in bytes, but if it is not four byte aligned, it is forced to the lower four byte aligned address. This applies to WCS only.

Stand-alone descriptors:

The following descriptors do not use either the count or address fields. They transfer the contents of the referenced register.

04 -- ADDR\_REGA 05 -- ADDR\_REGB 06 -- RAM\_BASE 07 -- FILE\_BASE 08 -- MAC\_DATA 09 -- Q\_IN\_RDY 0A -- Q\_OUT\_RDY 0B -- DBG\_ADDR 38 -- Map

This command allows an instruction in ROM to be replaced by an instruction in WCS. The new instruction will be located in the Host buffer. It will be stored in the first eight bytes of the buffer, with the high bits unused. To reset a mapped out instruction, map it to location 00.

| 0       | 1-3                                       | 4-7        |

|---------|-------------------------------------------|------------|

| Command | Address to                                | Address to |

|         | Map To                                    | Map Out    |

|         | Provisional Pat. App. of Alacritech, Inc. |            |

|         | Inventors Laurence B. Boucher et al.      |            |

Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US 69

· į

# 8 HARDWARE SPECIFICATION

## FEATURES

## • Peripheral Component Interconnect (PCI) Interface

- Universal PCI interface supports both 5.0V and 3.3V signaling environments.

- Supports both 32-bit and 64 bit PCI interface.

- Supports PCI clock frequencies from 15MHz to 66MHz

- High performance bus mastering architecture.

- Host memory based communications reduce register accesses.

- Host memory based interrupt status word reduces register reads.

- Plug and Play compatible.

- PCI specification revision 2.1 compliant.

- PCI bursts up to 512 bytes.

- Supports cache line operations up to 128 bytes.

- Both big-endian and little-endian byte alignments supported.

- Supports Expansion ROM.

#### • Network Interface

- Four internal 802.3 and ethernet compliant Macs.

- Media Independent Interface (MII) supports external PHYs.

- 10BASE-T, 100BASE-TX/FX and 100BASE-T4 supported.

- Full and half-duplex modes supported.

- Automatic PHY status polling notifies system of status change.

- Provides SNMP statistics counters.

- Supports broadcast and multicast packets.

- Provides promiscuous mode for network monitoring or multiple unicast address detection.

- Supports "huge packets" up to 32KB.

- Mac-layer loop-back test mode.

- Supports auto-negotiating Phys.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

### Memory Interface

- External Dram buffering of transmit and receive packets.

- Buffering configurable as 4MB, 8MB, 16MB or 32MB.

- 32-bit interface supports throughput of 224MB/s

- Supports external FLASH ROM up to 4 MB, for diskless boot applications.

- Supports external serial EEPROM for custom configuration and Mac addresses.

## Protocol Processor

- High speed, custom, 32-bit processor executes 66 million instructions per second.

- Processes IP, TCP and NETBIOS protocols.

- Supports up to 256 resident TCP/IP contexts.

- Writable control store (WCS) allows field updates for feature enhancements.

#### • Power

- 3.3V chip operation.

- PCI controlled 5.0V/3.3V I/O cell operation.

#### Packaging

- 272-pin plastic ball grid array.

- 91 PCI signals.

- 68 MII signals.

- 58 external memory signals.

- 1 clock signal.

- 54 signals split between power and ground.

- 272 total pins.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

#### GENERAL DESCRIPTION

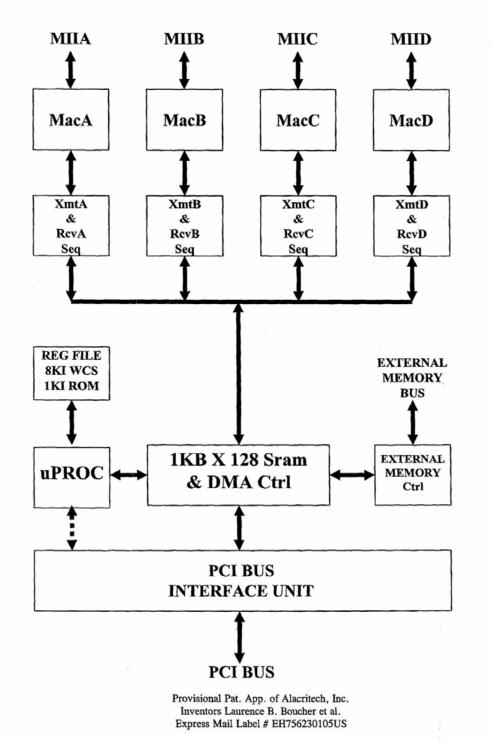

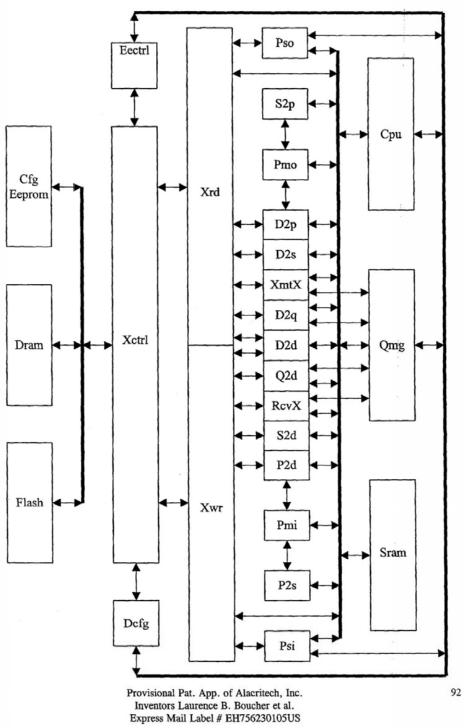

The microprocessor is a 32-bit, full-duplex, four channel, 10/100-Megabit per second (Mbps), Intelligent Network Interface Controller, designed to provide high-speed protocol processing for server applications. It combines the functions of a standard network interface controller and a protocol processor within a single chip. Although designed specifically for server applications, The microprocessor can be used by PCs, workstations and routers or anywhere that TCP/IP protocols are being utilized.

When combined with four 802.3/MII compliant Phys and Synchronous Dram (SDram), the INIC comprises four complete ethernet nodes. It contains four 802.3/ethernet compliant Macs, a PCI Bus Interface Unit (BIU), a memory controller, transmit fifos, receive fifos and a custom TCP/IP/NETBIOS protocol processor. The INIC supports 10Base-T , 100Base-TX, 100Base-FX and 100Base-T4 via the MII interface attachment of appropriate Phys.

The INIC Macs provide statistical information that may be used for SNMP. The Macs operate in promiscuous mode allowing the INIC to function as a network monitor, receive broadcast and multicast packets and implement multiple Mac addresses for each node.

Any 802.3/MII compliant PHY can be utilized, allowing the INIC to support 10BASE-T, 10BASE-T2, 100BASE-TX, 100BASE-TX and 100BASE-T4 as well as future interface standards. PHY identification and initialization is accomplished through host driver initialization routines. PHY status registers can be polled continuously by the INIC and detected PHY status changes reported to the host driver. The Mac can be configured to support a maximum frame size of 1518 bytes or 32768 bytes.

The 64-bit, multiplexed BIU provides a direct interface to the PCI bus for both slave and master functions. The INIC is capable of operating in either a 64-bit or 32-bit PCI environment, while supporting 64-bit addressing in either configuration. PCI bus frequencies up to 66MHz are supported yielding instantaneous bus transfer rates of 533MB/s. Both 5.0V and 3.3V signaling environments can be utilized by the INIC. Configurable cache-line size up to 256B will accommodate future architectures, and Expansion ROM/Flash support allows for diskless system booting. Non-PC applications are supported via programmable big and little endian modes. Host based communication has been utilized to provide the best system performance possible.

The INIC supports Plug-N-Play auto-configuration through the PCI configuration space. External pull-up and pull-down resistors, on the memory I/O pins, allow selection of various features during chip reset. Support of an external eeprom allows for local storage of configuration information such as Mac addresses.

External SDram provides frame buffering, which is configurable as 4MB, 8MB, 16MB or 32MB using the appropriate SIMMs. Use of -10 speed grades yields an external buffer bandwidth of 224MB/s. The buffer provides temporary storage of both incoming and outgoing frames. The protocol processor accesses the frames within the buffer in order to implement TCP/IP and NETBIOS. Incoming frames are processed, assembled then transferred to host memory under the control of the protocol processor. For transmit, data is moved from host memory to buffers where various headers are created before being transmitted out via the Mac.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

BLOCK DIAGRAM

73

÷, ÷

$\frac{1}{2}$

# • Cores/Cells

LSI Logic Ethernet-110 Core, 100Base & 10Base Mac with MII interface. LSI Logic single port Sram, triple port Sram and ROM available. LSI Logic PCI 66MHz, 5V compatible I/O cell. LSI Logic PLL

# • Die Size / Pin Count

LSI Logic G10 process.

| MODULE                   | DESCR                             | SPEED                                   |   | AREA                  |  |

|--------------------------|-----------------------------------|-----------------------------------------|---|-----------------------|--|

| Scratch RAM,             | 1Kx128 sport,                     | 4.37 ns nom.,                           |   | 06.77 mm <sup>2</sup> |  |

| WCS,                     | 8Kx49 sport,                      | 6.40 ns nom.,                           |   | 18.29 mm <sup>2</sup> |  |

| MAP,                     | 128x7 sport,                      | 3.50 ns nom.,                           |   | 00.24 mm <sup>2</sup> |  |

| ROM,                     | 1Kx49 32col,                      | 5.00 ns nom.,                           |   | 00.45 mm <sup>2</sup> |  |

| REGs,                    | 512x32 tport,                     | 6.10 ns nom.,                           |   | 03.49 mm <sup>2</sup> |  |

| Macs,                    | $.75 \text{ mm}^2 \text{ x } 4 =$ |                                         |   | 03.30 mm <sup>2</sup> |  |

| PLL,                     | .5 mm² ≈                          |                                         |   | $00.55 \text{ mm}^2$  |  |

| MISC LOGIC,              | 117,260 gates /                   | $(5035 \text{ gates } / \text{mm}^2) =$ |   | 23.29 mm <sup>2</sup> |  |

| TOTAL CORE               |                                   |                                         |   | 56.22 mm <sup>2</sup> |  |

|                          |                                   |                                         |   |                       |  |

| (Core side) <sup>2</sup> |                                   |                                         | = | 56.22 mm <sup>2</sup> |  |

| Core side                |                                   |                                         | = | 07.50 mm              |  |

| Die side                 | = core side +                     | 1.0 mm (I/O cells)                      | = | 08.50 mm              |  |

| Die area                 | = 8.5  mm x 8.                    | 5 mm                                    | = | 72.25 mm <sup>2</sup> |  |

|                          |                                   |                                         |   |                       |  |

| Pads needed              | = 220 signals >                   | x 1.25 (vss, vdd)                       | = | 275 pins              |  |

| LSI PBGA                 |                                   |                                         | = | 272 pins              |  |

|                          |                                   |                                         |   |                       |  |

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

# • Datapath Bandwidth

| (10MB/s/100Base) x 2 (full duplex) x 4 connections                                                     | 2  | 80 MB/s            |

|--------------------------------------------------------------------------------------------------------|----|--------------------|

| Average frame size                                                                                     | =  | 512 B              |

| Frame rate = $80MB/s / 512B$                                                                           | 11 | 156,250 frames / s |

| Cpu overhead / frame = (256 B context read) + (64B header read)<br>(128B context write) + (128B misc.) | +  | 512B / frame       |

| Total bandwidth = $(512B \text{ in}) + (512B \text{ out}) + (512B \text{ Cpu})$                        | =  | 1536B / frame      |

| Dram Bandwidth required = (1536B/frame) x (156,250 frames/s)                                           | =  | 240MB/s            |

| Dram Bandwidth @ 60MHz = (32 bytes / 167ns)                                                            | =  | 202MB/s            |

| Dram Bandwidth @ 66MHz = (32 bytes / 150ns)                                                            | =  | 224MB/s            |

| PCI Bandwidth required                                                                                 | =  | 80MB/s             |

| PCI Bandwidth available @ 30 MHz, 32b, average                                                         | =  | 46MB/s             |

| PCI Bandwidth available @ 33 MHz, 32b, average                                                         | -  | 50MB/s             |

| PCI Bandwidth available @ 60 MHz, 32b, average                                                         | =  | 92MB/s             |

| PCI Bandwidth available @ 66 MHz, 32b, average                                                         | =  | 100MB/s            |

| PCI Bandwidth available @ 30 MHz, 64b, average                                                         | =  | 92MB/s             |

| PCI Bandwidth available @ 33 MHz, 64b, average                                                         | =  | 100MB/s            |

| PCI Bandwidth available @ 60 MHz, 64b, average                                                         | =  | 184MB/s            |

| PCI Bandwidth available @ 66 MHz, 64b, average                                                         | =  | 200MB/s            |

|                                                                                                        |    |                    |

# • Cpu Bandwidth

| Receive frame interval = 512B / 40MB/s =                           | 12.8us  |                  |

|--------------------------------------------------------------------|---------|------------------|

| Instructions / frame @ 60MHz = (12.8us/frame) / (50ns/instruction) | =       | 256              |

| instructions/frame                                                 |         |                  |

| Instructions / frame @ 66MHz = (12.8us/frame) / (45ns/instruction) | =       | 284              |

| instructions/frame                                                 |         |                  |

| Required instructions / frame (per Clive) =                        | 250 in: | structions/frame |

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

75

÷

#### • Performance Features

- 512 registers improve performance through reduced scratch ram accesses and reduced instructions.

- Register windowing eliminates context-switching overhead.

- Separate instruction and data paths eliminate memory contention.

- Totally resident control store eliminates stalling during instruction fetch.

- Multiple logical processors eliminate context switching and improve real-time response.

- Pipelined architecture increases operating frequency.

- Shared register and scratch ram improve inter-processor communication.

- Fly-by state-Machine assists address compare and checksum calculation.

- TCP/IP-context caching reduces latency.

- Hardware implemented queues reduce Cpu overhead and latency.

- Horizontal microcode greatly improves instruction efficiency.

- Automatic frame DMA and status between Mac and dram buffer.

- Deterministic architecture coupled with context switching eliminates processor stalls.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

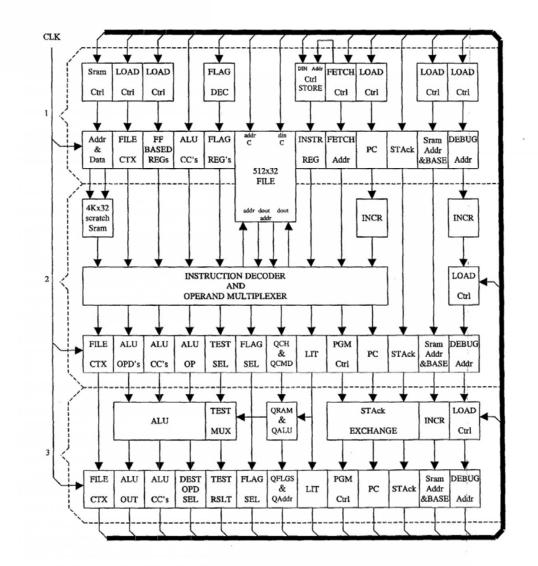

## PROCESSOR

The processor is a convenient means to provide a programmable state-machine which is capable of processing incoming frames, processing host commands, directing network traffic and directing PCI bus traffic. Three processors are implemented using shared hardware in a three-level pipelined architecture which launches and completes a single instruction for every clock cycle. The instructions are executed in three distinct phases corresponding to each of the pipeline stages where each phase is responsible for a different function.

The first instruction phase writes the instruction results of the last instruction to the destination operand, modifies the program counter (Pc), selects the address source for the instruction to fetch, then fetches the instruction from the control store. The fetched instruction is then stored in the instruction register at the end of the clock cycle.

The processor instructions reside in the on-chip control-store, which is implemented as a mixture of ROM and Sram. The ROM contains 1K instructions starting at address 0x0000 and aliases each 0x0400 locations throughout the first 0x8000 of instruction space. The Sram (WCS) will hold up to 0x2000 instructions starting at address 0x8000 and aliasing each 0x2000 locations throughout the last 0x8000 of instruction space. The ROM and Sram are both 49-bits wide accounting for bits [48:0] of the instruction microword. A separate mapping ram provides bits [55:49] of the microword (MapAddr) to allow replacement of faulty ROM based instructions. The mapping ram has a configuration of 128x7 which is insufficient to allow a separate map address for each of the 1K ROM locations. To allow re-mapping of the entire 1K ROM space, the map ram address lines are connected to the address bits Fetch[9:3]. The result is that the ROM is re-mapped in blocks of 8 contiguous locations.

The second instruction phase decodes the instruction which was stored in the instruction register. It is at this point that the map address is checked for a non-zero value which will cause the decoder to force a Jmp instruction to the map address. If a non-zero value is detected then the decoder selects the source operands for the Alu operation based on the values of the OpdASel, OpdBSel and AluOp fields. These operands are then stored in the decode register at the end of the clock cycle. Operands may originate from File, Sram, or flip-flop based registers. The second instruction phase is also where the results of the previous instruction are written to the Sram.

The third instruction phase is when the actual Alu operation is performed, the test condition is selected and the Stack push and pop are implemented. Results of the Alu operation are stored in the results register at the end of the clock cycle.

Following is a block diagram which shows the hardware functions associated with each of the instruction phases. Note that various functions have been distributed across the three phases of the instruction execution in order to minimize the combinatorial delays within any given phase.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

44

#### INSTRUCTION SET

The micro-instructions are divided into six types according to the program control directive. The microinstruction is further divided into sub-fields for which the definitions are dependent upon the instruction type. The six instruction types are listed below.

#### INSTRUCTION-WORD FORMAT

| TYPE | _[55:49]  | [48:47] | [46:42]  | [41:33]       | [32:24]      | [23:16] | [15:00] |

|------|-----------|---------|----------|---------------|--------------|---------|---------|

| Jcc  | 00000000  | 0b00,   | AluOp,   | OpdASel,      | OpdBSel,     | TstSel, | Literal |

| Jmp  | 0b0000000 | 0b01,   | AluOp,   | OpdASel,      | OpdBSel,     | FlgSel, | Literal |

| Jsr  | 060000000 | 0b10,   | AluOp,   | OpdASel,      | OpdBSel,     | FlgSel, | Literal |

| Rts  | 0b0000000 | 0b11,   | AluOp,   | OpdASel,      | OpdBSel,     | ohff,   | Literal |

| Nxt  | 0b0000000 | 0b11,   | AluOp,   | OpdASel,      | OpdBSel,     | FlgSel, | Literal |

| Map  | MapAddr   | ObXX,   | ObXXXXX, | OBXXXXXXXXXX, | ObXXXXXXXXX, | OhXX,   | 0hXXXX  |

All instructions include the Alu operation (AluOp), operand "A" select (OpdASel), operand "B" select (OpdBSel) and Literal fields. Other field usage depends upon the instruction type.

The "jump condition code" (Jcc) instruction causes the program counter to be altered if the condition selected by the "test select" (TstSel) field is asserted. The new program counter (Pc) value is loaded from either the Literal field or the AluOut as described in the following section and the Literal field may be used as a source for the Alu or the ram address if the new Pc value is sourced by the Alu.

The "jump" (Jmp) instruction causes the program counter to be altered unconditionally. The new program counter (Pc) value is loaded from either the Literal field or the AluOut as described in the following section. The format allows instruction bits 23:16 to be used to perform a flag operation and the Literal field may be used as a source for the Alu or the ram address if the new Pc value is sourced by the Alu.

The "jump subroutine" (Jsr) instruction causes the program counter to be altered unconditionally. The new program counter (Pc) value is loaded from either the Literal field or the AluOut as described in the following section. The old program counter value is stored on the top location of the Pc-Stack which is implemented as a LIFO memory. The format allows instruction bits 23:16 to be used to perform a flag operation and the Literal field may be used as a source for the Alu or the ram address if the new Pc value is sourced by the Alu.

The "Nxt" (Nxt) instruction causes the program counter to increment. The format allows instruction bits 23:16 to be used to perform a flag operation and the Literal field may be used as a source for the Alu or the ram address.

The "return from subroutine" (Rts) instruction is a special form of the Nxt instruction in which the "flag operation" (FlgSel) field is set to a value of 0hff. The current Pc value is replaced with the last value stored in the stack. The Literal field may be used as a source for the Alu or the ram address.

The Map instruction is provided to allow replacement of instructions which have been stored in ROM and is implemented any time the "map enable" (MapEn) bit has been set and the content of the "map address" (MapAddr) field is non-zero. The instruction decoder forces a jump instruction with the Alu operation and destination fields set to pass the MapAddr field to the program control block.

The program control is determined by a combination of **PgmCtrl**, **DstOpd**, **FlgSel** and **TstSe**l. The behavior of the program control is defined with the following "C-like" description.

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

#### SEQUENCER BEHAVIOR

```

if (MapEn & (MapAddr != 0b0000000)) {

//re-map instr

Stackc = Stackc;

StackB = StackB;

StackA = StackA;

InstrAddr = 0h8000 | Pc[2:0] | (MapAddr << 3);</pre>

Pc = InstrAddr + (Execute & -DbgMd);

Fetch = DbgMd ? DbgAddr:InstrAddr;

DbgAddr = DbgAddr + (Execute & DbgMd); }

else if (PgmCtrl == Jcc) {

//conditional jump

Stackc = Stackc;

StackB = StackB;

StackA = StackA;

InstrAddr = -Tst@TstSel ? Pc: (AluDst==Pc) ? AluOut:Literal;

Pc = InstrAddr + (Execute & ~DbgMd)

Fetch = DbgMd ? DbgAddr:InstrAddr;

DbgAddr = DbgAddr + (Execute & DbgMd); }

else if (PgmCtrl == Jmp) {

//jump

Stackc = Stackc;

StackB = StackB;

StackA = StackA;

InstrAddr = (AluDst == Pc) ? AluOut:Literal;

Pc = InstrAddr + (Execute & ~DbgMd)

Fetch = DbgMd ? DbgAddr:InstrAddr;

DbgAddr = DbgAddr + (Execute & DbgMd);}

else if (PgmCtrl == Jsr) {

//jump subroutine

Stackc = StackB;

StackB = StackA;

StackA = Pc;

InstrAddr = (AluDst == Pc) ? AluOut:Literal;

Pc = InstrAddr + (Execute & ~DbgMd)

Fetch = DbgMd ? DbgAddr:InstrAddr;

DbgAddr = DbgAddr + (Execute & DbgMd); }

else if (FlgSel == Rts) {

//return subroutine

InstrAddr = StackA;

StackA = StackB;

StackB = Stackc;

Stackc = ErrVec;

Pc = InstrAddr + (Execute & ~DbgMd)

Fetch = DbgMd ? DbgAddr:InstrAddr;

DbgAddr = DbgAddr + (Execute & DbgMd); }

else

{

InstrAddr = Pc;

//continue

StackA = StackA;

StackB = StackB;

Stackc = Stackc;

Pc = InstrAddr + (Execute & ~DbgMd)

Fetch = DbgMd ? DbgAddr:InstrAddr;

DbgAddr = DbgAddr + (Execute & DbgMd); }

```

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US 80

### ALU OPERATIONS

| AluOp   | OPERATION                                                                                                           | _                 |

|---------|---------------------------------------------------------------------------------------------------------------------|-------------------|

| 000000  | $A = (A \& \sim (1 << B));$<br>C = 0; V = (B >= 32) ? 1:0;                                                          | //bit clear       |

| 0b00001 | A = (A & B);<br>C = 0; V = 0;                                                                                       | //logical and     |

| 0b00010 | A = (Literal & B);<br>C = 0; V = 0;                                                                                 | //logical and     |

| 0b00011 | A = (-Literal & B);<br>C = 0; V = 0;                                                                                | //logical and not |

| 0600100 | A = (A   (1 << B));<br>C = 0; V = (B >= 32) ? 1:0;                                                                  | //bit set         |

| 0600101 | A = (A   B);<br>C = 0; V = 0;                                                                                       | //logical or      |

| 0b00110 | A = (Literal   B);<br>C = 0; V = 0;                                                                                 | //logical or      |

| 0b00111 | A = (-Literal   B);<br>C = 0; V = 0;                                                                                | //logical or not  |

| 0b01000 | for (i=31; i>=0; i) if B[i] continue; A=i;<br>C = 0; V = (B) ? 0:1;                                                 | //priority enc    |

| 0b01001 | $ \mathbf{A} = (\mathbf{A} ^{\mathbf{A}} \mathbf{B}); \\ \mathbf{C} = 0;  \mathbf{V} = 0; $                         | //logical xor     |

| 0b01010 | $A = ({Literal} ^ B);$<br>C = 0; V = 0;                                                                             | //logical xor     |

| 0b01011 | $A = ({-Literal} ^ B);$<br>C = 0; V = 0;                                                                            | //logical xor not |

| 0b01100 | $    \mathbf{A} = \mathbf{B}; \\ \mathbf{C} = 0; \ \mathbf{V} = 0; $                                                | //move            |

| 0b01101 | <b>A</b> = <b>B</b> [31:24] ^ <b>B</b> [23:16] ^ <b>B</b> [15:08] ^ <b>B</b> [07:00]<br><b>C</b> = 0; <b>V</b> = 0; | ;//hash           |

| 0601110 | <pre>A = {B[23:16],B[31:24],B[07:00],B[15:08]};<br/>C = 0; V = 0;</pre>                                             | //swap bytes      |

| 0b01111 | $A = \{B[15:00], B[31:16]\}; C = 0; V = 0;$                                                                         | //swap doublets   |

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

81

SCOELSOS LICITAL

1

÷

| AluOp   | FUNCTION                                                                          | _               |

|---------|-----------------------------------------------------------------------------------|-----------------|

| 0b10000 | A = (A + B);<br>C = (A + B)[32]; V = 0;                                           | //add B         |

| 0b10001 | A = (A + B + C);<br>C = (A + B + C) [32]; V = 0;                                  | //add B, carry  |

| 0b10010 | <pre>A = (Literal + B);<br/>C = (Literal + B)[32]; V = 0;</pre>                   | //add constant  |

| 0b10011 | A = (-Literal + B);<br>C = (-Literal + B)[32]; V = 0;                             | //sub constant  |

| 0b10100 | A = (A - B);<br>C = (A - B)[32]; V = 0;                                           | //sub B         |

| 0b10101 |                                                                                   | //sub B, borrow |

| 0b10110 | A = (-A + B);<br>C = (-A + B)[32]; V = 0;                                         | //sub A         |

| 0b10111 |                                                                                   | //sub A, borrow |

| 0b11000 | A = (A << B);<br>C = A[31]; V = (B >= 32) ? 0:1;                                  | //shift left A  |

| 0b11001 | <pre>A = (B &lt;&lt; Literal);<br/>C = B[31]; V = (Literal &gt;= 32) ? 0:1;</pre> | //shift left B  |

| 0b11010 | A = (B << 1);<br>C = B[31]; V = 0;                                                | //shift left B  |

| 0b11011 | n = (A - B);<br>C = (A - B) [32]; V = 0;                                          | //compare       |

| 0b11100 | A = (A >> B);<br>C = A[0]; V = (B >= 32) ? 1:0;                                   | //shift right A |

| 0b11101 | <pre>A = (B &gt;&gt; Literal);<br/>C = A[0]; V = (Literal &gt;= 32) ? 1:0;</pre>  | //shift right B |

| 0b11110 | A = (B >> 1);<br>C = A[0]; V = 0;                                                 | //shift right B |

| 0b11111 | n = (B - A);<br>C = (B - A)[32]; V = 0;                                           | //compare       |

Provisional Pat. App. of Alacritech, Inc. Inventors Laurence B. Boucher et al. Express Mail Label # EH756230105US

82

• ;

| OpdSel      | SELECTED C                                                                                                                                                                   | PERANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0b0000aaaaa | File                                                                                                                                                                         | <pre>File@(OpdSel[4:0]   FileBase); Allows paged access to any part of the register file.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0b0001aaaaa | CpuReg                                                                                                                                                                       | <pre>File@{2'b11, CpuId, OpdSel[4:0]}; Allows direct access to Cpu specific registers.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0b001XXXXXX | reserved                                                                                                                                                                     | Reserved for future expansion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 050100000XX | CpuStatus                                                                                                                                                                    | Ob000000000000BHD00000000000000CC<br>This is a read-only register providing information about the Cpu executing<br>(OpdSel[1:0]) cycles after the current cycle. "CC" represents a value<br>indicating the Cpu. Currently, only CpuId values of 0, 1 and 2 are returned.<br>"H" represents the current state of HIt, "D" indicates DbgMd and "B"<br>indicates BigMd. Writing this register has no effect.                                                                                                                                                                                               |

| 0b0100001XX | reserved                                                                                                                                                                     | Reserved for future expansion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0b0100010XX | Рс                                                                                                                                                                           | 0x0000AAAA<br>Writing to this address causes the program control logic to use AluOut as the<br>new Pc value in the event of a Jmp, Jcc or Jsr instruction for the Cpu<br>executing during the current cycle. If the current instruction is Nxt, Map, or<br>Rts, the register write has no effect. Reading this register returns the value in<br>Pc for the Cpu executing (OpdSel[1:0]) cycles after the current cycle.                                                                                                                                                                                  |

| 0b0100011XX | DbgAddr                                                                                                                                                                      | 0xD000AAAA<br>Writing to this register alters the contents of the debug address register<br>(DbgAddr) for the Cpu executing (OpdSel[1:0]) cycles after the current<br>cycle. DbgAddr provides the fetch address for the control-store when<br>DbgMd has been selected and the Cpu is executing. DbgAddr is also used<br>as the control-store address when performing a WrWcs@DbgAddr or<br>RdWcs@DbgAddr operation. "D" represents bit 31 of the register. It is a general<br>purpose flag that is used for event indication during simulation. Reading this<br>register returns a value of 0x00000000. |

| 0b01001XXXX | reserved                                                                                                                                                                     | Reserved for future expansion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 06010100000 | RamAddr = A                                                                                                                                                                  | ICCC, 0x000, 0b1, AAAA}<br>luOut[15] ? AluOut : (AluOut   RamBase);<br>luOut[31] ? CCC : AluCC;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |