## Intel Corp. v. Alacritech, Inc. IPR2018-00226, -00234, -00401

March 4, 2019

## **Demonstratives:** Table of Contents

### (1) 948 Patent (IPR2018-00234)

| 1.                             | A POSA would have been motivated to combine Thia and Tanenbaum96 (and Stevens2)                 | Slides 7-34   |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------|---------------|--|--|

| 2.                             | The prior art combinations disclose the limitations of the challenged claims of the 948 Patent  | Slides 35-62  |  |  |

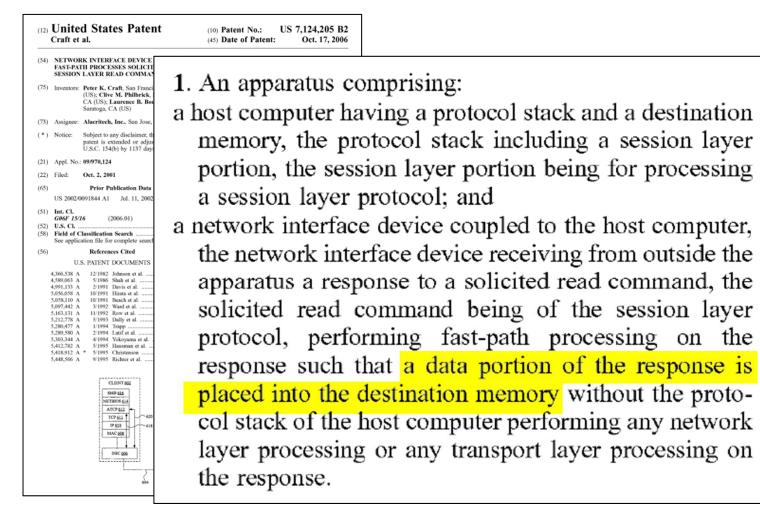

| (2) 205 Patent (IPR2018-00226) |                                                                                                 |               |  |  |

| 1.                             | Thia is enabling prior art                                                                      | Slides 67-71  |  |  |

| 2.                             | Thia teaches the network interface device performing all network and transport layer processing | Slides 72-89  |  |  |

| 3.                             | A POSA would have been motivated to combine Thia and SMB                                        | Slides 90-98  |  |  |

| 4.                             | Motion to Amend 205 Patent should be denied                                                     | Slides 99-112 |  |  |

### **Demonstratives: Table of Contents**

### (3) 699 Patent (IPR2018-00401)

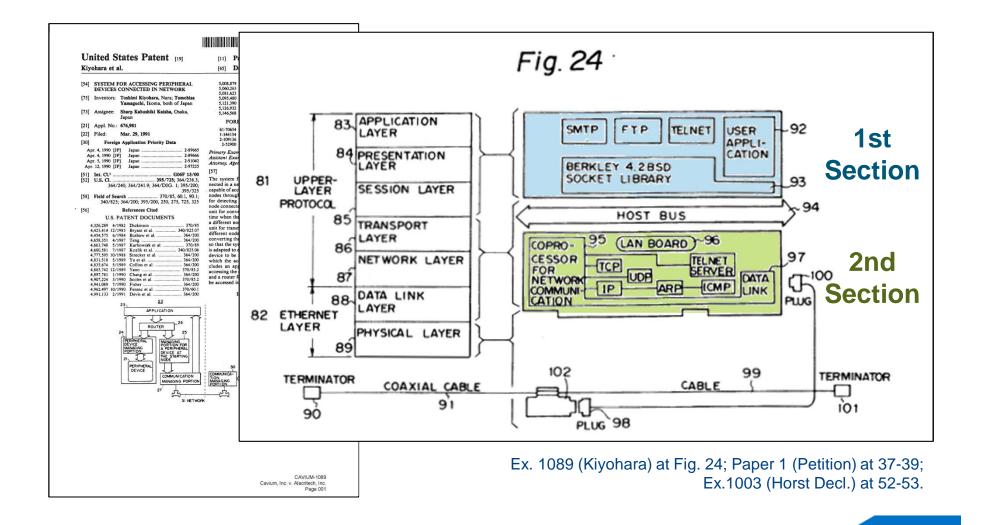

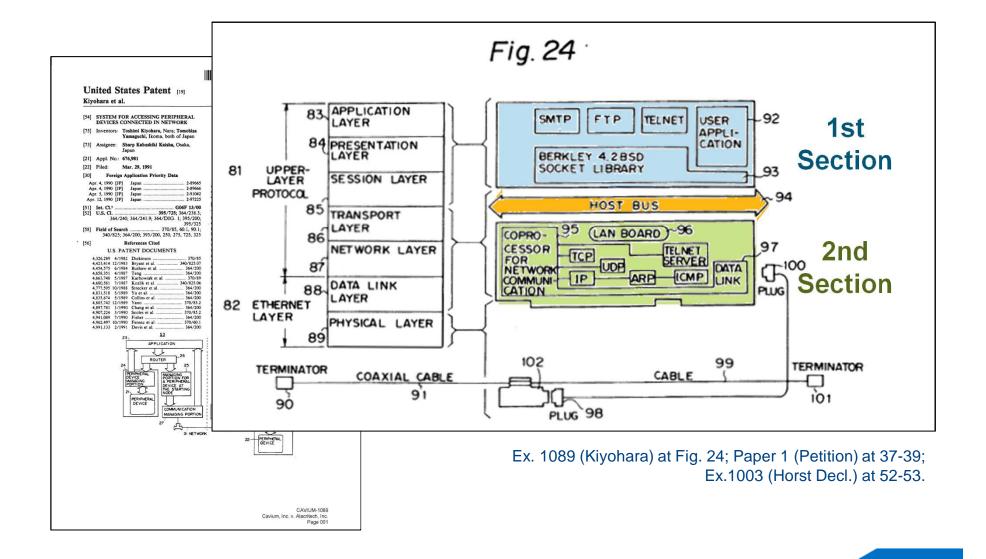

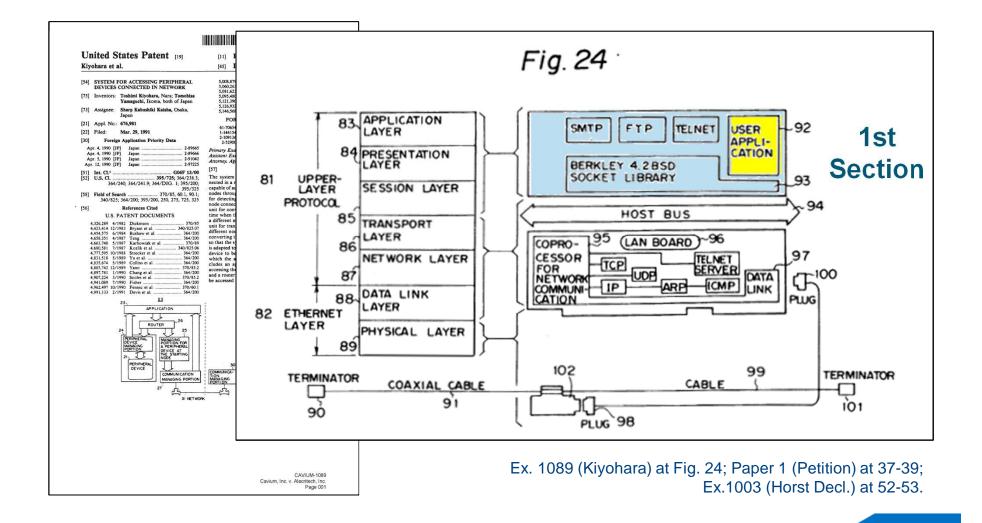

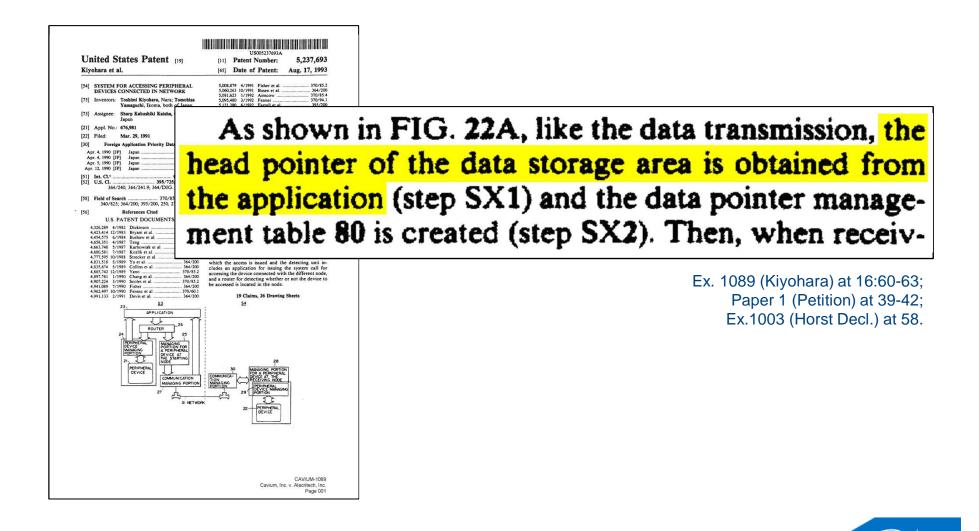

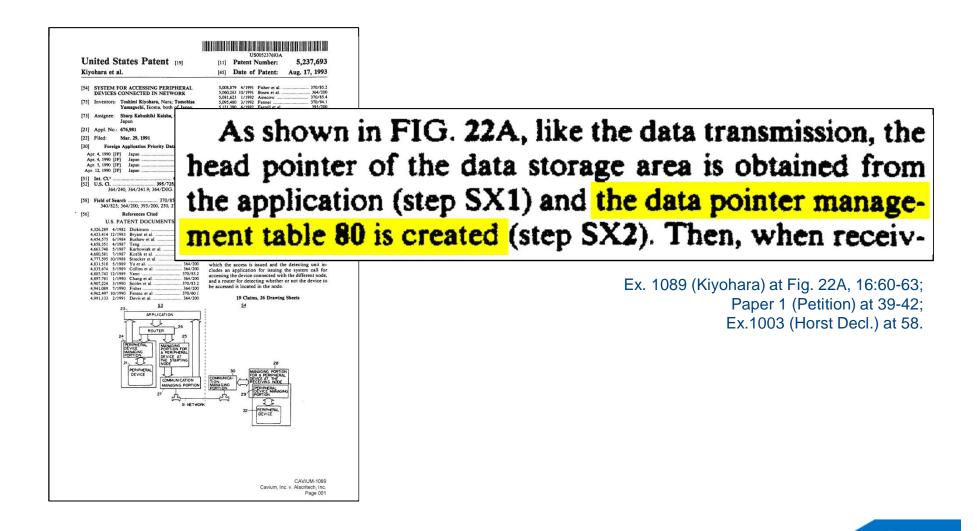

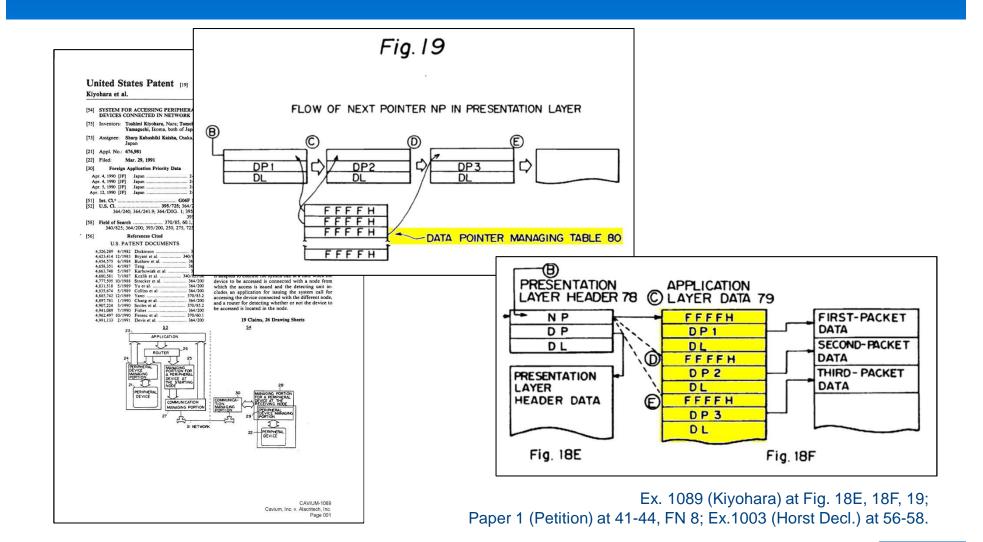

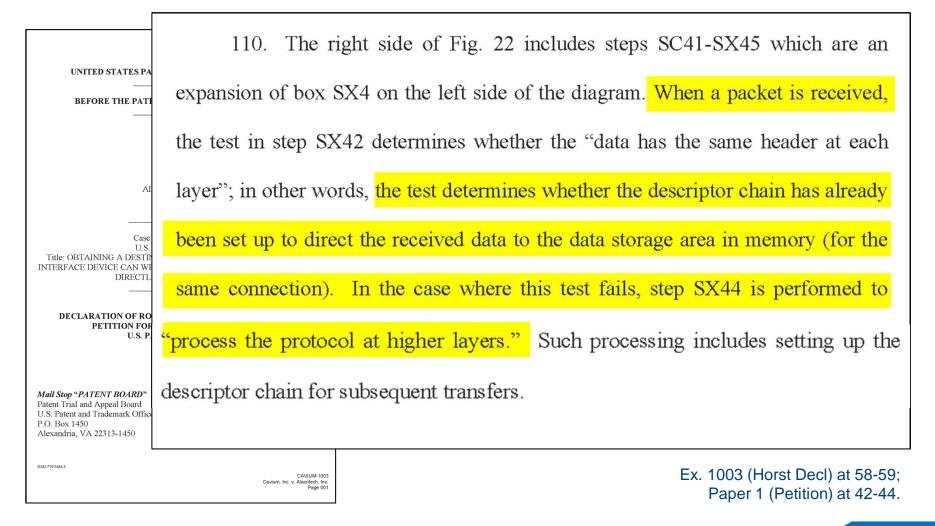

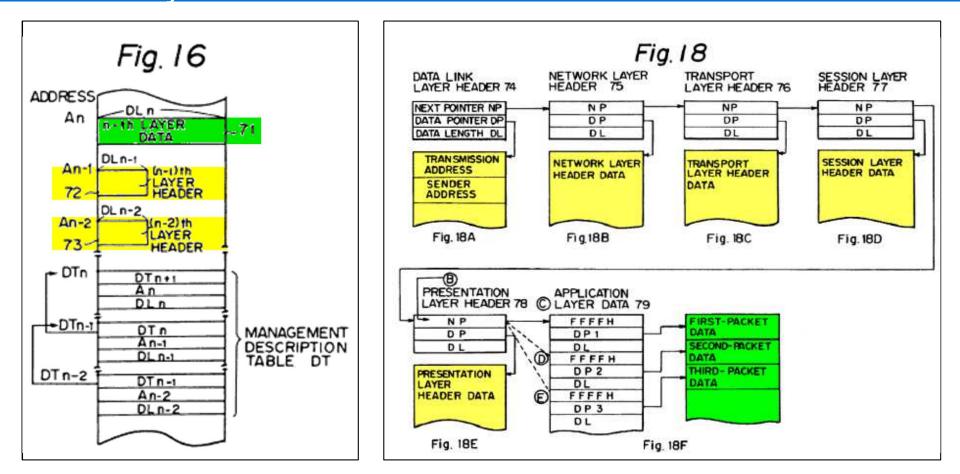

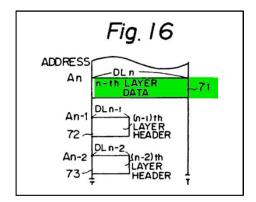

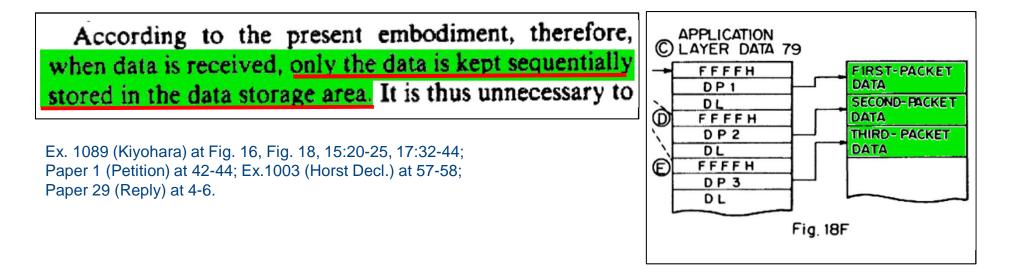

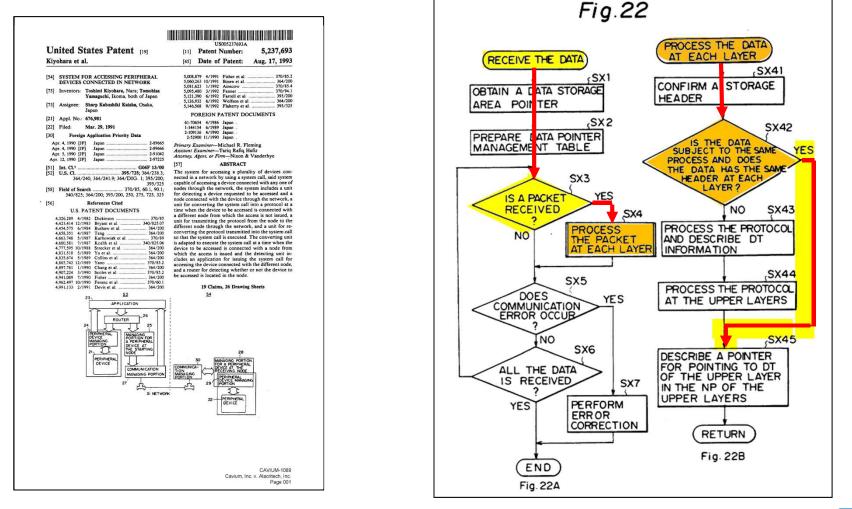

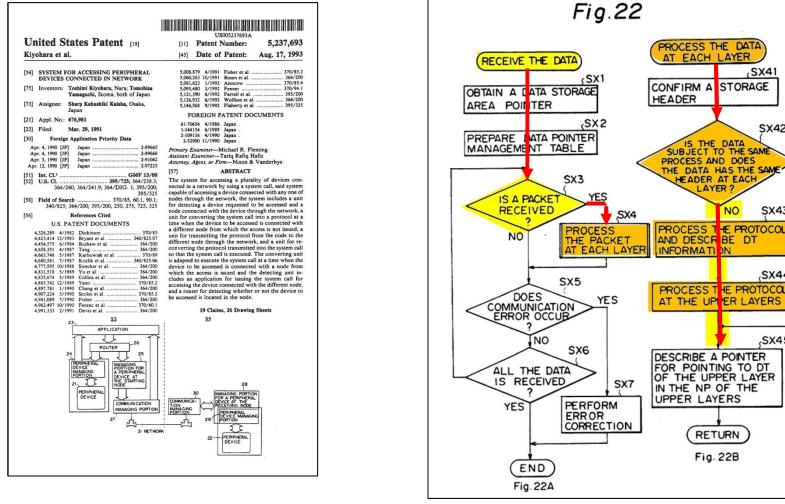

| 1. | Kiyohara transfers packet data without headers to the "destination"                                        | Slides 148-154 |

|----|------------------------------------------------------------------------------------------------------------|----------------|

| 2. | Kiyohara transfers packet data to the "destination" without the host processing network layer or transport | Slideo 155 162 |

|    | layer headers                                                                                              | Slides 155-163 |

| 3. | Kiyohara's data storage area is on the host                                                                | Slides 164-170 |

| 4. | Information in Kiyohara's data storage area is                                                             |                |

|    | controlled by the application                                                                              | Slides 171-174 |

| 5. | SMB is a session layer protocol (claims 2, 7)                                                              | Slides 175-187 |

(intel

## Demonstratives: Table of Contents

### (4) Common Issues

| 1.    | Secondary Considerations (IPR2018-00226, -00234, -00401)          | Slides 188-190 |

|-------|-------------------------------------------------------------------|----------------|

| 2.    | SMB is Prior Art (IPR2018-00226, -00401)                          | Slides 191-197 |

| 3.    | Motion to Exclude<br>(IPR2018-00226, -00234, -00401)              | Slides 198-224 |

| (5) P | etitions are not Time-Barred                                      |                |

| 1.    | 948 and 205 Petitions are not time-barred (IPR2018-00226, -00234) | Slides 225-270 |

| 2.    | 699 Petition is not time-barred (IPR2018-00401)                   | Slides 271-294 |

(intel

U.S. Patent No. 8,805,948 (948 Patent)

> IPR2018-00234 (Intel) IPR2018-00403 (Cavium) IPR2018-01307 (Dell)

\*All citations herein are to the IPR2018-00234 case unless otherwise noted.

### 948 Patent: Instituted Grounds

• Thia, Tannenbaum96, and Stevens2: claims 1, 3, 6-8, 17, 19, 21, and 22.

### 948 Patent: Disputes

- 1. A POSA would have been motivated to combine Thia and Tanenbaum96 (and Stevens2)

- 2. The prior art combinations disclose the limitations of the challenged claims of the 948 Patent

# The Board Has Rejected Many of PO's Arguments

- This Petition involves overlapping prior art and arguments as in prior related IPRs, including IPRs on the 880 Patent (IPR2018-01409; IPR2018-01410)

- Board has previously rejected PO's arguments

- -01409 FWD at 11-14: finding it would have been obvious to combine Thia and Tanenbaum96

- -1409 FWD at 10-11: finding that Thia and Tanenbaum96 teach storing data on the host without TCP headers

## 948 Patent: Disputes

- 1. A POSA would have been motivated to combine Thia and Tanenbaum96 (and Stevens2)

- a. Tanenbaum96 does not teach away from the combination (Board previously sided with Petitioner)

- b. The trend towards TCP/IP in the 1990s would motivate combining Thia's bypass architecture with TCP/IP (Board previously sided with Petitioner)

- c. A POSA would have understood that Thia's teachings are applicable to TCP/IP (Board previously sided with Petitioner)

- d. It would have been obvious to combine Stevens2 with Thia and Tanenbaum96

## The Board rejected PO's argument that Tanenbaum96 teaches away

Patent Owner argues that it would not have been obvious to one of ordinary skill in the art to have combined the teachings of Thia and Tanenbaum because, according to Patent Owner, Tanenbaum discloses a system that "does not introduce a separate processor" but that Thia supposedly discloses a system that has a separate processor. PO Resp. 49. In other words, Patent Owner argues that it would not have been obvious to one of ordinary skill in the art to have bodily incorporated the processor of Thia into the system of Tanenbaum (or vice versa). We are not persuaded by Patent Owner's argument at least because "[t]he test for obviousness is not whether the features of a secondary reference may be bodily incorporated into the structure of the primary reference.... Rather, the test is what the combined teachings of those references would have suggested to those of ordinary skill in the art." In re Keller, 642 F.2d 413, 425 (CCPA

1981).

IPR2017-01409 Paper 79 (FWD) at 12; see also Paper 35 (Reply) at 4-5.

## Tanenbaum96 does <u>not</u> teach away from a combination with Thia

#### Instead, it describes design preferences and tradeoffs

A tempting way to go fast is to build fast network interfaces in hardware. The difficulty with this strategy is that unless the protocol is exceedingly simple, hardware just means a plug-in board with a second CPU and its own program. To avoid having the network coprocessor be as expensive as the main CPU, it is often a slower chip. The consequence of this design is that much of the time the main (fast) CPU is idle waiting for the second (slow) CPU to do the critical work. It is a myth to think that the main CPU has other work to do while waiting. Furthermore, when two general-purpose CPUs communicate, race conditions can occur, so elaborate protocols are needed between the two processors to synchronize them correctly. Usually, the best approach is to make the protocols simple and have the main CPU do the work.

Ex. 1006.588-.589 (Tanenbaum96); see also Paper 35 (Reply) at 4; Ex. 1399.027-.029 (Horst Reply Decl.).

# Tanenbaum96 does not discourage offloading simple protocols

A tempting way to go fast is to build fast network interfaces in hardware. The difficulty with this strategy is that <u>unless</u> the protocol is exceedingly simple, hardware just means a plug-in board with a second CPU and its own program. To avoid having the network coprocessor be as expensive as the main CPU, it is often a slower chip. The consequence of this design is that much of the time the main

Ex. 1006.588 (Tanenbaum96); see also Paper 35 (Reply) at 4, 7; Ex.1399.028-.029 (Horst Reply Decl.).

12

Demonstrative Exhibit – Not Evidence

## Tanenbaum96: Transport processing is "straightforward" in the "normal case"

#### THIRD EDITION COMPUTER NETWORKS ANDREW S. TANENBAUM

TPDU processing overhead has two components: overhead per TPDU and overhead per byte. Both must be attacked. The key to fast TPDU processing is to separate out the normal case (one-way data transfer) and handle it specially. Although a sequence of special TPDUs are needed to get into the *ESTABLISHED* state, once there, TPDU processing is straightforward until one side starts to close the connection.

Ex. 1006.583 (Tanenbaum96); see also Paper 35 (Reply) at 4.

## Thia also recognizes the difficulty of offloading a complex protocol stack

14 A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*) Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems and Computer Engineering, Carleton University, Ottawa, Canada (\*\*) Abstract --- The Reduced Operation Protocol Engine (ROPE) presented here offloads The choice of hardware for the adaptor depends on the complexity of the functions it supports. In [2, 22] where the transport protocol layer is offloaded or in [7] where the full protocol stack can be offloaded, general purpose microprocessors are used. Probably because of the complexity of existing protocols, VLSI [24] implementation above the data link layer has been disappointing so far. In [8], dedicated VLSI chips are used to support TCP checksums. Also, some newer lightweight transport protocols are specially designed for VLSI implementation [1, 3]. non or exist [14, 21, 38], special protocol structures [15, 30] and hardware assist [22] by offloading all or part of the protocol functions to an adaptor. This paper takes the latter approach. The key problems associated with offboard processing include: see also Paper 35 (Reply) at 4. D Partitioning the functionality between the host and the adaptor is difficult and may easily lead to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offloading. For example, the buffer management task [36] may be offloaded, but this leaves the problem of control for accessing it within the full protocol logic. This research was done while Dr. Thia was at Carleton University G. Neufield et al. (eds.), Protocols for High Speed Networks IV © Springer Science+Business Media Dordrecht 1995

Ex. 1015.002 (Thia);

## Thia's solution: "Fast path" offload is based on header prediction

14

A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture

Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*)

Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems and Computer Engineering, Carleton University, Ottawa, Canada (\*\*)

Abstract — The Reduced Operation Protocol Engine (ROPE) presented here offloads

This paper presents a feasibility study for a new approach to hardware assistance. It combines the relatively simple operations needed for data transfer across multiple layers and provides a hardware "fast path" for them, which will be efficient for bulk data transfer. It is based on the "protocol bypass concept" [37] which is a generalization of Jacobson's "Header Prediction" algorithm [20] for TCP/IP. Bypass solves the problems identified above, which may limit the use of offboard processing, by implementing an entire service through all layers for certain cases. This simplifies the interface between the host and the adaptor chip

Improved sortware implementation of existing protocols [5, 55], parallel processing techniques [14, 21, 38], special protocol structures [15, 30] and hardware assist [22] by offloading all or part of the protocol functions to an adaptor. This paper takes the latter approach. The key problems associated with offboard processing include:

Partitioning the functionality between the host and the adaptor is difficult and may easily lead to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offloading. For example, the buffer management task [36] may be offloaded, but this leaves the problem of control for accessing it within the full protocol logic.

This research was done while Dr. Thia was at Carleton University

G. Neufield et al. (eds.), *Protocols for High Speed Networks IV* © Springer Science+Business Media Dordrecht 1995 Ex. 1015.002 (Thia); see also Paper 35 (Reply) at 4.

## Both disclose a bypass/fast-path based on TCP/IP header prediction

#### A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*)

Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems and Computer Engineering, Carleton University, Ottawa, Canada

14

Abreast — The Roberts Operators Prevect Engine (GDPF) presented here effects and the other of the strength strength strength strength strength and strength for data strength, The molecular in the MentPhysic this segment presenting path is durit understand. The strength str

Keyword codes: C.2.2, B.4.1 Keywords: Network Protocols, Data Communications Dr

#### Introduction

The above of Flue Optic inclusions, which offers high hardwidth and how its remains hardwidt be primore between the most of the normalization algorithm of the communication and providing its first end points of the system [216]. Obstitutions of the system point of

This research was done while Dr. This was at Cadoton University

G. Neufield et al. (eds.), Protocols for High Speed Network D Springer Science+Business Media Dordrecht 1995 This paper presents a feasibility study for a new approach to hardware assistance. It combines the relatively simple operations needed for data transfer across multiple layers and provides a hardware "fast path" for them, which will be efficient for bulk data transfer. It is based on the "protocol bypass concept" [37] which is a generalization of Jacobson's "Header Prediction" algorithm [20] for TCP/IP. Bypass solves the problems identified above, which may limit the use of offboard processing, by implementing an entire service through all layers for certain cases. This simplifies the interface between the host and the adaptor chip and minimizes their interaction, which is supported by an access test, some DMA processing and a simple command protocol. The chip design based on bypassing is called ROPE, for Reduced Operation Protocol Engine. The contribution of this paper is to define the host/chip interface and the chip operation, and to report on a VHDL-based feasibility study of the chip design. It appears to be feasible to support an end-system single-connection data rate approaching 1 Gbps.

#### Ex. 1015.002 (Thia); see also Paper 35 (Reply) at 2.

The <u>fast path</u> updates the connection record and copies the data to the user. While it is copying, it also computes the checksum, eliminating an extra pass over the data. If the checksum is correct, the connection record is updated and an acknowledgement is sent back. The general scheme of first making a quick check to see if the header is what is expected, and having a special procedure to handle that case, is called **header prediction**. Many TCP implementations use it. When this optimization and all the other ones discussed in this chapter are used together, it is possible to get TCP to run at 90 percent of the speed of a local memory-tomemory copy, assuming the network itself is fast enough.

Ex. 1006.585 (Tanenbaum96); see also Paper 35 (Reply) at 2.

## 948 Patent: Disputes

- 1. A POSA would have been motivated to combine Thia and Tanenbaum96 (and Stevens2)

- a. Tanenbaum96 does not teach away from the combination (Board previously sided with Petitioner)

- b. The trend towards TCP/IP in the 1990s would motivate combining Thia's bypass architecture with TCP/IP (Board previously sided with Petitioner)

- c. A POSA would have understood that Thia's teachings are applicable to TCP/IP (Board previously sided with Petitioner)

- d. It would have been obvious to combine Stevens2 with Thia and Tanenbaum96

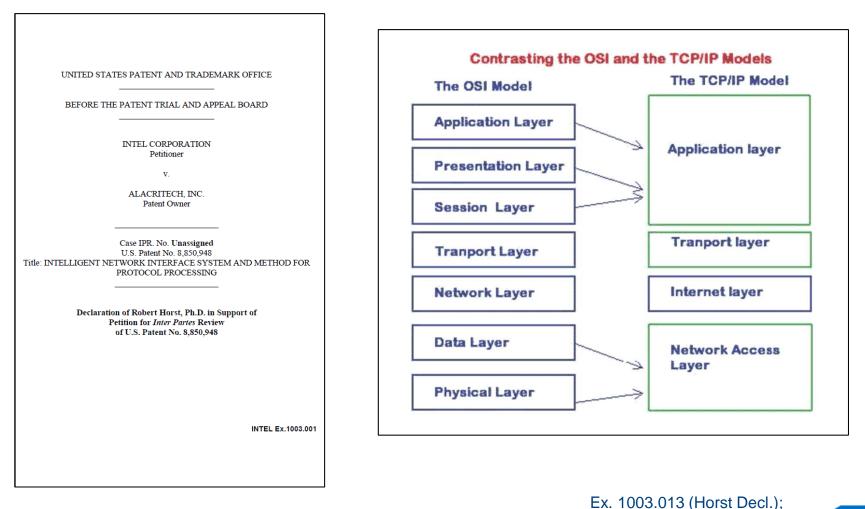

# The Board rejected PO's "lack of interest in OSI" argument

Trials@uspto.gov 571-272-7822 Entered: UNITED STATES PATENT AND TRADEMAR BEFORE THE PATENT TRIAL AND APPEAD INTEL CORPORATION, CAVIUM, LLC, and E Petitioner, v. ALACRITECH. INC... Patent Owner. Case IPR2017-01409 Patent 8,131,880 B21 Before STEPHEN C. SIU, DANIEL N. FISHMAN, and CHARLES J. BOUDREAU, Administrative Patent Judg SIU, Administrative Patent Judge. FINAL WRITTEN DECISION 35 U.S.C. § 318(a)

<sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2017-01 Inc., which filed a Petition in Case IPR2018-00338, were petitioners in this proceeding. According to updated man in this proceeding, Cavium, Inc. has now been converted to Cavium, LLC. Paper 74.

Patent Owner further argues that it would not have been obvious to one of ordinary skill in the art to have combined the teachings of Thia and Tanenbaum because "Tanenbaum explains that the lack of interest in OSI was due . . . to 'the enormous complexity of the [OSI] model and the protocols" and that, according to Patent Owner, there was an "undisputed lack of interest in OSI in the relevant timeframe." PO Resp. 51. However, as previously discussed, Petitioner relies on Tanenbaum for disclosing TCP/IP and not OSI. Even assuming Patent Owner's contention to be correct that Tanenbaum supposedly discloses a "lack of interest in OSI,"

Patent Owner does not assert or demonstrate persuasively that this presumed disclosure regarding an alleged "lack of interest in OSI" sufficiently refutes Petitioner's showing of obviousness of the disputed claims over the

combination of Thia and Tanenbaum.

IPR2017-01409 Paper 79 (FWD) at 13; see also Paper 35 (Reply) at 5.

# By 1996 OSI protocol use vanished and TCP/IP became dominant

### THIRD EDITION COMPUTER NETWORKS

ANDREW S. TANENBAUM

Furthermore, the networking hardware and software have completely changed since the second edition appeared. In 1988, nearly all networks were based on copper wire. Now, many are based on fiber optics or wireless communication. Proprietary networks, such as SNA, have become far less important than public networks, especially the Internet. The OSI protocols have quietly vanished, and the TCP/IP protocol suite has become dominant. In fact, so much has changed, the book has almost been rewritten from scratch.

Ex. 1006.016 (Tanenbaum96); see also Paper 2 (Petition) at 25, 57.

## Thia's hardware offload provides advantages over software alone

14

#### A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture

Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*)

Newbridge Networks, Dept. of Systems and

Abstract — The E critical functions of a path for data transfer. involves only a small hardware. Multiple-lay and buffer managemen are a significant overh paper describes the des using VHDL. The desi array technology, and per second, in a conne

Keyword codes: C.2.2 Keywords: Network P

1 Introduction

The advent of Fib rates, has shifted the p munications processing quality-of-service guar combination of operati the data stream. To alle improved software imp [14, 21, 38], special pr part of the protocol fu The key problems D Partitioning the fur

lead to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offloading. For example, the buffer management task [36] may be offloaded, but this leaves the problem of control for accessing it within the full protocol logic.

This research was done while Dr. Thia was at Carleton University

G. Neufield et al. (eds.), *Protocols for High Speed Networks IV* © Springer Science+Business Media Dordrecht 1995

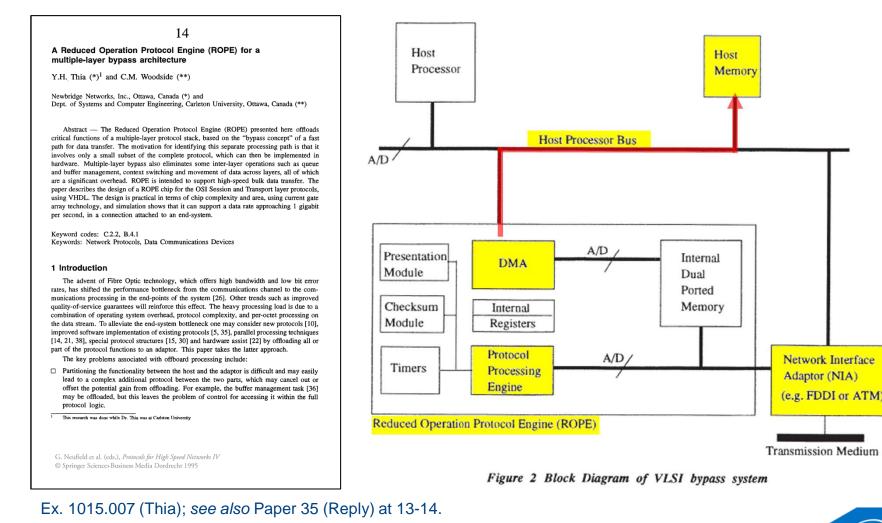

It can be concluded from this study that it is feasible to implement the bypass stack (at least for the transport and session layers) in VLSI and that the performance would be at least an order of magnitude higher than software protocol processing. The bypass system offloads the critical protocol functions and the associated non-protocol-specific functions onto a "Reduced Operation Protocol Engine" (ROPE). The gate count for the bypass chip can easily fit into a commercially available gate array Integrated Circuit. Per-octet operations are particularly efficient when performed on the chip. The host processor is relieved of a significant proportion of protocol processing and can concentrate on the application processing. The speed of communication processing in the host system can now match the transmission bandwidth of high-speed networks, e.g. ATM technology, thereby increasing the application-to-application throughput performance. (In an ATM system we assume that the segmentation

Ex. 1015.013 (Thia); see also Paper 35 (Reply) at 4-5.

## 948 Patent: Disputes

- 1. A POSA would have been motivated to combine Thia and Tanenbaum96 (and Stevens2)

- a. Tanenbaum96 does not teach away from the combination (Board previously sided with Petitioner)

- b. The trend towards TCP/IP in the 1990s would motivate combining Thia's bypass architecture with TCP/IP (Board previously sided with Petitioner)

- c. A POSA would have understood that Thia's teachings are applicable to TCP/IP (Board previously sided with Petitioner)

- d. It would have been obvious to combine Stevens2 with Thia and Tanenbaum96

# The Board rejected PO's "standard OSI protocol" argument

Trials@uspto.gov 571-272-7822 Entered: UNITED STATES PATENT AND TRADEMAN BEFORE THE PATENT TRIAL AND APPEA INTEL CORPORATION, CAVIUM, LLC, and E Petitioner, v. ALACRITECH. INC., Patent Owner. Case IPR2017-01409 Patent 8,131,880 B21 Before STEPHEN C. SIU, DANIEL N. FISHMAN, and CHARLES J. BOUDREAU, Administrative Patent Judg SIU, Administrative Patent Judge, FINAL WRITTEN DECISION 35 U.S.C. § 318(a) <sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2017-0 Inc., which filed a Petition in Case IPR2018-00338, were petitioners in this proceeding. According to updated man in this proceeding, Cavium, Inc. has now been converted to Cavium, LLC.

Paper 74.

Patent Owner also argues that it would not have been obvious to one of ordinary skill in the art to have combined the teachings of Thia and Tanenbaum because Thia allegedly discloses that "its bypass architecture can be used with 'any standard protocol'" but supposedly intends to disclose that "any standard protocol" includes only "OSI protocols" because "Thia refers to concepts and features that are part of the OSI model, not the TCP/IP model." PO Resp. 51. We are not persuaded by Patent Owner's argument at least because Patent Owner does not provide sufficient evidence supporting Patent Owner's allegation that one of skill in the art would have understood that Thia intended to disclose "any OSI protocol" but inadvertently discloses "any standard protocol." We agree with Petitioner (Pet. 30–35 (citing Ex. 1003)) that "Thia's bypass stack is a generalization of the ... algorithm for TCP/IP" and is not "confined to the OSI protocol." Pet. Reply 9. In

> IPR2017-01409 Paper 79 (FWD) at 13; see also Paper 35 (Reply) at 5.

## The Board rejected PO's argument that Thia teaches away from using TCP/IP

Patent Owner also argues that it would not have been obvious to one Trials@uspto.gov 571-272-7822 Entered: of ordinary skill in the art to have combined the teachings of Thia and UNITED STATES PATENT AND TRADEMAR Tanenbaum because Thia supposedly discloses "an easy migration path" by BEFORE THE PATENT TRIAL AND APPEAL "modify[ing] existing **OSI** stack software" but supposedly fails to disclose INTEL CORPORATION, CAVIUM, LLC, and E "modifying *TCP/IP* stack software." PO Resp. 53. We are not persuaded Petitioner, v. by Patent Owner's argument at least because the Petitioner's showing of ALACRITECH. INC... Patent Owner. obviousness of the claimed invention is based on the combination of Thia Case IPR2017-01409 Patent 8,131,880 B21 and Tanenbaum and not based on Thia alone. Before STEPHEN C. SIU, DANIEL N. FISHMAN, and CHARLES J. BOUDREAU, Administrative Patent Judges. IPR2017-01409 Paper 79 (FWD) at 14; SIU, Administrative Patent Judge see also Paper 35 (Reply) at 6-7.

FINAL WRITTEN DECISION 35 U.S.C. § 318(a)

<sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2017-01736, and Dell, Inc., which filed a Petition in Case IPR2018-00338, were joined as petitioners in this proceeding. According to updated mandatory notices filed in this proceeding, Cavium, Inc. has now been converted to Cavium, LLC. Paper 74.

## Both disclose a bypass/fast-path based on TCP/IP header prediction

#### 14

A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*)

Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems and Computer Engineering, Carleton University, Ottawa, Canada

### triads functions of a multiple-large protocol stack, based on the "Typnas concept" of a 1 to the data transfer. The movisms for for destrupting this separate processing path is that be observed by a multi-large star between the single-mean data and the single-mean data

#### Keyword codes: C.2.2, B.4.1 Keywords: Network Protocols, Data Communications De

#### Introduction

The absence of Films Optics technology, which offers high headscale and to be comparison of the stress of the str

combines the relatively simple operations needed for data transfer across multiple layers and provides a hardware "fast path" for them, which will be efficient for bulk data transfer. It is based on the "protocol bypass concept" [37] which is a generalization of Jacobson's "Header Prediction" algorithm [20] for TCP/IP. Bypass solves the problems identified above, which may limit the use of offboard processing, by implementing an entire service through all layers for certain cases. This simplifies the interface between the host and the adaptor chip and minimizes their interaction, which is supported by an access test, some DMA processing and a simple command protocol. The chip design based on bypassing is called ROPE, for Reduced Operation Protocol Engine. The contribution of this paper is to define the host/chip interface and the chip operation, and to report on a VHDL-based feasibility study of the chip design. It appears to be feasible to support an end-system single-connection data rate approaching 1 Gbps.

This paper presents a feasibility study for a new approach to hardware assistance. It

#### Ex. 1015.002 (Thia); see also Paper 35 (Reply) at 2.

The fast path updates the connection record and copies the data to the user. While it is copying, it also computes the checksum, eliminating an extra pass over the data. If the checksum is correct, the connection record is updated and an acknowledgement is sent back. The general scheme of first making a quick check to see if the header is what is expected, and having a special procedure to handle that case, is called **header prediction**. Many TCP implementations use it. When this optimization and all the other ones discussed in this chapter are used together, it is possible to get TCP to run at 90 percent of the speed of a local memory-tomemory copy, assuming the network itself is fast enough.

Ex. 1006.585 (Tanenbaum96); see also Paper 35 (Reply) at 2.

## Thia was not theoretical and offered a practical design for a hardware bypass

are a significant overhead. ROPE is intended to support high-speed bulk data transfer. The paper describes the design of a ROPE chip for the OSI Session and Transport layer protocols, using VHDL. The design is practical in terms of chip complexity and area, using current gate array technology, and simulation shows that it can support a data rate approaching 1 gigabit per second, in a connection attached to an end-system.

#### 4.3 First Design: Design Steps

Figure 3 shows the steps followed in this study. There were three stages, a behavioural model, a structural or RTL model, and a gate level design. These gave us two kinds of feasibility check, that the logic we specified will execute the protocol within the environment we envisage, and that the design is technically feasible, for instance in a reasonable chip area.

It can be concluded from this study that it is feasible to implement the bypass stack (at least for the transport and session layers) in VLSI and that the performance would be at least an order of magnitude higher than software protocol processing. The bypass system offloads the critical protocol functions and the associated non-protocol-specific functions onto a "Reduced Operation Protocol Engine" (ROPE). The gate count for the bypass chip can

Ex. 1015.001, .008, .013 (Thia); see also Paper 35 (Reply) at 7-8; Ex.1399.033-.034 (Horst Reply Decl.).

### Thia's teachings are not limited to OSI

#### 14

A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture

Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*)

Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems and Computer Engineering, Carletor

Abstract — The Reduced Operation Protocol Engine (NOTE) presence new onroads critical functions of a multiple-layer protocol stack, based on the "bypass concept" of a fast path for data transfer. The motivation for identifying this separate processing path is that it involves only a small subset of the complete protocol, which can then be implemented in

hardware. Multiple-layer bypass also eliminates some and buffer management, context switching and movern are a significant overhead. ROPE is intended to supp paper describes the design of a ROPE chip for the OSI using VHDL. The design is practical in terms of chip c array technology, and simulation shows that it can sup per second, in a connection attached to an end-system

Keyword codes: C.2.2, B.4.1 Keywords: Network Protocols, Data Communication

#### 1 Introduction

The advent of Fibre Optic technology, which off rates, has shifted the performance bottleneck from the munications processing in the end-points of the system quality-of-service guarantees will reinforce this effect. combination of operating system overhead, protocol of the data stream. To alleviate the end-system bottleneck improved software implementation of existing protocols [14, 21, 38], special protocol structures [15, 30] and ha part of the protocol functions to an adaptor. This pape The key problems associated with offboard proces

Partitioning the functionality between the host and lead to a complex additional protocol between the offset the potential gain from offloading. For exam may be offloaded, but this leaves the problem of protocol logic.

This research was done while Dr. Thia was at Carleton University

G. Neufield et al. (eds.), Protocols for High Speed Networks IV © Springer Science+Business Media Dordrecht 1995

## A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture

Abstract — The Reduced Operation Protocol Engine (ROPE) presented here offloads critical functions of a multiple-layer protocol stack, based on the "bypass concept" of a fast path for data transfer. The motivation for identifying this separate processing path is that it involves only a small subset of the complete protocol, which can then be implemented in hardware. Multiple-layer bypass also eliminates some inter-layer operations such as queue and buffer management, context switching and movement of data across layers, all of which are a significant overhead. ROPE is intended to support high-speed bulk data transfer. The paper describes the design of a ROPE chip for the OSI Session and Transport layer protocols, using VHDL. The design is practical in terms of chip complexity and area, using current gate array technology, and simulation shows that it can support a data rate approaching 1 gigabit per second, in a connection attached to an end-system.

> Ex. 1015.001 (Thia); see also Paper 35 (Reply) at 5; Ex. 1399.030-.031 (Horst Reply Decl.).

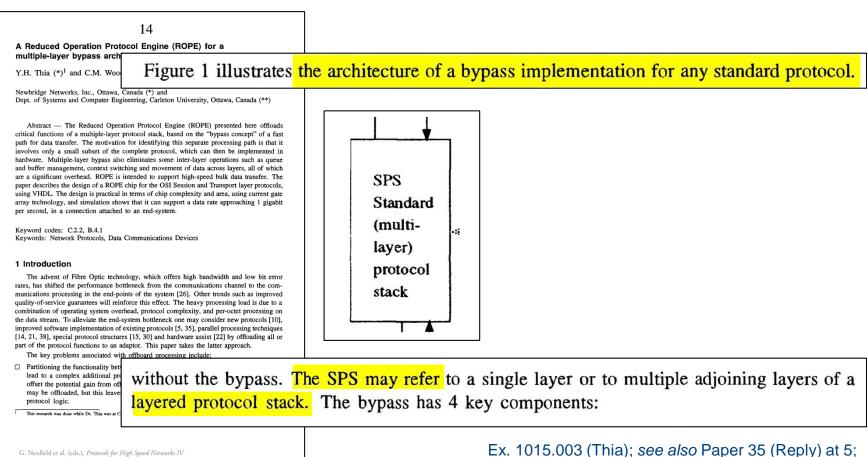

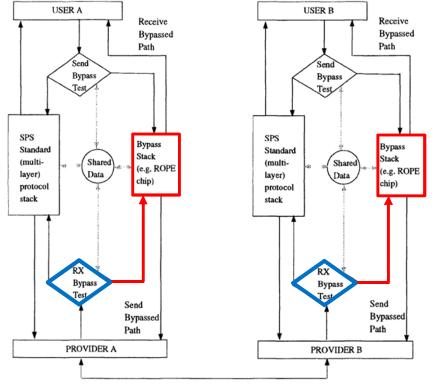

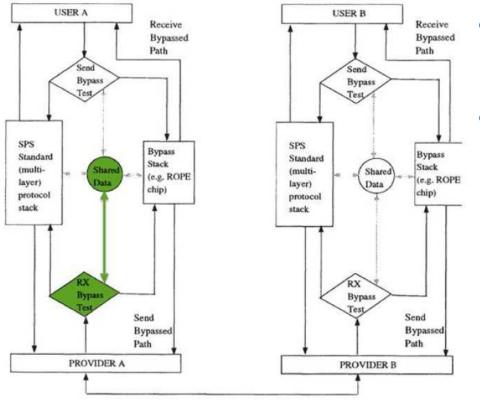

# Thia's standard protocol stack (SPS) is a "multi-layer" stack, not an "OSI" stack

© Springer Science+Business Media Dordrecht 1995

Ex. 1015.003 (Thia); see also Paper 35 (Reply) at 5; Ex. 1399.030-.031 (Horst Reply Decl.).

# Thia teaches that its bypass offload is more than one multi-layer stack

14 A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*) Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems A clean separation of functionality requiring only a simple protocol to communicate Abstract critical function between the host and adaptor is desired, and is provided by a bypass. Its particular set of path for data tra involves only a s hardware. Multip functions are complete in themselves and have a focussed interface with the host software and buffer manage are a significant paper describes th at the packet entry point. There is relatively infrequent switching between the SPS and using VHDL. The array technology, per second, in a the bypass stack; Keyword codes: Reduced non-protocol-specific processing overhead. For example the processing of ac-Keywords: Netwo knowledgment packets is dominated by interrupt handling, typically a few hundred in-1 Introductio The advent structions, rather than by the protocol processing itself. Our approach removes acknowlrates, has shifted munications pro quality-of-service edgment handling altogether from the host. Also, the bypass system can be extended to combination of or the data stream. improved softwar incorporate multiple-layer stacks and remove overhead that way; [14, 21, 38], spec part of the protoc The key pro Partitioning t lead to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offloading. For example, the buffer management task [36] Ex. 1015.005 (Thia); see also Paper 35 (Reply) at 6-7; may be offloaded, but this leaves the problem of control for accessing it within the full protocol logic. Ex.1399.030-.031 (Horst Reply Decl.). This research was done while Dr. This was at Carleton University G. Neufield et al. (eds.), Protocols for High Speed Networks IV © Springer Science+Business Media Dordrecht 1995

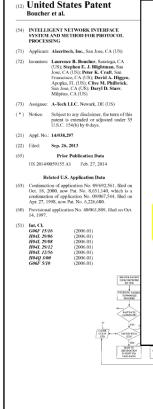

# TCP/IP and OSI were widely understood to be very similar

see also Paper 35 (Reply) at 6.

(intel)

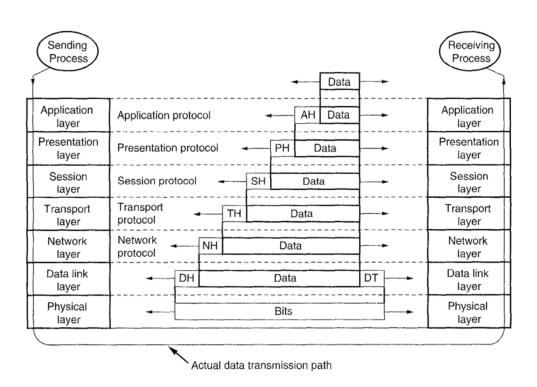

# The 948 Patent admits that TCP/IP layers correspond to OSI layers

####

REATE COR FOR

INTEL Ex.1001.001

plished at the presentation level. Application layers are serviced by respective presentation layers, the application layers translating between programs particular to individual hosts and standardized programs for presentation to either an application or an end user. The TCP/IP standard includes the lower four layers and application layers, but integrates the functions of session layers and presentation layers into adjacent layers. Generally speaking, application, presentation and session layers are defined as upper layers, while transport, network and data link layers are defined as lower layers.

Ex. 1001 at 2:10-19 (948 Patent); see also Paper 35 (Reply) at 6; Ex.1399.031-.032 (Horst Reply Decl.).

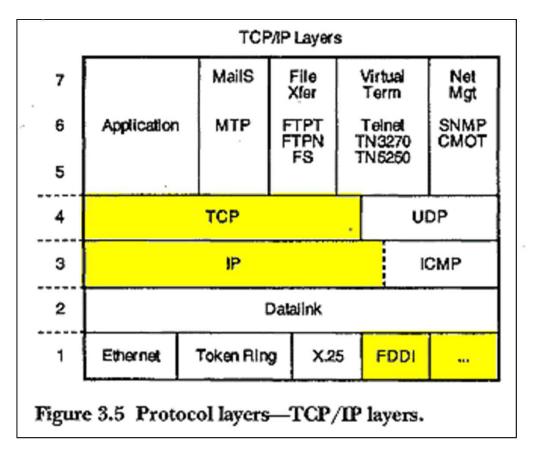

## Thia's disclosure of FDDI does not preclude TCP/IP as it was commonly known to use them together

Ex. 1252.022-.023 (McClain); see also Paper 35 (Reply) at 6.

(intel)

## 948 Patent: Disputes

- 1. A POSA would have been motivated to combine Thia and Tanenbaum96 (and Stevens2)

- a. Tanenbaum96 does not teach away from the combination

- b. The trend towards TCP/IP in the 1990s would motivate combining Thia's bypass architecture with TCP/IP

- c. A POSA would have understood that Thia's teachings are applicable to TCP/IP

- d. It would have been obvious to combine Stevens2 with Thia and Tanenbaum96

# Each discloses a bypass/fast-path based on TCP/IP header prediction

#### 28.4 Header Prediction

We now continue with the code in tcp\_input, from where we left off in Figure 28.8. *Header prediction* was put into the 4.3BSD Reno release by Van Jacobson. The only description of the algorithm, other than the source code we're about to examine, is in [Jacobson 1990b], which is a copy of three slides showing the code.

Header prediction helps unidirectional data transfer by handling the two common cases.

- 1. If TCP is sending data, the next expected segment for this connection is an ACK for outstanding data.

- 2. If TCP is receiving data, the next expected segment for this connection is the next in-sequence data segment.

In both cases a small set of tests determines if the next expected segment has been received, and if so, it is handled in-line, faster than the general processing that follows later in this chapter and the next.

Ex. 1013.960-.962 (Stevens2); see also Paper 35 (Reply) at 7; Paper 2 (Petition) at 56-60; Ex.1399.033-.034 (Horst Reply Decl.); Ex.1003.078-.080 (Horst Decl.).

The fast path updates the connection record and copies the data to the user. While it is copying, it also computes the checksum, eliminating an extra pass over the data. If the checksum is correct, the connection record is updated and an acknowledgement is sent back. The general scheme of first making a quick check to see if the header is what is expected, and having a special procedure to handle that case, is called **header prediction**. Many TCP implementations use it. When this optimization and all the other ones discussed in this chapter are used together, it is possible to get TCP to run at 90 percent of the speed of a local memory-tomemory copy, assuming the network itself is fast enough.

Ex. 1006.585 (Tanenbaum96); see also Paper 35 (Reply) at 2.

ínteľ.

## Each discloses a bypass/fast-path based on TCP/IP header prediction

#### 28.4 Header Prediction

We now continue with the code in tcp\_input, from where we left off in Figure 28.8. *Header prediction* was put into the 4.3BSD Reno release by Van Jacobson. The only description of the algorithm, other than the source code we're about to examine, is in [Jacobson 1990b], which is a copy of three slides showing the code.

Header prediction helps unidirectional data transfer by handling the two common cases.

- 1. If TCP is sending data, the next expected segment for this connection is an ACK for outstanding data.

- 2. If TCP is receiving data, the next expected segment for this connection is the next in-sequence data segment.

In both cases a small set of tests determines if the next expected segment has been received, and if so, it is handled in-line, faster than the general processing that follows later in this chapter and the next.

#### 14 A Reduced Operation Protocol Engine (ROPE) for a multiple-layer typass architecture Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*) Vandelaw Neurosci Bac Otera Constant Const

Abstract — The Reduced Operation Protocol Engine GDCPE presented here offsuch critical functions of an antibility-layer protocol starks, based on the "type-starks concept" of a fast stark for fast starkster. The motivation for lobstraphing this segments processing paths is that it in the starkster is the stark of the stark starkster is the stark of the stark starkster is the stark of the stark starkster is the stark stark stark stark stark and before management, context within gash movement of the starkster is the stark and before management, context within gash movement of the starkster is the stark stark stark stark stark stark starkster is the stark st

Keyword codes: C.2.2, B.4.1 Keywords: Network Protocols, Data Communications Device

#### Introduction

The above of Pilos Uppic schedulery, which offers high basic-basil and two but creatmannian and the state of the state quality of environments with instruct his effect. The heavy precessing load in due to a combination of operating in the environment of the state state of the instruction of the state of the part of the proceed structures (15, 35) and hadrone usual (21) of the state of the part of the proceed structures (15, 35) and hadrone usual (21) of the state of

Ited to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offboading. For example, the buffer management task [36] may be offboaded, but this leaves the problem of control for accessing it within the full protocol logic. The membra was fully a fully and the set of the protocol logic.

G. Neufleld et al. (eds.), Protocol for High Speed Networ © Springer Science+Business Media Dordrecht 1995 Ex. 1013.960-.962 (Stevens2); see also Paper 35 (Reply) at 7; Paper 2 (Petition) at 56-60; Ex.1399.033-.034 (Horst Reply Decl.); Ex.1003.078-.080 (Horst Decl.).

This paper presents a feasibility study for a new approach to hardware assistance. It combines the relatively simple operations needed for data transfer across multiple layers and provides a hardware "fast path" for them, which will be efficient for bulk data transfer. It is based on the "protocol bypass concept" [37] which is a generalization of Jacobson's "Header Prediction" algorithm [20] for TCP/IP. Bypass solves the problems identified above, which may limit the use of offboard processing, by implementing an entire service through all layers for certain cases. This simplifies the interface between the host and the adaptor chip and minimizes their interaction, which is supported by an access test, some DMA processing and a simple command protocol. The chip design based on bypassing is called ROPE, for

Ex. 1015.002 (Thia); see also Paper 35 at 2.

**inte**l

### 948 Patent: Disputes

- 1. A POSA would have been motivated to combine Thia and Tanenbaum96 (and Stevens2)

- 2. The prior art combinations disclose the limitations of the challenged claims of the 948 Patent

### 948 Patent: Disputes

- 2. The prior art combinations disclose the limitations of the challenged claims of the 948 Patent

- a. The combination discloses a network interface checking whether packets are IP fragmented

- b. The combination discloses checking whether "packets" have certain exception conditions / the combination discloses the protocol stack processing exception conditions

- c. The combination discloses bypassing host protocol stack processing and storing data from packets without exception conditions (Board previously found that Thia and Tanenbaum96 teach this)

### 948 Patent: Claims 1, 17

The invention claimed is:

**1**. A method for network communication by a host computer having a network interface that is connected to the host by an input/output bus, the method comprising:

- running, on the host computer, a protocol processing stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, with an application layer running above the TCP layer;

- initializing, by the host computer, a TCP connection that is defined by source and destination IP addresses and source and destination TCP ports;

- receiving, by the network interface, first and second packets, wherein the first packet has a first TCP header and contains first payload data for the application, and the second packet has a second TCP header and contains second payload data for the application;

- checking, by the network interface, whether the packets have certain exception conditions, including checking whether the packets are IP fragmented, checking whether the packets have a FIN flag set, and checking whether the packets are out of order;

- if the first packet has any of the exception conditions, then protocol processing the first TCP header by the protocol processing stack;

- if the second packet has any of the exception conditions, then protocol processing the second TCP header by the protocol processing stack;

- if the packets do not have any of the exception conditions, then bypassing host protocol processing of the TCP headers and storing the first payload data and the second payload data together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the first payload data and the second payload data.

**17**. An apparatus for network communication, the apparatus comprising:

- a host computer running a protocol stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, the protocol stack adapted to establish a TCP connection for an application layer running above the TCP layer, the TCP connection being defined by source and destination IP addresses and source and destination TCP ports;

- a network interface that is connected to the host computer by an input/output bus, the network interface adapted to parse the headers of received packets to determine whether the headers have the IP addresses and TCP ports that define the TCP connection and to check whether the packets have certain exception conditions, including whether the packets are IP fragmented, have a FIN flag set, or are out of order, the network interface having logic that directs any of the received packets that have the exception conditions to the protocol stack for processing, and directs the received packets that do not have any of the exception conditions to have their headers removed and their payload data stored together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the payload data that came from different packets of the received packets.

Ex. 1001 (948 Patent) at Claim 1, Claim 7.

### Thia + Tanenbaum96 teaches checking for fragmentation in fast-path test

#### 14

A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture

Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*)

Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems and Computer Engineering, Carleton University, Ottawa, Canada (\*\*)

Abstract — The Reduced Operation Protocol Engine (ROPE) presented here offloads critical functions of a multiple-layer protocol stack, based on the "bypass concept" of a fast path for data transfer. The motivation for identifying this separate processing path is that it involves only a small subset of the complete protocol, which can then be implemented in hardware. Multiple-layer bypass also eliminates some inter-layer operations such as queue and buffer management, context switching and movement of data across layers, all of which Thia's RX bypass test checks PDU headers to determine if packets are bypassable

phase. The receive bypass test matches the incoming PDU headers with a template that identifies the predicted bypassable headers. The bypass stack performs all the relevant protocol processing in the data transfer phase. The shared data are used to maintain state

The advent of Fubre Optic technology, which otters high bandwidth and low bit error rates, has shifted the performance bottleneck from the communications channel to the communications processing in the end-points of the system [26]. Other trends such as improved quality-of-service guarantees will reinforce this effect. The heavy processing load is due to a combination of operating system overhead, protocol complexity, and per-octet processing on the data stream. To alleviate the end-system bottleneck one may consider new protocols [10], improved software implementation of existing protocols [5, 35], parallel processing techniques [14, 21, 38], special protocol structures [15, 30] and hardware assist [22] by offloading all or part of the protocol functions to an adaptor. This paper takes the latter approach. The key problems associated with offboard processing include:

□ Partitioning the functionality between the host and the adaptor is difficult and may easily lead to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offloading. For example, the buffer management task [36] may be offloaded, but this leaves the problem of control for accessing it within the full protocol logic.

This research was done while Dr. Thia was at Carleton University

G. Neufield et al. (eds.), Protocols for High Speed Networks IV © Springer Science+Business Media Dordrecht 1995 Ex. 1015.003 (Thia); see also Paper 35 (Reply) at 8; Paper 2 at 75 (Petition).

### Thia + Tanenbaum96 teaches checking for fragmentation in fast-path test

#### 14

#### A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture

Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*)

Newbridge Networks, Inc., Ottawa, Canada (\*) and Dept. of Systems and Computer Engineering, Carleton University, Ottawa, Canada (\*\*)

Abstract — The Reduced Operation Protocol Engine (ROPE) presented here offloads critical functions of a multiple-layer protocol stack, based on the "bypass concept" of a fast path for data transfer. The motivation for identifying this separate processing path is that it involves only a small subset of the complete protocol, which can then be implemented in hardware. Multiple-layer bypass also eliminates some inter-layer operations such as queue and buffer management, context switching and movement of data across layers, all of which are a significant overhead. ROPE is intended to support high-speed bulk data transfer. The paper describes the design of a ROPE chip for the OSI Session and Transport layer protocols, using VHDL. The design is practical in terms of chip complexity and area, using current gate array technology, and simulation shows that it can support a data rate approaching I gigabit per second, in a connection attached to an end-system.

Keyword codes: C.2.2, B.4.1 Keywords: Network Protocols, Data Communications Devices

#### 1 Introduction

The advent of Fibre Optic technology, which offers high bandwidth and low bit error rates, has shifted the performance bottleneck from the communications channel to the communications processing in the end-points of the system [26]. Other trends such as improved quality-of-service guarantees will reinforce this effect. The heavy processing load is due to a combination of operating system overhead, protocol complexity, and per-octe processing on the data stream. To alleviate the end-system bottleneck one may consider new protocols [10], improved software implementation of existing protocols [5, 35], parallel processing techniques [14, 21, 38], special protocol structures [15, 30] and hardware assist [22] by offloading all or part of the protocol functions to an adaptor. This paper takes the latter approach.

The key problems associated with offboard processing include:

□ Partitioning the functionality between the host and the adaptor is difficult and may easily lead to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offloading. For example, the buffer management task [36] may be offloaded, but this leaves the problem of control for accessing it within the full protocol logic.

This research was done while Dr. Thia was at Carleton University

G. Neufield et al. (eds.), *Protocols for High Speed Networks IV* © Springer Science+Business Media Dordrecht 1995

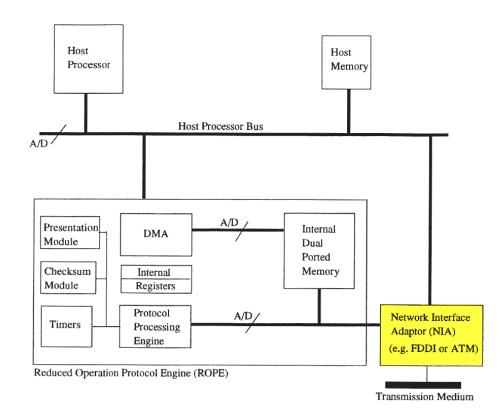

Figure 2 Block Diagram of VLSI bypass system

Ex. 1015.007 (Thia); see also Paper 35 (Reply) at 8; Paper 2 at 75 (Petition).

## Thia + Tanenbaum96 teaches checking for fragmentation in fast-path test

#### THIRD EDITION COMPUTER NETWORKS ANDREW S. TANENBAUM

The TPDU is then checked to see if it is a normal one: the state is *ESTAB*-*LISHED*, neither side is trying to close the connection, the TPDU is a full one, no special flags are set, and the sequence number is the one expected. These tests take just a handful of instructions. If all conditions are met, a special fast path TCP procedure is called.

Ex. 1006.585 (Tanenbaum96); see also Paper 35 (Reply) at 8.

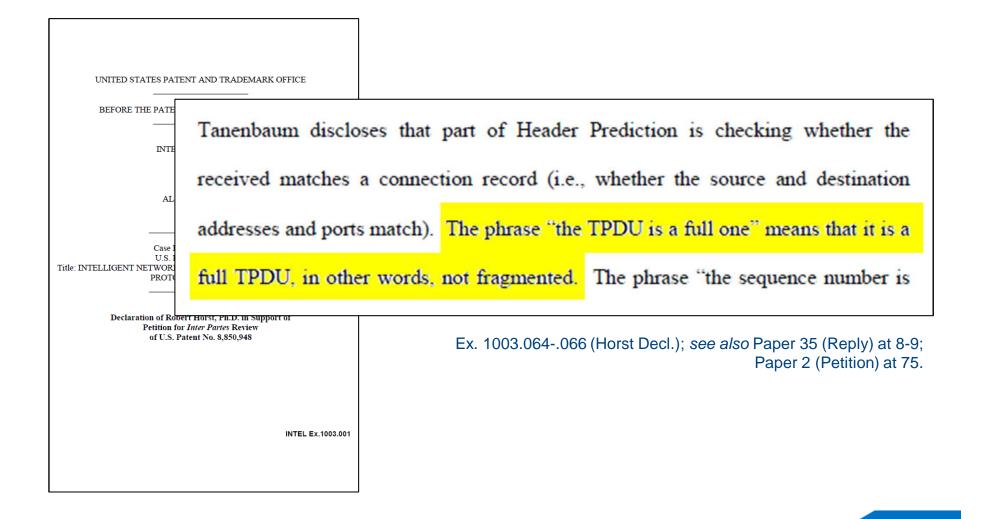

## Undisputed: A POSA would understand "the TPDU is a full one" to mean it is not fragmented

# PO admits a POSA would know how to check for fragmentation

### 948 Patent: Disputes

- 2. The prior art combinations disclose the limitations of the challenged claims of the 948 Patent

- a. The combination discloses a network interface checking whether packets are IP fragmented

- b. The combination discloses checking whether "packets" have certain exception conditions / the combination discloses the protocol stack processing exception conditions

- c. The combination discloses bypassing host protocol stack processing and storing data from packets without exception conditions (Board previously found that Thia and Tanenbaum96 teach this)

### 948 Patent: Claims 1, 17

The invention claimed is:

**1**. A method for network communication by a host computer having a network interface that is connected to the host by an input/output bus, the method comprising:

- running, on the host computer, a protocol processing stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, with an application layer running above the TCP layer;

- initializing, by the host computer, a TCP connection that is defined by source and destination IP addresses and source and destination TCP ports;

- receiving, by the network interface, first and second packets, wherein the first packet has a first TCP header and contains first payload data for the application, and the second packet has a second TCP header and contains second payload data for the application;

- checking, by the network interface, whether the packets have certain exception conditions, including checking whether the packets are IP fragmented, checking whether the packets have a FIN flag set, and checking whether the packets are out of order;

- if the first packet has any of the exception conditions, then protocol processing the first TCP header by the protocol processing stack;

- if the second packet has any of the exception conditions, then protocol processing the second TCP header by the protocol processing stack;

- if the packets do not have any of the exception conditions, then bypassing host protocol processing of the TCP headers and storing the first payload data and the second payload data together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the first payload data and the second payload data.

**17**. An apparatus for network communication, the apparatus comprising:

- a host computer running a protocol stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, the protocol stack adapted to establish a TCP connection for an application layer running above the TCP layer, the TCP connection being defined by source and destination IP addresses and source and destination TCP ports;

- a network interface that is connected to the host computer by an input/output bus, the network interface adapted to parse the headers of received packets to determine whether the headers have the IP addresses and TCP ports that define the TCP connection and to check whether the packets have certain exception conditions, including whether the packets are IP fragmented, have a FIN flag set, or are out of order, the network interface having logic that directs any of the received packets that have the exception conditions to the protocol stack for processing, and directs the received packets that do not have any of the exception conditions to have their headers removed and their payload data stored together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the payload data that came from different packets of the received packets.

Ex. 1001 (948 Patent) at Claim 1, Claim 7.

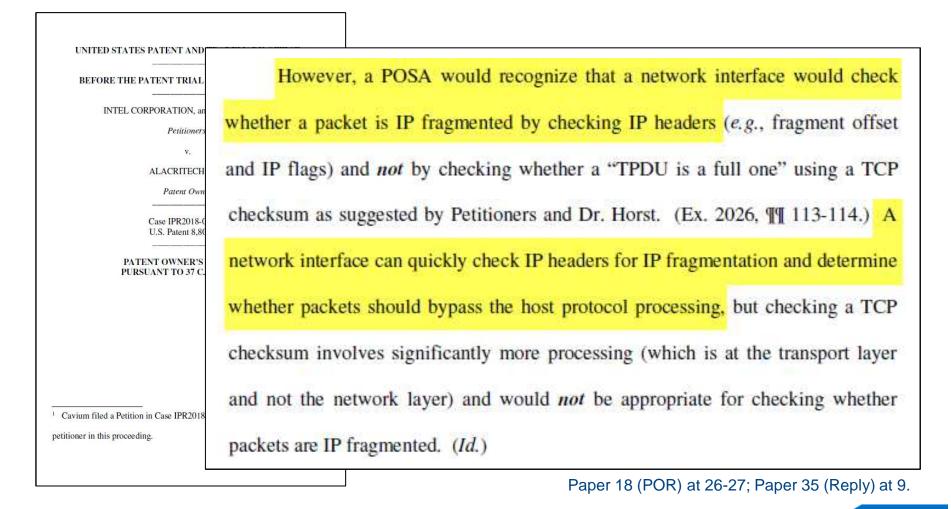

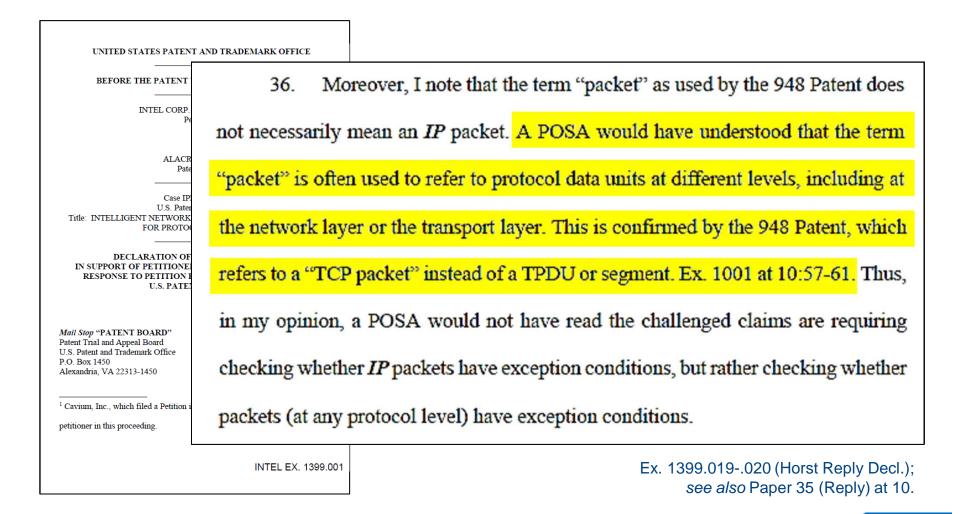

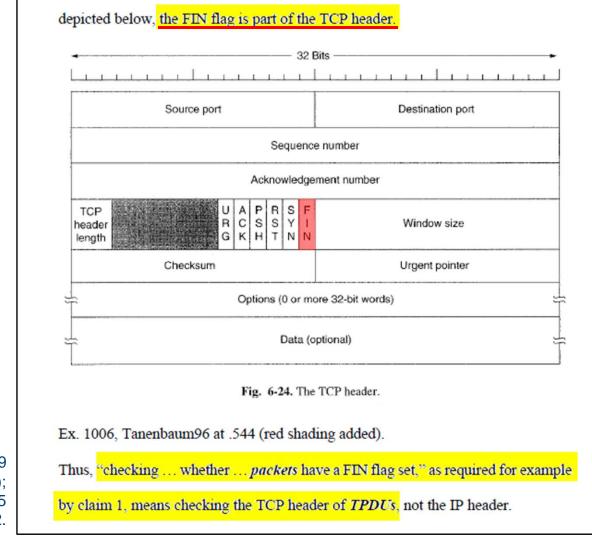

### A POSA would not have understood "packet" to be limited to an IP packet

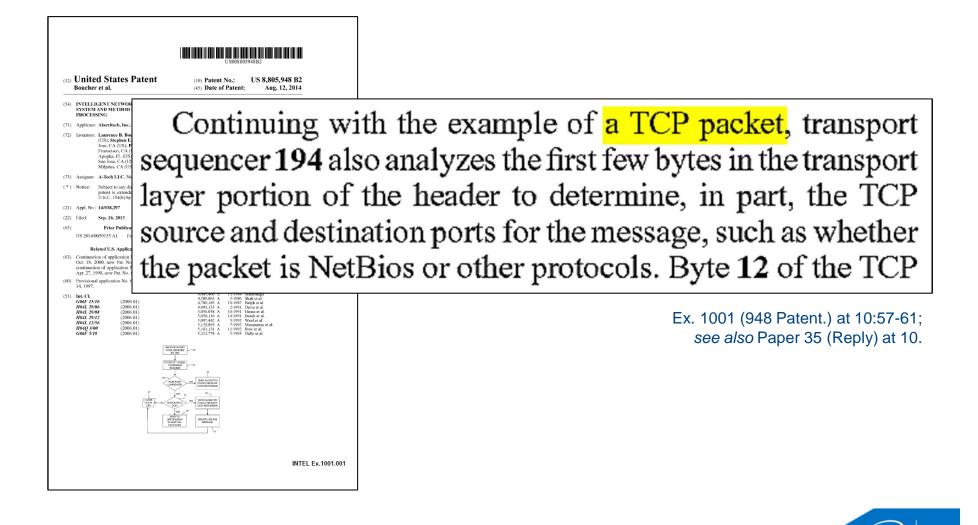

### 948 Patent refers to a "TCP packet" instead of a TPDU or segment; so "packet" not limited to IP

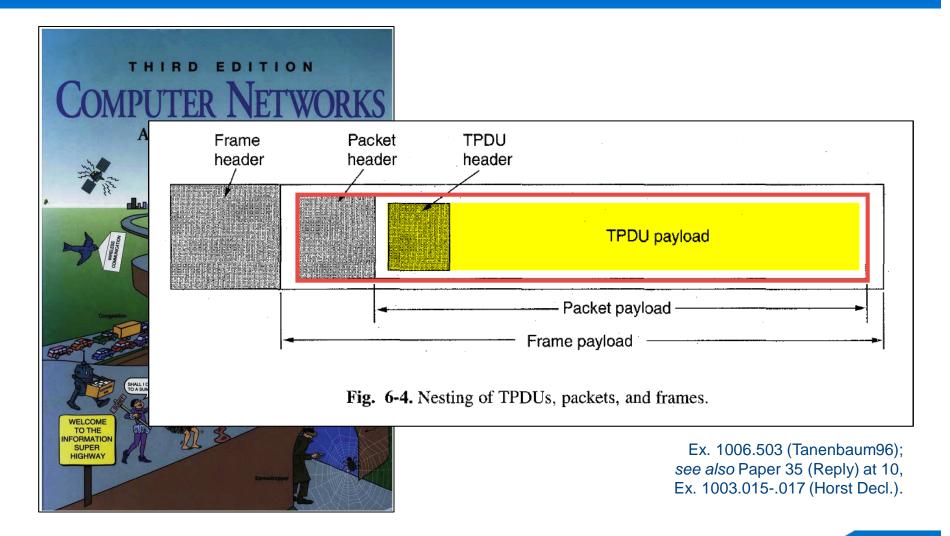

## Even if "packet" meant "IP packet," PO ignores that a TPDU/segment is part of an IP packet

**inte**l

### 948 Patent: Claims 1, 17

The invention claimed is:

**1**. A method for network communication by a host computer having a network interface that is connected to the host by an input/output bus, the method comprising:

- running, on the host computer, a protocol processing stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, with an application layer running above the TCP layer;

- initializing, by the host computer, a TCP connection that is defined by source and destination IP addresses and source and destination TCP ports;

- receiving, by the network interface, first and second packets, wherein the first packet has a first TCP header and contains first payload data for the application, and the second packet has a second TCP header and contains second payload data for the application;

- checking, by the network interface, whether the packets have certain exception conditions, including checking whether the packets are IP fragmented, checking whether the packets have a <u>FIN flag</u> set, and checking whether the packets are out of order;

- if the first packet has any of the exception conditions, then protocol processing the first TCP header by the protocol processing stack;

- if the second packet has any of the exception conditions, then protocol processing the second TCP header by the protocol processing stack;

- if the packets do not have any of the exception conditions, then bypassing host protocol processing of the TCP headers and storing the first payload data and the second payload data together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the first payload data and the second payload data.

**17**. An apparatus for network communication, the apparatus comprising:

- a host computer running a protocol stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, the protocol stack adapted to establish a TCP connection for an application layer running above the TCP layer, the TCP connection being defined by source and destination IP addresses and source and destination TCP ports;

- a network interface that is connected to the host computer by an input/output bus, the network interface adapted to parse the headers of received packets to determine whether the headers have the IP addresses and TCP ports that define the TCP connection and to check whether the packets have certain exception conditions, including whether the packets are IP fragmented, have a FIN flag set, or are out of order, the network interface having logic that directs any of the received packets that have the exception conditions to the protocol stack for processing, and directs the received packets that do not have any of the exception conditions to have their headers removed and their payload data stored together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the payload data that came from different packets of the received packets.

Ex. 1001 (948 Patent) at Claim 1, Claim 7.

## Checking a characteristic of a TPDU is checking whether the IP packet has that characteristic

Ex. 1399.017-.019 (Horst Reply Decl.); *see also* Paper 35 (Reply) at 11-12.

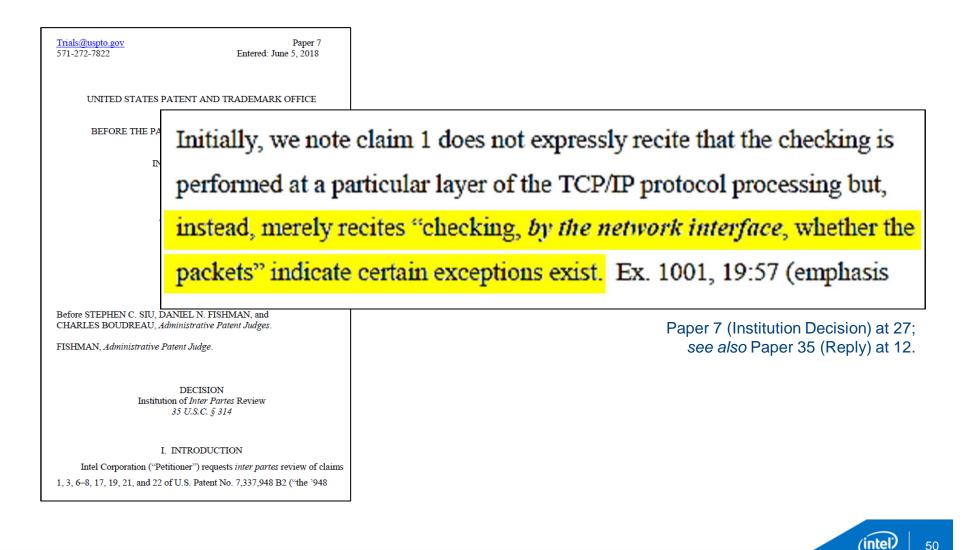

#### Institution Decision correctly noted the claims do not expressly recite checking at a particular layer

# Even if checking the network layer header were required (it is not), Thia does this

14 A Reduced Operation Protocol Engine (ROPE) for a multiple-layer bypass architecture Y.H. Thia (\*)<sup>1</sup> and C.M. Woodside (\*\*) Newbridge Networks, Inc., Ottawa Dept. of Systems and Computer The receive bypass test matches the incoming PDU headers with a template that phase. Abstract - The Reduced O critical functions of a multiple-la identifies the predicted bypassable headers. The bypass stack performs all the relevant path for data transfer. The motiv involves only a small subset of hardware. Multiple-layer bypass and buffer management, context switching and movement of data across layers, all of which are a significant overhead. ROPE is intended to support high-speed bulk data transfer. The Ex. 1015.003 (Thia); see also Paper 35 (Reply) at 12 n.4; paper describes the design of a ROPE chip for the OSI Session and Transport layer protocols, using VHDL. The design is practical in terms of chip complexity and area, using current gate array technology, and simulation shows that it can support a data rate approaching 1 gigabit Paper 2 (Petition) at 77. per second, in a connection attached to an end-system. Keyword codes: C.2.2, B.4.1 Keywords: Network Protocols, Data Communications Devices 1 Introduction The advent of Fibre Optic technology, which offers high bandwidth and low bit error rates, has shifted the performance bottleneck from the communications channel to the communications processing in the end-points of the system [26]. Other trends such as improved quality-of-service guarantees will reinforce this effect. The heavy processing load is due to a combination of operating system overhead, protocol complexity, and per-octet processing on the data stream. To alleviate the end-system bottleneck one may consider new protocols [10], improved software implementation of existing protocols [5, 35], parallel processing techniques [14, 21, 38], special protocol structures [15, 30] and hardware assist [22] by offloading all or part of the protocol functions to an adaptor. This paper takes the latter approach. The key problems associated with offboard processing include: □ Partitioning the functionality between the host and the adaptor is difficult and may easily lead to a complex additional protocol between the two parts, which may cancel out or offset the potential gain from offloading. For example, the buffer management task [36] may be offloaded, but this leaves the problem of control for accessing it within the full protocol logic. This research was done while Dr. This was at Carleton University G. Neufield et al. (eds.), Protocols for High Speed Networks IV © Springer Science+Business Media Dordrecht 1995

## Even if checking the IP header were required (it is not), Header Prediction does this

#### THIRD EDITION COMPUTER NETWORKS

Now let us look at fast path processing on the receiving side of Fig. 6-49. Step 1 is locating the connection record for the incoming TPDU. For ATM, finding the connection record is easy: the *VPI* field can be used as an index into the path table to find the virtual circuit table for that path and the *VCI* can be used as an index to find the connection record. For TCP, the connection record can be stored in a hash table for which some simple function of the two IP addresses and two ports is the key. Once the connection record has been located, both addresses and both ports must be compared to verify that the correct record has been found.

Ex.1006.584-.585 (Tanenbaum96); see also Paper 35 (Reply) at 12.

## PO makes the same flawed arguments regarding the protocol processing limitations

| UNITED STATES PATENT AND TRADEMARK<br><br>BEFORE THE PATENT TRIAL AND APPEAL F<br><br>INTEL CORPORATION, and CAVIUM, INC<br>Petitioners,<br>v.<br>ALACRITECH INC., | C. The Combination Does Not Show or Suggest "if the first packet<br>has any of the exception conditions, then protocol processing the<br>first TCP header by the protocol processing stack; [and] if the<br>second packet has any of the exception conditions, then protocol<br>processing the second TCP header by the protocol processing<br>stack" (claim 1) / "the network interface having logic that directs<br>any of the received packets that have the exception conditions to<br>the protocol stack for processing" (claim 17) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Patent Owner                                                                                                                                                       | These limitations are conditioned upon "check[ing] whether the packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Case IPR2018-00234 <sup>1</sup><br>U.S. Patent 8,805,948                                                                                                           | have certain exception conditions." As explained above, in Sections VIII.A-B, the                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PATENT OWNER'S RESPONSE<br>PURSUANT TO 37 C.F.R. § 42.120                                                                                                          | combination fails to disclose "check[ing] whether the packets have certain                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                    | exception conditions, including whether the packets are IP fragmented."                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                    | Accordingly, the combination cannot disclose these limitations for at least the                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                    | reason that they are conditioned upon "check[ing] whether the packets have certain                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <sup>1</sup> Cavium filed a Petition in Case IPR2018-00403 and has be<br>petitioner in this proceeding.                                                            | exception conditions." (Ex. 2026, ¶ 121.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

(intel)

### 948 Patent: Disputes

- 2. The prior art combinations disclose the limitations of the challenged claims of the 948 Patent

- a. The combination discloses a network interface checking whether packets are IP fragmented

- b. The combination discloses checking whether "packets" have certain exception conditions / the combination discloses the protocol stack processing exception conditions

- c. The combination discloses bypassing host protocol stack processing and storing data from packets without exception conditions (Board previously found that Thia and Tanenbaum96 teach this)

### 948 Patent: Claims 1, 17

The invention claimed is:

**1**. A method for network communication by a host computer having a network interface that is connected to the host by an input/output bus, the method comprising:

- running, on the host computer, a protocol processing stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, with an application layer running above the TCP layer;

- initializing, by the host computer, a TCP connection that is defined by source and destination IP addresses and source and destination TCP ports;

- receiving, by the network interface, first and second packets, wherein the first packet has a first TCP header and contains first payload data for the application, and the second packet has a second TCP header and contains second payload data for the application;

- checking, by the network interface, whether the packets have certain exception conditions, including checking whether the packets are IP fragmented, checking whether the packets have a FIN flag set, and checking whether the packets are out of order;

- if the first packet has any of the exception conditions, then protocol processing the first TCP header by the protocol processing stack;

- if the second packet has any of the exception conditions, then protocol processing the second TCP header by the protocol processing stack;

- if the packets do not have any of the exception conditions, then bypassing host protocol processing of the TCP headers and storing the first payload data and the second payload data together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the first payload data and the second payload data.

**17**. An apparatus for network communication, the apparatus comprising:

- a host computer running a protocol stack including an Internet Protocol (IP) layer and a Transmission Control Protocol (TCP) layer, the protocol stack adapted to establish a TCP connection for an application layer running above the TCP layer, the TCP connection being defined by source and destination IP addresses and source and destination TCP ports;

- a network interface that is connected to the host computer by an input/output bus, the network interface adapted to parse the headers of received packets to determine whether the headers have the IP addresses and TCP ports that define the TCP connection and to check whether the packets have certain exception conditions, including whether the packets are IP fragmented, have a FIN flag set, or are out of order, the network interface having logic that directs any of the received packets that have the exception conditions to the protocol stack for processing, and directs the received packets that do not have any of the exception conditions to have their headers removed and their payload data stored together in a buffer of the host computer, such that the payload data is stored in the buffer in order and without any TCP header stored between the payload data that came from different packets of the received packets.

Ex. 1001 (948 Patent) at Claim 1, Claim 7.

### The Board previously found Thia and Tanenbaum96 teach storing data on the host without TCP headers

Trials@uspto.gov 571-272-7822 E UNITED STATES PATENT AND TRAD BEFORE THE PATENT TRIAL AND A INTEL CORPORATION, CAVIUM, LLC Petitioner v. ALACRITECH. INC Patent Owner. Case IPR2017-01409 Patent 8,131,880 B2 Before STEPHEN C. SIU, DANIEL N. FISHMAN CHARLES J. BOUDREAU, Administrative Pater SIU, Administrative Patent Judge. FINAL WRITTEN DECISI 35 U.S.C. § 318(a) <sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2 Inc., which filed a Petition in Case IPR2018-0033

Patent Owner argues that Thia "merely states that the data portion of a packet may be copied" but "does not disclose or even suggest copying the data portion of a PDU *without transferring* the corresponding transport layer header." PO Resp. 46–47. However, as Petitioner points out, the combination of Thia and Tanenbaum discloses receiving a packet with a header and data portion and transferring the "data portion" of the packet to the host system memory. Patent Owner does not assert or demonstrate persuasively that Thia also discloses transferring the "header portion" of the packet to the host system memory. We are not persuaded by Patent Owner's argument. A skilled artisan would have understood that the data portion of the packet is transmitted to the host computer without the header.

petitioners in this proceeding. According to updated mandatory notices filed in this proceeding. Cavium, Inc. has now been converted to Cavium, LLC. Paper 74.

IPR2017-01409 Paper 79 (FWD) at 10-11; see also Paper 35 (Reply) at 13.

## PO cites to Thia's TX (not RX) disclosures, to argue Thia transfers a whole PDU to the host

### Dr. Horst (and Dr. Lin) explain that Thia's disclosure is for transmitting data

UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

INTEL CORP. and CAVIUM, INC., Petitioner,

> v. ALACRITECH, INC., Patent Owner.

Case IPR2018-00234<sup>1</sup> U.S. Patent No. 8,805,948 Title: INTELLIGENT NETWORK INTERFACE SYSTEM AND METHOD FOR PROTOCOL PROCESSING

DECLARATION OF ROBERT HORST, PH.D., IN SUPPORT OF PETITIONER'S REPLY TO PATENT OWNER'S RESPONSE TO PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 8,806,5948

Mail Stop "PATENT BOARD" Patent Trial and Appeal Board U.S. Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450

<sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2018-00403, has been joined as

petitioner in this proceeding.

INTEL EX. 1399.00

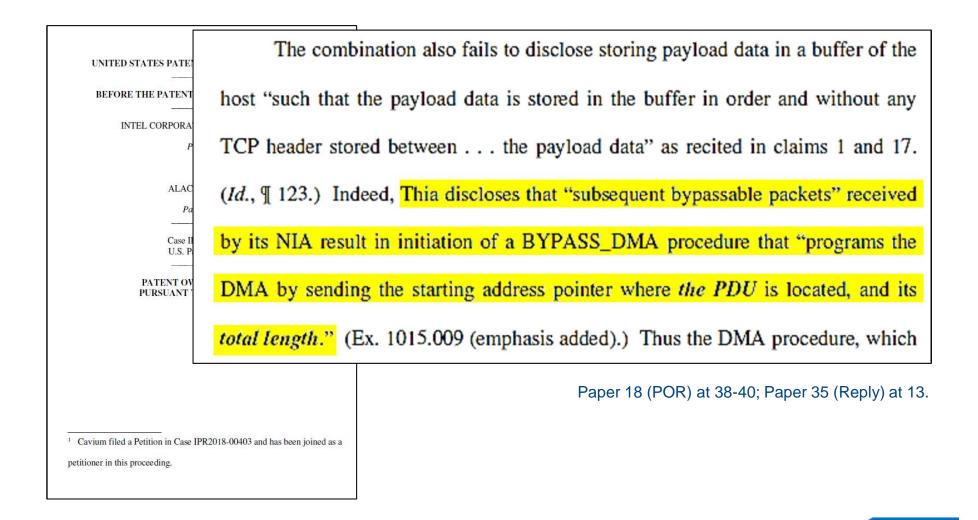

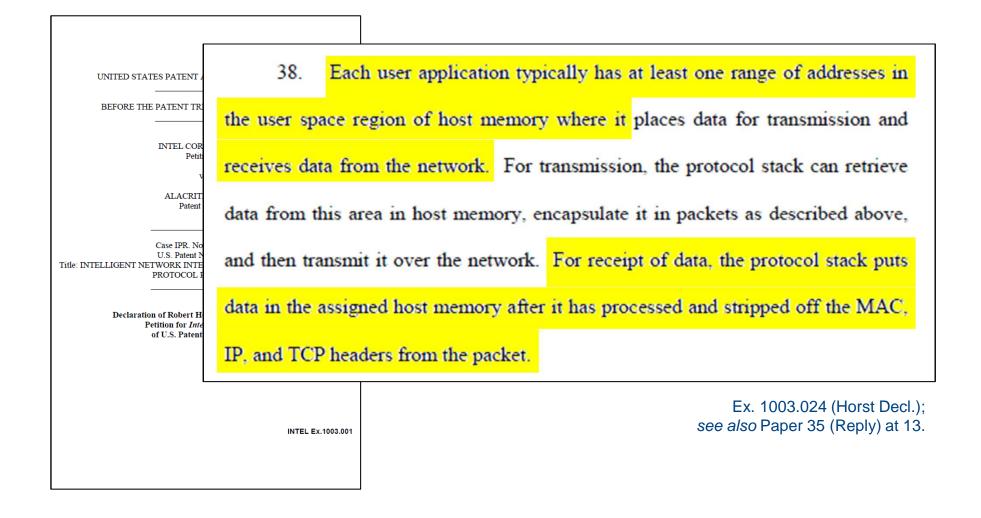

As explained by Dr. Lin in the 1410 Lin Reply Decl. (¶ 30), this 39. disclosure is actually describing that the host computer sends an entire packet (or PDU) to the internal dual ported memory of the ROPE chip for transmission on a network. It does not describe receiving a packet from the network and transferring data from the ROPE chip to the host. Specifically, it states that "the host" is what "initiates the BYPASS\_DMA procedure" and "programs the DMA by sending the starting address pointer where the PDU is located ..." In other words, the host sends the location of where the PDU is located on the host. "The destination address" for where to send the PDU from the host is "supplied by the bypass chip," and then "DMA transfers the PDU into the internal dual-ported SRAM" of the ROPE chip. See Ex. 1015, Thia at .009; see also id. at .007, Fig. 2 (illustrating the ROPE chip's "Internal Dual Ported Memory"). Thus, a major premise of Dr. Almeroth's analysis in paragraphs 122 through 128 is false.

Ex. 1399.021-.022 (Horst Reply Decl.); see also Paper 35 (Reply) at 13.

### TCP/IP strips off headers

#### Thia discloses transferring data to the host from the ROPE chip after processing the packet

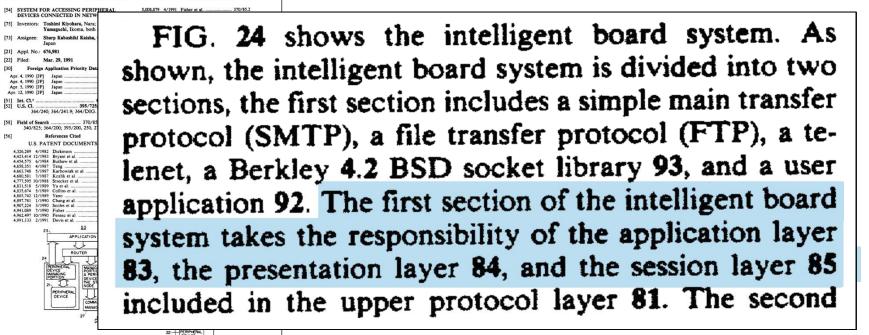

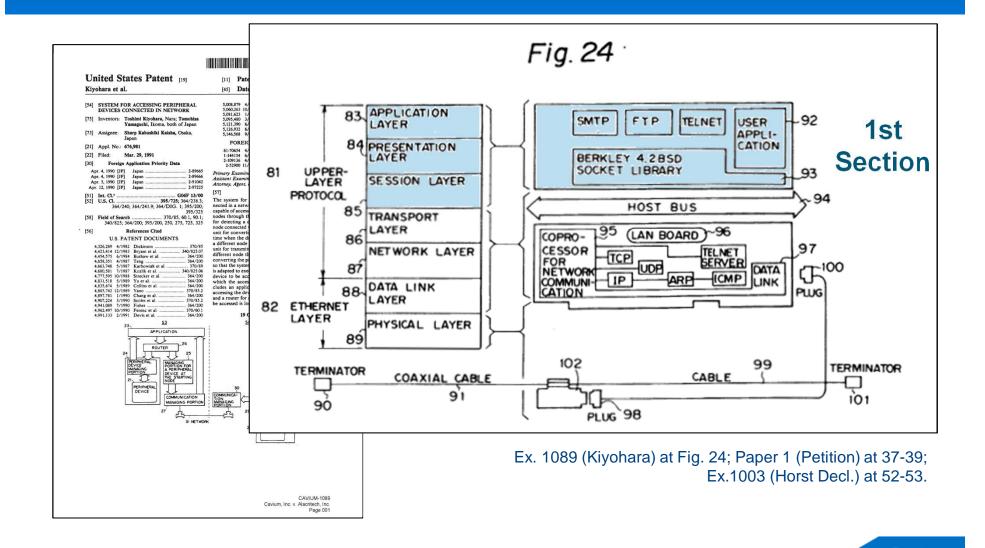

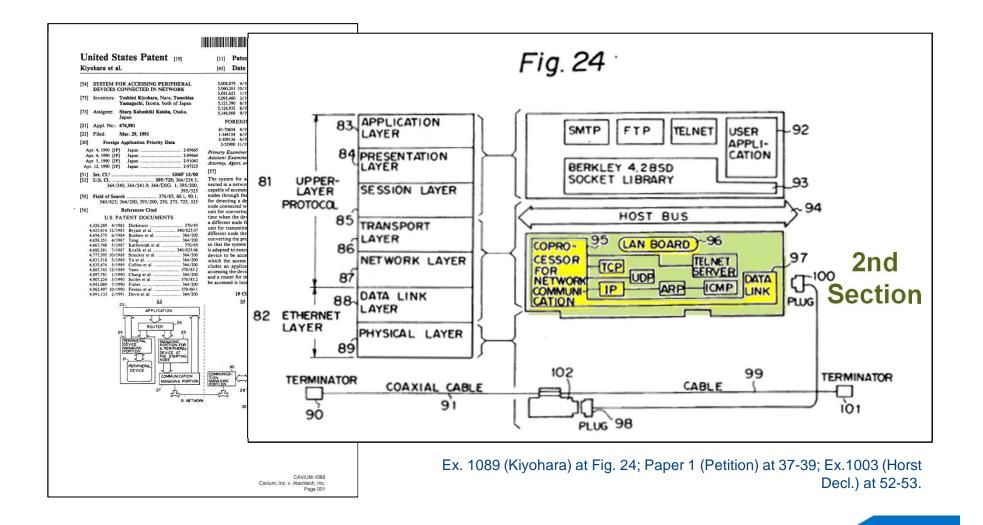

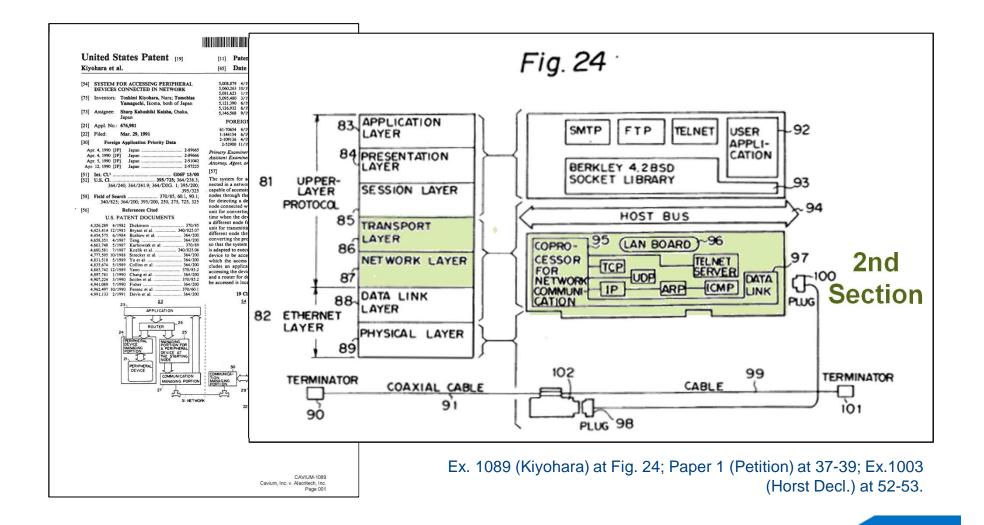

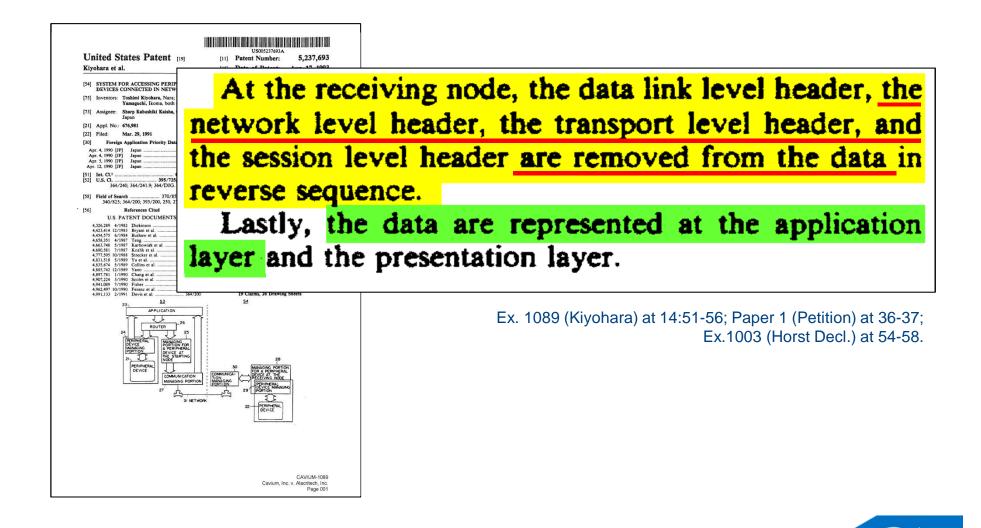

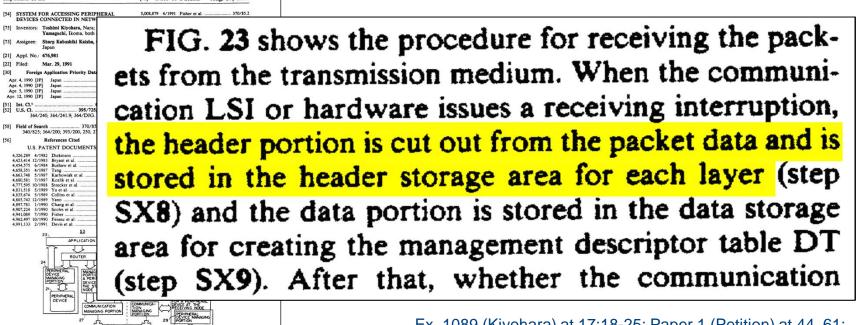

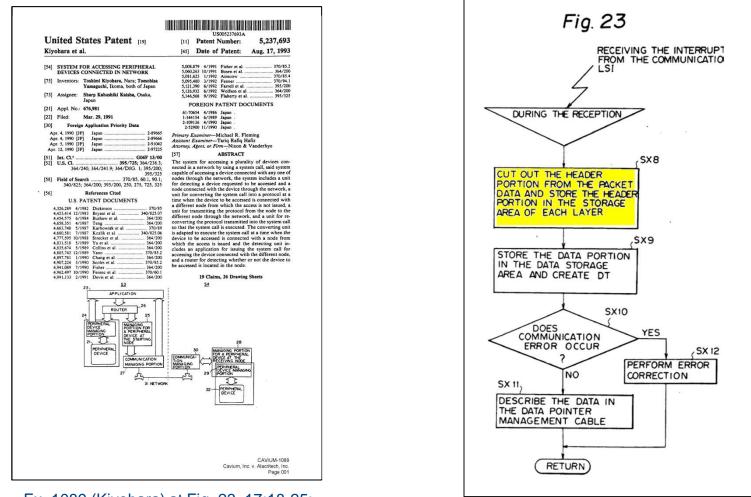

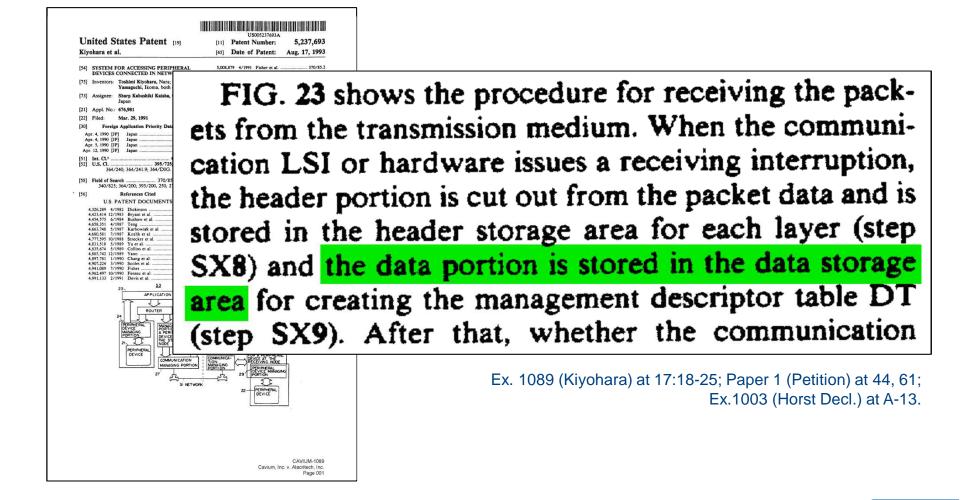

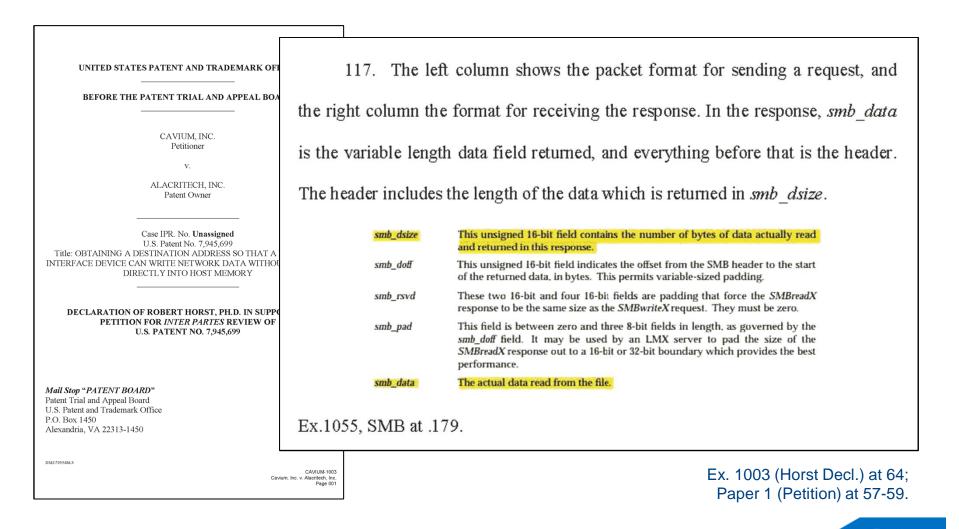

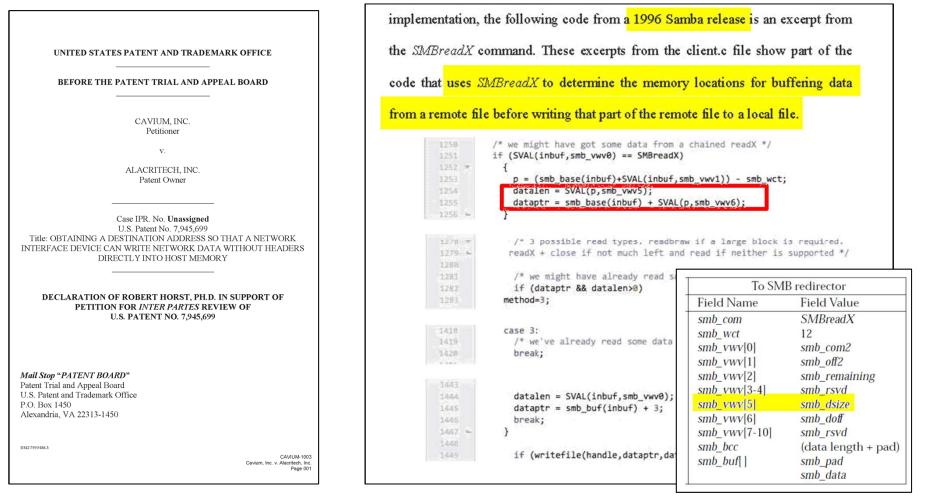

| 14<br>A Reduced Operation Protocol Engine (ROPE) for a<br>multiple-layer bypass architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                |  |