Feature selectors are used when enabling or setting features, such as remote wakeup, specific to a device, interface, or endpoint. The values for the feature selectors are given in Table 9-6.

Table 9-6. Standard Feature Selectors

| Feature Selector     | Recipient | Value |

|----------------------|-----------|-------|

| DEVICE_REMOTE_WAKEUP | Device    | 1     |

| ENDPOINT_HALT        | Endpoint  | 0     |

| TEST_MODE            | Device    | 2     |

If an unsupported or invalid request is made to a USB device, the device responds by returning STALL in the Data or Status stage of the request. If the device detects the error in the Setup stage, it is preferred that the device returns STALL at the earlier of the Data or Status stage. Receipt of an unsupported or invalid request does NOT cause the optional *Halt* feature on the control pipe to be set. If for any reason, the device becomes unable to communicate via its Default Control Pipe due to an error condition, the device must be reset to clear the condition and restart the Default Control Pipe.

#### 9.4.1 Clear Feature

This request is used to clear or disable a specific feature.

| bmRequestType                       | bRequest      | wValue              | windex                        | wLength | Data |

|-------------------------------------|---------------|---------------------|-------------------------------|---------|------|

| 00000000B<br>00000001B<br>00000010B | CLEAR_FEATURE | Feature<br>Selector | Zero<br>Interface<br>Endpoint | Zero    | None |

Feature selector values in wValue must be appropriate to the recipient. Only device feature selector values may be used when the recipient is a device, only interface feature selector values may be used when the recipient is an interface, and only endpoint feature selector values may be used when the recipient is an endpoint.

Refer to Table 9-6 for a definition of which feature selector values are defined for which recipients.

A ClearFeature() request that references a feature that cannot be cleared, that does not exist, or that references an interface or endpoint that does not exist, will cause the device to respond with a Request Error.

If wLength is non-zero, then the device behavior is not specified.

Default state: Device behavior when this request is received while the device is in the Default state

is not specified.

Address state: This request is valid when the device is in the Address state; references to interfaces

or to endpoints other than endpoint zero shall cause the device to respond with a

Request Error.

Configured state: This request is valid when the device is in the Configured state.

Note: The Test Mode feature cannot be cleared by the ClearFeature() request.

## 9.4.2 Get Configuration

This request returns the current device configuration value.

| bmRequestType | bRequest          | wValue | windex | wLength | Data                   |

|---------------|-------------------|--------|--------|---------|------------------------|

| 10000000B     | GET_CONFIGURATION | Zero   | Zero   | One     | Configuration<br>Value |

If the returned value is zero, the device is not configured.

If wValue, wIndex, or wLength are not as specified above, then the device behavior is not specified.

**Default state:** Device behavior when this request is received while the device is in the Default state

is not specified.

Address state: The value zero must be returned.

Configured state: The non-zero bConfigurationValue of the current configuration must be returned.

## 9.4.3 Get Descriptor

This request returns the specified descriptor if the descriptor exists.

| bmRequestType | bRequest       | wValue                                        | windex                                                | wLength              | Data       |

|---------------|----------------|-----------------------------------------------|-------------------------------------------------------|----------------------|------------|

| 10000000В     | GET_DESCRIPTOR | Descriptor<br>Type and<br>Descriptor<br>Index | Zero or<br>Language ID<br>(refer to<br>Section 9.6.7) | Descriptor<br>Length | Descriptor |

The wValue field specifies the descriptor type in the high byte (refer to Table 9-5) and the descriptor index in the low byte. The descriptor index is used to select a specific descriptor (only for configuration and string descriptors) when several descriptors of the same type are implemented in a device. For example, a device can implement several configuration descriptors. For other standard descriptors that can be retrieved via a GetDescriptor() request, a descriptor index of zero must be used. The range of values used for a descriptor index is from 0 to one less than the number of descriptors of that type implemented by the device.

The wIndex field specifies the Language ID for string descriptors or is reset to zero for other descriptors. The wLength field specifies the number of bytes to return. If the descriptor is longer than the wLength field, only the initial bytes of the descriptor are returned. If the descriptor is shorter than the wLength field, the device indicates the end of the control transfer by sending a short packet when further data is requested. A short packet is defined as a packet shorter than the maximum payload size or a zero length data packet (refer to Chapter 5).

The standard request to a device supports three types of descriptors: device (also device\_qualifier), configuration (also other\_speed\_configuration), and string. A high-speed capable device supports the device\_qualifier descriptor to return information about the device for the speed at which it is not operating (including wMaxPacketSize for the default endpoint and the number of configurations for the other speed). The other\_speed\_configuration returns information in the same structure as a configuration descriptor, but for a configuration if the device were operating at the other speed. A request for a configuration descriptor returns the configuration descriptor, all interface descriptors, and endpoint descriptors for all of the

interfaces in a single request. The first interface descriptor follows the configuration descriptor. The endpoint descriptors for the first interface follow the first interface descriptor. If there are additional interfaces, their interface descriptor and endpoint descriptors follow the first interface's endpoint descriptors. Class-specific and/or vendor-specific descriptors follow the standard descriptors they extend or modify.

All devices must provide a device descriptor and at least one configuration descriptor. If a device does not support a requested descriptor, it responds with a Request Error.

**Default state:** This is a valid request when the device is in the Default state.

Address state: This is a valid request when the device is in the Address state.

Configured state: This is a valid request when the device is in the Configured state.

## 9.4.4 Get Interface

This request returns the selected alternate setting for the specified interface.

| bmRequestType | bRequest      | wValue | windex    | wLength | Data                 |

|---------------|---------------|--------|-----------|---------|----------------------|

| 10000001B     | GET_INTERFACE | Zero   | Interface | One     | Alternate<br>Setting |

Some USB devices have configurations with interfaces that have mutually exclusive settings. This request allows the host to determine the currently selected alternate setting.

If wValue or wLength are not as specified above, then the device behavior is not specified.

If the interface specified does not exist, then the device responds with a Request Error.

Default state: Device behavior when this request is received while the device is in the Default state

is not specified.

Address state: A Request Error response is given by the device.

**Configured state**: This is a valid request when the device is in the Configured state.

#### 9.4.5 Get Status

This request returns status for the specified recipient.

| bmRequestType                       | bRequest   | wValue | windex                        | wLength | Data                                           |

|-------------------------------------|------------|--------|-------------------------------|---------|------------------------------------------------|

| 10000000B<br>10000001B<br>10000010B | GET_STATUS | Zero   | Zero<br>Interface<br>Endpoint | Two     | Device,<br>Interface, or<br>Endpoint<br>Status |

The Recipient bits of the bmRequestType field specify the desired recipient. The data returned is the current status of the specified recipient.

If wValue or wLength are not as specified above, or if wIndex is non-zero for a device status request, then the behavior of the device is not specified.

If an interface or an endpoint is specified that does not exist, then the device responds with a Request Error.

Default state: Device behavior when this request is received while the device is in the Default state

is not specified.

Address state: If an interface or an endpoint other than endpoint zero is specified, then the device

responds with a Request Error.

Configured state: If an interface or endpoint that does not exist is specified, then the device responds

with a Request Error.

A GetStatus() request to a device returns the information shown in Figure 9-4.

| erved (Reset to zero | )   |                                      | Remote | Self    |

|----------------------|-----|--------------------------------------|--------|---------|

|                      |     |                                      | Wakeup | Powered |

| D12                  | D11 | D10                                  | D9     | D8      |

| ).                   |     | 13 D12 D11  Reserved (Reset to zero) |        |         |

Figure 9-4. Information Returned by a GetStatus() Request to a Device

The *Self Powered* field indicates whether the device is currently self-powered. If D0 is reset to zero, the device is bus-powered. If D0 is set to one, the device is self-powered. The *Self Powered* field may not be changed by the SetFeature() or ClearFeature() requests.

The Remote Wakeup field indicates whether the device is currently enabled to request remote wakeup. The default mode for devices that support remote wakeup is disabled. If D1 is reset to zero, the ability of the device to signal remote wakeup is disabled. If D1 is set to one, the ability of the device to signal remote wakeup is enabled. The Remote Wakeup field can be modified by the SetFeature() and ClearFeature() requests using the DEVICE\_REMOTE\_WAKEUP feature selector. This field is reset to zero when the device is reset.

A GetStatus() request to an interface returns the information shown in Figure 9-5.

| D7  | D6  | D5  | D4          | D3            | D2  | D1 | D0 |

|-----|-----|-----|-------------|---------------|-----|----|----|

|     |     |     | Reserved (R | eset to zero) |     |    |    |

| D15 | D14 | D13 | D12         | D11           | D10 | D9 | D8 |

|     |     |     | Reserved (R | eset to zero) |     |    |    |

Figure 9-5. Information Returned by a GetStatus() Request to an Interface

A GetStatus() request to an endpoint returns the information shown in Figure 9-6.

| D7  | D6  | D5    | D4            | D3            | D2  | D1 | D0   |

|-----|-----|-------|---------------|---------------|-----|----|------|

|     |     | Reser | ved (Reset to | zero)         |     |    | Halt |

| D15 | D14 | D13   | D12           | D11           | D10 | D9 | D8   |

|     |     |       | Reserved (R   | eset to zero) |     |    |      |

Figure 9-6. Information Returned by a GetStatus() Request to an Endpoint

The *Halt* feature is required to be implemented for all interrupt and bulk endpoint types. If the endpoint is currently halted, then the *Halt* feature is set to one. Otherwise, the *Halt* feature is reset to zero. The *Halt* feature may optionally be set with the SetFeature(ENDPOINT\_HALT) request. When set by the SetFeature() request, the endpoint exhibits the same stall behavior as if the field had been set by a hardware condition. If the condition causing a halt has been removed, clearing the *Halt* feature via a ClearFeature(ENDPOINT\_HALT) request results in the endpoint no longer returning a STALL. For endpoints using data toggle, regardless of whether an endpoint has the *Halt* feature set, a ClearFeature(ENDPOINT\_HALT) request always results in the data toggle being reinitialized to DATA0. The *Halt* feature is reset to zero after either a SetConfiguration() or SetInterface() request even if the requested configuration or interface is the same as the current configuration or interface.

It is neither required nor recommended that the *Halt* feature be implemented for the Default Control Pipe. However, devices may set the *Halt* feature of the Default Control Pipe in order to reflect a functional error condition. If the feature is set to one, the device will return STALL in the Data and Status stages of each standard request to the pipe except GetStatus(), SetFeature(), and ClearFeature() requests. The device need not return STALL for class-specific and vendor-specific requests.

## 9.4.6 Set Address

This request sets the device address for all future device accesses.

| bmRequestType | bRequest    | wValue            | wIndex | wLength | Data |

|---------------|-------------|-------------------|--------|---------|------|

| 00000000B     | SET_ADDRESS | Device<br>Address | Zero   | Zero    | None |

The wValue field specifies the device address to use for all subsequent accesses.

As noted elsewhere, requests actually may result in up to three stages. In the first stage, the Setup packet is sent to the device. In the optional second stage, data is transferred between the host and the device. In the final stage, status is transferred between the host and the device. The direction of data and status transfer depends on whether the host is sending data to the device or the device is sending data to the host. The Status stage transfer is always in the opposite direction of the Data stage. If there is no Data stage, the Status stage is from the device to the host.

Stages after the initial Setup packet assume the same device address as the Setup packet. The USB device does not change its device address until after the Status stage of this request is completed successfully. Note that this is a difference between this request and all other requests. For all other requests, the operation indicated must be completed before the Status stage.

If the specified device address is greater than 127, or if wIndex or wLength are non-zero, then the behavior of the device is not specified.

Device response to SetAddress() with a value of 0 is undefined.

**Default state:** If the address specified is non-zero, then the device shall enter the Address state;

otherwise, the device remains in the Default state (this is not an error condition).

Address state: If the address specified is zero, then the device shall enter the Default state;

otherwise, the device remains in the Address state but uses the newly-specified

address.

Configured state: Device behavior when this request is received while the device is in the Configured

state is not specified.

## 9.4.7 Set Configuration

This request sets the device configuration.

| bmRequestType | bRequest          | wValue              | windex | wLength | Data |

|---------------|-------------------|---------------------|--------|---------|------|

| 0000000B      | SET_CONFIGURATION | Configuration Value | Zero   | Zero    | None |

The lower byte of the wValue field specifies the desired configuration. This configuration value must be zero or match a configuration value from a configuration descriptor. If the configuration value is zero, the device is placed in its Address state. The upper byte of the wValue field is reserved.

If wIndex, wLength, or the upper byte of wValue is non-zero, then the behavior of this request is not specified.

**Default state:** Device behavior when this request is received while the device is in the Default state

is not specified.

Address state: If the specified configuration value is zero, then the device remains in the Address

state. If the specified configuration value matches the configuration value from a configuration descriptor, then that configuration is selected and the device enters the

Configured state. Otherwise, the device responds with a Request Error.

Configured state: If the specified configuration value is zero, then the device enters the Address state.

If the specified configuration value matches the configuration value from a

configuration descriptor, then that configuration is selected and the device remains in

the Configured state. Otherwise, the device responds with a Request Error.

## 9.4.8 Set Descriptor

This request is optional and may be used to update existing descriptors or new descriptors may be added.

| bmRequestType | bRequest       | wValue                                        | windex                                                | wLength              | Data       |

|---------------|----------------|-----------------------------------------------|-------------------------------------------------------|----------------------|------------|

| 00000000В     | SET_DESCRIPTOR | Descriptor<br>Type and<br>Descriptor<br>Index | Language ID<br>(refer to<br>Section 9.6.7)<br>or zero | Descriptor<br>Length | Descriptor |

The wValue field specifies the descriptor type in the high byte (refer to Table 9-5) and the descriptor index in the low byte. The descriptor index is used to select a specific descriptor (only for configuration and string descriptors) when several descriptors of the same type are implemented in a device. For example, a device can implement several configuration descriptors. For other standard descriptors that can be set via a SetDescriptor() request, a descriptor index of zero must be used. The range of values used for a descriptor index is from 0 to one less than the number of descriptors of that type implemented by the device.

The wIndex field specifies the Language ID for string descriptors or is reset to zero for other descriptors. The wLength field specifies the number of bytes to transfer from the host to the device.

The only allowed values for descriptor type are device, configuration, and string descriptor types.

If this request is not supported, the device will respond with a Request Error.

Default state:

Device behavior when this request is received while the device is in the Default state

is not specified.

Address state:

If supported, this is a valid request when the device is in the Address state.

Configured state:

If supported, this is a valid request when the device is in the Configured state.

#### 9.4.9 Set Feature

This request is used to set or enable a specific feature.

| bmRequestType                       | bRequest    | wValue              | winde         | ex                            | wLength | Data |

|-------------------------------------|-------------|---------------------|---------------|-------------------------------|---------|------|

| 00000000B<br>00000001B<br>00000010B | SET_FEATURE | Feature<br>Selector | Test Selector | Zero<br>Interface<br>Endpoint | Zero    | None |

Feature selector values in wValue must be appropriate to the recipient. Only device feature selector values may be used when the recipient is a device; only interface feature selector values may be used when the recipient is an interface, and only endpoint feature selector values may be used when the recipient is an endpoint.

Refer to Table 9-6 for a definition of which feature selector values are defined for which recipients.

The TEST\_MODE feature is only defined for a device recipient (i.e., bmRequestType = 0) and the lower byte of wIndex must be zero. Setting the TEST\_MODE feature puts the device upstream facing port into test mode. The device will respond with a request error if the request contains an invalid test selector. The transition to test mode must be complete no later than 3 ms after the completion of the status stage of the request. The transition to test mode of an upstream facing port must not happen until after the status stage of the request. The power to the device must be cycled to exit test mode of an upstream facing port of a device. See Section 7.1.20 for definitions of each test mode. A device must support the TEST\_MODE feature when in the Default, Address or Configured high-speed device states.

A SetFeature() request that references a feature that cannot be set or that does not exist causes a STALL to be returned in the Status stage of the request.

Table 9-7. Test Mode Selectors

| Value   | Description                              |

|---------|------------------------------------------|

| 00H     | Reserved                                 |

| 01H     | Test_J                                   |

| 02H     | Test_K                                   |

| 03H     | Test_SE0_NAK                             |

| 04H     | Test_Packet                              |

| 05H     | Test_Force_Enable                        |

| 06H-3FH | Reserved for standard test selectors     |

| 3FH-BFH | Reserved                                 |

| C0H-FFH | Reserved for vendor-specific test modes. |

If the feature selector is *TEST\_MODE*, then the most significant byte of *wIndex* is used to specify the specific test mode. The recipient of a SetFeature(TEST\_MODE...) must be the device; i.e., the lower byte of *wIndex* must be zero and the *bmRequestType* must be set to zero. The device must have its power cycled to exit test mode. The valid test mode selectors are listed in Table 9-7. See Section 7.1.20 for more information about the specific test modes.

If wLength is non-zero, then the behavior of the device is not specified.

If an endpoint or interface is specified that does not exist, then the device responds with a Request Error.

**Default state:** A device must be able to accept a SetFeature(TEST\_MODE, TEST\_SELECTOR)

request when in the Default State. Device behavior for other SetFeature requests

while the device is in the Default state is not specified.

Address state: If an interface or an endpoint other than endpoint zero is specified, then the device

responds with a Request Error.

Configured state: This is a valid request when the device is in the Configured state.

## 9.4.10 Set Interface

This request allows the host to select an alternate setting for the specified interface.

| bmRequestType | bRequest      | wValue               | windex    | wLength | Data |

|---------------|---------------|----------------------|-----------|---------|------|

| 0000001B      | SET_INTERFACE | Alternate<br>Setting | Interface | Zero    | None |

Some USB devices have configurations with interfaces that have mutually exclusive settings. This request allows the host to select the desired alternate setting. If a device only supports a default setting for the specified interface, then a STALL may be returned in the Status stage of the request. This request cannot be used to change the set of configured interfaces (the SetConfiguration() request must be used instead).

If the interface or the alternate setting does not exist, then the device responds with a Request Error. If wLength is non-zero, then the behavior of the device is not specified.

Default state:

Device behavior when this request is received while the device is in the Default state

is not specified.

Address state:

The device must respond with a Request Error.

Configured state:

This is a valid request when the device is in the Configured state.

## 9.4.11 Synch Frame

This request is used to set and then report an endpoint's synchronization frame.

| bmRequestType | bRequest    | wValue | windex   | wLength | Data            |

|---------------|-------------|--------|----------|---------|-----------------|

| 10000010B     | SYNCH_FRAME | Zero   | Endpoint | Two     | Frame<br>Number |

When an endpoint supports isochronous transfers, the endpoint may also require per-frame transfers to vary in size according to a specific pattern. The host and the endpoint must agree on which frame the repeating pattern begins. The number of the frame in which the pattern began is returned to the host.

If a high-speed device supports the Synch Frame request, it must internally synchronize itself to the zeroth microframe and have a time notion of classic frame. Only the frame number is used to synchronize and reported by the device endpoint (i.e., no microframe number). The endpoint must synchronize to the zeroth microframe.

This value is only used for isochronous data transfers using implicit pattern synchronization. If wValue is non-zero or wLength is not two, then the behavior of the device is not specified.

If the specified endpoint does not support this request, then the device will respond with a Request Error.

Default state:

Device behavior when this request is received while the device is in the Default state

is not specified.

Address state:

The device shall respond with a Request Error.

Configured state:

This is a valid request when the device is in the Configured state.

## 9.5 Descriptors

USB devices report their attributes using descriptors. A descriptor is a data structure with a defined format. Each descriptor begins with a byte-wide field that contains the total number of bytes in the descriptor followed by a byte-wide field that identifies the descriptor type.

Using descriptors allows concise storage of the attributes of individual configurations because each configuration may reuse descriptors or portions of descriptors from other configurations that have the same characteristics. In this manner, the descriptors resemble individual data records in a relational database.

Where appropriate, descriptors contain references to string descriptors that provide displayable information describing a descriptor in human-readable form. The inclusion of string descriptors is optional. However, the reference fields within descriptors are mandatory. If a device does not support string descriptors, string reference fields must be reset to zero to indicate no string descriptor is available.

If a descriptor returns with a value in its length field that is less than defined by this specification, the descriptor is invalid and should be rejected by the host. If the descriptor returns with a value in its length

field that is greater than defined by this specification, the extra bytes are ignored by the host, but the next descriptor is located using the length returned rather than the length expected.

A device may return class- or vendor-specific descriptors in two ways:

- If the class or vendor specific descriptors use the same format as standard descriptors (e.g., start with a length byte and followed by a type byte), they must be returned interleaved with standard descriptors in the configuration information returned by a GetDescriptor(Configuration) request. In this case, the class or vendor-specific descriptors must follow a related standard descriptor they modify or extend.

- 2. If the class or vendor specific descriptors are independent of configuration information or use a non-standard format, a GetDescriptor() request specifying the class or vendor specific descriptor type and index may be used to retrieve the descriptor from the device. A class or vendor specification will define the appropriate way to retrieve these descriptors.

## 9.6 Standard USB Descriptor Definitions

The standard descriptors defined in this specification may only be modified or extended by revision of the Universal Serial Bus Specification.

Note: An extension to the USB 1.0 standard endpoint descriptor has been published in Device Class Specification for Audio Devices Revision 1.0. This is the only extension defined outside USB Specification that is allowed. Future revisions of the USB Specification that extend the standard endpoint descriptor will do so as to not conflict with the extension defined in the Audio Device Class Specification Revision 1.0.

## 9.6.1 Device

A device descriptor describes general information about a USB device. It includes information that applies globally to the device and all of the device's configurations. A USB device has only one device descriptor.

A high-speed capable device that has different device information for full-speed and high-speed must also have a device qualifier descriptor (see Section 9.6.2).

The DEVICE descriptor of a high-speed capable device has a version number of 2.0 (0200H). If the device is full-speed only or low-speed only, this version number indicates that it will respond correctly to a request for the device\_qualifier descriptor (i.e., it will respond with a request error).

The *bcdUSB* field contains a BCD version number. The value of the *bcdUSB* field is 0xJJMN for version JJ.M.N (JJ – major version number, M – minor version number, N – sub-minor version number), e.g., version 2.1.3 is represented with value 0x0213 and version 2.0 is represented with a value of 0x0200.

The bNumConfigurations field indicates the number of configurations at the current operating speed. Configurations for the other operating speed are not included in the count. If there are specific configurations of the device for specific speeds, the bNumConfigurations field only reflects the number of configurations for a single speed, not the total number of configurations for both speeds.

If the device is operating at high-speed, the *bMaxPacketSize0* field must be 64 indicating a 64 byte maximum packet. High-speed operation does not allow other maximum packet sizes for the control endpoint (endpoint 0).

All USB devices have a Default Control Pipe. The maximum packet size of a device's Default Control Pipe is described in the device descriptor. Endpoints specific to a configuration and its interface(s) are described in the configuration descriptor. A configuration and its interface(s) do not include an endpoint descriptor for the Default Control Pipe. Other than the maximum packet size, the characteristics of the Default Control Pipe are defined by this specification and are the same for all USB devices.

The *bNumConfigurations* field identifies the number of configurations the device supports. Table 9-8 shows the standard device descriptor.

Table 9-8. Standard Device Descriptor

| Offset | Field            | Size | Value    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|------------------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bLength          | 1    | Number   | Size of this descriptor in bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1      | bDescriptorType  | 1    | Constant | DEVICE Descriptor Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2      | bcdUSB           | 2    | BCD      | USB Specification Release Number in<br>Binary-Coded Decimal (i.e., 2.10 is 210H).<br>This field identifies the release of the USB<br>Specification with which the device and its<br>descriptors are compliant.                                                                                                                                                                                                                                                                                                                      |

| 4      | bDeviceClass     | 1    | Class    | Class code (assigned by the USB-IF).  If this field is reset to zero, each interface within a configuration specifies its own class information and the various interfaces operate independently.  If this field is set to a value between 1 and FEH, the device supports different class specifications on different interfaces and the interfaces may not operate independently. This value identifies the class definition used for the aggregate interfaces.  If this field is set to FFH, the device class is vendor-specific. |

| 5      | bDevice SubClass | 1    | SubClass | Subclass code (assigned by the USB-IF).  These codes are qualified by the value of the bDeviceClass field.  If the bDeviceClass field is reset to zero, this field must also be reset to zero.  If the bDeviceClass field is not set to FFH, all values are reserved for assignment by the USB-IF.                                                                                                                                                                                                                                  |

Table 9-8. Standard Device Descriptor (Continued)

| Offset | Field              | Size | Value    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|--------------------|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | bDeviceProtocol    | 1    | Protocol | Protocol code (assigned by the USB-IF). These codes are qualified by the value of the bDeviceClass and the bDeviceSubClass fields. If a device supports class-specific protocols on a device basis as opposed to an interface basis, this code identifies the protocols that the device uses as defined by the specification of the device class.  If this field is reset to zero, the device does not use class-specific protocols on a device basis. However, it may use class-specific protocols on an interface basis.  If this field is set to FFH, the device uses a vendor-specific protocol on a device basis |

| 7      | bMaxPacketSize0    | 1    | Number   | Maximum packet size for endpoint zero (only 8, 16, 32, or 64 are valid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8      | idVendor           | 2    | ID       | Vendor ID (assigned by the USB-IF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10     | idProduct          | 2    | ID       | Product ID (assigned by the manufacture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12     | bcdDevice          | 2    | BCD      | Device release number in binary-coded decimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14     | iManufacturer      | 1    | Index    | Index of string descriptor describing manufacturer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15     | iProduct           | 1    | Index    | Index of string descriptor describing product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16     | iSerialNumber      | 1    | Index    | Index of string descriptor describing the device's serial number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17     | bNumConfigurations | 1    | Number   | Number of possible configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## 9.6.2 Device\_Qualifier

The device\_qualifier descriptor describes information about a high-speed capable device that would change if the device were operating at the other speed. For example, if the device is currently operating at full-speed, the device\_qualifier returns information about how it would operate at high-speed and vice-versa. Table 9-9 shows the fields of the device\_qualifier descriptor.

Offset Field Size Value Description 0 bLength 1 Number Size of descriptor 1 bDescriptorType 1 Constant Device Qualifier Type 2 2 BCD **bcdUSB** USB specification version number (e.g., 0200H for V2.00) 4 bDeviceClass 1 Class Class Code 5 bDeviceSubClass SubClass SubClass Code 1 6 bDeviceProtocol 1 Protocol Protocol Code 7 bMaxPacketSize0 1 Number Maximum packet size for other speed 8 **bNumConfigurations** 1 Number Number of Other-speed Configurations 9 bReserved Zero Reserved for future use, must be zero

Table 9-9. Device\_Qualifier Descriptor

The vendor, product, device, manufacturer, product, and serialnumber fields of the standard device descriptor are not included in this descriptor since that information is constant for a device for all supported speeds. The version number for this descriptor must be at least 2.0 (0200H).

The host accesses this descriptor using the GetDescriptor() request. The descriptor type in the GetDescriptor() request is set to device qualifier (see Table 9-5).

If a full-speed only device (with a device descriptor version number equal to 0200H) receives a GetDescriptor() request for a device\_qualifier, it must respond with a request error. The host must not make a request for an other\_speed\_configuration descriptor unless it first successfully retrieves the device\_qualifier descriptor.

## 9.6.3 Configuration

The configuration descriptor describes information about a specific device configuration. The descriptor contains a *bConfigurationValue* field with a value that, when used as a parameter to the SetConfiguration() request, causes the device to assume the described configuration.

The descriptor describes the number of interfaces provided by the configuration. Each interface may operate independently. For example, an ISDN device might be configured with two interfaces, each providing 64 Kb/s bi-directional channels that have separate data sources or sinks on the host. Another configuration might present the ISDN device as a single interface, bonding the two channels into one 128 Kb/s bi-directional channel.

When the host requests the configuration descriptor, all related interface and endpoint descriptors are returned (refer to Section 9.4.3).

A USB device has one or more configuration descriptors. Each configuration has one or more interfaces and each interface has zero or more endpoints. An endpoint is not shared among interfaces within a single configuration unless the endpoint is used by alternate settings of the same interface. Endpoints may be shared among interfaces that are part of different configurations without this restriction.

Once configured, devices may support limited adjustments to the configuration. If a particular interface has alternate settings, an alternate may be selected after configuration. Table 9-10 shows the standard configuration descriptor.

Table 9-10. Standard Configuration Descriptor

| Offset | Field               | Size | Value    | Description                                                                                                                                                                                                |

|--------|---------------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bLength             | 1    | Number   | Size of this descriptor in bytes                                                                                                                                                                           |

| 1      | bDescriptorType     | 1    | Constant | CONFIGURATION Descriptor Type                                                                                                                                                                              |

| 2      | wTotalLength        | 2    | Number   | Total length of data returned for this configuration. Includes the combined length of all descriptors (configuration, interface, endpoint, and class- or vendor-specific) returned for this configuration. |

| 4      | bNumInterfaces      | 1    | Number   | Number of interfaces supported by this configuration                                                                                                                                                       |

| 5      | bConfigurationValue | 1    | Number   | Value to use as an argument to the SetConfiguration() request to select this configuration                                                                                                                 |

| 6      | iConfiguration      | 1    | Index    | Index of string descriptor describing this configuration                                                                                                                                                   |

Table 9-10. Standard Configuration Descriptor (Continued)

| Offset      | Field        | Size         | Value                                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7           | bmAttributes | 1            | Bitmap                                                                                                                                                                     | Configuration characteristics  D7: Reserved (set to one) D6: Self-powered D5: Remote Wakeup D40: Reserved (reset to zero)  D7 is reserved and must be set to one for historical reasons.  A device configuration that uses power from the bus and a local source reports a non-zero value in bMaxPower to indicate the amount of bus power required and sets D6. The actual power source at runtime may be determined using the GetStatus(DEVICE) request (see Section 9.4.5). |

|             |              |              |                                                                                                                                                                            | If a device configuration supports remote wakeup, D5 is set to one.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8 bMaxPower | bMaxPower 1  | axPower 1 mA | Maximum power consumption of the USB device from the bus in this specific configuration when the device is fully operational. Expressed in 2 mA units (i.e., 50 = 100 mA). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |              |              |                                                                                                                                                                            | Note: A device configuration reports whether the configuration is bus-powered or self-powered. Device status reports whether the device is currently self-powered. If a device is disconnected from its external power source, it updates device status to indicate that it is no longer self-powered.                                                                                                                                                                         |

|             |              |              |                                                                                                                                                                            | A device may not increase its power draw from the bus, when it loses its external power source, beyond the amount reported by its configuration.                                                                                                                                                                                                                                                                                                                               |

|             |              |              |                                                                                                                                                                            | If a device can continue to operate when disconnected from its external power source, it continues to do so. If the device cannot continue to operate, it fails operations it can no longer support. The USB System Software may determine the cause of the failure by checking the status and noting the loss of the device's power source.                                                                                                                                   |

# 9.6.4 Other\_Speed\_Configuration

The other\_speed\_configuration descriptor shown in Table 9-11 describes a configuration of a high-speed capable device if it were operating at its other possible speed. The structure of the other\_speed\_configuration is identical to a configuration descriptor.

Table 9-11. Other\_Speed\_Configuration Descriptor

| Offset           | Field               | Size | Value    | Description                                                |

|------------------|---------------------|------|----------|------------------------------------------------------------|

| 0                | bLength             | 1    | Number   | Size of descriptor                                         |

| 1                | bDescriptorType     | 1    | Constant | Other_speed_Configuration Type                             |

| 2                | wTotalLength        | 2    | Number   | Total length of data returned                              |

| 4                | bNumInterfaces      | 1    | Number   | Number of interfaces supported by this speed configuration |

| 5                | bConfigurationValue | 1    | Number   | Value to use to select configuration                       |

| 6 iConfiguration |                     | 1    | Index    | Index of string descriptor                                 |

| 7                | bmAttributes        | 1    | Bitmap   | Same as Configuration descriptor                           |

| 8                | bMaxPower           | 1    | mA       | Same as Configuration descriptor                           |

The host accesses this descriptor using the GetDescriptor() request. The descriptor type in the GetDescriptor() request is set to other speed configuration (see Table 9-5).

#### 9.6.5 Interface

The interface descriptor describes a specific interface within a configuration. A configuration provides one or more interfaces, each with zero or more endpoint descriptors describing a unique set of endpoints within the configuration. When a configuration supports more than one interface, the endpoint descriptors for a particular interface follow the interface descriptor in the data returned by the GetConfiguration() request. An interface descriptor is always returned as part of a configuration descriptor. Interface descriptors cannot be directly accessed with a GetDescriptor() or SetDescriptor() request.

An interface may include alternate settings that allow the endpoints and/or their characteristics to be varied after the device has been configured. The default setting for an interface is always alternate setting zero. The SetInterface() request is used to select an alternate setting or to return to the default setting. The GetInterface() request returns the selected alternate setting.

Alternate settings allow a portion of the device configuration to be varied while other interfaces remain in operation. If a configuration has alternate settings for one or more of its interfaces, a separate interface descriptor and its associated endpoints are included for each setting.

If a device configuration supported a single interface with two alternate settings, the configuration descriptor would be followed by an interface descriptor with the bInterfaceNumber and bAlternateSetting fields set to zero and then the endpoint descriptors for that setting, followed by another interface descriptor and its associated endpoint descriptors. The second interface descriptor's bInterfaceNumber field would also be set to zero, but the bAlternateSetting field of the second interface descriptor would be set to one.

If an interface uses only endpoint zero, no endpoint descriptors follow the interface descriptor. In this case, the *bNumEndpoints* field must be set to zero.

An interface descriptor never includes endpoint zero in the number of endpoints. Table 9-12 shows the standard interface descriptor.

Table 9-12. Standard Interface Descriptor

| Offset | Field              | Size | Value    | Description                                                                                                                                                                                                                                                                                                |

|--------|--------------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bLength            | 1    | Number   | Size of this descriptor in bytes                                                                                                                                                                                                                                                                           |

| 1      | bDescriptorType    | 1    | Constant | INTERFACE Descriptor Type                                                                                                                                                                                                                                                                                  |

| 2      | bInterfaceNumber   | 1    | Number   | Number of this interface. Zero-based value identifying the index in the array of concurrent interfaces supported by this configuration.                                                                                                                                                                    |

| 3      | bAlternateSetting  | 1    | Number   | Value used to select this alternate setting for the interface identified in the prior field                                                                                                                                                                                                                |

| 4      | bNumEndpoints      | 1    | Number   | Number of endpoints used by this interface (excluding endpoint zero). If this value is zero, this interface only uses the Default Control Pipe.                                                                                                                                                            |

| 5      | bInterfaceClass    | 1    | Class    | Class code (assigned by the USB-IF).  A value of zero is reserved for future standardization.  If this field is set to FFH, the interface class is vendor-specific.  All other values are reserved for assignment by the USB-IF.                                                                           |

| 6      | bInterfaceSubClass | 1    | SubClass | Subclass code (assigned by the USB-IF). These codes are qualified by the value of the bInterfaceClass field.  If the bInterfaceClass field is reset to zero, this field must also be reset to zero.  If the bInterfaceClass field is not set to FFH, all values are reserved for assignment by the USB-IF. |

Table 9-12. Standard Interface Descriptor (Continued)

| Offset | Field              | Size | Value    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|--------------------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | bInterfaceProtocol | 1    | Protocol | Protocol code (assigned by the USB). These codes are qualified by the value of the bInterfaceClass and the bInterfaceSubClass fields. If an interface supports class-specific requests, this code identifies the protocols that the device uses as defined by the specification of the device class.  If this field is reset to zero, the device does not use a class-specific protocol on this interface.  If this field is set to FFH, the device uses a vendor-specific protocol for this interface. |

| 8      | iInterface         | 1    | Index    | Index of string descriptor describing this interface                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## 9.6.6 Endpoint

Each endpoint used for an interface has its own descriptor. This descriptor contains the information required by the host to determine the bandwidth requirements of each endpoint. An endpoint descriptor is always returned as part of the configuration information returned by a GetDescriptor(Configuration) request. An endpoint descriptor cannot be directly accessed with a GetDescriptor() or SetDescriptor() request. There is never an endpoint descriptor for endpoint zero. Table 9-13 shows the standard endpoint descriptor.

Table 9-13. Standard Endpoint Descriptor

| Offset | Field            | Size | Value    | Description                                                                                                                                  |

|--------|------------------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bLength          | 1    | Number   | Size of this descriptor in bytes                                                                                                             |

| 1      | bDescriptorType  | 1    | Constant | ENDPOINT Descriptor Type                                                                                                                     |

| 2      | bEndpointAddress | 1    | Endpoint | The address of the endpoint on the USB device described by this descriptor. The address is encoded as follows:                               |

|        |                  |      |          | Bit 30: The endpoint number Bit 64: Reserved, reset to zero Bit 7: Direction, ignored for control endpoints 0 = OUT endpoint 1 = IN endpoint |

Table 9-13. Standard Endpoint Descriptor (Continued)

| Offset | Field        | Size | Value  | Description                                                                                                                |

|--------|--------------|------|--------|----------------------------------------------------------------------------------------------------------------------------|

| 3      | bmAttributes | 1    | Bitmap | This field describes the endpoint's attributes when it is configured using the bConfigurationValue.                        |

|        |              |      |        | Bits 10: Transfer Type 00 = Control 01 = Isochronous 10 = Bulk 11 = Interrupt                                              |

|        |              |      |        | If not an isochronous endpoint, bits 52 are reserved and must be set to zero. If isochronous, they are defined as follows: |

|        |              |      |        | Bits 32: Synchronization Type                                                                                              |

|        |              |      |        | 00 = No Synchronization<br>01 = Asynchronous<br>10 = Adaptive<br>11 = Synchronous                                          |

|        |              |      |        | Bits 54: Usage Type                                                                                                        |

|        |              |      |        | 00 = Data endpoint<br>01 = Feedback endpoint<br>10 = Implicit feedback Data endpoint<br>11 = Reserved                      |

|        |              | 1 H  |        | Refer to Chapter 5 for more information.                                                                                   |

|        |              |      |        | All other bits are reserved and must be reset to zero. Reserved bits must be ignored by the host.                          |

Table 9-13. Standard Endpoint Descriptor (Continued)

| Offset | Field          | Size | Value  | Description                                                                                                                                                                                                                                                                                                                        |

|--------|----------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4      | wMaxPacketSize | 2    | Number | Maximum packet size this endpoint is capable of sending or receiving when this configuration is selected.                                                                                                                                                                                                                          |

|        |                |      |        | For isochronous endpoints, this value is used to reserve the bus time in the schedule, required for the per-(micro)frame data payloads. The pipe may, on an ongoing basis, actually use less bandwidth than that reserved. The device reports, if necessary, the actual bandwidth used via its normal, non-USB defined mechanisms. |

|        |                |      |        | For all endpoints, bits 100 specify the maximum packet size (in bytes).                                                                                                                                                                                                                                                            |

|        |                |      |        | For high-speed isochronous and interrupt endpoints:                                                                                                                                                                                                                                                                                |

|        |                |      |        | Bits 1211 specify the number of additional transaction opportunities per microframe:                                                                                                                                                                                                                                               |

|        |                |      |        | 00 = None (1 transaction per microframe)<br>01 = 1 additional (2 per microframe)<br>10 = 2 additional (3 per microframe)<br>11 = Reserved                                                                                                                                                                                          |

|        |                |      |        | Bits 1513 are reserved and must be set to zero.                                                                                                                                                                                                                                                                                    |

|        |                |      |        | Refer to Chapter 5 for more information.                                                                                                                                                                                                                                                                                           |

| 6      | bInterval      | 1    | Number | Interval for polling endpoint for data transfers. Expressed in frames or microframes depending on the device operating speed (i.e., either 1 millisecond or 125 µs units).                                                                                                                                                         |

|        |                |      |        | For full-/high-speed isochronous endpoints, this value must be in the range from 1 to 16. The <i>bInterval</i> value is used as the exponent for a 2 <sup>binterval-1</sup> value; e.g., a <i>bInterval</i> of 4 means a period of 8 (2 <sup>4-1</sup> ).                                                                          |

|        |                |      |        | For full-/low-speed interrupt endpoints, the value of this field may be from 1 to 255.                                                                                                                                                                                                                                             |

|        |                |      |        | For high-speed interrupt endpoints, the <i>bInterval</i> value is used as the exponent for a 2 <sup>binterval-1</sup> value; e.g., a <i>bInterval</i> of 4 means a period of 8 (2 <sup>4-1</sup> ). This value must be from 1 to 16.                                                                                               |

|        |                |      |        | For high-speed bulk/control OUT endpoints, the bInterval must specify the maximum NAK rate of the endpoint. A value of 0 indicates the endpoint never NAKs. Other values indicate at most 1 NAK each bInterval number of microframes. This value must be in the range from 0 to 255.                                               |

|        |                |      |        | See Chapter 5 description of periods for more detail.                                                                                                                                                                                                                                                                              |

The bmAttributes field provides information about the endpoint's Transfer Type (bits 1..0) and Synchronization Type (bits 3..2). In addition, the Usage Type bit (bits 5..4) indicate whether this is an endpoint used for normal data transfers (bits 5..4=00B), whether it is used to convey explicit feedback information for one or more data endpoints (bits 5..4=01B) or whether it is a data endpoint that also serves

as an implicit feedback endpoint for one or more data endpoints (bits 5..4=10B). Bits 5..2 are only meaningful for isochronous endpoints and must be reset to zero for all other transfer types.

If the endpoint is used as an explicit feedback endpoint (bits 5..4=01B), then the Transfer Type must be set to isochronous (bits1..0 = 01B) and the Synchronization Type must be set to No Synchronization (bits 3..2=00B).

A feedback endpoint (explicit or implicit) needs to be associated with one (or more) isochronous data endpoints to which it provides feedback service. The association is based on endpoint number matching. A feedback endpoint always has the opposite direction from the data endpoint(s) it services. If multiple data endpoints are to be serviced by the same feedback endpoint, the data endpoints must have ascending ordered—but not necessarily consecutive—endpoint numbers. The first data endpoint and the feedback endpoint must have the same endpoint number (and opposite direction). This ensures that a data endpoint can uniquely identify its feedback endpoint by searching for the first feedback endpoint that has an endpoint number equal or less than its own endpoint number.

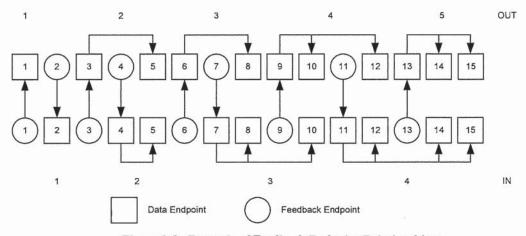

*Example*: Consider the extreme case where there is a need for five groups of OUT asynchronous isochronous endpoints and at the same time four groups of IN adaptive isochronous endpoints. Each group needs a separate feedback endpoint and the groups are composed as shown in Figure 9-7.

| OUT<br>Group | Nr of OUT<br>Endpoints | IN<br>Group | Nr of IN<br>Endpoints |

|--------------|------------------------|-------------|-----------------------|

| 1            | 1                      | 6           | 1                     |

| 2            | 2                      | 7           | 2                     |

| 3            | 2                      | 8           | 3                     |

| 4            | 3                      | 9           | 4                     |

| 5            | 3                      |             |                       |

Figure 9-7. Example of Feedback Endpoint Numbers

The endpoint numbers can be intertwined as illustrated in Figure 9-8.

Figure 9-8. Example of Feedback Endpoint Relationships

High-speed isochronous and interrupt endpoints use bits 12..11 of wMaxPacketSize to specify multiple transactions for each microframe specified by bInterval. If bits 12..11 of wMaxPacketSize are zero, the maximum packet size for the endpoint can be any allowed value (as defined in Chapter 5). If bits 12..11 of wMaxPacketSize are not zero (0), the allowed values for wMaxPacketSize bits 10..0 are limited as shown in Table 9-14.

Table 9-14. Allowed wMaxPacketSize Values for Different Numbers of Transactions per Microframe

| wMaxPacketSize<br>bits 1211 | wMaxPacketSize<br>bits 100 Values<br>Allowed |  |

|-----------------------------|----------------------------------------------|--|

| 00                          | 1 – 1024                                     |  |

| 01                          | 513 – 1024                                   |  |

| 10                          | 683 – 1024                                   |  |

| 11                          | N/A; reserved                                |  |

For high-speed bulk and control OUT endpoints, the *bInterval* field is only used for compliance purposes; the host controller is not required to change its behavior based on the value in this field.

## 9.6.7 String

String descriptors are optional. As noted previously, if a device does not support string descriptors, all references to string descriptors within device, configuration, and interface descriptors must be reset to zero.

String descriptors use UNICODE encodings as defined by *The Unicode Standard, Worldwide Character Encoding, Version 3.0*, The Unicode Consortium, Addison-Wesley Publishing Company, Reading, Massachusetts (URL: http://www.unicode.com). The strings in a USB device may support multiple languages. When requesting a string descriptor, the requester specifies the desired language using a sixteenbit language ID (LANGID) defined by the USB-IF. The list of currently defined USB LANGIDs can be found at http://www.usb.org/developers/docs.html. String index zero for all languages returns a string descriptor that contains an array of two-byte LANGID codes supported by the device. Table 9-15 shows the LANGID code array. A USB device may omit all string descriptors. USB devices that omit all string descriptors must not return an array of LANGID codes.

The array of LANGID codes is not NULL-terminated. The size of the array (in bytes) is computed by subtracting two from the value of the first byte of the descriptor.

Table 9-15. String Descriptor Zero, Specifying Languages Supported by the Device

| Offset | Field           | Size | Value    | Description                      |

|--------|-----------------|------|----------|----------------------------------|

| 0      | bLength         | 1    | N+2      | Size of this descriptor in bytes |

| 1      | bDescriptorType | 1    | Constant | STRING Descriptor Type           |

| 2      | wLANGID[0]      | 2    | Number   | LANGID code zero                 |

| ***    |                 |      |          |                                  |

| N      | wLANGID[x]      | 2    | Number   | LANGID code x                    |

The UNICODE string descriptor (shown in Table 9-16) is not NULL-terminated. The string length is computed by subtracting two from the value of the first byte of the descriptor.

Table 9-16. UNICODE String Descriptor

| Offset | Field           | Size | Value    | Description                      |

|--------|-----------------|------|----------|----------------------------------|

| 0      | bLength         | 1    | Number   | Size of this descriptor in bytes |

| 1      | bDescriptorType | 1    | Constant | STRING Descriptor Type           |