# (12) United States Patent

## Venkatesan et al.

# et al.

## (54) METHOD FOR FORMING A DUAL INLAID COPPER INTERCONNECT STRUCTURE

- (75) Inventors: Suresh Venkatesan; Bradley P. Smith; Mohammed Rabiul Islam, all of Austin, TX (US)

- (73) Assignee: Motorola, Inc., Schaumburg, IL (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/352,134

- (22) Filed: Jul. 13, 1999

- (51) Int. Cl.<sup>7</sup> ..... H01L 21/4763; H01L 21/44

- (52) U.S. Cl. ..... 438/638; 438/618; 438/634;

#### (56) **References Cited**

### U.S. PATENT DOCUMENTS

| 6,077,768 | * | 6/2000 | Ong et al  | 438/622 |

|-----------|---|--------|------------|---------|

| 6,100,184 | * | 8/2000 | Zhao et al | 438/638 |

| 6,103,619 | * | 8/2000 | Lai        | 438/638 |

## OTHER PUBLICATIONS

US 6,326,301 B1

Dec. 4, 2001

Nakamura et al., "High Performance Al Dual Damascene Process with Elevated Double Stoppers," Microelectronics Engineering Laboratory, Toshiba Corporation, IEEE (1998).

\* cited by examiner

(10) Patent No.:

(45) Date of Patent:

Primary Examiner—Richard Elms

Assistant Examiner-Adam J. Pyonin

(74) Attorney, Agent, or Firm—Keith E. Witek; Patricia S. Goddard

## (57) ABSTRACT

A dual inlaid copper interconnect structure uses a plasma enhanced nitride (PEN) bottom capping layer and a silicon rich silicon oxynitride intermediate etch stop layer. The interfaces (16a, 16b, 20a, and 20b) between these layers (16 and 20) and their adjacent dielectric layers (18 and 22) are positioned in the stack (13) independent of the desired aspect ratio of trench openings of the copper interconnect in order to improve optical properties of the dielectric stack (13). Etch processing is then used to position the layers (16) and (20) at locations within the inlaid structure depth that result in one or more of reduced DC leakage current, improved optical performance, higher frequency of operation, reduced cross talk, increased flexibility of design, or like improvements.

#### 16 Claims, 5 Drawing Sheets

Sheet 1 of 5

FIG.1

FIG.2

FIG.3

FIG.4

FIG.9

20

## METHOD FOR FORMING A DUAL INLAID **COPPER INTERCONNECT STRUCTURE**

## FIELD OF THE INVENTION

The present invention relates generally to semiconductor manufacturing, and more particularly to, forming a dual inlaid copper interconnect within an integrated circuit (IC).

### BACKGROUND OF THE INVENTION

In the integrated circuit (IC) industry, aluminum interconnects are now being replaced with copper-based inlaid interconnect structures. Copper interconnects are fairly new to the semiconductor industry and are very different from the more commonly used aluminum-based systems. For this reason, copper interconnects have uncovered new problems not before anticipated or addressed by integrated circuit manufacturing facilities. Specifically, a dual inlaid copper interconnect structure comprises at least two etch stop layers interleaved between at least two thicker silicon dioxide layers for a total of four layers of dielectric where aluminum usually required only one dielectric material made via one deposition step. The stack of at least two dielectric layers and at least two etch stop layers used by copper interconnects is lithographically patterned and etched in multiple photo steps and via multiple etch processes where aluminum interconnects generally need no such processing. Further the copper metallurgy itself usually requires multiple materials (e.g., barrier layers, seed layers, bulk layers, etc.), multiple deposition steps, and/or one or more chemical mechanical polishing (CMP) processes where aluminum processes needs only a single and simple deposition step.

In order to make these more complex copper interconnect structures efficiently and with high yield, engineers must consider many different combinations of complexities not before addressed. Specifically, lithographic and etch processing of dual inlaid copper structures must contend with one or more of: (1) adverse chemical interactions related to copper; (2) more complicated optical issues associated with the dielectric interfaces in the copper dielectric stack (e.g., 40 ties of films within the dielectric stack must also be considlight reflection, destructive interference, light distortion, etc.); (3) disadvantageous electrical properties associated with dielectric materials and etch stop layers within the copper dielectric stack; (4) complications in etch chemistries and etch processing; and (5) the more complicated mechanical integrity of the inlaid structure. While one of these five factors may have been faced by aluminum on occasion, never has a combination of two or more of these issues been a serious concern for aluminum-based ICs.

In addition to the collective weight of several of the five 50 factors enumerated above, many copper-based designs require that different copper layers over the same integrated circuit have different trench depths and thicknesses. For example, the dual inlaid via height within inlaid structures may be designed to vary from layer to layer on the same IC, 55 stack in a manner that is unacceptable. and different trench interconnect depths within the dual inlaid structures may also vary between the first metal layer and the Nth metal layer within a single integrated circuit (N being up to or greater than eight in current IC devices).

With respect to the first of the five factors enumerated 60 above, integrated circuit engineers are concerned with adverse chemical interactions that are associated with copper based materials and processing. Copper will adversely react with ambient air and oxidize in a manner that could reduce integrated circuit yield and/or adversely increase the 65 resistance of the electrical interconnects. In addition, all etch stops and/or capping layers in contact with the copper must

be adequate diffusion barriers to prevent copper and associated impurities within the copper from diffusing through the film and contaminating adjacent dielectric layers or underlying electrical devices.

In addition to chemical reactions, engineers who are designing copper-based interconnects should also be concerned with the optical properties of the dielectric stack used to define a dual inlaid or inlaid structure. Chemically mechanically polished (CMP) copper has a highly reflective top surface which may readily reflect light/energy during lithographic operations. Furthermore, the plurality of dielectric layers in the dielectric stack of a copper interconnect creates many interfaces of different materials that can adversely reflect light and cause distortion of critical dimensions (CDs) and/or destructive interference whereby photoresist is not properly exposed and developed. In other words, at certain depths of lithographic focus, wavelengths of light, and thicknesses of material, light reflected from a surface of a copper interconnect or dielectric interfaces may destructively interfere or distort various lithographic feature sizes resulting in reduced yield and/or reduced performance of an integrated circuit. Therefore, various etch stop and capping layers within an inlaid copper structure should be geometrically and chemically designed with adequate anti-reflective coating (ARC) properties so that a high yield integrated circuit can be manufactured in an effective manner.

Specifically, the thicknesses of the dielectric and etch stop layers within the dielectric inlaid stack must be carefully engineered to reduce reflectance and/or ensure that any reflectance that occurs is primarily destructive interference when some level of reflection is unavoidable. In addition, the index of refraction (N) and the extinction coefficient (K) of the materials within the dielectric stack need to be carefully considered in order to tune the optical properties of the stack to the wavelength of lithographic light utilized. In 35 addition, the interface between different materials within the dielectric stack must be carefully placed to avoid the various optical problems associated with unwanted reflection.

In addition to the chemical interaction concerns and optical concerns discussed above, various electrical properered. Since the etch stop layers, ARC layers, and/or capping layers of the dielectric stack generally contact the interconnect metallurgy, the etch stop/ARC layers need to be materially engineered and physically placed within the dielectric 45 stack to prevent unacceptable levels of leakage current between adjacent interconnects within an integrated circuit. In addition, the dielectric constants of these materials and/or the physical placement and cross sectional geometry of these materials need to be carefully engineered and considered in order to ensure that the IC may be operated at a high frequency of operation absent of significant cross talk and/or parasitic capacitance. In addition, the above engineering should strive to solve these problems while not to complicating the etch chemistries or the etch steps of the dielectric

The various layers contained within a dielectric stack of a dual inlaid copper interconnect create various mechanical concerns as well. The materials used in the dielectric stack must be engineered to provide adequate adhesion between silicon dioxide, copper, and various copper barrier materials. In addition, the stress exerted by these various films on the integrated circuit structure should be at or below an acceptable threshold. Further, the geometric aspect ratio of the via openings and the trench interconnect openings of the dual inlaid structure need to adjusted in order to ensure reduced keyhole formation, reduced voiding, and improved copper electromigration (EM) resistance.

55

A problem is that any one of the above concerns may be addressed and optimized within an IC interconnect structure when ignoring all the other concerns. When two or three, not to mention all five, of the above discussed concerns are considered at once, it is difficult to make the proper tradeoffs and decisions that result in the best possible inlaid structure for a certain set of conditions.

Therefore, it should be evident to one of ordinary skill in the art that many complicated and sometimes conflicting 10 concerns must be considered and balanced when engineering a multi-layer dielectric stack for use in copper interconnected devices. A structure that considers two or more of these needs and creates an improved inlaid structure is needed in the art.

## BRIEF DESCRIPTION OF THE DRAWINGS

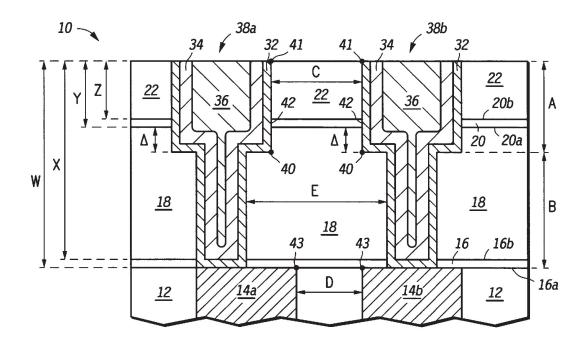

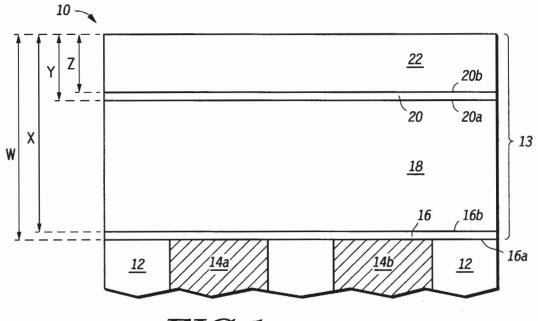

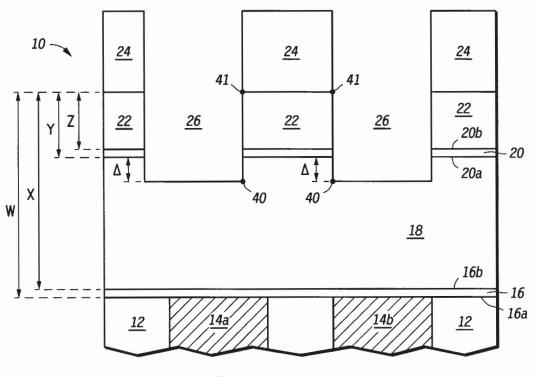

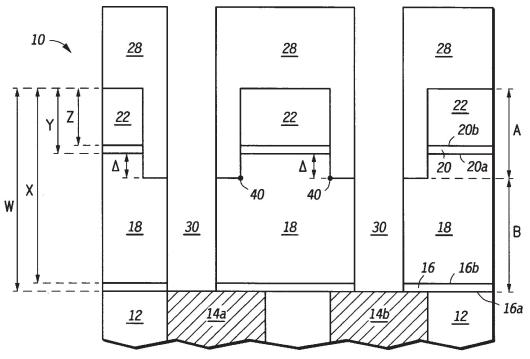

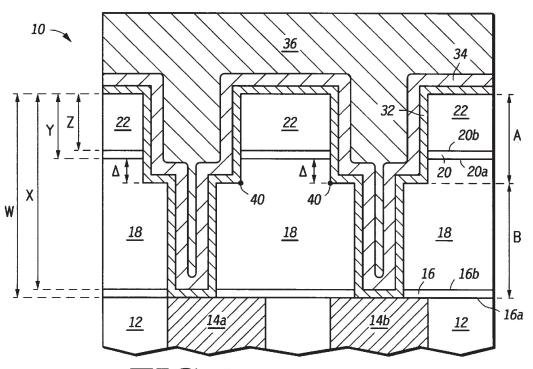

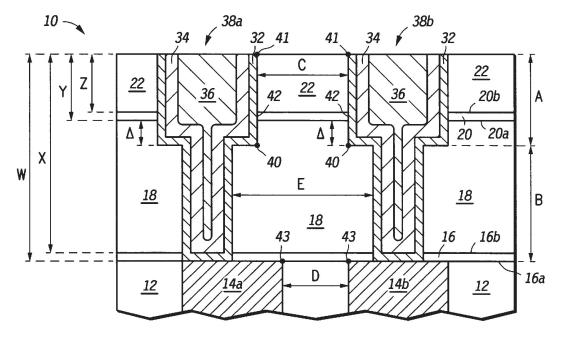

FIGS. 1-5 illustrate, in cross sectional diagrams, a first method for forming a copper interconnect structure.

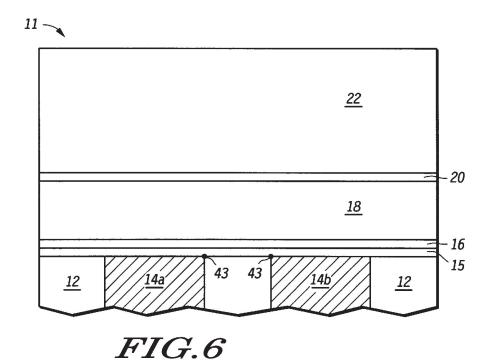

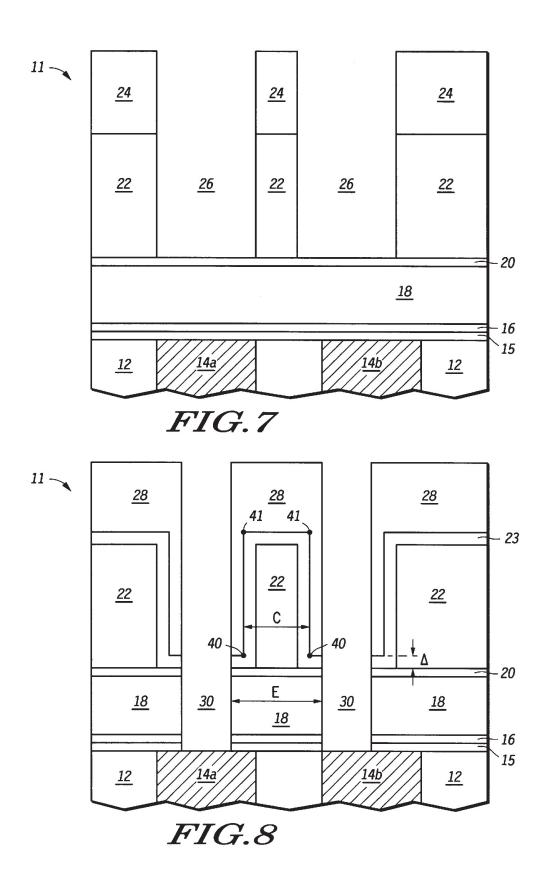

method that is used for forming dual inlaid copper interconnects on an integrated circuit (IC).

It will be appreciated that for simplicity and clarity of illustration, elements illustrated in the drawings have not necessarily been drawn to scale. For example, the dimen- 25 sions of some of the elements are exaggerated relative to other elements for clarity. Further, where considered appropriate, reference numerals have been repeated among the drawings to indicate corresponding or analogous elements.

## DESCRIPTION OF A PREFERRED EMBODIMENT

Generally each of the two embodiments taught in FIGS. 1-9 herein teach a copper dual inlaid interconnect process 35 and structure that is formed through a dielectric stack. The dielectric stack is specifically engineered based upon the results of significant experimentation and testing. The materials used for the etch stop/ARC layers and dielectric layers within the dielectric stack, as well as their physical place- 40 ment within this structure and geometry, were designed to optimize or make acceptable trade-offs between two or more of: (1) optimal chemical protection of copper interconnects; (2) improved optical properties within the dielectric stack; (3) improved electrical properties of the structure; (4) 45 reduced etch processing complexity; and (5) improved mechanical integrity of the copper interconnect. In addition, the interconnect structure processing taught herein are flexible for different environments (different materials, different lithographic wavelengths etc.). Further, the processing 50 taught herein allows integrated circuits (ICs) to be manufactured with multiple layers of metal interconnects wherein each layer of metal may have different trench interconnect opening aspect ratios and different via connection opening aspect ratios.

The materials primarily considered for use as etch stop layers and ARCs herein were chemical vapor deposited (CVD) silicon nitride (SiN<sub>x</sub>), plasma enhanced silicon nitride (PEN), silicon oxynitride (SiO $_{v}N_{v}$ ), and silicon rich silicon oxynitride nitride (Si—SiO<sub>x</sub>N<sub>y</sub>). It was found that 60 CVD silicon nitride films resulted in very good line-to-line current leakage performance, but that CVD silicon nitride must be deposited at a temperature that is too high for use with copper. Also, fear of copper cross-contamination generally prevents manufacturing facilities from putting wafers 65 with copper already on them into a CVD furnace. In addition, the higher dielectric constant of most silicon

nitride films (e.g.,  $\in_r=7.0-8.0$ ) when compared to silicon oxide (roughly  $\in_{r}=4.0$ ) resulted in unacceptable high frequency performance of copper interconnects as well as unacceptable cross-talk in some test structures. Therefore, while CVD silicon nitride may be used as an etch stop or ARC layer within any portion of the dielectric stack taught herein, it was generally determined that a better set of trade-offs could be obtained by avoiding any use of conventional CVD silicon nitride films within the inlaid dielectric stacks taught herein.

In addition to CVD silicon nitride, stoichiometric silicon oxynitride (SiON) was also studied in various positions and geometries within the dielectric stack. Stoichiometric silicon oxynitride with an index of refraction of n=1.6 and an extension coefficient of k=0.0 showed very low line-to-line leakage as did CVD silicon nitride. However, stoichiometric SiON also acted as a poor anti-reflective coating (ARC) and a poor via etch stop layer within dielectric stacks. Therefore, while stoichiometric silicon oxynitride may be used in the FIGS. 6-9 illustrate, in cross sectional diagram, a second 20 embodiments taught herein, it was generally found that other materials would likely produce a more acceptable dielectric stack for copper dual inlaid use.

> In addition to CVD silicon nitride and stoichiometric SiON, silicon-rich SiON films were researched as capping layers and as etch stop layers in a copper dual inlaid dielectric stack. Many compositions of silicon-rich SiON films were found to be excellent anti-reflective coatings (ARCs) and/or excellent etch stop layers within the dielectric stack, however, their use as a copper capping layer was not practical. SiON was less attractive as a copper capping layer since this material had a greater likelihood of chemically reacting with the copper at the Cu-SiON interface. This reaction produced interfacial films which were shown to occasionally increase leakage current between adjacent copper interconnects and increase sheet resistance within individual interconnects. Therefore, when considering several of the five areas of concern enumerated above when searching for an improved etch stop, capping, and ARC layer combination, it was found that a silicon-rich silicon oxynitride films were best put to use as an intermediate etch stop layer near a central portion of the inlaid dielectric stack. However, Si-rich SiON material can be engineered to be generally used in any etch stop, ARC layer, or capping function within the devices taught herein, sometimes to less, but potentially acceptable, effect.

> The final of the four layers researched for use in the dielectric stack was plasma enhanced silicon nitride (PEN). It was found that plasma enhanced silicon nitride was an optimal capping layer to place in direct contact with copper since experimental results indicated either no degradation in sheet resistance or an acceptable interconnect resistance. In addition, PEN resulted in a reduction in leakage current while the containment and protection of the copper over time was within accepted tolerances.

> In addition to determining the optimal material composition of various etch stop layers, ARC layers, and capping layers within the dielectric stack, the embodiments taught herein specifically engineer the various thicknesses, geometric properties, and physical positions of layers within the inlaid dielectric stack in order to improve or maintain the optical integrity of the interconnect structure during manufacturing. Therefore, the selection of materials discussed above has typically improved the chemical stability of the copper interconnect, improved the electrical properties of the interconnect structures, and provided adequate mechanical stability to the integrated circuit while at the same time being engineered to provide adequate or improved optical

properties over and above that available in prior art inlaid structures. In addition to obtaining these benefits, the etch processing taught herein is not significantly complicated compared to conventional copper processing. In addition, the resulting cross-sectional geometries (i.e., aspect ratio) of the trench interconnect opening in the via interconnect opening are also optimized in the structures herein to allow for formation of copper interconnects with reduced voiding and keyholes so that integrated circuit (IC) yield is enhanced.

Specific details of the various embodiments may be understood with specific references FIGS. 1-9.

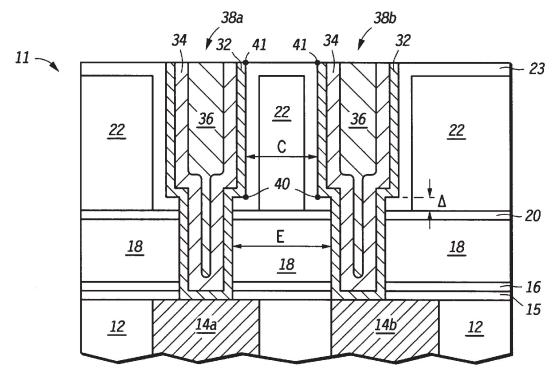

Specifically, FIGS. 1-5 illustrate a first embodiment that may be used to form a dual inlaid copper interconnect structure within an integrated circuit (IC).

FIG. 1 illustrates a few beginning process steps that are used to start the formation of an integrated circuit 10. Integrated circuit 10 is to contain one or more layers of inlaid copper interconnect structures. In FIG. 1, all the shown elements are formed over a substrate surface, printed circuit board (PCB) or like substrate. While not specifically illustrated in FIG. 1, the substrate material which is commonly used for integrated circuit formation is one of silicon, silicon germanium, germanium, gallium arsenide, other III-V compounds, a silicon carbide, epitaxial regions, silicon on insulator (SOI) substrates, or like starting material. Over this substrate is formed any number of passive devices such as resistors, capacitors, inductors, diodes, and the like. In addition, the substrate may support up to millions of inte-30 grated active devices, such as NMOS transistors, PMOS transistors, bipolar transistors, JFETs, thyristors, SCRs, memory cells, logic gates, and/or like electrical circuitry. Furthermore, micromachined and/or electromechanical devices such as pressure transducers, gears, engines, detectors, and/or the like may be formed on the integrated circuit (IC) substrate.

The various devices that are formed on top of the substrate may be interconnected by one or more metallic layers. A single metallic layer may be used to form many segmented  $_{40}$  16 of roughly 500 angstroms worked well when using interconnects across the integrated circuit (IC). FIG. 1 specifically illustrates that a first metallic layer is used to form at least two such interconnects 14a and 14b. FIG. 1 illustrates that a dielectric layer 12 is generally used to electrically isolate one interconnect 14a from another interconnect 14b within one metallic layer. Any one interconnect layer of an integrated circuit may contain millions of individuals and segmented interconnects similar to 14a and 14b, and an integrated circuit may contain up to 8 or more stacked layers of interconnect metallurgy over the top of one 50 another. In FIG. 1, interconnects such as 14a and 14b are generally formed as one of either tungsten (W) plugs, tungsten local interconnects, aluminum wiring, inlaid copper interconnects, polysilicon regions, dual inlaid copper interconnects, composite metallic contacts, and/or like inte- 55 grated circuit conductive members. In addition, various dielectric layers taught herein, such as dielectric layer 12, are usually one or more of tetraethelorthosilicate (TEOS), fluorine doped TEOS (f-TEOS), low k dielectrics, borophosphosilicate glass (BPSG), phosphosilicate glass (PSG), spin 60 on glasses (SOG), silicon nitride layers, metal oxides, air gaps, composites thereof, and/or like dielectric regions.

FIG. 1 illustrates that a dielectric stack 13 is formed over a top of the interconnects 14a and 14b and a top of the dielectric layer 12. Generally, a dielectric stack is any 65 vertically stacked combination of two or more different dielectric materials. Specifically, FIG. 1 illustrates a dielec-

tric stack 13 that contains four layers 16, 18, 20, and 22. The layers 16, 18, 20, and 22 are subsequently used to form dual inlaid copper interconnect structures across an IC.

As previously discussed, the capping layer 16 must be physically positioned, geometrically designed, and composed of a material that provides certain acceptable properties and/or functions. Generally, the layer 16 should be an acceptable protective layer for the interconnects 14a and 14b, especially if these layers may be adversely affected by  $_{10}$  exposure to an environment. For example, if layers 14a and 14b are a copper-based interconnects, layer 16 should provide adequate containment and protection of copper to prevent or reduce copper oxidation or contamination. Furthermore, layer 16 should function as an adequate barrier 15 layer that prevents any copper contaminants or like contaminants from diffusing from regions 14a and 14b into adjacent dielectric layers such as layers 12 and 18. The thickness and position of the layer 16 as well as its index of refraction (N) and its extinction coefficient (K) should serve 20 to improve the optical integrity of the dielectric stack 13 (i.e., reduce distortion, reduce destructive interference, etc.). Proper engineering of this layer will result in reduced destructive interference upon light reflection, diminish any intensity of reflected light, and reduced distortion of litho-25 graphic critical dimensions (CD's) upon reflection. In addition, layer 16 should be chosen to provide acceptable levels of leakage current between the layers 14a and 14b while providing for high frequency performance having reduced cross talk between layers 14a and 14b.

As previously discussed, it has been determined that a plasma enhanced silicon nitride (PEN) layer is an optimal layer for use as layer 16 in FIG. 1 in order to reasonably obtain the above objectives. While it was found that plasma enhanced nitride (PEN) is a most appropriate choice for the 35 material used for layer 16, other materials such as silicon oxynitride, silicon rich silicon nitride, silicon rich silicon oxynitride, CVD silicon nitride, or composites of these materials with or without PEN may be used as the capping layer 16 in FIG. 1. It was found that a thickness of the layer lithographic exposures of roughly 365 nm (i.e., I-line). However, other thicknesses may be used for I line, and other thicknesses are used for different wavelengths of exposure in order to optimally change the dimensions X and W in the figures do different lithographic characteristics. Other thicknesses may be easily derived for other commonly used lithographic wavelengths, such as 248 nm (deep UV). In essence, the thickness of this film as well as its placement within the stack is also largely a function of the wavelength used for lithographic operations as is the engineered index of refraction and extension coefficient of this film. In addition, the reflective properties of the interface 16b and 16a is also largely a function of the composition and physical dimensions of the layers 18 and 12. Therefore, while an optimal layer 16 is roughly a 500 angstrom PEN layer when using I-line in the environment discussed herein, other reasonable thicknesses and other materials may be used for layer 16 under different circumstances.

A dielectric layer 18 is formed within the dielectric stack 13 overlying the capping layer 16. In a preferred form, for improved electrical properties, adequate mechanical properties, and adequate optical properties, the layer 18 was selected as a CVD TEOS laver. However, the laver 18 may be any other dielectric layer taught herein or may be any composite thereof. Generally, the thickness of the layer (X-Y) is selected to be roughly 8000 angstroms in thickness. This thickness is selected to improve the optical properties of the structure when using lithographic wavelengths of 365 nanometers (I-line) for photoresist processing over the dielectric stack 13. It should be understood that different thicknesses will result when different lithographic wavelengths are used, different material compositions are 5 selected, different thicknesses of material are deposited, different interfaces are created, different chemical compositions are formed, and/or the like.

After formation of the layer 18, an etch stop layer 20 is deposited over the layer 18 and the dielectric stack 13. 10 tride may be used for layer 20. For example, a thicker layer Generally, the layer 20 is chosen as any layer that can be an etch stop for the overlying layer 22. In addition, it is advantageous if the layer 20 prevents copper leakage. Further, the thickness and material composition of layer 20 should be engineered to improve the optical properties of the 15 overall structure 13. Since the layer 20 will generally be adjacent or in close proximity to the trench interconnect regions and since these trench interconnect regions are more closely spaced to each other via dimension C (see FIG. 5), the layer 20 of FIG. 1 needs to be electrically robust enough  $_{20}$  nanometers, the 600 Angstroms silicon rich SiON layer is to ensure low levels of leakage current. Further, an improved device is formed if the layer 20 has a dielectric constant and capacitive geometry that is conducive to higher frequencies of operation without adversely high parasitic capacitors and/or excessive cross talk. 25

A material that was found to provide a good trade off and balance among the above considerations was silicon-rich silicon oxynitride (Si-SiON). A silicon rich silicon oxynitride film provides an excellent antireflective coating (ARC) for improved optical properties and was also found to be an 30 excellent etch stop layer for the overlying layer 22. In addition, the minimal surface area contacted the layer 20 to any subsequent metallurgy ensured that any reactions that could occur therebetween were of little impact to the overall performance of the device. It was found that the SiON layer

20 and the barrier materials of the copper interconnect, if they reacted with each other, did not result in unacceptable degradation in sheet resistance or unacceptable increase in line-to-line leakage current.

Generally, a thickness of the silicon-rich SiON layer 20 (Y-Z) is on the order of 600 angstroms for I-line lithographic processing. It is important to note that different thicknesses of layer 20 may be used and that different materials or composites of materials other than silicon-rich silicon oxyniof stoichiometric silicon oxynitride may replace the silicon rich silicon oxynitride layer 20, but such a layer would likely need to be at least 1000 angstroms in thickness whereby etch throughput, leakage, etc. may be altered. Other composite materials and/or different thicknesses may be optimal in other circumstances where different materials are used for layers 18 and 22, different lithographic wavelengths are used, or different conditions apply. However, for the materials discussed so far and for I-line lithography of 365 optimal with the above discussed layers 18 and 20.

After formation of layer 20, a top layer 22 is formed as a top portion of the dielectric stack 13. Layer 22 is generally analogous to the layer 18 in term of material composition. However, the layer 22 is generally deposited to a thickness that is less than the layer 18. As shown in FIG. 1, various surfaces 16a, 16b, 20a and 20b must be adequately positioned within the trench and subject to properly engineered indices of refraction in extinction coefficient values in order to improve the optical characteristics of the overall interconnect structure. For this purpose, the layer 22 is generally a CVD TEOS layer that is roughly 4000-5000 angstroms in thickness.

In summary of FIG. 1, an acceptable dielectric stack was found to be:

| TA  | BI   | F | 1 |

|-----|------|---|---|

| 111 | LU I | _ |   |

| Thickness of Layer<br>(range and target)<br>300-800<br>Angstroms,<br>500 Angstrom<br>target | Useful Process<br>Information<br>use a parallel plate<br>RF reactor by<br>Applied Materials,<br>flow both SiH <sub>4</sub> and                                                                                                                                                                                  | Refractive Index (N)<br>1.5-3.0 with roughly<br>2.3 being a target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Extinction<br>Coefficient (K)<br>0.0 to 0.4 with<br>0.027 being a target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Angstroms,<br>500 Angstrom                                                                  | RF reactor by<br>Applied Materials,<br>flow both SiH <sub>4</sub> and                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                             | NH4 at 370° C. to 410° C.                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8,000 Angstrom<br>target<br>300–800<br>Angstroms,                                           | use a parallel plate<br>RF reactor by<br>Applied Materials,<br>flow all of SiH4,                                                                                                                                                                                                                                | 2.0-4.0 with one of<br>either 2.8 or 3.5<br>being a target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.1 to 1.0 with one<br>of either 0.3 or 0.7<br>being a target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3,000–6,000<br>Angstroms,<br>4,500 Angstrom                                                 | 370° C. to 410° C.                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| target<br>300–800<br>Angstroms,<br>500 Angstrom<br>target                                   | use a parallel plate<br>RF reactor by<br>Applied Materials,<br>flow both SiH4 and<br>NH4 at<br>370° C, to 410° C.                                                                                                                                                                                               | 1.0–3.0 with roughly 2.1 being a target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.0 to 0.4 with 0.0 being a target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6,000–10,000<br>Angstroms,<br>8,000 Angstrom<br>target<br>300–800                           | use a parallel plate                                                                                                                                                                                                                                                                                            | 2.0-4.0 with 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.1 to 1.5 with 0.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| )                                                                                           | <ul> <li>Angstroms,<br/>8,000 Angstrom<br/>target<br/>300–800<br/>Angstroms,<br/>600 Angstrom<br/>target</li> <li>3,000–6,000<br/>Angstroms,<br/>4,500 Angstrom<br/>target<br/>300–800<br/>Angstroms,<br/>500 Angstrom<br/>target</li> <li>6,000–10,000<br/>Angstroms,<br/>8,000 Angstrom<br/>target</li> </ul> | 6,000–10,000<br>r Angstroms,<br>8,000 Angstrom<br>target<br>300–800<br>4ngstroms,<br>arget<br>400 Angstrom<br>target<br>300–600<br>Angstroms,<br>4,500 Angstrom<br>target<br>300–800<br>4,500 Angstrom,<br>4,500 Angstrom,<br>500 Angstrom,<br>500 Angstrom,<br>4,500 Angstrom,<br>500 Angstrom, | 6,000-10,000<br>r Angstroms,<br>8,000 Angstrom<br>target<br>300-800<br>Angstroms,<br>target<br>300-800<br>Angstroms,<br>target<br>300-800<br>Angstrom<br>target<br>300-800<br>Angstrom<br>target<br>300-6,000<br>Angstroms,<br>4,500 Angstrom<br>target<br>300-800<br>use a parallel plate<br>30,000-6,000<br>Angstroms,<br>4,500 Angstrom<br>target<br>300-800<br>use a parallel plate<br>Angstroms,<br>4,500 Angstrom<br>target<br>300-800<br>use a parallel plate<br>Angstroms,<br>4,500 Angstrom<br>target<br>300-800<br>Angstroms,<br>4,500 Angstrom<br>target<br>300-800<br>Angstroms,<br>4,500 Angstrom<br>target<br>300-800<br>Angstroms,<br>3,000-6,000<br>Angstrom<br>target<br>300-800<br>Angstroms,<br>4,500 Angstrom<br>target<br>300-800<br>Angstroms,<br>3,000-6,000<br>Angstroms,<br>4,500 Angstrom<br>target<br>500 Angstrom<br>4,500 Angstrom<br>4,500 Angstrom<br>500 Angstrom<br>5 |

60

| TABLE | 1-continued |

|-------|-------------|

|-------|-------------|

| Wavelength of<br>Lithiography | Layer ID and<br>Material               | Thickness of Layer (range and target)                 | Useful Process<br>Information                                                                     | Refractive Index (N) | Extinction<br>Coefficient (K) |

|-------------------------------|----------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------|-------------------------------|

|                               | layer 20<br>(Si rich SiON)             | Angstroms,<br>600 Angstrom<br>target                  | RF reactor by<br>Applied Matenals,<br>flow all of SiH4,<br>N2O, and NH4, at<br>370° C. to 410° C. | being a target       | being a target                |

|                               | top dielectnc<br>layer<br>(TEOS layer) | 3,000–6,000<br>Angstroms,<br>4,500 Angstrom<br>target |                                                                                                   |                      |                               |

In addition, stoichiometric SION may be used in place of the silicon-rich SiON if formed to thicknesses above 1000 Angstroms with an N value of roughly 1.6 and a K value of roughly 0.0 at I-line (365 nm) lithographic exposure. Stoichiometric SiON when exposed with Deep UV was similar 20 since certain aspect ratios are better than others at reduce except that N was roughly 1.7 and K was roughly 0.03.

9

FIG. 2 illustrates that a photoresist layer 24 is spin coated or deposited over a top of the layer 22. A lithography mask is then placed between a light source or energy source and the photoresist 24. Energy or light is then passed selectively through the mask or altered by the mask to selectively expose portions of the photoresist 24. Generally, this exposure is I-line exposure at 365 nanometers. However, other lithographic processes such as deep UV at 248 nanometers, graphic wavelengths or processing may be used.

As previously stated, changes in the lithography process may require changes in the thicknesses, materials, placement, or processing of the dielectric stack 13 to further optimize the stack 13 to these environmental alterations. It 35 is important to note that the lithographic wavelength of light that used will generally determine the dimensions W, X, Y, and Z illustrated in FIG. 1. When using I-line lithography at 365 nanometers, a roughly 4000-5000 angstrom thickness of TEOS layer 22, a roughly 600 angstrom thickness of  $_{40}$ silicon rich SiON layer 20, a roughly 8000 angstrom thickness of TEOS layer 18, and a roughly 500 angstrom thickness of the plasma enhanced nitride (PEN) laver 16 creates interfaces 16A, 16B, 20A, and 20B at depths W, X, Y, and Z that prevent or substantially reduce adverse destructive 45 ings 26, the photoresist 24 is removed by an ashing process. interference and/or distortion when performing the lithographic step illustrated in FIG. 2 (see Table 1 above).

After the portions of the photoresist 24 are lithographically exposed as taught herein, a chemical development process is used to remove certain portions of the photoresist 50 24 selective to other portions of the photoresist. After photoresist development, the wafer is placed within a reactive ion etch (RIE) chamber or like plasma etch system whereby an oxide etch is used to remove portions of the layer 22 that are exposed by the openings in the photoresist 55 corners 40 and 41 as illustrated in FIG. 2. When placing a layer 24. This oxide etch is generally performed selective to the silicon rich silicon oxynitride (Si-SiON) layer 20. Optical endpoint detection or like endpoint techniques may be used to determine when a substantial portion of the layer 20 has been exposed through the dielectric layer 22. At this point, the etch chemistry is altered to a second etch chemistry which removes exposed portions of the SiON layer 20 within the openings in the photoresist 24.

It is important to note that the layer 20 is positioned at a relatively shallow height Y within the dielectric stack 13 to 65 result in improved optical properties within the dielectric stack 13 during lithographic operations. However, adequate

trench interconnect cross-sectional area is needed to produce acceptably low line resistance and to create desired aspect ratios for subsequent CVD, electroplating, electroless, or like copper fill operations. Proper aspect ratios are preferred voiding and key hole formation during copper fill operations. In order to provide for this optimal geometry or aspect ratio of the trench region 26, the trench region 26 is extended by an additional oxide etch a distance  $\Delta$  into the layer 18 as illustrated in FIG. 2. Generally,  $\Delta$  is a few hundred Angstroms to a few thousand Angstroms with about 1,000 Angstroms being typical. Generally, etch stop layers are used to ensure uniformity and repeatability within a dielectric stack etching process. Therefore, trenching beyond the phase shift lithography, x-ray, SCALPEL, or other litho- 30 depth of an etch stop layer via an additional timed etch is unusual in the art. However, due to current advances in conventional timed etch processing, the standard deviation from wafer-to-wafer and the standard deviation across a surface of a single wafer when performing the  $\Delta$  etch of layer 18 in FIG. 2 is very acceptable. This over-etch is so well controlled using modern oxide etch procedures that the dimension  $\Delta$  can be controlled to within a distribution of few tens or hundreds of angstroms for all openings 26 wafer-towafer and across the same wafer. Therefore, even though an additional trenching operation into layer 18 is performed, repeatable and consistent dimensions of a trench interconnect opening 26 are very possible since the dimension  $\Delta$  is only a fraction of the total depth of the trench interconnect region 26. After formation of the trench interconnect open-

> The positioning of the SiON layer 20 at a shallow depth the stack 13 and compensating for such shallow placement by a  $\Delta$  etch is advantageous for two reasons. First, this shallow positioning of the layer 20 improves the optical properties of the dielectric stack 13. An additional benefit from this shallow placement of the layer 20 along with the  $\Delta$  etch is that the SiON layer 20 is physically placed along a side wall of the trench region 26 so that layer 20 is physically removed vertically from the trench interconnect high dielectric constant material (e.g., silicon nitride with  $\in$ r~8) at these corners 40 and/or 41, the electrical performance of copper inlaid interconnects is degraded by greater direct current (DC) leakage and reduced high frequency performance. Therefore, the shallow positioning of layer 20 in the dielectric stack 13 for the purpose of optical improvements may have the side effect of also improving the electrical properties of the interconnect structure.

> FIG. 3 illustrates that a second photoresist layer 28 is deposited over a surface of the wafer after the openings 26 are formed via FIG. 2. A second masking, lithographic, and chemical development process is used in FIG. 3 to form via

50

60

openings within the photoresist 28 as illustrated in FIG. 3. These via openings in the photoresist 28 expose a via portion of the layer 18 within the trench interconnect 26. These via portions are etched by an oxide reactive ion etch (RIE) or a like plasma process until portions of the plasma enhanced nitride (PEN) layer 16 is exposed. At this point, via a timed etch or some form of etch endpointing, the etch chemistry and/or process parameters are switched to a plasma enhanced nitride etch which removes exposed portions of the layer 16 within the vias 30. In another embodiment, a 10 timed etch may be performed whereby no stopping on the nitride layer occurs. The resulting via openings 30 expose some portion of the regions 14a and 14b to enable electrical contact of the regions 14a and 14b to overlying metallurgy that is formed in later processing steps.