# SILCON VLSI TECHNOLOGY Fundamentals, Practice and Modeling

James D. Plummer • Michael D. Deal • Peter B. Griffin TSMC 1309 Prentice Hall Electronics and VLSI Series—Charles Sodini, Series Editor

# Silicon VLSI Technology

# **Fundamentals, Practice and Modeling**

James D. Plummer Michael Deal Peter B. Griffin

Department of Electrical Engineering Stanford University

Prentice Hall Upper Saddle River, NJ 07458

#### Library of Congress Cataloging-in-Publication Data

Silicon VLSI technology p. cm. ISBN 0-13-085037-3 1. Integrated circuits—Very large scale integration—Design and construction. 2. Silicon. 3. Silicon oxide films. 4. Metal oxide semiconductors. 5. Silicon technology. TK7874.75.S54 2000 621.39'5—dc21 99-42745

9-42745 CIP

Publisher: Tom Robbins Associate Editor: Alice Dworkin Editorial/Production Supervision: Rose Kernan Vice President and Editorial Director, ECS: Marcia Horton Vice President of Production and Manufacturing: David W. Riccardi Executive Managing Editor: Vince O'Brien Marketing Manager: Danny Hoyt Managing Editor: David A. George Manufacturing Buyer: Pat Brown Manufacturing Manager: Trudy Pisciotti Art Director: Jayne Conte Cover Design: Bruce Kenselaar Editorial Assistant: Jesse Power Copy Editor: Martha Williams Composition: D&G Limited, LLC

©2000 by Prentice Hall, Inc. Upper Saddle River, New Jersey 07458

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

The author and publisher of this book have used their best efforts in preparing this book. These efforts include the development, research, and testing of the theories and programs to determine their effectiveness. The author and publisher make no warranty of any kind, expressed or implied, with regard to these programs or the documentation contained in this book. The author and publisher shall not be liable in any event for incidental or consequential damages in connection with, or arising out of, the furnishing, performance, or use of these programs.

Printed in the United States of America

10 9 8 7 6 5 4 3 2

ISBN 0-13-085037-3

Prentice Hall International (UK) Limited, London Prentice Hall of Australia Pty. Limited, Sydney Prentice Hall Canada Inc., Toronto Prentice Hall Hispanoamericana, S.A., Mexico Prentice Hall of India Private Limited, New Delhi Prentice Hall of Japan, Inc., Tokyo Pearson Education Pte., Ltd., Singapore Editora Prentice<sup>†</sup> Hall do Brasil, Ltda., Rio de Janeiro

| Contents |  |

|----------|--|

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|           |       | Preface                                                             | xi  |

|-----------|-------|---------------------------------------------------------------------|-----|

| Chapter 1 | Intro | duction and Historical Perspective                                  | 1   |

|           | 1.1   | Introduction                                                        | . 1 |

|           | 1.2   | Integrated Circuits and the Planar Process—Key Inventions That Made |     |

|           |       | It All Possible                                                     | . 7 |

|           | 1.3   | Semiconductors                                                      | 13  |

|           | 1.4   | Semiconductor Devices                                               | 33  |

|           |       | 1.4.1 PN Diodes                                                     | 33  |

|           |       | 1.4.2 MOS Transistors                                               | 36  |

|           |       | 1.4.3 Bipolar Junction Transistors                                  | 39  |

|           | 1.5   | Semiconductor Technology Families.                                  | 41  |

|           | 1.6   | Modern Scientific Discovery-Experiments, Theory, and                |     |

|           |       | Computer Simulation                                                 | 43  |

|           | 1.7   | The Plan For This Book                                              | 45  |

|           | 1.8   | Summary of Key Ideas                                                | 46  |

|           | 1.9   | References                                                          |     |

|           | 1.10  | Problems                                                            |     |

# Chapter 2 Modern CMOS Technology

| 2.1 | Introdu | uction                                                       |

|-----|---------|--------------------------------------------------------------|

| 2.2 | CMOS    | Process Flow                                                 |

|     | 2.2.1   | The Beginning—Choosing a Substrate                           |

|     | 2.2.2   | Active Region Formation                                      |

|     | 2.2.3   | Process Option for Device Isolation—Shallow Trench Isolation |

|     | 2.2.4   | N and P Well Formation                                       |

|     | 2.2.5   | Process Options for Active Region and Well Formation         |

|     | 2.2.6   | Gate Formation                                               |

|     | 2.2.7   | Tip or Extension (LDD) Formation                             |

|     | 2.2.8   | Source/Drain Formation                                       |

|     | 2.2.9   | Contact and Local Interconnect Formation                     |

|     | 2.2.10  | Multilevel Metal Formation                                   |

| 2.3 | Summa   | rry of Key Ideas                                             |

| 2.4 | Probem  | ns                                                           |

| Chapter 3 | Cry<br>0 | ystal Growth, Wafer Fabrication and Basic Properties<br>of Silicon Wafers | 93  |

|-----------|----------|---------------------------------------------------------------------------|-----|

|           | 3.1      | Introduction                                                              |     |

|           | 3.2      | Historical Development and Basic Concepts                                 |     |

|           |          | 3.2.1 Crystal Structure                                                   |     |

|           |          | 3.2.2 Defects in Crystals                                                 |     |

|           |          | 3.2.3 Raw Materials and Purification                                      | 101 |

|           |          | 3.2.4 Czochralski and Float-Zone Crystal Growth Methods                   |     |

|           |          | 3.2.5 Wafer Preparation and Specification                                 |     |

|           | 3.3      | Manufacturing Methods and Equipment                                       |     |

|           | 3.4      | Measurement Methods.                                                      |     |

|           |          | 3.4.1 Electrical Measurements                                             |     |

|           |          | 3.4.1.1 Hot Point Probe                                                   |     |

|           |          | 3.4.1.2 Sheet Resistance                                                  |     |

|           |          | 3.4.1.3 Hall Effect Measurements                                          |     |

|           |          | 3.4.2 Physical Measurements                                               |     |

|           |          | 3.4.2.1 Defect Etches                                                     |     |

|           |          | 3.4.2.2 Fourier Transform Infrared Spectroscopy (FTIR)                    |     |

|           |          | 3.4.2.3 Electron Microscopy                                               |     |

|           | 3.5      | Models and Simulation.                                                    |     |

|           |          | 3.5.1 Czochralski Crystal Growth                                          |     |

|           |          | 3.5.2 Dopant Incorporation during CZ Crystal Growth                       |     |

|           |          | 3.5.3 Zone Refining and FZ Growth                                         | 128 |

|           |          | 3.5.4 Point Defects                                                       |     |

|           |          | 3.5.5 Oxygen in Silicon                                                   |     |

|           |          | 3.5.6 Carbon in Silicon                                                   |     |

|           |          | 3.5.7 Simulation                                                          |     |

|           | 3.6      | Limits and Future Trends in Technologies and Models                       |     |

|           | 3.7      | Summary of Key Ideas                                                      |     |

|           | 3.8      | References                                                                |     |

|           | 3.9      | Problems                                                                  |     |

| Chapter 4 | Sen      | niconductor Manufacturing—Clean Rooms, Wafer Cleaning,                    |     |

|           | a        | nd Gettering                                                              | 151 |

|           | 4.1      | Introduction                                                              | 151 |

|           | 4.2      | Historical Development and Basic Concepts                                 |     |

|           |          | 4.2.1 Level 1 Contamination Reduction: Clean Factories                    |     |

|           |          | 4.2.2 Level 2 Contamination Reduction: Wafer Cleaning                     |     |

|           |          | 4.2.3 Level 3 Contamination Reduction: Gettering                          |     |

|           | 4.3      | Manufacturing Methods and Equipment.                                      | 165 |

|           |          | 4.3.1 Level 1 Contamination Reduction: Clean Factories                    | 165 |

|           |          | 4.3.2 Level 2 Contamination Reduction: Wafer Cleaning.                    |     |

|           |          | 4.3.3 Level 3 Contamination Reduction: Gettering.                         | 167 |

|           | 4.4      | Measurement Methods.                                                      | 160 |

|           |          | 4.4.1 Level 1 Contamination Reduction: Clean Factories                    | 160 |

|           |          |                                                                           |     |

|     | 4.4.2   | Level 2  | Contamination Reduction: Wafer Cleaning                 | 173 |

|-----|---------|----------|---------------------------------------------------------|-----|

|     | 4.4.3   | Level 3  | Contamination Reduction: Gettering.                     | 176 |

| 4.5 | Models  | and Sim  | ulation                                                 | 180 |

|     | 4.5.1   | Level 1  | Contamination Reduction: Clean Factories                | 181 |

|     | 4.5.2   | Level 2  | Contamination Reduction: Wafer Cleaning.                | 184 |

|     | 4.5.3   |          | Contamination Reduction: Gettering.                     |     |

|     |         | 4.5.3.1  | Step 1: Making the Metal Atoms Mobile                   |     |

|     |         | 4.5.3.2  | Step 2: Metal Diffusion to the Gettering Site           |     |

|     |         | 4.5.3.3  | Step 3: Trapping the Metal Atoms at the Gettering Site. | 190 |

| 4.6 | Limits  | and Futu | re Trends in Technologies and Models                    | 193 |

| 4.7 |         |          | y Ideas                                                 |     |

| 4.7 |         | <i>,</i> | ·                                                       |     |

| 4.9 | Problei | ms       |                                                         | 198 |

|     |         |          |                                                         |     |

|     |         |          |                                                         |     |

# Chapter 5 Lithography

-

| 5.1 | Introd          | uction                                                            | 201 |

|-----|-----------------|-------------------------------------------------------------------|-----|

| 5.2 |                 | ical Development and Basic Concepts                               |     |

| 5.4 | 5.2.1           | Light Sources.                                                    |     |

|     | 5.2.1           | Wafer Exposure Systems                                            |     |

|     | S & hand & hand | 5.2.2.1 Optics Basics—Ray Tracing and Diffraction                 |     |

|     |                 | 5.2.2.2 Projection Systems (Fraunhofer Diffraction)               |     |

|     |                 | 5.2.2.3 Contact and Proximity Systems (Fresnel Diffraction)       |     |

|     | 5.2.3           | Photoresists                                                      |     |

|     | 01200           | 5.2.3.1 g-line and i-line Resists                                 |     |

|     |                 | 5.2.3.2 Deep Ultraviolet (DUV) Resists                            |     |

|     |                 | 5.2.3.3 Basic Properties and Characterization of Resists          |     |

|     | 5.2.4           | Mask Engineering—Optical Proximity Correction and Phase Shifting. |     |

| 5.3 | Manuf           | facturing Methods and Equipment.                                  |     |

|     | 5.3.1           | Wafer Exposure Systems                                            |     |

|     | 5.3.2           | Photoresists                                                      |     |

| 5.4 | Measu           | rement Methods                                                    | 241 |

|     | 5.4.1           | Measurement of Mask Features and Defects                          | 242 |

|     | 5.4.2           | Measurement of Resist Patterns                                    | 244 |

|     | 5.4.3           | Measurement of Etched Features.                                   | 244 |

| 5.5 | Mode            | ls and Simulation                                                 | 246 |

|     | 5.5.1           | Wafer Exposure Systems                                            | 247 |

|     | 5.5.2           | Optical Intensity Pattern in the Photoresist                      | 253 |

|     | 5.5.3           | Photoresist Exposure                                              |     |

|     |                 | 5.5.3.1 g-line and i-line DNQ Resists.                            |     |

|     |                 | 5.5.3.2 DUV Resists                                               |     |

|     | 5.5.4           | Postexposure Bake (PEB)                                           |     |

|     |                 | 5.5.4.1 g-line and i-line DNQ Resists                             |     |

|     |                 | 5.5.4.2 DUV Resists                                               |     |

|     | 5.5.5           | Photoresist Developing                                            |     |

|     | 5.5.6           | Photoresist Postbake                                              | 270 |

|           | 7.1 | Introduction.                                                                                                                                                                                                    | 371 |

|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 7 | Doj | pant Diffusion                                                                                                                                                                                                   | 371 |

|           | 6.9 | Problems                                                                                                                                                                                                         | 364 |

|           | 6.8 | References                                                                                                                                                                                                       |     |

|           | 6.7 | Summary of Key Ideas                                                                                                                                                                                             |     |

|           | 6.6 | Limits and Future Trends in Technologies and Models                                                                                                                                                              |     |

|           |     | 6.5.14 Complete Oxidation Module Simulation                                                                                                                                                                      |     |

|           |     | 6.5.13 Si/SiO <sub>2</sub> Interface Charges                                                                                                                                                                     |     |

|           |     | 6.5.12 Silicide Oxidation                                                                                                                                                                                        |     |

|           |     | 6.5.11 Si <sub>3</sub> N <sub>4</sub> Growth and Oxidation Kinetics                                                                                                                                              |     |

|           |     | 6.5.10 Polysilicon Oxidation                                                                                                                                                                                     |     |

|           |     | 6.5.9 Substrate Doping Effects.                                                                                                                                                                                  |     |

|           |     | 6.5.8 Advanced Point Defect Based Models for Oxidation                                                                                                                                                           |     |

|           |     | $6.5.6  \text{Mixed Ambient Growth Kinetics} \\ 6.5.7  2D \text{ SiO}_2 \text{ Growth Kinetics} \\ \dots $ |     |

|           |     | <ul><li>6.5.5 Dependence of Growth Kinetics on Crystal Orientation</li><li>6.5.6 Mixed Ambient Growth Kinetics</li></ul>                                                                                         |     |

|           |     | 6.5.4 Dependence of Growth Kinetics on Pressure                                                                                                                                                                  |     |

|           |     | 6.5.3 Thin Oxide $SiO_2$ Growth Kinetics                                                                                                                                                                         |     |

|           |     | 6.5.2 Other Models for Planar Oxidation Kinetics                                                                                                                                                                 |     |

|           |     | 6.5.1 First-Order Planar Growth Kinetic — The Linear Parabolic Model                                                                                                                                             |     |

|           | 6.5 | Models and Simulation                                                                                                                                                                                            |     |

|           |     | 6.4.3 Electrical Measurements—The MOS Capacitor                                                                                                                                                                  | 301 |

|           |     | 6.4.2 Optical Measurements                                                                                                                                                                                       |     |

|           |     | 6.4.1 Physical Measurements                                                                                                                                                                                      |     |

|           | 6.4 | Measurement Methods.                                                                                                                                                                                             |     |

|           | 6.3 | Manufacturing Methods and Equipment.                                                                                                                                                                             |     |

|           | 6.2 | Historical Development and Basic Concepts                                                                                                                                                                        |     |

|           | 6.1 | Introduction                                                                                                                                                                                                     | 287 |

| Chapter 6 | The | ermal Oxidation and the Si/SiO <sub>2</sub> Interface                                                                                                                                                            | 287 |

|           | 5.9 | Problems                                                                                                                                                                                                         | 205 |

|           | 5.8 | References                                                                                                                                                                                                       |     |

|           | 5.7 | Summary of Key Ideas                                                                                                                                                                                             |     |

|           |     | 5.6.4 New Resists                                                                                                                                                                                                |     |

|           |     | 5.6.3 Advanced Mask Engineering                                                                                                                                                                                  |     |

|           |     | 5.6.2 X-ray Lithography                                                                                                                                                                                          |     |

|           | 5.0 | 5.6.1 Electron Beam Lithography                                                                                                                                                                                  |     |

|           | 5.6 | Limits and Future Trends in Technologies and Models                                                                                                                                                              |     |

|           |     | 5.5.7 Advanced Mask Engineering                                                                                                                                                                                  | 271 |

| 7.1 | Introdu | iction                                       |

|-----|---------|----------------------------------------------|

| 7.2 | Histori | cal Development and Basic Concepts           |

|     | 7.2.1   | Dopant Solid Solubility                      |

|     | 7.2.2   | Diffusion from a Macroscopic Viewpoint       |

|     | 7.2.3   | Analytic Solutions of the Diffusion Equation |

|     | 7.2.4   | Gaussian Solution in an Infinite Medium      |

|     |         |                                              |

|       | 7.2.5   | Gaussian Solution Near a Surface                                   | 381 |

|-------|---------|--------------------------------------------------------------------|-----|

|       | 7.2.6   | Error-Function Solution in an Infinite Medium                      | 382 |

|       | 7.2.7   | Error-Function Solution Near a Surface                             | 384 |

|       | 7.2.8   | Intrinsic Diffusion Coefficients of Dopants in Silicon             | 386 |

|       | 7.2.9   | Effect of Successive Diffusion Steps                               |     |

|       | 7.2.10  | Design and Evaluation of Diffused Layers                           |     |

|       | 7.2.11  | Summary of Basic Diffusion Concepts                                |     |

| 7.3   | Manufa  | acturing Methods and Equipment.                                    |     |

| 7.4   |         | rement Methods                                                     |     |

|       | 7.4.1   | SIMS                                                               | 396 |

|       | 7.4.2   | Spreading Resistance                                               | 397 |

|       | 7.4.3   | Sheet Resistance                                                   | 398 |

|       | 7.4.4   | Capacitance Voltage                                                | 399 |

|       | 7.4.5   | TEM Cross Section.                                                 |     |

|       | 7.4.6   | 2D Electrical Measurements Using Scanning Probe Microscopy         | 400 |

|       | 7.4.7   | Inverse Electrical Measurements                                    | 402 |

| 7.5   | Models  | and Simulation                                                     | 403 |

|       | 7.5.1   | Numerical Solutions of the Diffusion Equation                      | 403 |

|       | 7.5.2   | Modifications to Fick's Laws to Account for Electric Field Effects | 406 |

|       | 7.5.3   | Modifications to Fick's Laws to Account for                        |     |

|       |         | Concentration-Dependent Diffusion                                  | 409 |

|       | 7.5.4   | Segregation                                                        | 413 |

|       | 7.5.5   | Interfacial Dopant Pileup                                          |     |

|       | 7.5.6   | Summary of the Macroscopic Diffusion Approach                      | 417 |

|       | 7.5.7   | The Physical Basis for Diffusion at an Atomic Scale                |     |

|       | 7.5.8   | Oxidation-Enhanced or -Retarded Diffusion                          |     |

|       | 7.5.9   | Dopant Diffusion Occurs by Both I and V                            |     |

|       | 7.5.10  | Activation Energy for Self-Diffusion and Dopant Diffusion          |     |

|       | 7.5.11  | Dopant-Defect Interactions                                         | 426 |

|       | 7.5.12  | Chemical Equilibrium Formulation for Dopant-Defect Interactions .  |     |

|       | 7.5.13  | Simplified Expression for Modeling.                                |     |

|       | 7.5.14  | Charge State Effects                                               |     |

| 7.6   |         | and Future Trends in Technologies and Models                       |     |

|       | 7.6.1   | Doping Methods                                                     | 440 |

|       | 7.6.2   | Advanced Dopant Profile Modeling—Fully Kinetic Description         |     |

|       |         | of Dopant-Defect Interactions                                      |     |

| 7.7   |         | rry of Key Ideas                                                   |     |

| 7.8   |         | nces                                                               |     |

| 7.9   | Probler | ns                                                                 | 445 |

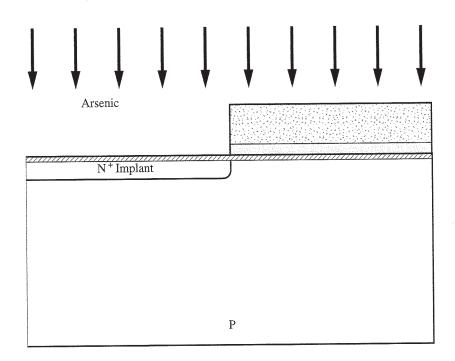

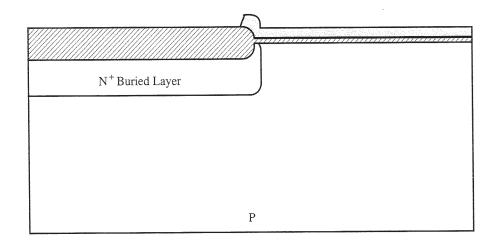

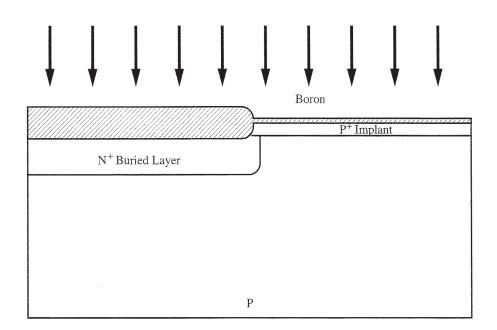

| Ion I | mplant  | ation                                                              | 451 |

| 8.1 | Introduction                                                     |

|-----|------------------------------------------------------------------|

| 8.2 | Historical Development and Basic Concepts                        |

|     | 8.2.1 Implants in Real Silicon—The Role of the Crystal Structure |

| 8.3 | Manufacturing Methods and Equipment                              |

Chapter 8

|           |     | 8.3.1 High-Energy Implants                                      | 466       |

|-----------|-----|-----------------------------------------------------------------|-----------|

|           |     | 8.3.2 Ultralow Energy Implants                                  |           |

|           |     | 8.3.3 Ion Beam Heating                                          |           |

|           | 8.4 | Measurement Methods                                             |           |

|           | 8.5 | Models and Simulations                                          |           |

|           |     | 8.5.1 Nuclear Stopping                                          |           |

|           |     | 8.5.2 Nonlocal Electronic Stopping                              |           |

|           |     | 8.5.3 Local Electronic Stopping                                 |           |

|           |     | 8.5.4 Total Stopping Powers                                     |           |

|           |     | 8.5.5 Damage Production                                         |           |

|           |     | 8.5.6 Damage Annealing                                          |           |

|           |     | 8.5.7 Solid-Phase Epitaxy                                       |           |

|           |     | 8.5.8 Dopant Activation                                         |           |

|           |     | 8.5.9 Transient-Enhanced Diffusion                              |           |

|           |     | 8.5.10 Atomic-Level Understanding of TED                        |           |

|           |     | 8.5.11 Effects on Devices                                       |           |

|           | 8.6 | Limits and Future Trends in Technologies and Models             |           |

|           | 8.7 | Summary of Key Ideas                                            |           |

|           | 8.8 | References                                                      | 500       |

|           | 8.9 | Problems                                                        |           |

| Chapter 9 | Thi | in Film Deposition                                              | 509       |

|           | 9.1 | Introduction                                                    | 509       |

|           | 9.2 | Historical Development and Basic Concepts                       |           |

|           |     | 9.2.1 Chemical Vapor Deposition (CVD)                           | 512       |

|           |     | 9.2.1.1 Atmospheric Pressure Chemical Vapor Deposition (A       | PCVD) 513 |

|           |     | 9.2.1.2 Low-Pressure Chemical Vapor Deposition (LPCVD).         | 525       |

|           |     | 9.2.1.3 Plasma-Enhanced Chemical Vapor Deposition (PECV         |           |

|           |     | 9.2.1.4 High-Density Plasma Chemical Vapor Deposition           | 2)        |

|           |     | (HDPCVD)                                                        | 530       |

|           |     | 9.2.2 Physical Vapor Deposition (PVD)                           |           |

|           |     | 9.2.2.1 Evaporation                                             |           |

|           |     | 9.2.2.2 Sputter Deposition                                      | 539       |

|           | 9.3 | Manufacturing Methods                                           | 554       |

|           |     | 9.3.1 Epitaxial Silicon Deposition                              |           |

|           |     | 9.3.2 Polycrystalline Silicon Deposition                        | 558       |

|           |     | 9.3.3 Silicon Nitride Deposition                                | 561       |

|           |     | 9.3.4 Silicon Dioxide Deposition                                | 563       |

|           |     | 9.3.5 Al Deposition                                             | 565       |

|           |     | 9.3.6 Ti and Ti-W Deposition                                    | 566       |

|           |     | 9.3.7 W Deposition                                              | 567       |

|           |     | 9.3.8 TiSi <sub>2</sub> and WSi <sub>2</sub> Deposition $\dots$ | 567       |

|           |     | 9.3.9 TiN Deposition                                            |           |

|           |     | 9.3.10 Cu Deposition                                            |           |

|           | 9.4 | Measurement Methods.                                            |           |

|           |     |                                                                 |           |

|            | 9.5  | Models and Simulation                                         | 573   |

|------------|------|---------------------------------------------------------------|-------|

|            | 2.00 | 9.5.1 Models for Deposition Simulations                       |       |

|            |      | 9.5.1.1 Models in Physically Based Simulators Such as SPEEDIE |       |

|            |      | 9.5.1.2 Models for Different Types of Deposition Systems      |       |

|            |      | 9.5.1.3 Comparing CVD and PVD and Typical Parameter Values    |       |

|            |      | 9.5.2 Simulations of Deposition Using a Physically Based      |       |

|            |      | Simulator, SPEEDIE                                            | 590   |

|            |      | 9.5.3 Other Deposition Simulations                            |       |

|            | 9.6  | Limits and Future Trends in Technologies and Models           |       |

|            | 9.7  | Summary of Key Ideas                                          | 602   |

|            | 9.8  | References                                                    |       |

|            | 9.9  | Problems                                                      | 605   |

| Chapter 10 | Etch | ling                                                          | 609   |

| 1          | 10.1 | Introduction                                                  | 609   |

|            | 10.1 | Historical Development and Basic Concepts                     |       |

|            | 10.2 | 10.2.1 Wet Etching                                            |       |

|            |      | 10.2.1     Plasma Etching                                     |       |

|            |      | 10.2.2 Plasma Etching Mechanisms                              | . 621 |

|            |      | 10.2.2.2 Twise of Diagno Etab Systems                         |       |

|      |                      | 10.2.2.1           | Flashia Etchnig Mechanishis            |     |  |

|------|----------------------|--------------------|----------------------------------------|-----|--|

|      |                      | 10.2.2.2           | Types of Plasma Etch Systems           |     |  |

|      |                      | 10.2.2.3           |                                        |     |  |

| 10.3 | Manufa               |                    | ſethods                                |     |  |

|      | 10.3.1               |                    | Etching Conditions and Issues          |     |  |

|      | 10.3.2               |                    | Etch Methods for Various Films         |     |  |

|      |                      | 10.3.2.1           | Plasma Etching Silicon Dioxide         | 644 |  |

|      |                      | 10.3.2.2           |                                        | 647 |  |

|      |                      | 10.3.2.3           | Plasma Etching Aluminum                | 649 |  |

| 10.4 |                      |                    | ethods                                 |     |  |

| 10.5 | Models               | els and Simulation |                                        |     |  |

|      | 10.5.1               | Models f           | for Etching Simulation                 |     |  |

|      | 10.5.2               |                    | Models—Linear Etch Model               |     |  |

|      | 10.5.3               | Etching            | Models—Saturation/Adsorption Model for |     |  |

|      |                      | Ion-E              | nhanced Etching                        |     |  |

|      | 10.5.4               | Etching            | Models—More Advanced Models            | 669 |  |

|      | 10.5.5               | Other E            | tching Simulations                     | 671 |  |

| 10.6 | Limits               | and Futur          | re Trends in Technologies and Models   |     |  |

| 10.7 | Summary of Key Ideas |                    |                                        |     |  |

| 10.8 |                      |                    |                                        |     |  |

| 10.9 | Proble               | ms                 |                                        | 679 |  |

|      |                      |                    |                                        |     |  |

# Chapter 11 Back-End Technology

| 11.1 | Introdu | ıction                             | 1 |

|------|---------|------------------------------------|---|

|      |         | cal Development and Basic Concepts |   |

|      | 11.2.1  | Contacts                           | 8 |

|      |         | Interconnects and Vias             |   |

|      | 11.2.3   | Dielectrics                                  |  |

|------|----------|----------------------------------------------|--|

| 11.3 | Manufa   | acturing Methods and Equipment               |  |

|      | 11.3.1   | Silicided Gates and Source/Drain Regions     |  |

|      | 11.3.2   | First-level Dielectric Processing            |  |

|      | 11.3.3   | Contact Formation                            |  |

|      | 11.3.4   | Global Interconnects                         |  |

|      | 11.3.5   | IMD Deposition and Planarization             |  |

|      | 11.3.6   | Via Formation                                |  |

|      | 11.3.7   | Final Steps                                  |  |

| 11.4 | Measu    | ement Methods                                |  |

|      | 11.4.1   | Morphological Measurements                   |  |

|      | 11.4.2   | Electrical Measurements                      |  |

|      | 11.4.3   | Chemical and Structural Measurements         |  |

|      | 11.4.4   | Mechanical Measurements                      |  |

| 11.5 | Models   | and Simulation                               |  |

|      | 11.5.1   | Silicide Formation                           |  |

|      | 11.5.2   | Chemical-Mechanical Polishing                |  |

|      | 11.5.3   | Reflow                                       |  |

|      | 11.5.4   | Grain Growth                                 |  |

|      | 11.5.5   | Diffusion in Polycrystalline Materials       |  |

|      | 11.5.6   | Electromigration                             |  |

| 11.6 | Limits a | and Future Trends in Technologies and Models |  |

| 11.7 | Summa    | ry of Key Ideas                              |  |

| 11.8 | Referen  | nces                                         |  |

| 11.9 | Problem  | ns                                           |  |

|      |          |                                              |  |

# Appendices

## 787

| A.1  | Standard Prefixes                                                                             | 787 |

|------|-----------------------------------------------------------------------------------------------|-----|

| A.2  | Useful Conversions                                                                            |     |

| A.3  | Physical Constants                                                                            |     |

| A.4  | Physical Properties of Silicon                                                                |     |

| A.5  | Properties of Insulators Used in Silicon Technology                                           |     |

| A.6  | Color Chart for Deposited Si <sub>3</sub> N <sub>4</sub> Films Observed Perpendicularly under |     |

|      | Daylight Fluorescent Lighting.                                                                | 789 |

| A.7  | Color Chart for Thermally Grown SiO <sub>2</sub> Films Observed Perpendicularly               |     |

|      | under Daylight Fluorescent Lighting                                                           | 790 |

| A.8  | Irwin Curves                                                                                  | 791 |

| A.9  | Error Function                                                                                | 793 |

| A.10 | List of Important Symbols                                                                     |     |

| A.11 | List of Common Acronyms                                                                       |     |

| A.12 | Tables in Text                                                                                |     |

| A.13 | Answers to Selected Problems                                                                  |     |

### Index

# Modern CMOS Technology

#### 2.1 Introduction

In most of the remaining chapters in this book, we will discuss the process technologies used in silicon IC manufacturing individually. Individual technologies are clearly most useful when they are combined in a complete process flow sequence to produce chips. It is often the case that unit process steps are designed the way that they are because of the context in which those steps are used. For example, while a dopant may be diffused into a semiconductor to a desired final junction depth using many combinations of times and temperatures, the fact that the junction being formed might be diffused in the middle of a complex process flow may greatly restrict the possible choices of times and temperatures. In other words, the wafer's past history and the future process steps it may see can greatly influence how one chooses to perform a particular unit process step.

For this reason, and because we believe that understanding how complete process flows are put together aids understanding of individual process steps, we will describe in this chapter a complete modern Very Large Scale Integrated (VLSI) circuit process flow. The example we have chosen is typical of today's state of the art. CMOS technology has dominated silicon integrated circuits for the past 15 years and most people in the industry today believe that its dominance will continue for the foreseeable future for the reasons discussed in Chapter 1 (high performance, low power, supply voltage scalability, and circuit flexibility). In fact the SIA industry roadmap (NTRS) that we discussed in Chapter 1 assumes the continuation of CMOS technology through at least 2012.

For readers who are new to silicon technology, some of the ideas introduced in this chapter may not be fully appreciated until after later chapters on individual process steps have been read. However, we recommend that such people read this chapter before proceeding further because doing so will make the later material more understandable. A second reading of this chapter after the remainder of the book has been studied may also prove useful. In many cases, typical process conditions that might be used in a given step are presented in this chapter without full explanation. This is simply because we have not yet discussed the quantitative models and other tools at our disposal to calculate such parameters. As we do so in later chapters, we will revisit the CMOS process flow described here and discuss in more detail the reasons for particular process conditions used in this chapter.

#### 2.2 CMOS Process Flow

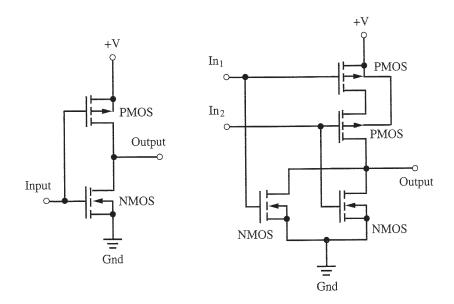

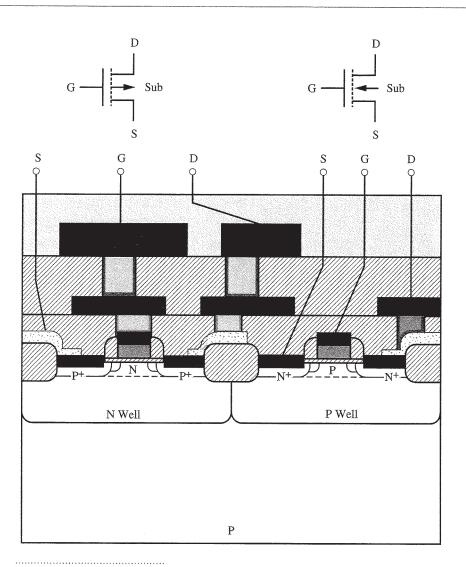

Two typical CMOS circuits are shown in Figure 2–1. The simple inverter circuit on the left was described in Chapter 1. The NOR gate on the right illustrates how additional NMOS and PMOS devices can be added to the inverter circuit to realize more complex logic functions. In the NOR circuit, if either input 1 or input 2 or both of them are high, the output will be pulled to ground through one or both of the NMOS devices which will be turned on. Only if both inputs are low will the output be pulled high through the two series PMOS devices that are both turned on under this condition. The circuit thus implements the NOR function. To build these types of circuits, we need a technology that can integrate NMOS and PMOS devices on the same chip. In fact, many CMOS technologies also implement various types of resistors, capacitors, thin film transistors, and perhaps other types of devices as well. We will limit our discussion here to the two basic devices and describe a technology to build them. Extensions of this technology to include other components are reasonably straightforward and we will see some examples of such extensions in later chapters.

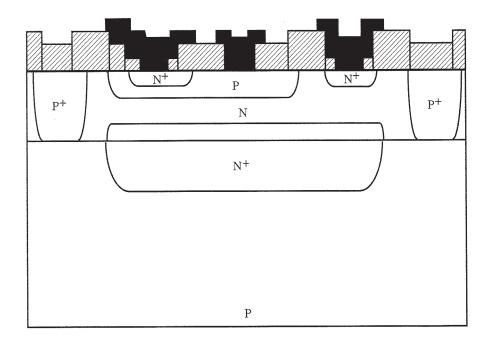

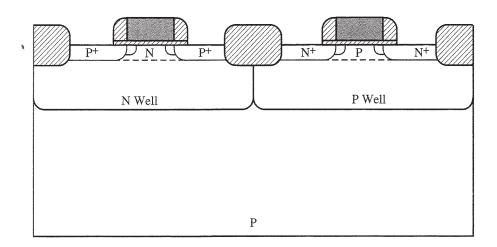

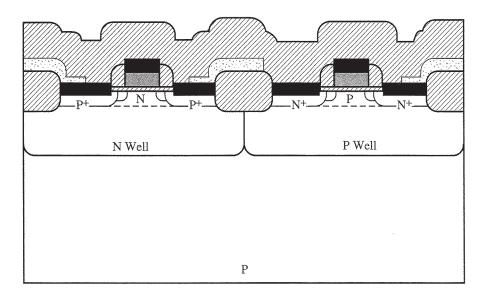

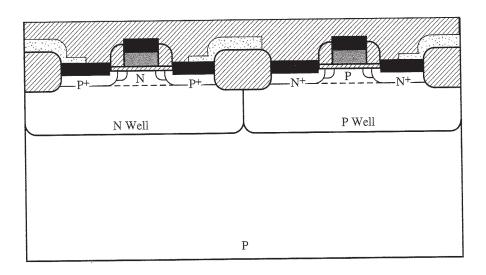

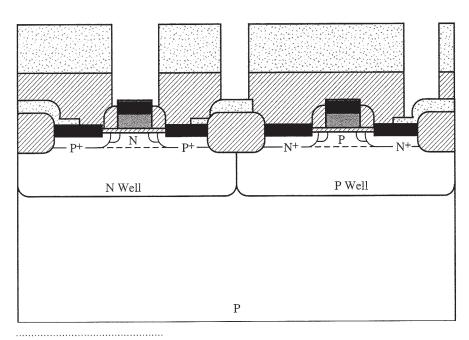

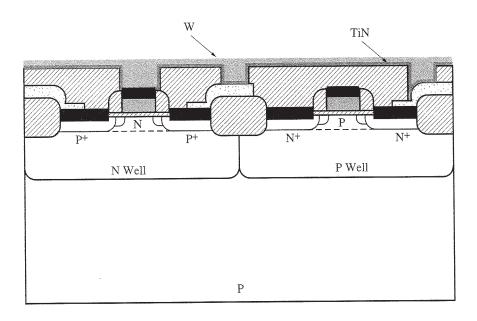

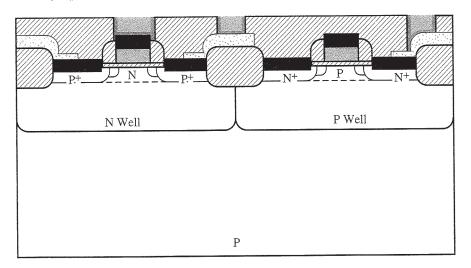

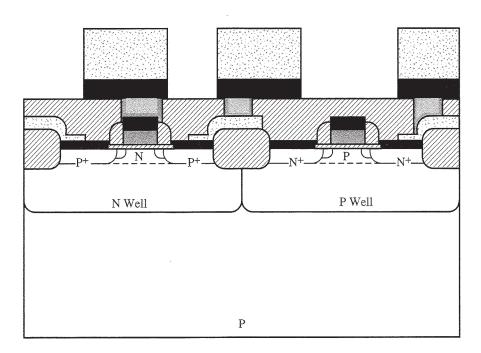

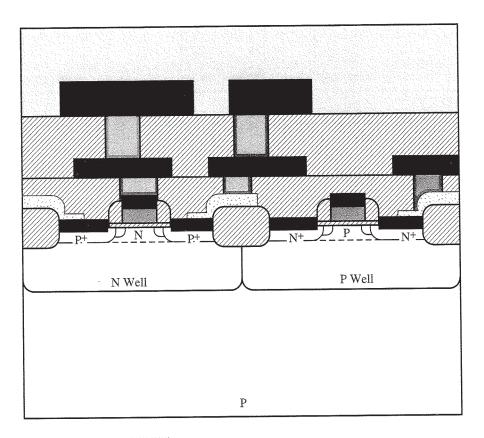

The end result of the process flow we will discuss is shown in Figure 2–2. To fabricate a structure like this, we will find that 16 photolithography steps and well over 100 individual process steps are required. The final integrated circuit may contain millions of components like those shown in the figure, each of which must work correctly.

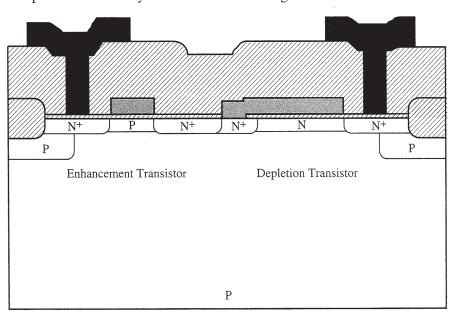

There are two active device types shown in the figure, corresponding to those required to implement the circuits in Figure 2–1. The individual source, drain, and gate regions of the NMOS and PMOS devices are identifiable in the cross section. In addition to the active devices, there are many other parts to the overall structure. Some of this "overhead" is required to electrically isolate the active devices from each other. Other

**Figure 2–1** Simple CMOS circuits. An inverter is shown on the left and a NOR circuit on the right. The NOR circuit implements the function Output  $= \overline{IN_1 + IN_2}$ .

**Figure 2–2** Coss section of the final CMOS integrated circit. A PMOS transistor is shown on the left, an NMOS device on the right.

parts of the structure provide multiple wiring levels above the active devices to interconnect them to perform particular circuit functions. Finally, some regions are included simply to improve the performance of the individual devices by decreasing parasitic resistances or improving voltage ratings. As we proceed through the steps required to build this chip, we will discuss each of these points in greater detail.

#### 2.2.1 The Beginning—Choosing a Substrate

Before we begin actual wafer fabrication, we must of course choose the starting wafers. In general this means specifying type (N or P), resistivity (doping level), crystal orientation, wafer size, and a number of other parameters having to do with wafer flatness, trace impurity levels, and so on. The major choices are the type, resistivity, and orientation.

Figure 2–2 indicates that the final structure has a P-type substrate. In most CMOS integrated circuits, the substrate has a moderately high resistivity (25–50  $\Omega$ cm) which corresponds to a doping level on the order of  $10^{15}$  cm<sup>-3</sup> (Figure 1–18). As is apparent from Figure 2–2, the active devices are actually built in wells diffused into the surface of the wafer. The doping levels in these wells are chosen to optimize the electrical properties of the active devices, as we will see later in this chapter. Typically the well doping levels are on the order of  $10^{16} - 10^{17}$  cm<sup>-3</sup> near the wafer surface. In order to reproducibly manufacture such wells, the background doping (the substrate doping in this case) needs to be significantly less than the well doping. Thus the substrate doping is normally chosen to be on the order of  $10^{15}$  cm<sup>-3</sup>.

The observant reader might notice that the NMOS device could actually be built directly in the P substrate without adding the P well near the surface. In fact this is exactly the way the structure was sketched in Figure 1–34 for simplicity. While some CMOS circuits are actually built this way today, the twin well process illustrated in Figure 2–2 is much more common because the doping process used to produce the P well (ion implantation) is much better controlled in manufacturing than is the substrate doping. Also, since the P well and N well doping concentrations are on the same order, it is easier to start with a much more lightly doped substrate and tailor the wells for the NMOS and PMOS devices individually.

The observant reader might also note in Figure 1–34 that a substrate consisting of a P layer on a  $P^+$  substrate was illustrated. This is one of the technology options we will consider later in Section 2.2.5.

The only other major parameter we need to specify in the starting substrate is the crystal orientation. We will discuss crystal structure in more detail in Chapter 3. However, virtually all modern silicon integrated circuits are manufactured today from wafers with a (100) surface orientation. The principal reason for this is that the properties of the Si/SiO<sub>2</sub> interface are significantly better when a (100) crystal is used. We will discuss the reasons for this in detail in Chapter 6, but the key idea is that the electrical properties of this interface are intimately connected with the atomic bonding between Si and O that takes place when an SiO<sub>2</sub> layer is thermally grown on Si. It is found experimentally that there are fewer imperfections (unsatisfied bonds) on a (100) surface than is the case on other silicon surfaces. Primarily for this reason, we will choose a (100) surface orientation for our starting wafers.

We will also discuss in Chapter 4 some processing which is often done on the starting substrates before any actual device fabrication is begun. This processing is aimed at minimizing the sensitivity of the wafers to trace contaminants that can be introduced to the wafers during the many manufacturing steps they go through to build circuits. These preliminary processing steps are called gettering and the most common process today is known as "intrinsic gettering." Since these steps are not essential to the device fabrication process, we will defer discussion of them to Chapter 4.

#### 2.2.2 Active Region Formation

Modern CMOS chips integrate millions of active devices (NMOS and PMOS) side by side in a common silicon substrate. Circuits are designed with these devices to imple-

ment complex logic or analog functions. In designing such circuits, it is usually assumed that the individual devices do not interact with each other except through their circuit interconnections. In other words, we need to make certain that the individual devices on the chip are electrically isolated from each other. This is accomplished most often by growing a fairly thick layer of  $SiO_2$  in between each of the active devices.  $SiO_2$  is essentially a perfect insulator and provides the needed isolation. This process of locally oxidizing the silicon substrate is known as the LOCOS process (LOCal Oxidation of Silicon). The regions between these thick  $SiO_2$  layers, where transistors will be built, are called the "active" regions of the substrate.

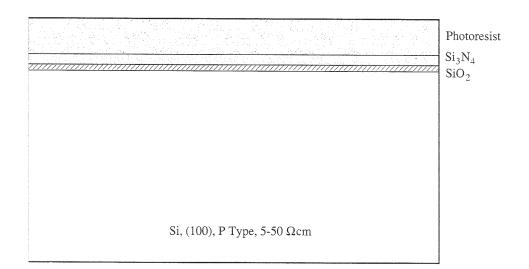

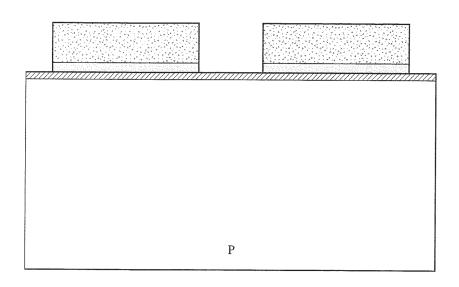

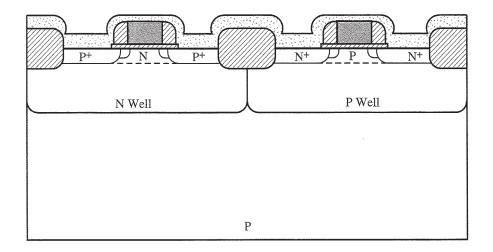

We begin with the steps shown in Figure 2–3. The wafers are first cleaned in a combination of chemical baths that remove any impurities from the surface. A thermal SiO<sub>2</sub> layer is then grown on the Si surface by placing the wafers in a high-temperature furnace. A typical furnace cycle might be 15 minutes at 900°C in an H<sub>2</sub>O atmosphere. Although the H<sub>2</sub>O ambient could be produced by boiling water, it is more common today to actually react H<sub>2</sub> and O<sub>2</sub> in the back end of the furnace to produce H<sub>2</sub>O. This is generally a cleaner method for generating the steam required for the oxidation. The furnace cycle described above would produce an oxide of about 40 nm (400 Å). Such an oxide could also be grown in a pure O<sub>2</sub> ambient using a cycle of about 45 min at 1000°C. The oxide growth rate is much slower in O<sub>2</sub> compared to H<sub>2</sub>O (Chapter 6), so higher temperatures and/or longer times are required in O<sub>2</sub> to grow the same oxide thickness.

The wafers are then transferred to a second furnace, which is used to deposit a thin layer of  $Si_3N_4$  (typically 80 nm). This deposition occurs when reactants like  $NH_3$  and  $SiH_4$  are introduced into the furnace at a temperature of about 800°C, forming  $Si_3N_4$  through a simple chemical reaction such as

$$3\mathrm{SiH}_4 + 4\mathrm{NH}_3 \rightarrow \mathrm{Si}_3\mathrm{N}_4 + 12\mathrm{H}_2 \tag{2.1}$$

**Figure 2–3** Following initial cleaning, an SiO<sub>2</sub> layer is thermally grown on the silicon substrate. A Si<sub>3</sub>N<sub>4</sub> layer is then deposited by LPCVD. Photoresist is spun on the wafer to prepare for the first masking operation.

Generally this deposition is done below atmospheric pressure because this produces better uniformity over larger wafer lots in the deposited films. Pumps are normally used on the furnace exhaust to reduce the pressure. Systems in which such depositions are done are usually called Low-Pressure Chemical Vapor Deposition (LPCVD) systems. We will discuss them in more detail in Chapter 9.

The nitride layers deposited by such machines are normally highly stressed, with the  $Si_3N_4$  under tensile stress. This produces a large compressive stress in the underlying Si substrate which can lead to defect generation if it is not carefully controlled. In fact, the major purpose of the SiO<sub>2</sub> layer under the Si<sub>3</sub>N<sub>4</sub> is to help relieve this stress. SiO<sub>2</sub> layers are under compressive stress when they are thermally grown on Si and if the thicknesses of the SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> layers are properly chosen, the stresses in the two layers can partially compensate each other, reducing the stresses in the Si substrate. The thicknesses chosen above do this.

The final step in Figure 2–3 is the deposition of a photoresist layer in preparation for masking. Since photoresists are liquids at room temperature, they are normally simply spun onto the wafers. The resist viscosity and the spin speed determine the final resist thickness, which is typically about 1  $\mu$ m. (Note that the dimensions in all the drawings in this book are not exactly to scale, since the photoresist layer in Figure 2–3 is really more than 10 times the thickness of the oxide or nitride layers, and the substrate is typically 500 times as thick as the photoresist layer. The liberties we take with scale in these drawings are intended to improve clarity.)

After the photoresist is spun onto the wafer, it is usually baked at about 100°C in order to drive off solvents from the layer. The resist is then exposed using a mask, which defines the pattern for the LOCOS regions. The photolithography process is both complex and expensive and was illustrated conceptually in Figure 1–9. We will describe it in much greater detail in Chapter 5. The machines which accomplish the exposure are often called "steppers" because they usually expose only a small area of the wafer during each exposure and then "step" to the next adjacent field to expose. Such machines must be capable today of printing lines on the order of 250 nm (0.25  $\mu$ m) and placing these patterns on the wafer with an accuracy which is < 100 nm. They typically cost several million dollars.

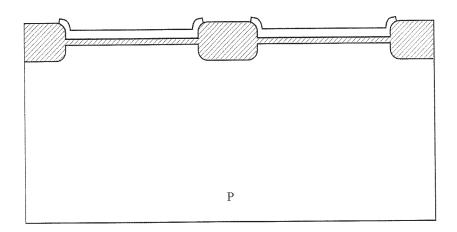

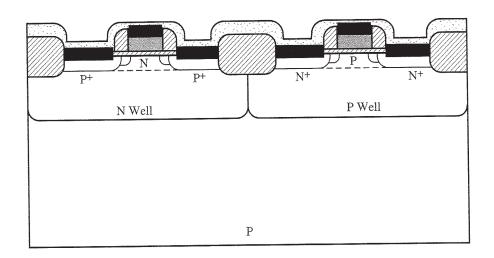

The photoresists themselves are complex hydrocarbon mixtures. The actual ultra violet (UV) light-sensitive part of the resist is only a portion of the total mixture. In the case of a positive resist, which is the most common type today, the molecule in the resist which is sensitive to light, absorbs UV photons and changes its chemical structure in response to the light. The result is that the molecule and the resist itself then dissolve in the developing solution. Negative resists also respond to UV light but become insoluble in the regions in which they are exposed. Figure 2–4 shows our CMOS wafer after the resist has been exposed and developed.

An additional step is also illustrated in Figure 2–4. After the pattern is defined in the resist, the  $Si_3N_4$  is etched using dry etching, with the resist as a mask. This is usually accomplished in a fluorine plasma. We will discuss dry etching in Chapter 10, but a typical reaction might involve the generation of F atoms in a plasma, using a  $CF_4$  or  $NF_3$  gas source and a reaction of the following type:

**Figure 2–4** Mask 1 patterns the photoresist. The Si<sub>3</sub>N<sub>4</sub> layer is removed where it is not protected by the photoresist by dry etching.

$$\mathrm{Si}_{3}\mathrm{N}_{4} + 12\mathrm{F} \to 3\mathrm{Si}\mathrm{F}_{4} + 2\mathrm{N}_{2} \tag{2.2}$$

The most common type of etching system uses two parallel plates to confine the gas reactants. An RF voltage (usually 13.56 MHz) is applied across the electrodes to create a plasma and with it many neutral and charged molecules and atoms. It is important that the byproducts of the etching reaction be volatile at the etching temperature (usually room temperature), so that they can easily be pumped out of the reaction chamber.

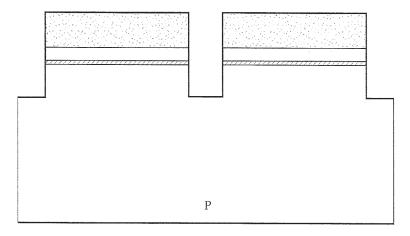

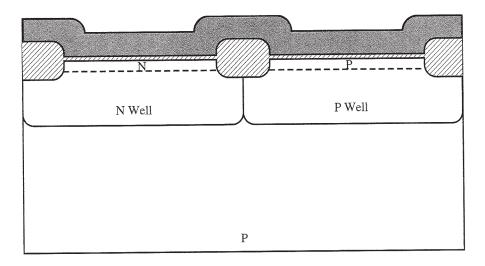

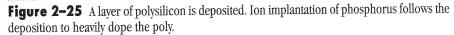

Once the Si<sub>3</sub>N<sub>4</sub> etching is completed, we are through with the resist and it can be chemically removed in sulfuric acid, or stripped in an O<sub>2</sub> plasma, neither of which significantly attacks the underlying Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> layers. Following cleaning, the wafers are then placed into a furnace in an oxidizing ambient. This grows a thick SiO<sub>2</sub> layer locally on the wafer surface. The Si<sub>3</sub>N<sub>4</sub> layer on the surface prevents oxidation where it is present because Si<sub>3</sub>N<sub>4</sub> is a very dense material and prevents the H<sub>2</sub>O or O<sub>2</sub> from diffusing to the Si surface where oxidation takes place. This local oxidation or LOCOS process might be done at 1000°C for 90 min in H<sub>2</sub>O to locally grow about 500 nm (0.5 µm) of SiO<sub>2</sub>. The structure at this point is illustrated in Figure 2–5.

After the furnace operation, the  $Si_3N_4$  layer can then be stripped. This is conveniently done in hot phosphoric acid, which is highly selective between  $Si_3N_4$  and  $SiO_2$ . The  $Si_3N_4$ could also be removed using dry (plasma) etching using a reaction like Eq. (2.2). However a process that gives good selectivity to  $SiO_2$  would be required so that not very much of the LOCOS oxide is etched away during the stripping of the  $Si_3N_4$ . Selectivity is often a very important issue in etch steps throughout the wafer fabrication process. We will discuss this issue more carefully in Chapter 10.

An alternative to the  $SiO_2/Si_3N_4$  stack used in Figure 2–3 is to use a three-layer stack of  $SiO_2$ , polysilicon, and  $Si_3N_4$  to mask the oxidation process. This process is called the poly-buffered LOCOS process because of the incorporation of the polysilicon layer.

Figure 2–5 After photoresist stripping, the field oxide is grown in an oxidizing ambient.

As was the case in the LOCOS process, the function of the nitride layer is to block the oxidation from occurring wherever the  $Si_3N_4$  is present. The underlying oxide and poly layers are both designed to help with the stress relief problem. Poly-buffered LOCOS uses a thicker  $Si_3N_4$  layer than was the case in the LOCOS process (about 200 nm versus about 80 nm) and a thinner oxide layer (about 20 nm versus about 40 nm). The polysilicon layer permits these changes because it helps to relieve the large stresses, which would otherwise cause defects to form in the silicon substrate during the LOCOS oxidation. The polysilicon is deposited in an LPCVD machine similar to the one described for  $Si_3N_4$  in connection with Eq. (2.1), except that only one reactant gas containing silicon is used (SiH<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, for example). A poly thickness of about 100 nm (0.1 µm) would be typical.

Why would we want to use a thicker nitride layer and a thinner pad oxide in the LO-COS process? The answer lies in a subtlety of LOCOS that we have not discussed to this point. Consider Figure 2–5 for example. The oxidation which takes place during LOCOS extends for some distance under the  $Si_3N_4$  edge. The characteristic shape that this twodimensional (2D) oxidation process produces is often called a bird's head or a bird's beak. This shape is only shown qualitatively in Figure 2–5; we will study this process in more detail in Chapter 6 and use numerical simulation tools to study the exact shape more carefully. The oxidation extends under the nitride edge because the oxidant (H<sub>2</sub>O) can diffuse sideways as well as vertically through the pad oxide layer, to reach the silicon surface where it reacts to grow  $SiO_2$ . In fact, the nitride layer will bend up as oxide grows underneath it as Figure 2–5 qualitatively illustrates. This means that the oxide actually grows over a larger surface region than the mask pattern used to define the  $Si_3N_4$ . This is a major concern when we are defining very small active devices, because surface area that is lost to this encroachment of the oxide significantly decreases device density.

The answer to the question we posed then is that the combination of a thicker nitride, a thinner pad oxide which provides less of a pathway for lateral oxidant diffusion, and a polysilicon layer which itself can oxidize along its edges during LOCOS produces a much sharper transition between the oxidized and unoxidized regions. This allows for tighter design rules and higher device density.

#### 2.2.3 Process Option for Device Isolation—Shallow Trench Isolation

We digress in our process flow description at this point to consider an alternative method for forming isolation regions between active devices. This alternative—Shallow Trench Isolation or STI—is beginning to be used in manufacturing today and will likely be the method of choice in the future. As we will see, STI actually etches trenches in the silicon substrate between active devices and then refills them with SiO<sub>2</sub>. Such a process completely eliminates the bird's beak shape characteristic of LOCOS isolation and thus allows physically smaller isolation regions to be formed.

The process begins the same way as the LOCOS process.  $SiO_2$  and  $Si_3N_4$  layers are thermally grown and deposited respectively, as shown in Figure 2–3. The thicknesses of these layers are approximately the same as in the LOCOS process. However the stressrelated issues, which tightly constrained these thicknesses in the LOCOS case, are relaxed somewhat in the STI process because there is no long high-temperature oxidation in STI, during which stresses can generate defects in the silicon substrate. Nevertheless, an SiO<sub>2</sub> thickness of about 10 – 20 nm and an Si<sub>3</sub>N<sub>4</sub> thickness of about 50 – 100 nm would be typical. Photoresist is then applied, exposed, and developed as in Figure 2–4.

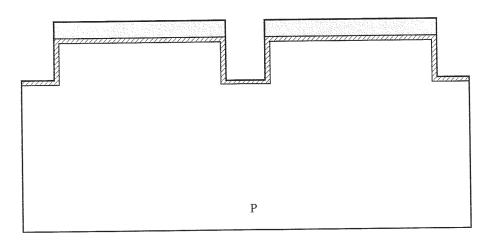

Figure 2–6 illustrates the next steps. The nitride and oxide layers are etched using the photoresist as a mask. This would typically be done as described above in Eq. (2.2), using a fluorine-based plasma chemistry for both materials. The next step is to etch the trenches in the silicon which are typically on the order of 0.5  $\mu$ m deep. This can be done again using the photoresist as a mask, or the photoresists can be stripped and the nitride layer can then serve as the mask. The trench etching is a relatively critical step. It is important that the trench walls be relatively vertical so that there is little undercutting into the adjacent active device regions. However, the trench will later be filled with a deposited oxide and this filling process needs to completely fill the trenches without leaving voids. This often means that the trench walls should not be perfectly vertical but rather have a small slope. In addition, the top and bottom corners of the trenches ideally need to be slightly rounded in order to avoid problems later in oxidizing very sharp corners and to avoid electrical effects associated with very sharp corners. Thus the etch

**Figure 2–6** After mask 1 defines the photoresist, the Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub>, and Si trenches are successively plasma etched to create the shallow trenches for isolation.

67)

**Figure 2–7** A thin "liner" oxide is thermally grown in the trenches. The nitride prevents any additional oxidation on the top surface of the wafer.

chemistry for this silicon etch must be very carefully chosen. Often a bromine-based plasma chemistry is used in this application, as discussed in more detail in Chapter 10.

The next step in the process is to thermally grow a thin (10 - 20 -nm) "liner" oxide on the trench sidewalls and bottoms as shown in Figure 2–7. While most of the trench will be filled with a deposited oxide, thermally growing the first part produces a better Si/SiO<sub>2</sub> interface and if the oxidation is done at relatively high temperature ( $\approx 1100^{\circ}\text{C}$ ), the process will also help to round the corners of the trenches as well. The better Si/SiO<sub>2</sub> interface results from the lower electrical charge densities that thermal oxidations can produce. The corner rounding results from the viscoelastic flow properties of SiO<sub>2</sub> at high temperatures. We will discuss these issues in Chapter 6.

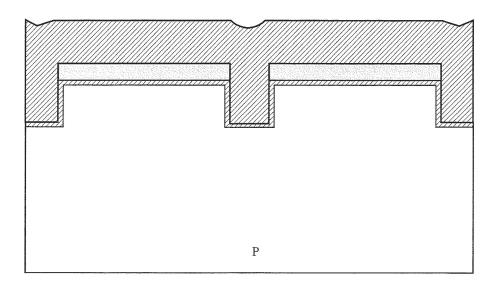

The next step, illustrated in Figure 2–8, is the deposition of a thick  $SiO_2$  layer by chemical vapor deposition. It is important here that the filling process not leave gaps or voids in the trenches, which could happen if the deposition closed the top part of the trench before the bottom parts were completely filled. A number of deposition systems exist which do a good job of filling structures like this. One example is a High-Density Plasma or HDP system, which could be used in this application. We will discuss these systems in Chapter 10.

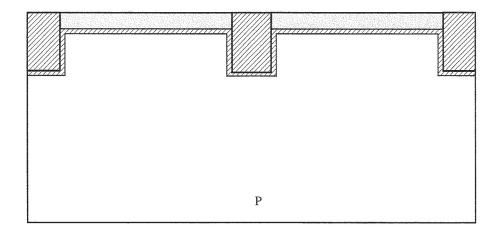

The final step in the STI process is illustrated in Figure 2–9. This involves literally polishing the excess  $SiO_2$  off the top surface of the wafer, leaving a planar substrate with  $SiO_2$  filled trenches. This polishing process uses a technique known as Chemical-Mechanical Polishing or CMP, which we will discuss in Chapter 11 since the most common use of CMP today is in back-end processing. In this process, the wafer is placed face down in a polishing machine and the upper surface is literally polished flat using a high-pH silica slurry. While this process sounds crude compared to the sophisticated processing techniques generally used to fabricate chips, CMP has been found to work extremely well and it has found widespread application. The nitride layer serves as a polishing stop and once the CMP operation is complete, the  $Si_3N_4$  can be chemically removed as in the LOCOS process described earlier.

At this stage, the wafers are ready for device fabrication in the active regions. A comparison of Figures 2–5 and 2–9 illustrates both the similarities and the differences

**Figure 2–8** SiO<sub>2</sub> is deposited to completely fill the trenches. This would typically require 0.5  $-1 \mu m$  of SiO<sub>2</sub> to be deposited, depending on the trench depth and geometry.

in LOCOS and STI. Both processes produce thick  $SiO_2$  regions laterally isolating adjacent device structures. However the STI process produces more compact structures because there is very little lateral encroachment of the isolation structure into adjacent active regions.

One might ask why the STI process has not been used in manufacturing until quite recently since it seems like a simple process and it produces more compact isolation regions compared to LOCOS. There are really two answers to this question. The first is that when device geometries were larger, the small area loss due to lateral encroachment in the LOCOS process was not a significant factor in overall chip density. The second reason is perhaps more important. While STI seems like a simple process, there are actually a number of subtle issues associated with this technology which have proven difficult to solve in a manufacturing environment. These issues include filling the trenches with no gaps, using CMP to planarize the wafer, and avoiding subtle electrical effects associated with the corners of the trenches which can affect device isolation. These issues have now been largely solved with new processes and new manufacturing equipment, with the result that STI is now beginning to be used in manufacturing. Its inherent density advantage over LOCOS suggests that STI will dominate in the future.

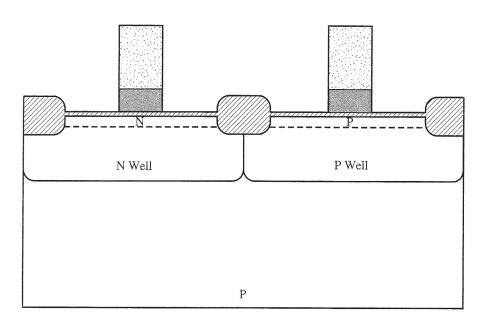

#### 2.2.4 N and P Well Formation

We now return to our CMOS process flow and we will pick up the LOCOS isolation technology where we left it in Figure 2–5. If STI were used as the isolation process, the steps below would be largely unchanged. We would simply use the cross section in Figure 2–9 rather than Figure 2–5 as our starting point to continue the process flow.

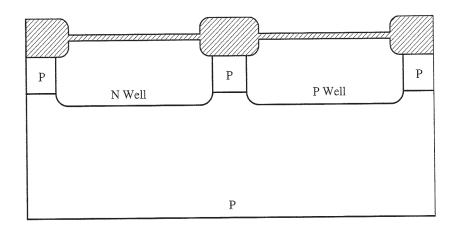

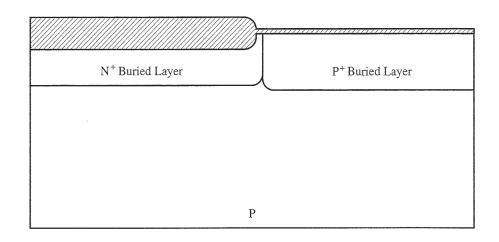

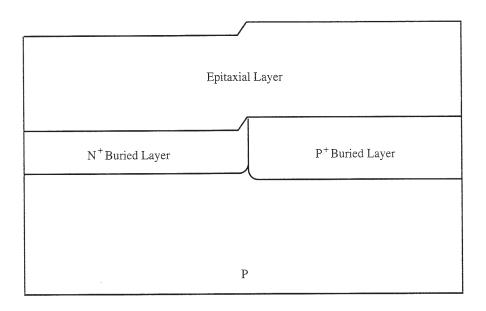

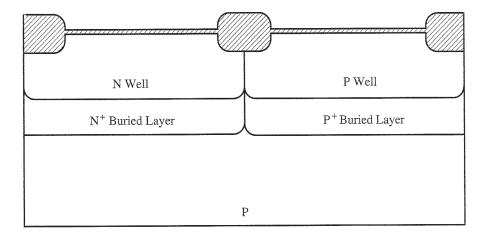

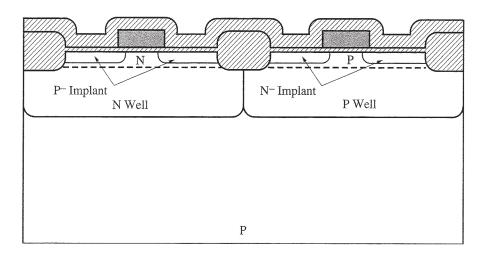

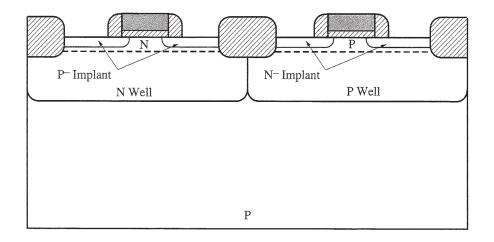

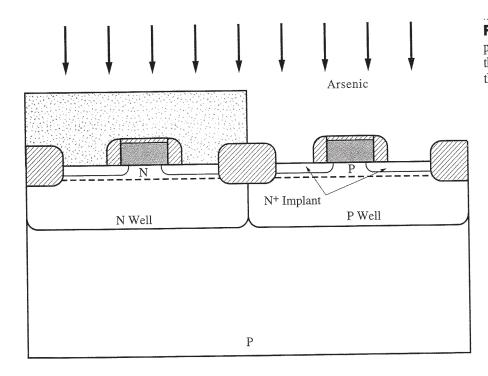

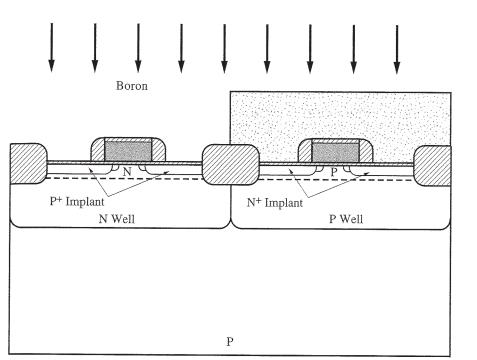

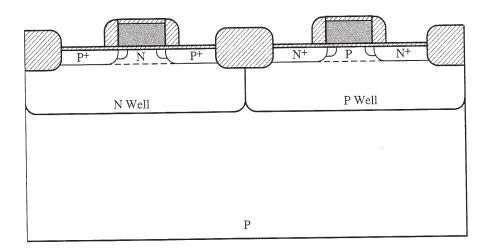

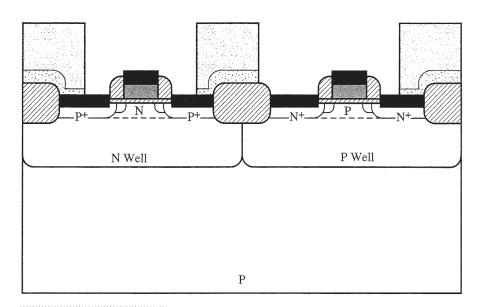

In the final device cross section in Figure 2–2, the active devices are shown in P- and N-type wells. These wells tailor the substrate doping locally to provide optimum device characteristics. The well doping affects device characteristics such as the MOS transistor threshold voltage and I-V characteristics and PN junction capacitances. For example, recall in Chapter 1, Eqs. (1.23) – (1.25) which describe the electrical properties of PN diodes and notice the presence of the doping levels  $N_D$  and  $N_A$  in these expressions. The steps required to form the P and N wells are illustrated in Figures 2–10 to 2–12.

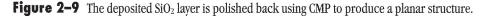

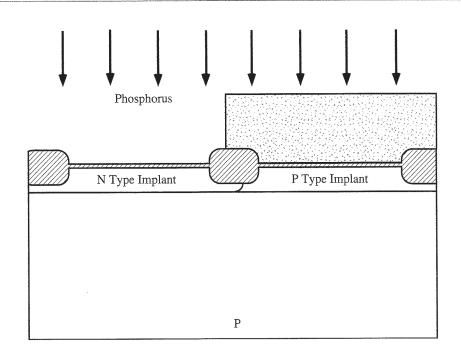

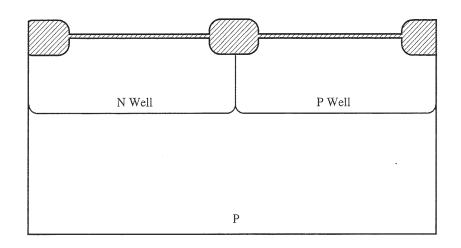

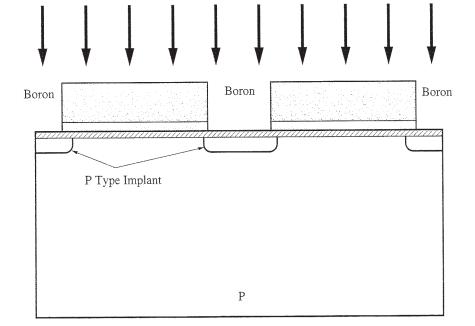

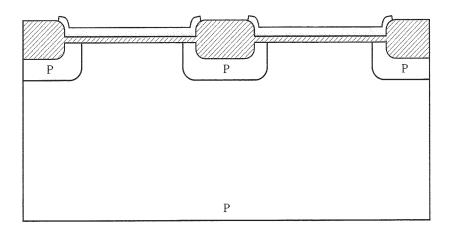

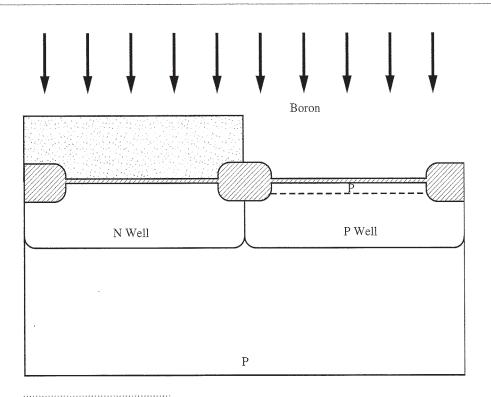

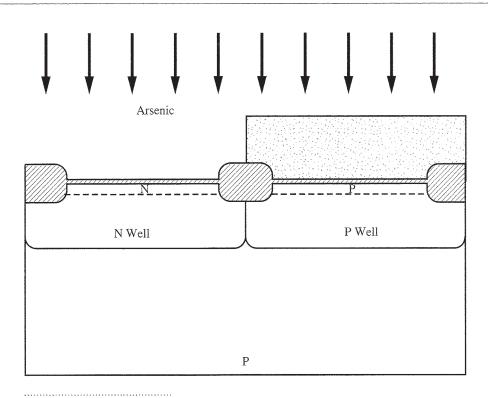

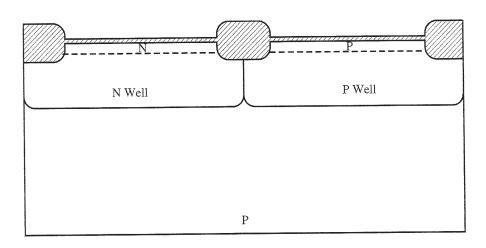

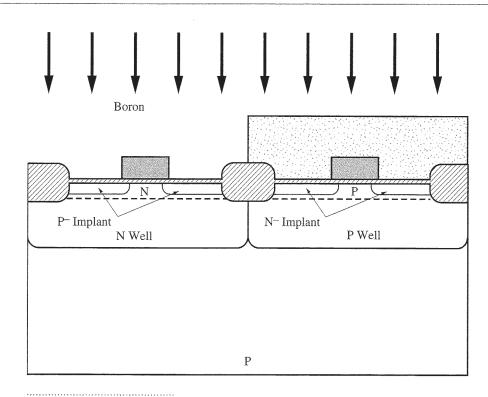

In Figure 2–10, photoresist is spun onto the wafer and mask 2 is used to expose the resist and to define the regions where P wells are to be formed. The P regions are created by a process known as ion implantation, which we will discuss in Chapter 8. The machines which perform this step are really small linear accelerators. A source of the ion to be implanted (boron in this case) is provided, usually from a gas. Positively charged ions ( $B^+$ ) are formed by exposing the source gas to an arc discharge. The ions

**Figure 2–10** Photoresist is used to mask the regions where PMOS devices will be built using mask 2. A boron implant provides the doping for the P wells for the NMOS devices.

are then accelerated in an electric field to some final energy, usually expressed in keV. Since many types of ions may be formed in the source region, all ion implanters select the particular ion to be implanted by bending the ion beam through a magnetic field. Ions of different masses will bend at different rates in the magnetic field, allowing one type of ion to be selected at the output by adjustment of the field strength. Once the selection process is complete, final acceleration of the B<sup>+</sup> takes place along with either electrostatic scanning of the beam or mechanical scanning of the wafer to provide a uniform implant dose across the wafer.

In our case, we would need to pick an implant energy sufficiently large that the B<sup>+</sup> ions penetrated the thin and thick SiO<sub>2</sub> layers on the wafer surface, but not so large that the beam penetrated through the photoresist which must mask against the implant. This is possible in this case because the field oxide is on the order of 0.5  $\mu$ m and the photoresist is at least twice this thick. The B<sup>+</sup> implant needs to penetrate through the thin SiO<sub>2</sub> layer in order to form the P well. It also needs to penetrate through the field oxide although the reason is not so obvious in this case. As was pointed out earlier, the purpose of the field oxide is to provide lateral isolation between adjacent MOS transistors. If the doping is too light under the field oxide, it is possible that surface inversion can occur in these regions, providing electrical connections between adjacent devices through parasitic MOS devices (field oxide transistors). By ensuring that the well implants penetrate through the field oxide, the doping is increased under the field oxide, preventing this parasitic inversion problem. We will study ion implantation in detail in Chapter 8 and see how to choose the accelerating energy for the B<sup>+</sup> ions, but for the situation described here, an energy of 150 – 200 keV would be typical.

The amount of B<sup>+</sup> we implant (or the dose), is determined by the device requirements. Here we are forming a P well whose concentration is required to be on the order of  $5 \times 10^{16}$  to  $10^{17}$  cm<sup>-3</sup> in order to provide correct device electrical characteristics. In Chapter 8 we will see how to calculate this dose, but a dose on the order of  $10^{13}$  cm<sup>-2</sup> would be typical. (Note that implant doses are expressed as an areal dose per cm<sup>2</sup>, while doping concentrations are volume concentrations per cm<sup>3</sup>.)

An important point about ion implantation has not been made to this point. Implantation of ions into a crystalline substrate causes damage. This is easy to visualize since an incoming ion with an energy of perhaps 100 keV can clearly collide with and dislodge silicon atoms in the substrate which have a binding energy of only 4 Si-Si bonds (about 12 eV). Visualize a billiard-ball-like collision between the incoming 100 keV B<sup>+</sup> ion and a stationary Si atom and you can easily imagine that the silicon atom will likely be recoiled a significant distance from its original lattice site. In fact many such recoils are produced as the B<sup>+</sup> ion gradually comes to rest. This damage must be somehow repaired since the devices we want to end up with require virtually perfect crystalline substrates. Fortunately, the repair process is not as difficult as it might initially seem. A simple furnace step usually suffices. Heating the wafers allows the dislodged silicon atoms to diffuse and find a vacant lattice site, thus repairing the damage. Such a high temperature step will soon occur in our process description and will accomplish this crystal repair function. This can be done in short times at high temperatures (e.g., 10 sec at 1000°C) or in longer times at lower temperatures (e.g., 30 min at 800°C). We will study implantation and damage annealing in greater detail in Chapter 8.

Chapter 2 Modern CMOS Technology

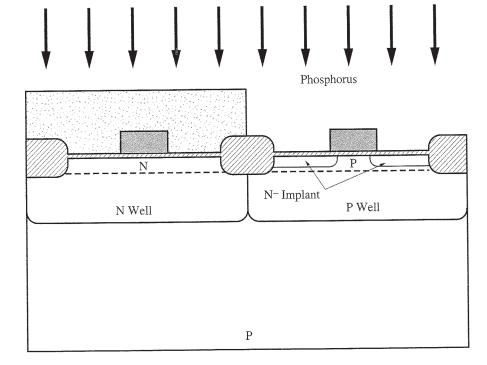

**Figure 2–11** Photoresist is used to mask the regions where NMOS devices will be built using mask 3. A phosphorus implant provides the doping for the N wells for the PMOS devices.

Once the boron implant is complete, we are finished with the photoresist and it is then stripped either chemically or in an  $O_2$  plasma. Photoresist and mask 3 are now used as shown in Figure 2–11 to define the regions where N wells will be placed in the silicon. The process is identical to that just described for the P wells except that in this case an N-type dopant, phosphorus, is implanted. The energy of the phosphorus implant is again chosen to penetrate the oxide layers but not the photoresist. Phosphorus is a heavier atom than boron (atomic mass = 31 versus 11), so a higher energy is required to obtain an implant to the same depth into the silicon. In this situation an energy of 300–400 keV would be chosen. The dose of the phosphorus implant would typically be on the same order as the boron P well implant since the purpose is similar in both cases.

There are several common N-type dopants available for use in silicon (phosphorus, arsenic, and antimony) and yet we specifically chose phosphorus in this case. The next step in the process is to diffuse the P and N wells to a junction depth of typically several microns, as illustrated in Figure 2–12. Boron and phosphorus have essentially matched diffusion coefficients and so they will produce wells with about the same junction depth when they are simultaneously diffused. The other N-type dopants, arsenic and antimony, both have much smaller diffusion coefficients and so for the process described here, the N well would be much shallower than the P well, which is not desired if we want matched NMOS and PMOS characteristics. Another issue with arsenic and antimony in this particular step in the process is that they are much heavier atoms than phosphorus and hence would require much higher implant energies.