# A New LDD Structure: Total Overlap with Polysilicon Spacer (TOPS)

J. E. MOON, T. GARFINKEL, J. CHUNG, M. WONG, P. K. KO, AND CHENMING HU, FELLOW, IEEE

Abstract—This letter presents a new fully overlapped lightly doped drain structure—the total overlap with polysilicon spacer (TOPS) structure. The TOPS structure achieves full gate overlap of the lightly doped region with simple processing. TOPS devices have demonstrated superior performance and reliability compared to oxide-spacer lightly doped drain (LDD) devices, with an order of magnitude advantage in current degradation under stress for the same initial current drive or 30% more drive for the same amount of degradation. TOPS devices also show a much smaller sensitivity to n<sup>-</sup> dose variation than LDD devices. Gate-induced drain leakage (GIDL) is reported for the first time in fully overlapped LDD devices.

#### I. Introduction

THE long-term reliability of n-channel MOSFET's has been a major concern as device channel lengths have been reduced to submicrometer and deep-submicrometer dimensions [1], [2]. The lightly doped drain (LDD) structure [3] has been widely investigated as a means of reducing the lateral electric field and the associated hot-carrier effects on reliability. Theoretical and experimental investigations [4]–[6] have demonstrated that gate control over the n<sup>-</sup> region is a crucial element in both the performance and reliability of LDD devices. This letter presents a new fully overlapped lightly doped drain structure—the total overlap with polysilicon spacer (TOPS) structure. Unlike other proposed fully overlapped structures which require complicated fabrication sequences or unusual fabrication techniques [5]–[7], the TOPS structure achieves full overlap with simple and proven processing techniques.

## II. DEVICE PROCESSING

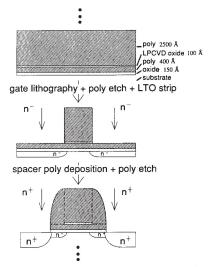

Fig. 1 shows the critical steps in the fabrication sequence. Gate oxide is grown after LOCOS isolation, and then layers of thin polysilicon, very thin LPCVD oxide, and thick doped polysilicon are deposited. Wafers were cleaned in piranha  $(H_2SO_4/H_2O_2)$  after thin polysilicon deposition, followed by removal of chemical oxide in dilute HF; the thin oxide deposition was followed directly by thick polysilicon deposition. Gate definition (using the thin LPCVD oxide as an etch stop) is followed by  $n^-$  implantation through the thin oxide and thin polysilicon layers, and removal of the thin oxide in

Manuscript received November 14, 1989; revised January 25, 1990. This work was supported in part by JSEP under Contract F49620-87-C-0041 and by ISTO/SDIO through ONR under Contract N00014-85-K-0603. J. E. Moon was supported by a Doctoral Award from Eastman Kodak Company.

The authors are with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720. IEEE Log Number 9035748.

Fig. 1. TOPS structure layered gate and polysilicon spacer formation. Gate and spacer definitions are accomplished by plasma etching with oxide endpoint detection. Typical CVD film thicknesses are shown.

dilute buffered HF. Doped polysilicon is then deposited and etched to form the polysilicon spacer. The last etch proceeds until a well-defined endpoint corresponding to gate oxide and field oxide is detected. Both polysilicon etches are very easily controlled and do not require the extremely high selectivity or timed etching of previously reported structures [5], [6]. The oxide-spacer LDD devices were prepared by n- implantation after gate definition, followed by LPCVD oxide deposition, densification, and etch-back to form the oxide spacer [8]. Control over formation of the TOPS polysilicon spacer is much easier than that of the LDD oxide spacer because of the easily detected endpoint; the oxide spacer etch must be timed. Source/drain n<sup>+</sup> implantation, contact formation, and metallization follow a standard process sequence. Although it was not done in this initial study, silicidization of gate, source, and drain could be done by additional process steps after the polysilicon spacer formation.

All devices had a gate oxide of 15 nm and were fabricated using the deep-submicrometer optical lithographic technique reported earlier [9]. All spacer lengths were designed to be 0.2  $\mu$ m. TOPS devices received n<sup>-</sup> doses of 0.5, 1.0, and 3.0  $\times$  10<sup>13</sup> cm<sup>-2</sup>, and the oxide-spacer LDD devices received doses of 0.5 and 1.5  $\times$  10<sup>13</sup> cm<sup>-2</sup>. Two types of TOPS devices, having either *in-situ* doped or undoped thin polysilicon, were

0741-3106/90/0500-0221\$01.00 © 1990 IEEE

TABLE I

EFFECT OF n Dose Variation on Performance of TOPS and LDD

Devices

$I_{d \text{ sat}}$  values measured at  $V_g = 5 \text{ V}$ ;  $g_{m \text{sat}}$  values measured at  $V_d = 3 \text{ V}$ .

| Structure | Dose (cm <sup>-2</sup> ) | Performance               |                           |

|-----------|--------------------------|---------------------------|---------------------------|

|           |                          | I <sub>dsat</sub> (mA/μm) | g <sub>msat</sub> (mS/mm) |

| TOPS      | 0.5 x 10 <sup>13</sup>   | 0.45/0.36                 | 118/103                   |

|           | 1.0 x 10 <sup>13</sup>   | 0.46/0.36                 | 120/104                   |

|           | 3.0 x 10 <sup>13</sup>   | 0.48/0.38                 | 122/104                   |

| LDD       | 0.5 x 10 <sup>13</sup>   | 0.36/0.32                 | 90/84                     |

|           | 1.5 x 10 <sup>13</sup>   | 0.43/0.36                 | 110/98                    |

<sup>\*</sup> Dual entries are for  $L_{eff}$ =0.5  $\mu m$  and  $L_{eff}$ =0.8  $\mu m$ .

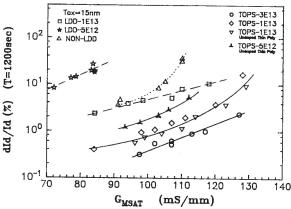

Fig. 2. Overall performance comparison of TOPS, LDD, and non-LDD technologies. Degradation values are for forward linear operation and  $g_{msat}$  values are measured at  $V_d=3~\rm V$ .

made in order to investigate the possibility of modifying the gate work function through the doping of the bottom layer of the gate [10]. *In-situ* doped polysilicon was used in all TOPS devices for the thick top layer of the gate and for the polysilicon spacer.

## III. PERFORMANCE AND RELIABILITY

Performance and reliability characteristics of non-LDD, conventional oxide-spacer LDD, and TOPS n-MOSFET devices have been evaluated. Table I contains a comparison of TOPS and LDD device performance for  $L_{\rm eff}$  of 0.5 and 0.8  $\mu m$ . The TOPS structure, due to the fully overlapped gate, shows better current drive and larger transconductance than an LDD structure of comparable channel length. The  $g_m$  characteristics of the TOPS devices approach those of non-LDD's in magnitude. At  $V_d = 3$  V the peak  $g_m$  of non-LDD, TOPS, and oxide spacer LDD devices were 109, 104, and 98 mS/mm, respectively, for an  $L_{\rm eff}$  of 0.8  $\mu m$ . The drive advantage of TOPS devices over LDD devices was seen to increase with decreasing channel length, with as much as 20% more at  $L_{\text{eff}} = 0.3 \ \mu\text{m}$  (0.62 versus 0.52 mA/ $\mu$ m). Importantly, the TOPS devices show a much smaller sensitivity to n- dose variation than the LDD devices do over the range of doses evaluated, as shown in Table I. It should be noted that device and process characteristics have not necessarily been optimized with respect to  $n^-$  dose and spacer length in this initial feasibility study.

For a given  $L_{\rm eff}$  the TOPS device has significantly less substrate current than the non-LDD device. Peak  $I_{sub}$  (at  $V_d$ 5 V and  $V_g \sim 2$  V;  $W = 10 \mu \text{m}$ ,  $L_{\text{eff}} = 0.8 \mu \text{m}$ ) was 81, 16, and 8  $\mu A$  for non-LDD, TOPS, and LDD devices, respectively. Although TOPS devices have more  $I_{sub}$  than oxide spacer LDD devices, they exhibit significantly less hot-carrier degradation. After 20 min of stressing at peak  $I_{sub}$  and  $V_D = 6$ V, a TOPS device with  $L_{\rm eff} = 0.8 \, \mu \rm m$  shows a forward linear current degradation of 1.0% compared to 4.4 and 34% for the LDD and non-LDD devices, respectively. Creation of interface traps by hot carriers and subsequent electron trapping is offset in the TOPS device by the overlapped gate, whereas in the LDD device only fringing fields are available to exert control over the resistive n- region. A definitive comparison of performance and reliability among the three device structures is shown in Fig. 2. The superiority of the TOPS devices compared to the LDD and non-LDD devices in this study is clearly demonstrated, with roughly an order of magnitude advantage in degradation for the same drive or 30% more drive for the same amount of degradation. Fig. 2 also shows the effect of n dose variations for the levels studied. The TOPS structure again appears to be less sensitive to n- dose variability.

The doping of the thin polysilicon layer (as deposited) had no demonstrable effect on the current drive or reliability of the TOPS devices. One plausible explanation for the lack of a noticeable effect of thin polysilicon doping on both performance and reliability is that the undoped thin polysilicon may have been subsequently doped by diffusion from the top gate and spacer polysilicon. The thermal cycle after gate definition and source/drain implant was carefully controlled in order to limit junction drive-in (a total of 30 min at 925°C), but it is possible that dopant diffusion occurred rapidly along polysilicon grain boundaries.

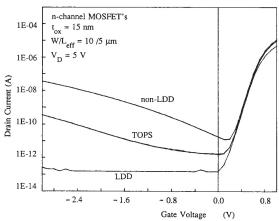

The gate-induced drain leakage (GIDL) [11] behavior of non-LDD, oxide-spacer LDD, and TOPS devices are compared in Fig. 3. Besides hot-carrier degradation, GIDL is considered to be another major factor in limiting the power-supply voltage for deep-submicrometer MOS technologies [2]. The non-LDD MOSFET has the largest GIDL, as expected [11]. Of the remaining two devices, the oxide-spacer LDD is GIDL-free while the TOPS device still shows significant

Fig. 3. GIDL behavior of TOPS, LDD, and non-LDD devices. Implanted  $n^-$  doses are 3 imes 10<sup>13</sup> and 1.5 imes 10<sup>13</sup> cm<sup>-2</sup> for the TOPS and LDD

GIDL. Because the gate would overlap the n<sup>+</sup> region in any fully overlapped LDD device such as TOPS, we expect GIDL to be an important design consideration for fully overlapped LDD structures.

### IV. Conclusions

A new fully overlapped LDD structure-TOPS-has been fabricated and characterized. TOPS devices produce more current drive and better transconductance than oxide-spacer LDD devices of equivalent size. A major advantage of TOPS over LDD is its improved reliability. Even though the TOPS devices had greater  $I_{sub}$  than LDD devices, current degradation under hot-electron stressing conditions is significantly less for the TOPS devices. The choice of n - dose is less critical for the TOPS structure than for the LDD structure in the results

reported here, implying less overall process sensitivity. GIDL was noted in the TOPS devices, the first such report of this behavior in fully overlapped LDD devices. This represents an important design constraint for submicrometer devices. The superior performance and reliability characteristics of the TOPS structure merit further investigation for deep-submicrometer applications.

#### REFERENCES

- [1] C. Hu et al., "Hot-electron induced MOSFET degradation-Model, monitor, and improvement," IEEE Trans. Electron Devices, vol. ED-32, no. 2, p. 375, 1985.

- M.-C. Jeng et al., "Design guidelines for deep-submicrometer MOSFET's," in *IEDM Tech. Dig.*, 1988, p. 386.

S. Ogura, P. J. Tsang, W. W. Walker, D. L. Critchlow, and J. F. Shepard, "Design and characteristics of the lightly doped drain-source (LDD) insulated gate field-effect transistor," IEEE Trans. Electron Devices, vol. ED-27, no. 8, p. 1359, 1980. K. Mayaram, J. C. Lee, and C. Hu, "A model for the electric field in

- lightly doped drain structures," IEEE Trans. Electron Devices, vol. ED-34, no. 7, p. 1509, 1987. T.-Y. Huang et al., "A new LDD transistor with inverse-T gate

- structure," IEEE Electron Device Lett., vol. EDL-8, no. 4, p. 151,

- R. Izawa, T. Kure, S. Iijima, and E. Takeda, "The impact of gatedrain overlapped LDD (GOLD) for deep submicron VLSI's," IEDM Tech. Dig., 1987, p. 38.

- T. Hori, K. Kurimoto, T. Yabu, and G. Fuse, "A new submicron MOSFET with LATID (large-tilt-angle implanted drain) structure," in Dig. Tech. Papers Symp. VLSI Technol., 1988, p. 15.

- S. Ogura, P. J. Tsang, W. W. Walker, D. L. Critchlow, and J. F. Shepard, "Elimination of hot electron gate current by the lightly doped drain-source structure," in IEDM Tech. Dig., 1981, p. 651

- J. Chung et al., "Deep-submicrometer MOS device fabrication using a photoresist-ashing technique," IEEE Electron Device Lett., vol. 9, no. 4, p. 186, 1988.

- J. R. Pfiester and L. C. Parrillo, "A novel p-1/p+ poly gate CMOS VLSI Technology," IEEE Trans. Electron Devices, vol. 35, no. 8, p. 1305, 1988.

- T. Y. Chan, J. Chen, P. K. Ko, and C. Hu, "The impact of gateinduced drain leakage current on MOSFET scaling," in IEDM Tech. Dig., 1987, p. 718.