# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD

TAIWAN SEMICONDUCTOR MANUFACTURING CO., LTD, Petitioner,

V.

GODO KAISHA IP BRIDGE 1, Patent Owner.

Case IPR2017-01841 Patent 7,893,501

IP Bridge Exhibit 2027 TSMC v. Godo Kaisha IP Bridge 1 IPR2017-01841

### PATENT OWNER'S DEMONSTRATIVE EXHIBITS

### I. INTRODUCTION

Patent Owner's Response ("Response") confirms that the challenged claims are unpatentable. There is no dispute that Igarashi discloses the allegedly novel "protruding gate" that provided the basis for allowance.<sup>2</sup> Moreover, Patent Owner ("PO") does not dispute that the instituted grounds expressly disclose every limitation of the challenged claims, except the "active region." Nor does PO dispute that the references would have been obvious to combine. Instead, PO merely repeats the same arguments that it already raised in its Patent Owner's Preliminary Response ("POPR"<sup>3</sup>) that Igarashi's disclosure somehow lacks an "active region," one of the most basic aspects of a semiconductor device. These

Reply, Paper No. 22, at 1

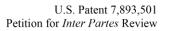

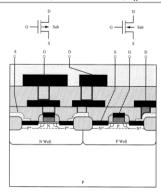

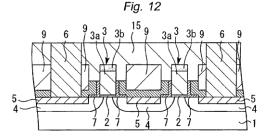

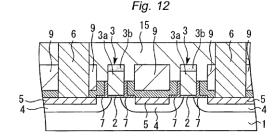

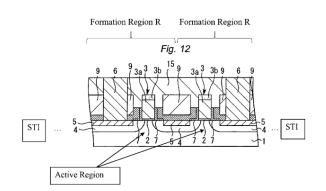

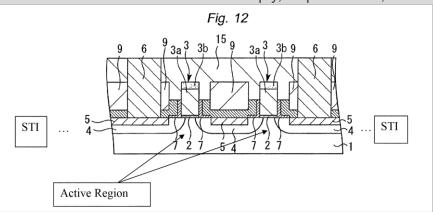

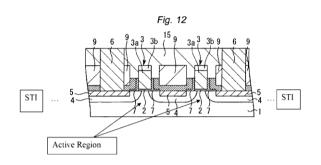

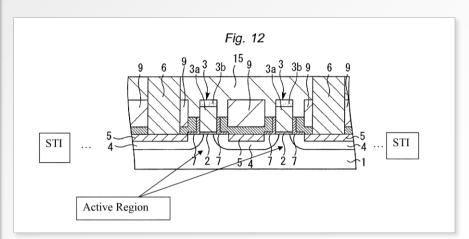

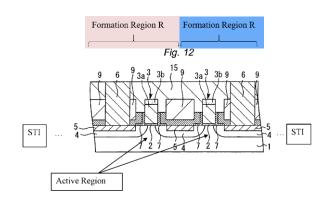

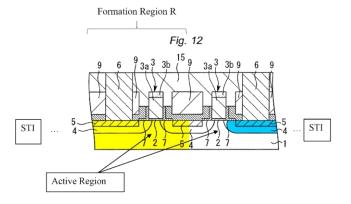

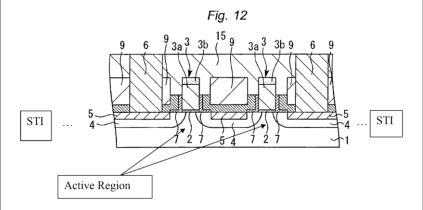

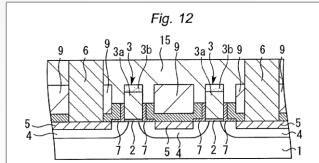

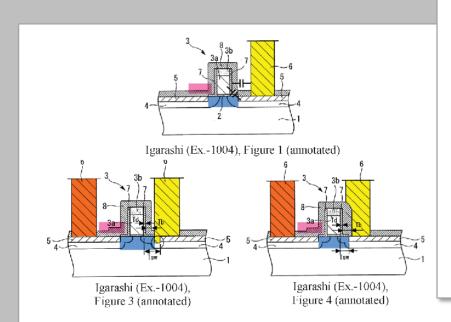

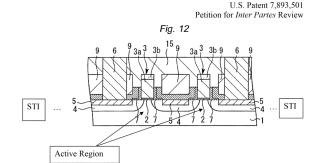

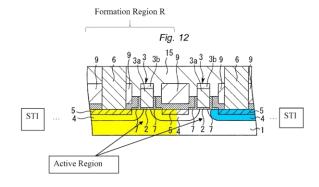

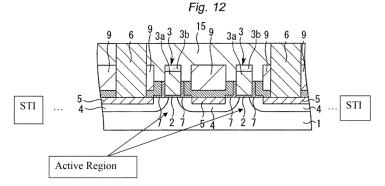

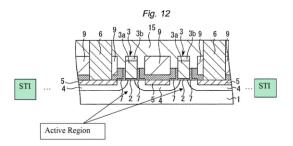

(Igarashi at Fig. 12 (Ex-1004) (annotated).) (Shanfield Decl. ¶66 (Ex-1002).)

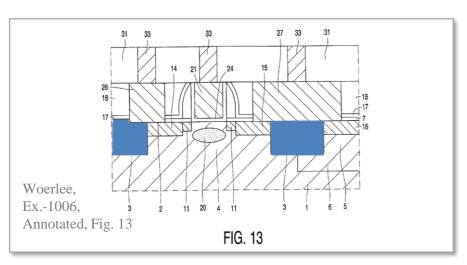

To the extent that Igarashi does not explicitly disclose the location of the "active element region" and therefore that the active region is "made of" the semiconductor substrate, Woerlee discloses this limitation. (Shanfield Decl. ¶67 (Ex-1002).) For example, Woerlee discloses an active region 4 "made of" the semiconductor body 1 in Fig. 13:

# "Petitions Fail to Demonstrate that the Igarashi/Woerlee Device Comprises a MISFET that Includes an 'Active Region' as Required by All Challenged claims." (POR, 37)

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes:

an active region made of a semiconductor substrate;

- a gate insulating film formed on the active region;

- a gate electrode formed on the gate insulating film;

- source/drain regions formed in regions of the active region located on both sides of the gate electrode; and

- a silicon nitride film formed over from side surfaces of the gate electrode to upper surfaces of the source/drain regions, wherein:

- the silicon nitride film is not formed on an upper surface of the gate electrode, and

- the gate electrode protrudes upward from a surface level of parts of the silicon nitride film located at both side surfaces of the gate electrode.

Ex. 1001, '501 patent at Claim 1

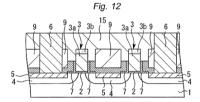

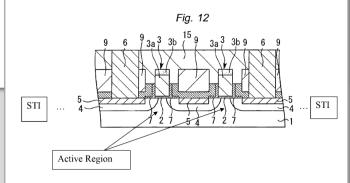

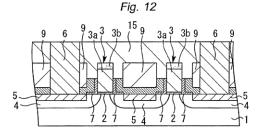

b) Claim 1 – Active Region (element [1a])

Claim 1 recites "an active region made of a semiconductor substrate." ('501 patent, claim 1 (Ex-1001).) Igarashi in view of Woerlee discloses this limitation. (Shanfield Decl. ¶64 (Ex-1002).)

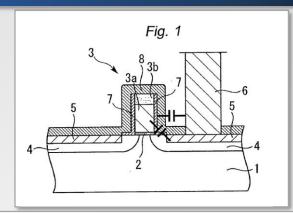

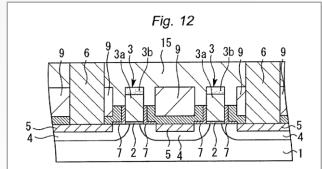

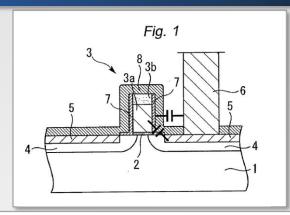

For example, Igarashi discloses a "semiconductor substrate 1," as illustrated in Fig. 12:

(Igarashi at Fig. 12 (Ex-1004); see also, e.g., id. at [0044]-[0045], [0112] (discussing the "semiconductor substrate 1").) (Shanfield Decl. ¶65 (Ex-1002).)

A POSITA would have understood that Igarashi discloses an active region made of the semiconductor substrate 1 because Igarashi discloses: "First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the active element region for forming the well and controlling the threshold value." (Igarashi at [0068] (Ex-1004).) That is, Igarashi discloses an "active region made

regions) in Woerlee are formed in regions of the active region 4 located on both sides of the gate electrode 21 (as recited in claim 1, element 1d below). The modified device would also have an active element region (active region) divided by the STI regions (isolation region) formed in the semiconductor substrate 1 (as recited in claim 10 below), just as the active region 4 is divided by an isolation region 3 formed in the semiconductor substrate 1 in Woerlee. (Shanfield Decl. ¶73 (Ex-1002).)

Therefore, Igarashi in view of Woerlee discloses "an active region made of a semiconductor substrate." (Shanfield Decl. ¶74 (Ex-1002).)

c) Claim 1 – Active Region (element [1a]) – Reasons to Modify

It would have been obvious to modify Igarashi in view of Woerlee's teachings of an active region "made of" a semiconductor substrate (recited in claim 1, element 1a) and an active region divided by an isolation region formed in the semiconductor substrate (recited in claim 10 below). In particular, it would have been obvious to apply Woerlee's teachings to Igarashi by forming Igarashi's active region in the substrate and defining it with STI regions that divide the active region. (Shanfield Decl. ¶75 (Ex-1002).)

First, a POSITA would have looked to the teachings of Woerlee because it is in the same field of endeavor as Igarashi. Igarashi discloses a MISFET device with a "silicon semiconductor substrate 1" where "[e]lement isolation is performed" to

32

Petition, Paper No. 2, at 24, 25

Petition, Paper No. 2, at 32

# "Petition's ... rationale ... supporting the assertion that Igarashi teaches ... Fig. 12 includes STI regions ... is non-existent." POR 38-39

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes:

an active region made of a semiconductor substrate;

- a gate insulating film formed on the active region;

- a gate electrode formed on the gate insulating film;

- source/drain regions formed in regions of the active region located on both sides of the gate electrode; and

- a silicon nitride film formed over from side surfaces of the gate electrode to upper surfaces of the source/drain regions, wherein:

- the silicon nitride film is not formed on an upper surface of the gate electrode, and

- the gate electrode protrudes upward from a surface level of parts of the silicon nitride film located at both side surfaces of the gate electrode.

Ex. 1001, '501 patent at Claim 1

b) Claim 1 – Active Region (element [1a])

Claim 1 recites "an active region made of a semiconductor substrate." ('501 patent, claim 1 (Ex-1001).) Igarashi in view of Woerlee discloses this limitation. (Shanfield Decl. ¶64 (Ex-1002).)

For example, Igarashi discloses a "semiconductor substrate 1," as illustrated in Fig. 12:

(Igarashi at Fig. 12 (Ex-1004); see also, e.g., id. at [0044]-[0045], [0112] (discussing the "semiconductor substrate 1").) (Shanfield Decl. ¶65 (Ex-1002).)

A POSITA would have understood that Igarashi discloses an active region made of the semiconductor substrate 1 because Igarashi discloses: "First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the active element region for forming the well and controlling the threshold value."

(Igarashi at [0068] (Ex-1004).) That is, Igarashi discloses an "active region made

Petition, Paper No. 2, at 24, 25

Based on the current record, however, we find it is clear from Igarashi that the disclosure of "active element region[s]" discussed in paragraph 68 with respect to the "First Embodiment" is equally applicable to the "Fifth Embodiment" upon which Petitioner primarily relies. For example, the description of the method for manufacturing the semiconductor device of the "Fifth Embodiment" refers back to earlier described embodiments of Igarashi, ultimately referencing the discussion of the method for manufacturing the semiconductor device of the "First Embodiment." Ex. 1004 ¶ 119 ("FIGS. 13A and 13[B] are schematic sectional views sequentially showing the method for manufacturing the semiconductor device shown in FIG. 12 [the Fifth Embodiment]. Here, FIG. 13A shows the same process as in FIG. 11B . . . . "), ¶¶ 112-13 ("FIGS. 11A to 11C are schematic sectional views showing the method for manufacturing the semiconductor device shown in FIG. 10 [the Fourth Embodiment]. . . . First, as FIG. 11A shows, gate electrodes 3 are formed, and silicon nitride films 7 and silicon nitride films S are formed so as to cover the gate electrodes 3 in the same process as in FIG. 5 . . . . "), ¶ 68 ("[T]he method for manufacturing the semiconductor device of First Embodiment will be described. In the following description of the manufacturing method, the major process for forming the silicon nitride film 7 will be described referring to FIGS. 5A to 5E, and other processes will be described without referring to drawings. First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the active element region for forming the well and controlling the threshold value.").

Institution Decision, Paper No. 10, at 19

### **Intrinsic Evidence – Active Region**

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes: an active region made of a semiconductor substrate;

'501 patent at Claim 1

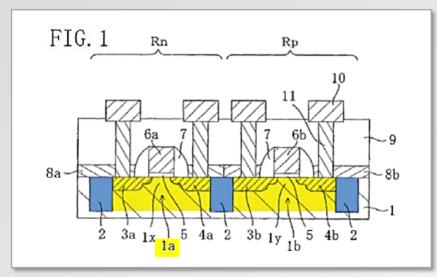

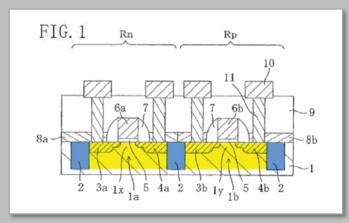

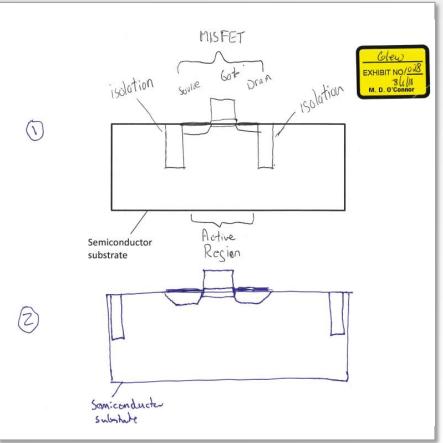

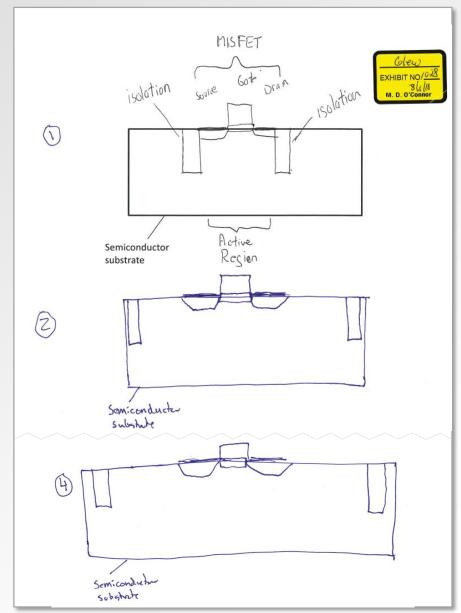

Glew Decl., Ex. 2007, ¶ 69, Annotated Fig.1 of '501 patent (cited POR at 9)

The semiconductor device includes an nMISFET formation region Rn which includes the active region 1a and in which an nMISFET is to be formed and a pMISFET formation region Rp which includes the active region 1b and in which a pMISFET is to be formed.

'501 patent, at 3:24-28 (cited POR at 8)

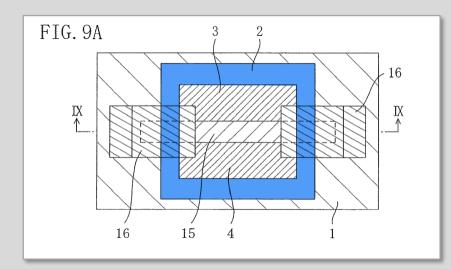

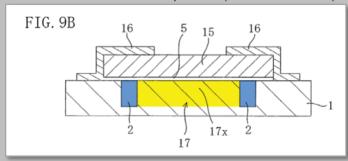

Glew Decl., Ex. 2007, ¶ 68, Annotated Fig.9A of '501 patent (cited POR at 8)

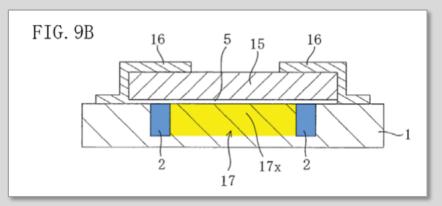

Glew Decl., Ex. 2007, ¶ 69, Annotated Fig.9B of '501 patent (cited POR at 8)

## Extrinsic Evidence – Active Region

Woerlee, Ex. 1006, Annotated Figure 13 (cited POR at 57)

As the Petitions acknowledge, Woerlee teaches isolation (STI) regions 3 that form an active region 4 for *each transistor*, so that each transistor has a dedicated active region and is electrically isolated by the isolation regions 3 from the other transistors formed in the substrate. Petition at 28 ("isolation regions 3 formed in the semiconductor substrate 1 define the active region 4 of the substrate body 1 where *the* [singular] transistor is formed."), 30 ("the active region 4 is the region 'in the semiconductor body' where 'a [singular] transistor ... is to be manufactured."); Ex.-2007, ¶128. The Petitions cite to Woerlee Fig. 13 and 4:66-

POR at 56

The MOS transistors that comprise an integrated circuit must be electrically isolated from each other during fabrication. Isolation is required to prevent unwanted conduction paths between the devices, to avoid creation of inversion layers outside the channel regions of transistors, and to reduce leakage currents. To achieve a sufficient level of electrical isolation between neighboring transistors on a chip surface, the devices are typically created in dedicated regions called active areas, where each active area is surrounded by a relatively thick oxide barrier called the field oxide.

One possible technique to create isolated active areas on silicon surface is first to grow a thick field oxide over the entire surface of the chip, and then to selectively etch the oxide in certain regions, to define the active areas. This fabrication technique, called etched field-oxide isolation, is already illustrated in Fig. 2.4(b) and Fig. 2.4(c). Here, the field oxide is selectively etched away to expose the silicon surface on which the MOS

Kang, Ex. 1011, at 28 (cited POR at 31)

## "All of the extrinsic evidence is consistent with [Patent Owner's proposed] BRI of 'active region'" (POR at 30)

from the specification into the claims). Contrary to Patent Owner's assertion, the evidence of record does not establish that "a transistor's 'active region' refers to a region that is dedicated to that transistor." Prelim. Resp. 3–4, 29–30. For example, Plummer<sup>10</sup> describes that "regions between these [isolation] layers, where transistors will be built, are called the 'active' regions of the substrate" (Ex. 1008, 53), and Rabaey<sup>11</sup> describes "active" regions" as "the regions where transistors will be constructed" (Ex. 1010, 42). Nothing about these descriptions connotes a requirement for a one-to-one correspondence of active regions-to-transistors, as Patent Owner contends.

Institution Decision, Paper No. 10, at 8-9

### **Extrinsic Evidence – Active Region**

#### DECLARATION OF ALEXANDER D. GLEW

each other"). "Device" and "transistor" are sometimes used interchangeably in these references, as a transistor (e.g., NMOS or PMOS) is a type of device. *E.g.*, Ex. 1008 (Plummer) at 51 ("A *PMOS transistor* is shown on the left, an *NMOS device* on the right."), 52 ("Modern CMOS chips integrate millions of active")

### Glew Decl., Ex. 2007, ¶ 84 (cited POR 31)

**Figure 2–2** Coss section of the final CMOS integrated circit. A PMOS transistor is shown on the left, an NMOS device on the right.

Plummer, Ex. 1008, at 51, Fig. 2-2 (cited Glew Decl., Ex. 2007, ¶¶ 83-84, cited POR 31)

ment complex logic or analog functions. In designing such circuits, it is usually assumed that the individual <u>devices</u> do not interact with each other except through their circuit interconnections. In other words, we need to make certain that the <u>individual devices</u> on the chip <u>are electrically isolated from each other</u>. This is accomplished most often by growing a fairly thick layer of  $SiO_2$  in between each of the active devices.  $SiO_2$  is essentially a perfect insulator and provides the needed isolation. This process of locally oxidizing the silicon substrate is known as the LOCOS process (LOCal Oxidation of Silicon). The regions between these thick  $SiO_2$  layers, where transistors will be built, are called the "active" regions of the substrate.

Ex. 1008 at 53 (cited Ex. 2007, ¶¶ 83-84, cited POR 31)

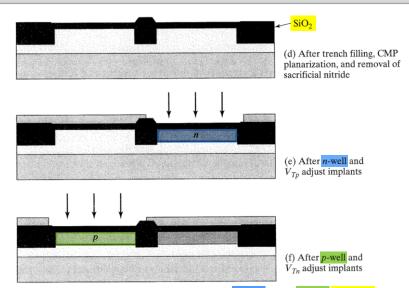

#### 2.2.4 Simplified CMOS Process Flow

The gross outline of a potential CMOS process flow is given in Figure 2-6. The process starts with the definition of the <u>active regions</u>—these are the regions where <u>transistors</u> will be constructed. All other areas of the die will be covered with a thick layer of silicon dioxide (SiO<sub>2</sub>)

A more detailed breakdown of the flow into individual process steps and their impact on the semiconductor material is shown graphically in Figure 2-7. While most of the operations

Rabaey, Ex. 1010 at 42-43 (cited Glew Decl., Ex. 2007, ¶¶ 84,152, cited POR 31,76)

**Figure 2-7** Process flow for the fabrication of an NMOS and a PMOS transistor in a dual-well CMOS process. Be aware that the drawings are stylized for understanding and that the aspects ratios are not proportioned to reality.

Rabaey, Ex. 1010 at 44 (cited Glew Decl., Ex. 2007, ¶¶ 84,152, cited POR 31, 76)

• Diffusion regions (n and p), which define the areas where transistors can be formed. These regions are often called the active areas. Diffusions of an inverse type are needed to implement contacts to the wells or to the substrate. These are called select regions.

Rabaey, Ex. 1010 at 48 (cited Glew Decl., Ex. 2007, ¶ 82, cited POR 31) 9

## The Claims Require That the MISFET Includes An Active Region

IPR2017-01841, IPR2017-01842 Patent 7,893,501 B2

'active region' refers to a region that is dedicated to that transistor." Prelim. Resp. 3–4, 29–30. For example, Plummer<sup>10</sup> describes that "regions between these [isolation] layers, where transistors will be built, are called the 'active' regions of the substrate" (Ex. 1008, 53), and Rabaey<sup>11</sup> describes "active regions" as "the regions where transistors will be constructed" (Ex. 1010, 42). Nothing about these descriptions connotes a requirement for a one-to-one correspondence of active regions-to-transistors, as Patent Owner contends.

Based on the record now before us, we are not persuaded that the claimed "active region" is limited to a region associated with a single transistor (i.e., "a region of a semiconductor substrate dedicated to the MISFET and defined by isolation regions that isolate the MISFET from other transistors formed in the substrate"), as Patent Owner contends. As discussed *infra*, Section II.E, Igarashi includes disclosure of "active element regions," which we find to be within the scope of the plain and ordinary meaning of "active region." Thus, we need not further construe "active region" for purposes of this Decision. The parties, however, may address further construction of the term during trial.

B. Principles of Law

A claim is unpatentable under 35 U.S.C. § 103(a) if the differences between the subject matter sought to be patented and the prior art are such

Institution Decision, Paper No. 10, at 9

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes: an active region made of a semiconductor substrate;

'501 patent, at Claim 1

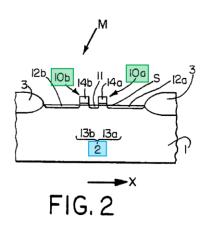

The semiconductor device of this example is a sense amplifier for a DRAM. As shown in FIG. 2, the sense amplifier includes a semiconductor layer 1 which may be a single-crystal semiconductor substrate, an active region 2 formed in an upper surface portion of the semiconductor layer 1, and isolation regions 3 for isolating the active region 2 from other active regions for other devices such as DRAM memory cells constituting a semiconductor memory device.

Agata, Ex 1025, 5:9-18 (cited Patent Owner's Sur-Reply, Paper No. 28, at 1)

<sup>&</sup>lt;sup>10</sup> JAMES D. PLUMMER ET AL., SILICON VLSI TECHNOLOGY: FUNDAMENTALS, PRACTICE AND MODELING (Charles Sonini ed., Prentice Hall, Inc., 2000) (Ex. 1008).

<sup>&</sup>lt;sup>11</sup> JAN M. RABAEY ET AL., DIGITAL INTEGRATED CIRCUITS: A DESIGN PERSPECTIVE (Charles G. Sonini ed., Pearson Educ., Inc., 2d ed. 2003) (Ex. 1010).

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes:

an active region made of a semiconductor substrate; a gate insulating film formed on the active region; a gate electrode formed on the gate insulating film; source/drain regions formed in regions of the active region located on both sides of the gate electrode; and

a silicon nitride film formed over from side surfaces of the gate electrode to upper surfaces of the source/drain regions, wherein:

the silicon nitride film is not formed on an upper surface of the gate electrode, and

the gate electrode protrudes upward from a surface level of parts of the silicon nitride film located at both side surfaces of the gate electrode.

'501 patent at Claim 1

| '501 Patent Claim 1              | Igarashi        | Woerlee |

|----------------------------------|-----------------|---------|

| [1p] 1. A semiconductor device,  | [0002], [0117], |         |

| comprising a MISFET, wherein the | Fig. 12         |         |

| MISFET includes:                 |                 |         |

Petition, Paper No. 2, at 23

U.S. Patent 7,893,501 Petition for *Inter Partes* Review

| '501 Patent Claim 1                           | Igarashi | Woerlee |

|-----------------------------------------------|----------|---------|

| nitride film located at both side surfaces of |          |         |

| the gate electrode.                           |          |         |

#### a) Claim 1 – Preamble (element [1p])

The preamble of claim 1 recites "[a] semiconductor device, comprising a

MISFET, wherein the MISFET includes." ('501 patent, claim 1 (Ex-1001).)

Igarashi discloses the preamble. (Shanfield Decl. ¶61 (Ex-1002).)

For example, Igarashi discloses: "The present invention relates to a semiconductor device, and a method for manufacturing the semiconductor device, specifically to the gate structure of an MOS transistor and the contact structure that contains gate wirings and LIC (local interconnect)." (Igarashi at [0002] (Ex-1004).) A metal—oxide—semiconductor (MOS) transistor is a type of MISFET where the insulator is an oxide. (*E.g.*, Shimizu at 59 ("A MISFET having a gate insulating film made of a silicon oxide film is usually called a MOSFET (Metal Oxide Semiconductor Field Effect Transistor).") (Ex-1009).) Thus, by disclosing a MOS transistor, Igarashi discloses a MISFET. (Shanfield Decl. ¶62 (Ex-1002).)

Therefore, Igarashi discloses the preamble. (Shanfield Decl. ¶63 (Ex-1002).)

b) Claim 1 – Active Region (element [1a])

24

Petition, Paper No. 2, at 24

<sup>&</sup>lt;sup>4</sup> All highlighting (bold and italicized) is added unless otherwise noted.

## The Petition Fails To Identify a 'MISFET Includes: An Active Region' As Claimed

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes: an active region made of a semiconductor substrate;

#### '501 Patent Claim 1

[1p] 1. A semiconductor device, comprising a MISFET, wherein the MISFET includes:

[1a] an active region made of a semiconductor substrate;

Petition, Paper No. 2, at 23

#### b) Claim 1 – Active Region (element [1a])

Claim 1 recites "an active region made of a semiconductor substrate." ('501 patent, claim 1 (Ex-1001).) Igarashi in view of Woerlee discloses this limitation.

(Shanfield Decl. ¶64 (Ex-1002).)

For example, Igarashi discloses a "semiconductor substrate 1," as illustrated in Fig. 12:

Fig. 12

(Igarashi at Fig. 12 (Ex-1004); see also, e.g., id. at [0044]-[0045], [0112] (discussing the "semiconductor substrate 1").) (Shanfield Decl. ¶65 (Ex-1002).)

A POSITA would have understood that Igarashi discloses an active region made of the semiconductor substrate 1 because Igarashi discloses: "First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the active element region for forming the well and controlling the threshold value." (Igarashi at [0068] (Ex-1004).) That is, Igarashi discloses an "active region made

### '501 patent, at Claim 1

regions) in Woerlee are formed in regions of the active region 4 located on both sides of the gate electrode 21 (as recited in claim 1, element 1d below). The modified device would also have an active element region (active region) divided by the STI regions (isolation region) formed in the semiconductor substrate 1 (as recited in claim 10 below), just as the active region 4 is divided by an isolation region 3 formed in the semiconductor substrate 1 in Woerlee. (Shanfield Decl. ¶73 (Ex-1002).)

Therefore, Igarashi in view of Woerlee discloses "an active region made of a semiconductor substrate." (Shanfield Decl. ¶74 (Ex-1002).)

c) Claim 1 – Active Region (element [1a]) – Reasons to Modify

It would have been obvious to modify Igarashi in view of Woerlee's teachings of an active region "made of" a semiconductor substrate (recited in claim 1, element 1a) and an active region divided by an isolation region formed in the semiconductor substrate (recited in claim 10 below). In particular, it would have been obvious to apply Woerlee's teachings to Igarashi by forming Igarashi's active region in the substrate and defining it with STI regions that divide the active region. (Shanfield Decl. ¶75 (Ex-1002).)

First, a POSITA would have looked to the teachings of Woerlee because it is in the same field of endeavor as Igarashi. Igarashi discloses a MISFET device with a "silicon semiconductor substrate 1" where "fellement isolation is performed" to

## The Petition Fails To Identify a 'MISFET Includes: An Active Region' As Claimed

a. The Petitions Fail to Meet Petitioner's Burden of Demonstrating How and Why Any MISFET in the Igarashi/Woerlee Combination Includes an "Active Region" Meeting the Agreed-Upon BRI

The Petitions must specify the grounds with particularity. 35 U.S.C.

§312(a)(3) (requiring IPR petitions to identify "with particularity . . . the evidence

that supports the grounds for the challenge to each claim"); 37 C.F.R.

§42.104(b)(4) ("The petition must specify where each element of the claim is

found in the prior art patents or printed publications relied upon."); Harmonic, 815

F.3d at 1363; Kranos, IPR2016-01649, Paper No. 25 at 29, 36, 39-42.

The Petitions fail to meet Petitioner's burden of establishing that *any*MISFET in the Igarashi/Woerlee combination "includes: an active region" meeting the agreed-upon BRI. Ex.-2007, ¶132.

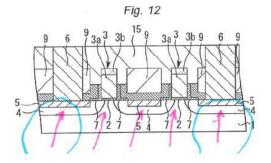

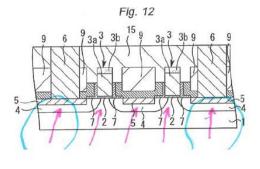

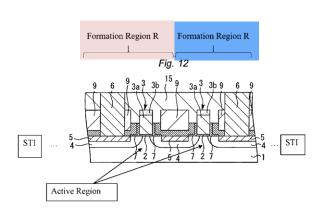

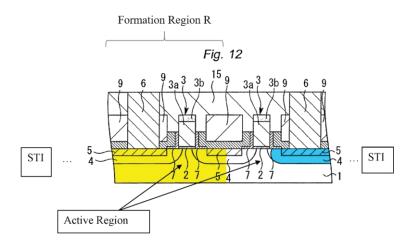

As shown in Petitioner's modified Fig. 12 (reproduced below), the Petitions insert "STI" regions on the left and right sides, and further label the figure with a box "Active Region" and two arrows pointing to the channel regions under the gates of the two MISFETs. Ex.-2007, ¶132. The Petitions allege the "active element region is made of the substrate 1 of Igarashi and divided by STI regions." -1841-Petition at 27, 37. Ex.-2007, ¶132.

## Shanfield's Declaration Does Not Solve The Problems In The Petition As He Repeats The Petition Verbatim

U.S. Patent 7,893,501 Petition for *Inter Partes* Review

Claim 1 recites "an active region made of a semiconductor substrate." ('501 patent, claim 1 (Ex-1001).) Igarashi in view of Woerlee discloses this limitation. (Shanfield Decl. ¶64 (Ex-1002).)

For example, Igarashi discloses a "semiconductor substrate 1," as illustrated in Fig. 12:

(Igarashi at Fig. 12 (Ex-1004); see also, e.g., id. at [0044]-[0045], [0112] (discussing the "semiconductor substrate 1").) (Shanfield Decl. ¶65 (Ex-1002).)

A POSITA would have understood that Igarashi discloses an active region made of the semiconductor substrate 1 because Igarashi discloses: "First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the active element region for forming the well and controlling the threshold value." (Igarashi at [0068] (Ex-1004).) That is, Igarashi discloses an "active region made

U.S. Patent 7,893,501 Declaration of Stanley R. Shanfield, Ph.D.

- 63. Therefore, Igarashi discloses the preamble.

- b) Claim 1 Active Region (element [1a])

- 64. Claim 1 recites "an active region made of a semiconductor substrate."

('501 patent, claim 1 (Ex-1001).) Igarashi in view of Woerlee discloses this

limitation.

- 65. For example, Igarashi discloses a "semiconductor substrate 1," as illustrated in Fig. 12:

(Igarashi at Fig. 12 (Ex-1004); see also, e.g., id. at [0044]-[0045], [0112] (discussing the "semiconductor substrate 1").)

66. A POSITA would have understood that Igarashi discloses an active region made of the semiconductor substrate 1 because Igarashi discloses: "First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the

25

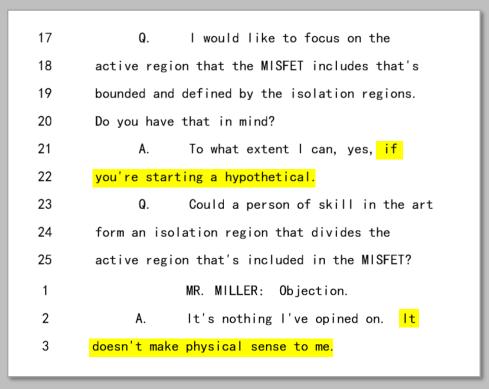

"Shanfield refused to explain whether ... the alleged 'active region' was the entire region bounded by isolation regions so that there was only one 'active region' present, or ... more than one 'active region' was present." (POR 63)

- 2 Q. How many active regions are shown in the

- 3 cross-section of figure 12 of Igarashi?

- 4 MR. SMITH: Objection.

- 5 A. Again, I'm taking "active region" as used

- 6 in the claim language and understanding it with

- respect to the claim language, and that's the

- 8 consideration I made. I didn't do any counting

- 9 exercises as to the number of active regions or --

- because there was no reference to -- or the need to

- count regions in understanding the claim language.

Shanfield Opening Depo., Ex. 2010 at 424:2-11 (cited in POR at 70)

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

device that Dr. Glew would expect to have an "active region." Ex. 2007, ¶¶91-92; see also, Ex. 1024, 110:23-111:4. Ex. 1027, ¶33.

C. Patent Owner's Attacks on Dr. Shanfield's Testimony are Purely a Distraction

PO desperately attacks Dr. Shanfield in its Response for allegedly not answering the question of whether Igarashi shows one active region or two active regions. Response, 13-14. However, Dr. Shanfield repeatedly tried to explain how this was not a distinction relevant to the challenged claims or his analysis. When PO persisted in trying to get Dr. Shanfield to say it was one active region or two, Dr. Shanfield testified truthfully that this was not a question that made sense

- 22 -

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

technically.<sup>6</sup> Dr. Shanfield was not unable or unwilling to answer the question. To the contrary, he repeatedly and patiently answered PO's questions over two full days of deposition and even stayed in deposition for over an hour beyond PO's allotted seven hours on the second day. Ex. 1027, ¶34. The trouble for PO is not that Dr. Shanfield did not provide an answer—it is that PO just did not like the answer he gave.

For example, in the very passage PO cites to support Dr. Shanfield's alleged non-answers (PO cites Ex. 2010, 437:23-438:10, omitting lines 11-19, bracketed

<sup>6</sup> In contrast, Dr. Glew demonstrated a lack of familiarity with the opinions set forth in his own declaration and could not testify one way or another whether testimony he offered in his own declaration was correct. *Compare:* "Q. Would you agree that once LOCOS and STI were discovered, they allowed manufacturers to pack transistors more densely than a semiconductor device? A. I haven't opined on the enabling nature of LOCOS or STI in my declaration. That would require a separate analysis." (Ex. 1024, 105:23-106:4), *with:* "Once isolation techniques such LOCOS and then STI were discovered, they were frequently implemented, as they allowed manufacturers to pack transistors more densely in semiconductor devices..." (Ex. 2007, ¶112).

- 23 -

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

below), Dr. Shanfield explains that PO's counsel's questions did not make technical sense and that he was doing his best to answer them:

- "I have explained that that isn't a meaningful question, in that that isn't

a consideration I needed to make in order to interpret the claim

language."

- "[I am happy to tell you what the interpretation of 'active region' I made with respect to the claim language. Since you're using the claim language, I'm compelled to answer in terms of the claim language in that context, and I think trying a -- trying to get me to -- to create a new description of what's connected and what isn't isn't the consideration I was making in interpreting the claim]." (Ex. 2010, 438:11-19.) Ex. 1027, ¶35.

PO also fails to note that this same line of confusing questioning and Dr.

Shanfield's efforts to clarify and answer went on for numerous pages of deposition transcript preceding the cited passage. Ex. 2010, 410:1-437:22. Through his testimony, and consistent with his declaration, Dr. Shanfield explained how Igarashi invalidates the claims under either view.

A non-exhaustive sampling of his answer includes:

- 24 -

## Shanfield's Deposition Testimony First Asserted that there are Two Active Regions

- O. Does the transistor on the left and the

- transistor on the right in your annotated figure 12

- share the same active region?

- 15 A. No.

- Q. Is there more than one active region shown

- in figure 12?

- 18 A. (Witness reviews document.) The active

- region is "the region bounded by isolation regions

- where the transistor is formed."

- 21 I'm pointing to two different active

- regions where two different transistors are formed.

Shanfield Opening Depo, Ex. 2009, at 91:12-22 (cited POR at 64)

- 9 Q. So you testified yesterday that there were

- two active regions in the substrate.

- A. No, I never testified that.

Shanfield Opening Depo., Ex. 2010, at 401:9-11 (cited POR at 66)

The problem with Shanfield's assertion that the regions where the transistors are formed include two distinct "active regions" is clear from the highlighted figure above. It is irreconcilable with his own testimony that the active region is "defined by" the STI regions, as he modified Fig. 12 to show only one alleged STI region on each side of the transistors (thus allowing for no more than one active region that could be "defined by" the two alleged STI regions). Ex.-2007, ¶139-40; Ex.-2009, 93:11-20. *Neither* of the highlighted regions where a transistor is formed is bounded by the isolation regions because there is no isolation region between the transistors. Ex.-2007, ¶140. Indeed, there can be no isolation region between the transistors because they share a source/drain region. Ex.-1004, ¶0088, Fig. 12; Ex.-2007, ¶140.

65

POR at 65

### **Shanfield Gave Inconsistent Testimony**

- A. So starting with page 35 -- and, again, 21 I'm explaining what an active region is appropriate to the context of the '501 patent. So if you look 23 at figure 12 on page 35 of my declaration 1002, O. Does the transistor on the left and the 12 transistor on the right in your annotated figure 12 13 share the same active region? 14 A. No. 15 Q. Is there more than one active region shown 16 in figure 12? 17 A. (Witness reviews document.) The active 18 region is "the region bounded by isolation regions where the transistor is formed." 20 I'm pointing to two different active 21 regions where two different transistors are formed. 22

- Shanfield Opening Depo., Ex. 2009, at 86:21-24; 91:12-22 (cited POR at 64)

- Q. In the bracketed region, is there one or more than one active region? MR. SMITH: Objection. 10 A. The active region is the region where 11 transistors are formed between the isolation, and there's one active region here because of the way I've drawn it. Q. So that bracket reflects that there is one active region; is that correct? A. Given the definition I'm applying, which 17 is, it's the -- and I -- as I've pointed out, Igarashi doesn't explain what's going on here. I've put "..." with the assumption or with the presumption that there's more transistor formation out here (indicating); and, ves, then, that is one active region. 23

Shanfield Opening Depo., Ex. 2010, at 406:8-23 (cited POR at 68)

## **Shanfield Gave Inconsistent Testimony**

- Q. Does the transistor on the left and the

- transistor on the right in your annotated figure 12

- share the same active region?

- 15 A. No.

Shanfield Opening Depo., Ex. 2009, at 91:12-15 (cited POR at 64)

- 2 O. Doctor Shanfield, is there one or more

- 3 than one active region located between the STIs in

- 4 figure 12 of Igarashi on page 35 of your

- 5 declaration?

- MR. SMITH: Objection.

- A. I think I explained that they're sharing

- an active region, 'cause they're sharing a region

- where transistors are being formed.

- Q. What do you mean when you say "they are

- 11 sharing"?

- 12 A. This gate on the left and this gate on the

- 13 right are a pair of devices connected together, and

- 14 those -- or this -- this construction, which is a

- device in itself, has got an active region under

- 16 it.

Shanfield Opening Depo., Ex. 2010 at 409:2-16 (cited POR at 70)

technically.<sup>6</sup> Dr. Shanfield was not unable or unwilling to answer the question. To the contrary, he repeatedly and patiently answered PO's questions over two full days of deposition and even stayed in deposition for over an hour beyond PO's allotted seven hours on the second day. Ex. 1027, ¶34. The trouble for PO is not that Dr. Shanfield did not provide an answer—it is that PO just did not like the answer he gave.

For example, in the very passage PO cites to support Dr. Shanfield's alleged non-answers (PO cites Ex. 2010, 437:23-438:10, omitting lines 11-19, bracketed

### Reply, Paper No. 22, at 23

Petition, Paper No. 2, at 27

the agreed-upon BRI in the modified-Igarashi Fig. 12, as there is no "MISFET [that] includes" the region bounded by the isolation region. *Id.*

After walking away from his assertion that there are two active regions in modified-Igarashi Fig. 12, Shanfield spent the next hour of the deposition wrestling with the simple question of whether the two (or more) transistors in the Fifth Embodiment of Fig. 12 include a single "active region" or more than one. Ex.-2007, ¶147. At times, he suggested that there might be just one active region bounded by the isolation region he alleged must be present in Igarashi's Fifth Embodiment. Ex.-2010, 406:8-23 ("there's one active region here" in Fig. 12); Ex.-2007, ¶147; see also Ex.-2010, 409:2-16 ("I think I explained that they're sharing an active region.").

But Shanfield refused to maintain and defend that position, because it too is indefensible. Ex.-2010, 421:10-24, 424:2-11, 427:20-428:9; Ex.-2007, ¶147. Unwilling to defend the (indefensible) position that the active area for any MISFET includes an area of the substrate where a *different* transistor is formed, Shanfield ultimately refused to take a position on whether there was a single active region in his modified-Igarashi Fig. 12. Ex.-2010, 421:10-24 (\*I didn't go through any counting exercise."), 424:2-11 (\*I didn't do any counting exercises as to the number of active regions"), 427:20-428:9; Ex.-2007, ¶147. He testified that he

specification, as would any person of ordinary skill." Ex.-2010, 430:5-9; Ex.-2007, ¶147. Yet he repeatedly refused to delineate the boundaries of the alleged active region(s) in Fig. 12 of Igarashi, or to describe how many active regions were shown in Fig. 12. Ex.-2007, ¶147; e.g., Ex.-2010, 437:23-438:10.

For instance, when asked the simple question of whether two portions of the device shown below in Fig. 12 of Igarashi (annotated by Shanfield using pink arrows circled in blue) together comprised one or more than one active region, Shanfield stated that he "can't answer." Ex.-2010, 437:23-438:10 ("Q. [T]he two arrows that you circled in blue, are they in one or more than one active region? ...

A. I have explained that that is isn't [sic] a meaningful question in that that isn't a consideration I needed to make in order to interpret the claim language. What I needed to understand was what 'active region' meant in the context of the claim.

So I can't answer."); Ex.-2007, ¶147.

71

70

"simply knew what 'active region' was in the context of this claim and the

specification, as would any person of ordinary skill." Ex.-2010, 430:5-9; Ex.-2007, ¶147. Yet he repeatedly refused to delineate the boundaries of the alleged active region(s) in Fig. 12 of Igarashi, or to describe how many active regions were shown in Fig. 12. Ex.-2007, ¶147; e.g., Ex.-2010, 437:23-438:10.

For instance, when asked the simple question of whether two portions of the device shown below in Fig. 12 of Igarashi (annotated by Shanfield using pink arrows circled in blue) together comprised one or more than one active region, Shanfield stated that he "can't answer." Ex.-2010, 437:23-438:10 ("Q. [T]he two arrows that you circled in blue, are they in one or more than one active region? ...

A. I have explained that that is isn't [sic] a meaningful question in that that isn't a consideration I needed to make in order to interpret the claim language. What I needed to understand was what 'active region' meant in the context of the claim.

So I can't answer."); Ex.-2007, ¶147.

71

1. A semiconductor device, comprising a MISFET, wherein

#### the MISFET includes:

an active region made of a semiconductor substrate; a gate insulating film formed on the active region; a gate electrode formed on the gate insulating film; source/drain regions formed in regions of the active region located on both sides of the gate electrode; and

a silicon nitride film formed over from side surfaces of the gate electrode to upper surfaces of the source/drain regions, wherein:

the silicon nitride film is not formed on an upper surface of the gate electrode, and

the gate electrode protrudes upward from a surface level of parts of the silicon nitride film located at both side surfaces of the gate electrode.

### '501 patent at Claim 1

Mapping the agreed-upon BRI of "active region" and claim 1's

requirement that "the MISFET includes: an active region" onto the prior art

structure the Petitions allege meets the claimed "active region" is the furthest

thing from irrelevant. Harmonic Inc. v. Avid Tech., Inc., 815 F.3d 1356, 1363

(Fed. Cir. 2016) (affirming final written decision upholding patentability where

Petitioner offered merely "conclusory" discussion of the prior art and failed to

explain with particularity how the limitations were disclosed); Kranos Corp. v.

Riddell, Inc., IPR2016-01649, Paper No. 25 at 29, 36, 39-42 (PTAB Feb. 7, 2018)

(Petitioner failed to meet its burden where "it is unclear from Petitioner's argument

where each element of [the challenged claims] is found in" the prior art and the

Board "decline[d] to speculate as to Petitioner's intentions").

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

- "But what I can provide is what was asked of me and what I put in my

declaration, and that is, is -- active region, as used in the claim, claim

1, is the gate insulating film formed on the active region? Yes.

- "It's an active region between two insulating -- STI regions or

isolating regions; and it's, indeed, a gate insulating film on the

transistor that you've labeled 'A' and the other transistor on the right.

It has a gate insulating film formed on the active region.

- "Is source-drain regions formed in regions of the active region? Yes, there are several regions of the active region where source-drain regions are formed. And with that analysis, I could conclude that Igarashi met these two limitations I'm describing."

Ex. 2010, 429:12-430:5. Dr. Shanfield's opinion that Igarashi discloses the claimed "active region" is presented in his declaration and confirmed in his testimony. PO's assertion that Dr. Shanfield could not answer is simply wrong. Ex. 1027, ¶36.

D. Patent Owner Again Incorrectly Argues that the Petition Relies on Woerlee Only for the Location of the Active Region

PO argued in its POPR that "even if a [POSITA] would have been led to combine the features of Igarashi and Woerlee in the manner alleged in the Petition, the resulting semiconductor device does not include a MISFET having an active

- 25 -

REPLY DECLARATION OF STANLEY R. SHANFIELD, PH.D.

**TSMC 1027**

Shanfield Reply Decl., Ex. 1027

## The Petition Fails To Identify a 'MISFET Includes: An Active Region' As Claimed

b) Claim 1 – Active Region (element [1a])

Claim 1 recites "an active region made of a semiconductor substrate." ('501 patent, claim 1 (Ex-1001).) Igarashi in view of Woerlee discloses this limitation. (Shanfield Decl. ¶64 (Ex-1002).)

For example, Igarashi discloses a "semiconductor substrate 1," as illustrated in Fig. 12:

(Igarashi at Fig. 12 (Ex-1004); see also, e.g., id. at [0044]-[0045], [0112] (discussing the "semiconductor substrate 1").) (Shanfield Decl. ¶65 (Ex-1002).)

A POSITA would have understood that Igarashi discloses an active region made of the semiconductor substrate 1 because Igarashi discloses: "First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the active element region for forming the well and controlling the threshold value." (Igarashi at [0068] (Ex-1004).) That is, Igarashi discloses an "active region made

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes: an active region made of a semiconductor substrate;

### '501 patent at Claim 1

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

Moreover, the Petition showed that Igarashi's isolation region teachings were applicable to its Figure 12 embodiment. Specifically, the Petition cites Figure 12, which shows the "semiconductor substrate 1." Petition, 25. Then, the Petition explains that a POSITA would have understood that the semiconductor substrate 1 in Fig. 12 has an active region because Igarashi expressly discloses an "active element region" made of the semiconductor substrate 1. Petition 25-26, citing Ex. 1004, [0068]; Ex. 1002, [66; Ex. 1010, 42-43. Ex. 1027, [27.

Accordingly, both the Petition and Dr. Shanfield's testimony have been clear and consistent throughout this proceeding: Igarashi discloses the "active region" of the challenged claims in connection with its Fifth Embodiment. Moreover, as discussed below in Section III.D, the Petition also demonstrated it would have been obvious to form the active region disclosed in Igarashi in semiconductor substrate 1 of Igarshi's Fifth Embodiment in view of the teachings of Woerlee. Ex. 1027, ¶28.

#### B. Igarashi Discloses a MISFET that Includes an "Active Region"

A person of ordinary skill would have viewed the region between the two STI in Igarashi where the two transistors are formed as an "active region" formed between those two STI. As noted in the Petition: "The use of the 'trench method' confirms the 'active element region' (active region) is made of the semiconductor substrate 1 because according to the trench method the active region is formed in

## The Petition Fails To Identify a 'MISFET Includes: An Active Region' As Claimed

Pet. at 27, Petitioner's Modified-Igarashi Fig. 12, Ex.-1004, Fig. 12

As the Petitions and Petitioner's expert agree, a MISFET's active region must be both bounded and defined by an isolation region. §VI.A.1; Ex.-2007,

¶133. The Petitions and Petitioner's expert also agree that a MISFET's active region must be the region in which the MISFET is formed. §VI.A.1; Ex.-2007,

¶133. Yet the Petitions failed to explain how or why the Petitions' modified-

Igarashi Fig. 12 has a MISFET that "includes" an active region meeting both these

requirements. Ex.-2007, ¶133.

Despite agreeing that an "active region" as claimed must be *defined and*bounded by isolation regions (§VI.A.1), the Petitions fail to identify the

boundaries of the alleged "Active Region" in modified-Igarashi Fig. 12. Ex.-2007,

¶133. The Petitions' mapping, such as it is, of "active region" onto the modified-Igarashi Fig. 12 is vague and insufficient. *Harmonic*, 815 F.3d at 1363; *Kranos*,

IPR2016-01649, Paper No. 25 at 29, 36, 39-42.

## "Petitioner's New Arguments regarding Active Region"

*First*, even transistors that do not use isolation regions such as STI still have active regions—otherwise, the transistors would simply not function. The absence of an isolation region does not signify the absence of an active region. *Second*, by the

Reply, Paper No. 22, at 14

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

the substrate and defined by the STI regions. Petition, 25-26, citing Ex, 1010, 42-43 (explaining that the manufacturing process for a MISFET "starts with the definition of the active regions—these are the regions where transistors will be constructed. All other areas of the die will be covered with a thick layer of silicon dioxide (SiO2) called the field oxide. This oxide acts as the insulator between neighboring devices, and it is either grown (as in the process of Figure 2-1) or deposited in etched trenches (Figure 2-2)—hence, the name trench insulation.")

As discussed in Section II above with respect to Agata and Rashed (and PO's district court infringement contentions), it is visibly clear that Igarashi discloses the claimed "active region" of the '501 patent. Ex. 1027, ¶29.

As discussed below, Dr. Shanfield was asked during his deposition whether this active region would be considered one active region or two active regions.

Under either view, Igarashi's disclosure meets the claim limitations because the MISFETs in either case include an active region bounded by STI. Under the first, each MISFET includes an active region because each transistor is formed in the active region between the STI. There is nothing that precludes multiple transistors from being formed in the active region, nor does the claim require that each transistor have its own active region that is separated from other active regions by isolation regions. See Section II, above: Ex. 1025. Indeed, Dr. Glew admitted that

- 20 -

Reply, Paper No. 22, at 20-21

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

the term "includes" in claim 1 means "that it has at least these features." Ex. 1024, 94:20-95:7. Under the second, each transistor includes an active region because there are two transistors and two active regions. Ex. 1027, ¶30-31.

PO's (and Dr. Glew's) arguments against Igarashi's "active region" are internally inconsistent. For example, in its Response, PO first argues that the entire region bounded by isolation regions is not the formation region for *any* transistors. Response, 17-18. Yet, in the very next sentence, PO concedes that this region is the formation region for at least two transistors. Response, 18 ("It is undisputed that there are at least two transistors in Igarashi's Fig. 12."). Ex. 1027, ¶32.

PO's attempt to argue that Igarashi's Figure 12 embodiment somehow does not have an active region because it is a memory device also fails. Response, 33-34. When asked to provide examples of known devices having "active regions," Dr. Glew admitted that there were various types of devices—including "logic and memory devices"—that would have "active regions." Ex. 1024, 97:7-18. Ex. 1027, ¶33.

And, as Dr. Glew confirmed in his declaration, Igarashi's Fifth Embodiment shown in Figure 12 "comprises a portion of a memory cell"—precisely the type of

- 21 -

## "Petitioner's New Arguments that Isolation Region Not Required to Form an Active Region"

*First*, even transistors that do not use isolation regions such as STI still have active regions—otherwise, the transistors would simply not function. The absence of an isolation region does not signify the absence of an active region. *Second*, by the

leakage current flow. It was known to POSITAs that isolation regions that define and divide the active regions are required in all transistor devices because they prevent stray potentials (voltages) and current leaks between devices. In particular,

Reply, Paper No. 22, at 14

Petition at 33

A POSITA would have understood that Igarashi discloses an active region made of the semiconductor substrate 1 because Igarashi discloses: "First, an insulating film for isolating elements is formed on a silicon semiconductor substrate 1. Element isolation is performed using methods such as the LOCOS method or the trench method. Thereafter, ion implantation is performed to the active element region for forming the well and controlling the threshold value."

(Igarashi at [0068] (Ex-1004).) That is, Igarashi discloses an "active region made of the semiconductor substrate" both because it explicitly discloses a "active element region" and because it discloses using the "trench method" for "element isolation," meaning the trench method is used to form shallow trench isolation (STI) regions that define the active region where the transistor is formed.

(Shanfield Decl. ¶66 (Ex-1002).)

Petition at 25-26

## The Petition Asserted That An Active Region Must Be Bounded By Isolation And Be The Region Where the Transistor is Formed

62,66. The dispute between the parties relates to whether, and if so how, the claim requirement that "the MISFET includes: an active region" is met by the prior art relied upon in the grounds.

The Petitions and Petitioner's Expert Consistently Characterize the Active Region as an Area of the Semiconductor Substrate Defined by an Isolation Region Where the Transistor Is Formed

While the Petitions did not offer an explicit interpretation, they consistently characterized the active region as an area of the semiconductor substrate defined by an isolation region where the transistor is formed. Ex.-2007, ¶63-64; see, e.g., Petition at 26 ("isolation (STI) regions that define the active region where the transistor is formed."); id. ("the active region is ... defined by the STI regions."); id. at 28 ("isolation regions 3 ... define the active region 4 of the substrate body 1 where the transistor is formed."); id. at 30 ("the active region is an area of the semiconductor body 1 defined and separated by field insulation region 3.").

In his declarations and at his deposition, Shanfield consistently described the "active region" in the same manner. Ex.-2007, ¶65; Ex.-1002, ¶ 66; *see*, *e.g.*, Ex.-1002, ¶ 37,39 ("The STI are formed using the trench method and define the active region."),40,68,70 (Woerlee's "active region 4 is an area of semiconductor body 1 defined and separated by field insulation region 3"), 72,76 ("[e]lement isolation is performed' to define the 'active element region.""), 77-80, 89; Ex.-2009, 45:22-46:23 ("The '501-patent describes the active region made of the substrate as a

region bounded by isolation regions where the transistor is formed."), 48:3-6, 51:12-21, 52:16-20, 69:7-9, 89:17-22, 90:14-18, 91:16-20; Ex.-2010, 406:8-14; see also, e.g., Ex.-1002, ¶¶ 37,39-40,67,69,70-71,73,77-81, 90,154.

2. The '501-Patent Specification Describes an Active Region as an Area of the Semiconductor Substrate Defined by an Isolation Region Where the Transistor is Formed

In the '501-patent, an "active region" of a MISFET refers to a region of the semiconductor substrate defined by an isolation region in which the MISFET is formed. Ex.-2007, ¶67. The specification repeatedly refers to a semiconductor substrate being divided by an isolation region into a plurality of active regions. Ex.-2007, ¶¶67-69; *e.g.*, Ex.-1001, 3:21-23 ("an Si (100) substrate is divided into a plurality of active regions 1a and 1b by an isolation region 2"), 6:22-26 ("forming an isolation region 2 for dividing the substrate into active regions 1a, 1b and so on"), 9:38-39, 10:53-54, 12:25-28 ("forming an isolation region 2 for dividing the substrate into active regions 1a, 1b and so on"), Figs. 1-9.

The specification describes each transistor as having a formation region (e.g., Rn, Rp) that includes the active region in which the transistor is formed. Ex.-1001, 3:24-28. All embodiments illustrated in figures of the '501-patent illustrate a semiconductor device comprising MISFET formation regions Rn, Rp that include active regions (e.g., active regions 1a, 1b) that are defined by isolation region 2, have transistors formed therein, and where the transistor's source/drain regions 3, 4

28

### "Petitioner's New Arguments regarding Active Region"

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

the substrate and defined by the STI regions. Petition, 25-26, *citing* Ex, 1010, 42-43 (explaining that the manufacturing process for a MISFET "starts with the definition of the active regions—these are the regions where transistors will be constructed. All other areas of the die will be covered with a thick layer of silicon dioxide (SiO2) called the field oxide. This oxide acts as the insulator between neighboring devices, and it is either grown (as in the process of Figure 2-1) or deposited in etched trenches (Figure 2-2)—hence, the name trench insulation.") As discussed in Section II above with respect to Agata and Rashed (and PO's district court infringement contentions), it is visibly clear that Igarashi discloses the claimed "active region" of the '501 patent. Ex. 1027, ¶29.

As discussed below, Dr. Shanfield was asked during his deposition whether this active region would be considered one active region or two active regions.

Under either view, Igarashi's disclosure meets the claim limitations because the MISFETs in either case include an active region bounded by STI. Under the first, each MISFET includes an active region because each transistor is formed in the active region between the STI. There is nothing that precludes multiple transistors from being formed in the active region, nor does the claim require that each transistor have its own active region that is separated from other active regions by isolation regions. *See* Section II, above; Ex. 1025. Indeed, Dr. Glew admitted that

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

the term "includes" in claim 1 means "that it has at least these features." Ex. 1024, 94:20-95:7. Under the second, each transistor includes an active region because there are two transistors and two active regions. Ex. 1027, ¶¶30-31.

Reply, Paper No. 22, at 21

Petition at 27

- 20 -

Reply, Paper No. 22, at 20

## The Argument That In Igarashi/Woerlee Fig. 12 Two Transistors Share The Same Active Region Is Improper New Argument

4. Reply, p. 19, l. 16 to p. 21, l. 3, p.10, l. 17 to p. 13, l. 5; Ex. 1027, ¶ 16-18, 29-31: Argument that the *entire* area "between the two STI in Igarashi [modified Fig. 12]" meets the claimed "active region" is **new**, as the Petition and its supporting expert declaration *nowhere* explain whether this area is alleged to include one or two (one per transistor) active regions as confirmed by the contradictory and ultimately non-comital testimony of Petitioner's expert at deposition. E.g., Ex. 2009 at 91:12-92:14 (two active regions); Ex. 2010 at 400:16-401:11 (denying prior testimony; identifying one active region); 406:5-408:9 (retracting testimony for annotated Figure 12 (Ex. 2002 described at Ex. 2010 at 404:12-20; 192:21-22) and requesting to strike testimony); 410:1-24 ("can't answer"); 416:11-17 (not relevant to understanding the claim); 424:2-11 (not needed to understand claim). 5. Reply, p. 20, l. 11, p. 21, l. 3; Ex. 1027, ¶ 31: Petitioner's cursory and conclusory "argument," that the area "between the two STI in Igarashi [modified Fig. 12]" includes multiple "active regions" (one per transistor) contradicts the new argument in #4 and also is new, as the Petition and its supporting expert declaration *nowhere* explained whether this area is alleged to include one or two (one per transistor) active regions as confirmed by the contradictory and ultimately non-comital testimony of Petitioner's expert at deposition cited in #4.

Dated: July 24, 2018

Respectfully submitted,

By /Gerald B. Hrycyszyn / Gerald B. Hrycyszyn, Reg. No. 50,474

2

Paper 27, Patent Owner's Identification of Improper Arguments, at 2

4. The Reply at 9-13 and 19-22 responds to the arguments in the POR on pages 14-21, 28-29, 33-36, and 58-74 that Igarashi's Fig. 12 embodiment does not have a single large active region or two smaller active regions that satisfy the claims. In response, the Reply confirms that a POSITA would have viewed the region between the two STI as the claimed active region and identifies where this is shown in the Pet. Reply at 19-20 (citing Pet. at 25-26). The Reply also confirms in response to the POR that Igarashi discloses the claimed active region under either view and that PO's construction is unduly narrow. Reply at 9-13, 20-22. The Reply specifically states at 9:1-4 and 21:4-22:2 that these arguments respond to POR at 17-18, 33-34, 28-29, and 74. The Reply also responds to PO's mischaracterization of Dr. Shanfield's testimony. Reply at 22-25; see also Ex. 2009 at 93:16-20 (clarifying region between STI is an active region, not two active regions); Ex. 2010 at 401:9-402:4 (confirming clarification); id. at 408:10-17, 411:7-412:3 (confirming region between STI is the active region); id. at 429:12-430:5, 437:11-19 (attempting to clarify and answer confusing questions).

5. As noted for 4., the Reply at 20-21 responds the POR's arguments that Igarashi does not have a single large active region or two smaller active regions that satisfy the claims and confirms Igarashi discloses the active region under either view.

Dated: July 27, 2018

Respectfully Submitted,

/Michael Smith/

Michael H. Smith, Reg. No. 71,190

2

Paper 29, Petitioner's Response, at 1-2

## The Argument That Igarashi/Woerlee Fig. 12 Has A Separate Active Region For Each Transistor Is Improper New Argument

4. Reply, p. 19, l. 16 to p. 21, l. 3, p.10, l. 17 to p. 13, l. 5; Ex. 1027, ¶¶ 16-18, 29-31; Argument that the *entire* area "between the two STI in Igarashi [modified Fig. 12]" meets the claimed "active region" is *new*, as the Petition and its supporting expert declaration *nowhere* explain whether this area is alleged to include one or two (one per transistor) active regions as confirmed by the contradictory and ultimately non-comital testimony of Petitioner's expert at deposition. *E.g.*, Ex. 2009 at 91:12-92:14 (two active regions); Ex. 2010 at 400:16-401:11 (denying prior testimony; identifying one active region); 406:5-408:9 (retracting testimony for annotated Figure 12 (Ex. 2002 described at Ex. 2010 at 404:12-20; 192:21-22) and requesting to strike testimony); 410:1-24 ("can't answer"); 416:11-17 (not relevant to understanding the claim); 424:2-11 (not needed to understand claim).

5. Reply, p. 20, l. 11, p. 21, l. 3; Ex. 1027, ¶ 31; Petitioner's cursory and conclusory "argument," that the area "between the two STI in Igarashi [modified]

conclusory "argument," that the area "between the two STI in Igarashi [modified Fig. 12]" includes multiple "active regions" (one per transistor) contradicts the new argument in #4 and also is new, as the Petition and its supporting expert declaration *nowhere* explained whether this area is alleged to include one or two (one per transistor) active regions as confirmed by the contradictory and ultimately non-comital testimony of Petitioner's expert at deposition cited in #4.

Dated: July 24, 2018 Respectfully submitted,

By /Gerald B. Hrycyszyn / Gerald B. Hrycyszyn, Reg. No. 50,474

-

Paper No. 27, Patent Owner's Identification of Improper Arguments, at 2

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Response Pursuant to July 20, 2018 Order

single large active region or two smaller active regions that satisfy the claims. In response, the Reply confirms that a POSITA would have viewed the region between the two STI as the claimed active region and identifies where this is shown in the Pet. Reply at 19-20 (*citing* Pet. at 25-26). The Reply also confirms in response to the POR that Igarashi discloses the claimed active region under either view and that PO's construction is unduly narrow. Reply at 9-13, 20-22. The Reply specifically states at 9:1-4 and 21:4-22:2 that these arguments respond to POR at 17-18, 33-34, 28-29, and 74. The Reply also responds to PO's mischaracterization of Dr. Shanfield's testimony. Reply at 22-25; *see also* Ex. 2009 at 93:16-20 (clarifying region between STI is an active region, not two active regions); Ex. 2010 at 401:9-402:4 (confirming clarification); *id.* at 408:10-17, 411:7-412:3 (confirming region between STI is the active region); *id.* at 429:12-430:5, 437:11-19 (attempting to clarify and answer confusing questions).

does not have a single large active region or two smaller active regions that satisfy the claims and confirms Igarashi discloses the active region under either view.

Dated: July 27, 2018 Respectfully Submitted,

/Michael Smith/

Michael H. Smith, Reg. No. 71,190

2

Paper No. 29, Petitioner's Response, at 2

## The New Argument That Igarashi/Woerlee Fig. 12 Has A Separate Active Region For Each Transistor Fails

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

the term "includes" in claim 1 means "that it has at least these features." Ex. 1024, 94:20-95:7. Under the second, each transistor includes an active region because there are two transistors and two active regions. Ex. 1027, ¶30-31.

PO's (and Dr. Glew's) arguments against Igarashi's "active region" are internally inconsistent. For example, in its Response, PO first argues that the entire region bounded by isolation regions is not the formation region for *any* transistors. Response, 17-18. Yet, in the very next sentence, PO concedes that this region is the formation region for at least two transistors. Response, 18 ("It is undisputed that there are at least two transistors in Igarashi's Fig. 12."). Ex. 1027, ¶32.

PO's attempt to argue that Igarashi's Figure 12 embodiment somehow does not have an active region because it is a memory device also fails. Response, 33-34. When asked to provide examples of known devices having "active regions," Dr. Glew admitted that there were various types of devices—including "logic and *memory* devices"—that would have "active regions." Ex. 1024, 97:7-18. Ex. 1027, ¶33.

And, as Dr. Glew confirmed in his declaration, Igarashi's Fifth Embodiment shown in Figure 12 "comprises a portion of a memory cell"—precisely the type of

U.S. Patent 7,893,501 IPR2017-01841 Reply Declaration of Stanley R. Shanfield, Ph.D.

thick layer of silicon dioxide (SiO2) called the field oxide. This oxide acts as the insulator between neighboring devices, and it is either grown (as in the process of Figure 2-1) or deposited in etched trenches (Figure 2-2)—hence, the name trench insulation.") As discussed in Section II above with respect to Agata and Rashed (and Patent Owner's district court infringement contentions), it is visibly clear that Igarashi discloses the claimed "active region" of the '501 patent.

- As discussed below, I was asked during deposition whether this active region would be considered one active region or two active regions.

- 31. In either view, Igarashi's disclosure meets the claim limitations because the MISFETs in either case include an active region bounded by STI. Under the first view, each MISFET includes an active region because each transistor is formed in the active region between the STI. There is nothing that precludes multiple transistors, each with their own channel, from being formed in the active region, nor does the claim require that each transistor have its own active region that is separated from other active regions by isolation regions. *See* Section II, above; Ex. 1025. I note that Dr. Glew admitted that the term "includes" in claim 1 means "that it has at least these features." Ex. 1024, 94:20-95:7. Under the second view, each transistor includes an active region because there are two transistors and two active regions.

- 21 -

Shanfield Reply Decl., Ex. 1027, ¶¶ 30-31

## The New Argument That Igarashi/Woerlee Fig. 12 Has A Separate Active Region For Each Transistor Fails

The problem with Shanfield's assertion that the regions where the transistors are formed include two distinct "active regions" is clear from the highlighted figure above. It is irreconcilable with his own testimony that the active region is "defined by" the STI regions, as he modified Fig. 12 to show only one alleged STI region on each side of the transistors (thus allowing for no more than one active region that could be "defined by" the two alleged STI regions). Ex.-2007, ¶139-40; Ex.-2009, 93:11-20. *Neither* of the highlighted regions where a transistor is formed is bounded by the isolation regions because there is no isolation region between the transistors. Ex.-2007, ¶140. Indeed, there can be no isolation region between the transistors because they share a source/drain region. Ex.-1004, ¶0088, Fig. 12; Ex.-2007, ¶140.

65

140. Petitioner modified Fig. 12 to show only one alleged STI region on each side of the transistors. This allows for no more than one active region that possibly could be "defined by" the two alleged STI regions. Neither of the highlighted formation regions where a transistor is formed (*see* annotated version of Petitioner's modified Igarashi Figure 12 above) is bounded by the isolation region, or includes an active region bounded by the isolation region, because there is no isolation region between the transistors of the alleged combination. Petitioner and Dr. Shanfield never allege that there would have been an isolation region between the transistors of the alleged combination, and never explain how the two alleged STI regions included in Petitioner's modified Fig. 12 can define, between themselves, two separate active regions. In fact, there can be no isolation region between the transistors because they share a common source/drain region, which

7

Glew Decl., Ex. 2007, ¶140 (cited POR at 65)

## The New Argument That Igarashi/Woerlee Fig. 12 Has A Separate Active Region For Each Transistor Fails

U.S. Patent 7,893,501 IPR2017-01841 Petitioner's Reply to Patent Owner's Response

First, even transistors that do not use isolation regions such as STI still have active regions—otherwise, the transistors would simply not function. The absence of an isolation region does not signify the absence of an active region. Second, by the time of the alleged invention in 2003, virtually all transistors included isolation regions. A POSITA at the time of the alleged invention would not have understood Igarashi to be implemented in a manner that omitted isolation regions or structures (such as STI) because: (i) the transistors commonly used by then were too small for spacing alone to be a functional alternative to isolation regions or structures (such as STI); and (ii) Igarashi expressly discloses the use of isolation regions and such isolation regions would have been obvious in view of Woerlee. Ex. 1027, ¶19; Petition, 25-27; Ex. 1024, 111:18-25 (admitting that using spacing rather than isolation "would not be a typical solution" for memory cells in the 2003 timeframe).

Accordingly, PO's interpretation of an "active region" is inappropriately narrow, forecloses substantial portions of the technical field, and is purely designed to escape the overwhelming prior art. Ex. 1027, ¶20.

### III. IGARASHI AND WOERLEE DISCLOSE THE CLAIMED "ACTIVE REGION"

PO again incorrectly argues that the Fifth Embodiment described in Igarashi, itself, does not teach STI regions forming an active region. Response, 37. The

- 14 -

The Petitions and Petitioner's Expert Consistently Characterize the Active Region as an Area of the Semiconductor Substrate Defined by an Isolation Region Where the Transistor Is Formed

While the Petitions did not offer an explicit interpretation, they consistently characterized the active region as an area of the semiconductor substrate defined by an isolation region where the transistor is formed. Ex.-2007, ¶63-64; see, e.g., Petition at 26 ("isolation (STI) regions that define the active region where the transistor is formed."); id. ('the active region is ... defined by the STI regions."); id. at 28 ("isolation regions 3 ... define the active region 4 of the substrate body 1 where the transistor is formed."); id. at 30 ("the active region is an area of the semiconductor body 1 defined and separated by field insulation region 3.").

In his declarations and at his deposition, Shanfield consistently described the "active region" in the same manner. Ex.-2007, ¶65; Ex.-1002, ¶ 66; see, e.g., Ex.-1002, ¶¶ 37,39 ("The STI are formed using the trench method and define the active region."),40,68,70 (Woerlee's "active region 4 is an area of semiconductor body 1 defined and separated by field insulation region 3"), 72,76 ("'[e]lement isolation is performed' to define the 'active element region.'"), 77-80, 89; Ex.-2009, 45:22-46:23 ("The '501-patent describes the active region made of the substrate as a region bounded by isolation regions where the transistor is formed."), 48:3-6, 51:12-21, 52:16-20, 69:7-9, 89:17-22, 90:14-18, 91:16-20; Ex.-2010, 406:8-14; see also, e.g., Ex.-1002, ¶¶ 37,39-40,67,69,70-71,73,77-81, 90,154.

POR, Paper No. 20, at 27-28

## The New Argument That Igarashi/Woerlee Fig. 12 Has A Separate Active Region For Each Transistor Fails

region. *Id.*, ¶¶6-7. Agata and Rashed say no such thing. To the contrary, they explicitly state that it is the larger "device," to which the active region is dedicated, that "includes" the active region. *Id.*, ¶¶3-5. Agata and Rashed *corroborate* Dr. Glew's testimony that a structure (whether a multi-transistor device in Agata and Rashed or a MISFET in the '501 patent) "includes" an active region only if the active region is dedicated to the structure that "includes" it. *Id.* ¶¶ 7-8. No evidence supports an assertion that any transistor in modified Igarashi Fig. 12 "includes" an active region encompassing other transistors. *Id.*, ¶¶6-7.

Third, Petitioner's assertion that "all functional MOSFET transistors have an active region" is wrong—an active region must be bounded by isolation and a transistor can be formed without isolation. *Id.* ¶ 9; POR at VI.A, VII.C.1.b. While a transistor must be formed in a region, the '501 patent is clear that that is a "formation region," and only if isolation is provided does the formation region include a smaller active region. Ex. 2024 ¶9; Ex. 1001 at 3:20-28, Fig. 1.

Fourth, Petitioner's assertions that interpreting "active region" to encompass multiple transistors is not "prohibited" or "precluded" (Reply at 6, 10, 12) not only ignore the claimed requirement that the "MISFET includes an active region," they also violate the black letter law cited in the POR at 26.

Dated: July 27, 2018

Respectfully submitted, Godo Kaisha IP Bridge 1 By /Richard Giunta / Richard F. Giunta, Reg. No. 36,149

1

dedicated to the MISFET. Agata, Rashed, and the '501 patent refer to a structure (respectively, "sense amplifier", "device," and "MISFET") that "includes" an active region where the active region is *dedicated* to the structure that "includes" it.

- 9. Dr. Shanfield's assertion that "all functional MOSFET transistors have an active region" is unsupported and wrong—an area not defined by isolation is *not* an active region. *See* Ex. 2007 at VII.A, VIII.C.1.b. All transistors must have a region in the substrate where they are formed, but as the '501 patent makes clear this is a "formation region." Ex. 1001 at 3:20-28, Fig. 1.

- 10. Dr. Shanfield mischaracterizes my deposition testimony which addressed the term "comprise" and not "includes." Ex. 1027, ¶31; Ex. 1024 at 94:13-95:7. The open ended "comprising" transition in claim 1 does not eliminate the requirement that the "MISFET includes: an active region," which the grounds do not meet. *See* Ex. 2007 at VIII.C.

- 11. Dr. Shanfield's suggestion that the '501 patent does not show 1-to-1 correspondence between the active regions and MISFETs because the figures are cross sections (Ex. 1027, ¶¶ 14-15) is wrong with respect to Fig. 9A, and refuted by the '501 specification. '501 patent at 3:24-28 (each MISFET "formation region ... *includes* the active region"). Fig. 9A is a "plane view of an MISFET" (3:8-10, 14:42-45) and illustrates isolation region 2 bounding the active region in which the transistor is formed, i.e., defining the boundary of the active region on all sides.

3

Glew Sur-Reply Decl., Ex. 2024 at 3

Patent Owner's Sur-Reply, Paper No. 28, at 3

## A MISFET's Active Region Must Be Defined By Isolation and Be Where the MISFET Is Formed

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes: an active region made of a semiconductor substrate;

'501 patent, at Claim 1

In the Petitions' modified-Igarashi Fig. 12 the entire region of the substrate bounded by the alleged isolation region is not the formation region for *any* MISFET. Ex.-2007, ¶145. Taking the left MISFET as an example, the transistor is formed in the region in yellow below. *Id.* There are other regions of the substrate bounded by the alleged isolation region, e.g., the area in blue, that are unquestionably *not* part of the region (yellow below) where the left MISFET is formed. *Id.*

Neither of the MISFETs shown in the Petitions' modified-Igarashi Fig. 12 is formed in and includes the entire region of the substrate bounded by the isolation region, so the region bounded by the isolation region is not an "active region" of either MISFET. Ex.-2007, ¶146. Thus, there is not one "active region" that meets

# Claim 1 Requires That the MISFET Is The Larger Whole That Includes The Active Region Not Vice Versa

1. A semiconductor device, comprising a MISFET, wherein

the MISFET includes:

- an active region made of a semiconductor substrate;

- a gate insulating film formed on the active region;

- a gate electrode formed on the gate insulating film;

- source/drain regions formed in regions of the active region located on both sides of the gate electrode; and

- a silicon nitride film formed over from side surfaces of the gate electrode to upper surfaces of the source/drain regions, wherein:

- the silicon nitride film is not formed on an upper surface of the gate electrode, and

- the gate electrode protrudes upward from a surface level of parts of the silicon nitride film located at both side surfaces of the gate electrode.

'501 patent at Claim 1

agreed-upon BRI. Ex.-2007, ¶¶136-41. Given that Petitioner's expert Shanfield was unwilling to take a position refuting Dr. Glew's opinion, the testimony of Patent Owner's expert on this critical issue stands unrebutted.

c. No Transistor Includes the Region Bounded by the Alleged Isolation Region in the Petitions' Modified-Igarashi Fig. 12, So There Is Not One "Active Region"

All challenged claims require that "the MISFET includes: an active region."