which again reflects the frequency insensitivity of loss tangent. Table I gives the dielectric properties of the anodic oxide grown under the conditions used in the fabrication of interconnect patterns.

#### Reliability

As discussed earlier the environment of high humidity and elevated temperature have the most deleterious effects upon aluminum interconnects. Transistor-transistor logic circuits were fabricated by the anodic process and subjected to a battery of reliability evaluation. The most severe environment encountered were those of 85% relative humidity, 85 degrees centigrade, pressure cooker  $(121^{\circ}C \pm 3\ 100\%$  R.H. 15 psig) and a boiling water test which involves immersion of the device in boiling deionized water. Table II is a compilation of results of these tests. All tests unless otherwise noted were performed upon plastic encapsulated devices. The extremely low failure rates are indicative of the passivation provided by the anodic oxide. Those devices which did fail were subjected to failure analysis. It was determined that most failures were associated with the bond pad areas which do not receive an anodic overcoat. Some of the failures were noted which could be associated with corrosion of leads which were imbedded in and overcoated with the anodic oxide.

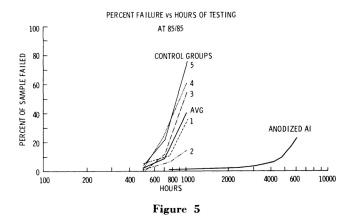

Figure 5 is comparative data of anodized versus glass passivated process on identical devices of a different device type. Both the anodized samples and the control groups were subjected to the same 85% relative humidity  $85^{\circ}C$  environment. Both groups were unencapsulated. This data indicated that the passivating capability of the anodic oxide is nearly an order of magnitude greater than that of a glass overcoat.

#### Conclusion

The anodic processing of aluminum interconnect patterns provides a method of rendering aluminum interconnect compatible with non hermetic packaging. The presence of the barrier layer at the aluminum surface acts to greatly enhance the corrosion resistance of aluminum metal. The reliability of such interconnects on plastic encapsulated integrated circuits has been demonstrated. An evaluation of the dielectric properties of the anodic oxide of aluminum indicate properties which are compatible with single and multilevel interconnects for integrated circuits.

# CURRENT CONCEPTS IN THE PASSIVATION AND ENCAPSULATION OF SEMICONDUCTOR DEVICES

by E E E

BRUCE É. DEAL Research and Development Laboratory Fairchild Camera and Instrument Corporation Palo Alto, California 94304 71C38EI-21

## Introduction

For several years after the introduction of the Planar passivated transistor,<sup>1</sup> this simple structure with thermal silicon dioxide over the junctions provided the basis of the standard semiconductor technology. The device was sealed in a hermetic metal package and little subsequent attention had to be given to it. Gold or aluminum bonds were made to aluminum contacts alloyed to the silicon contact regions. However, the development of integrated circuits, initially simple by today's standards, lead to increased complexity of structure and of fabrication procedures. Furthermore, improved reliability became a necessity with the introduction of MOS transistors, which are very surface sensitive. It was found that by careful processing the same thermal oxide passivated structures in metal packages could provide stable MOS devices. However, it also became apparent that for mass production and low costs required in the industry, other means of passivation and encapsulation would have to be developed. This was especially true when the complexity of the integrated circuits was combined with the sensitiveness of MOS devices.

This paper provides a review of these new concepts in passivation and encapsulation of semiconductor devices. The changing role of the dielectric films used for passivation and protection will be discussed along with newer approaches to the metal contacts and interconnections. Also, the various types of packagesmetal, ceramic and plastic—will be briefly described, as well as problems associated with each system. Finally, the use of dielectric layers for providing corrosion and mechanical protection of the metallized circuits will be considered, along with possible interactions between the various packaging materials and device components. It will be observed that the proper selection of the dielectric films will be a key factor in the successful development of reliable, low cost semiconductor devices.

#### Passivation

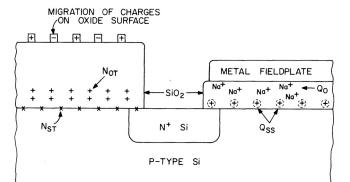

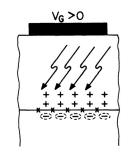

A cross-section of a typical, Planar-passivated diffused junction in silicon is shown in Figure 1. The drawing is such that the lefthand side might represent a diode or a collector-base junction of a bipolar transistor, while the right-hand includes a metal field plate over the oxide as is the case for an MOS transistor. It is now well known that several charges can be associated with the thermally oxidized silicon system. These include fast interface states,  $N_{st}$ , fixed surface charge,  $Q_{ss}$ , mobile impurity charge,  $Q_o$ , and traps due to ionizing radiation,  $N_{ot}$ , as well as ion or charge migration on the oxide surface.<sup>2-4</sup> These charges and their location in the oxide are also indicated in Figure 1. The measurement and characterization of these charges has been the subject of numerous investigations, many of them listed in the MIS bibliographies of Schlegal.<sup>5</sup> Many of these investigations made use of the MOS capacitance-voltage method of analysis,<sup>6-7</sup> and this procedure continues to provide a rapid but simple means of studying charge effects in dielectric layers on semiconductors.

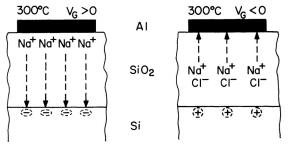

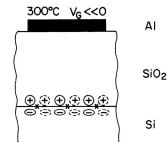

The presence (or migration) of the charges in the MOS structures has been found to have an appreciable effect on device

Figure 1—Example of Charges Associated with Thermally Oxidized Silicon Device Structure:  $Q_{ss}$ , Fixed Surface Charge;  $Q_s$ , Mobile Impurity Ion;  $N_{st}$ , Fast Surface State;  $N_{ot}$ , Hole Traps Formed by Ionizing Radiation; and Charge Migration on Oxide Surface. electrical properties. For instance, low current beta, noise, and breakdown voltage of bipolar transistors can be affected, while turn-on voltage and channel conductance in MOS devices have a critical dependence on the charge densities. Figure 2 indicates some of the possible changes in the densities or location of these charges in the oxide due to electric fields and the resulting effects on the silicon surface. It has been adequately demonstrated, however, that by careful processing, these charge densities can be controlled and minimized so that stable MOS and other devices can be fabricated.<sup>2</sup> However, as the need for increased production of more complex devices occurred with an additional requirement of lower costs, it was found that the control procedures required for stable oxide-passivated devices were very difficult to implement under production conditions. Further, expensive hermetic packages were also required for these sensitive devices. While the thermal oxide can be produced free of ionic contaminants, its structure does not prevent subsequent penetration by ionic impurities or other contamination even at low temperatures. Thus the concept of double dielectrics was established, in which a second dielectric capable of masking ionic impurity migration is deposited over the passivating thermal oxide.

The first dielectric to be used as a passivating layer over thermally oxidized silicon devices was phosphosilicate glass (PSG).<sup>8</sup> It is applied by the vapor deposition of  $P_2O_a$  as in diffusion predeposition processing, the phosphorus oxide mixing with the outer SiO<sub>2</sub> layer to form a  $P_2O_a$ -SiO<sub>2</sub> glass-like structure. This film was found to prevent ionic impurities from diffusing through it as well as to getter impurity ions such as sodium from the underlying SiO<sub>2</sub>. Its disadvantages were that it reacts readily with water as well as exhibiting an undesirable structural polarization effect.<sup>9</sup> Even so, under proper conditions, i.e. controlled thickness and phosphorus concentration, it can be used effectively to better passivate thermal oxides and the associated device structures.<sup>10</sup>

Another type of passivating layer used in conjunction with thermal oxides is a "dense" dielectric such as silicon nitride (Si<sub>a</sub>N<sub>4</sub>) or aluminum oxide (Al<sub>2</sub>O<sub>3</sub>). This type of film prevents the ionic impurities from diffusing through it due to close-packed structure, as opposed to the complexing or gettering action of the phosphosilicate glass. Silicon nitride is generally deposited by the vapor phase reaction of SiH<sub>4</sub> or SiCl<sub>4</sub> with NH<sub>3</sub> in the temperature range 650-1000°C, while alumina films have been produced by the low temperature anodization of deposited aluminum as well as the higher temperature vapor deposition processes. Both types of films have also been deposited by sputtering techniques. Investigations

- (a) MIGRATION OF POSI-TIVE IONS (Q<sub>0</sub>) THROUGH OXIDE TO SiO<sub>2</sub> -Si INTERFACE

- (b) MIGRATION OF POSI-TIVE IONS TO AI-SiO<sub>2</sub> INTERFACE, LEAVING IMMOBILE NEGATIVE IONS IN OXIDE

Figure 2—Examples of Processing Effects on Density or Location of Four Types of Charges in Thermally Oxidized Silicon Structure. involving double layers of  $Si_{\rm B}N_{\rm t}$  or  $Al_2O_3$  over thermally oxidized silicon are reported  $^{11-15}$

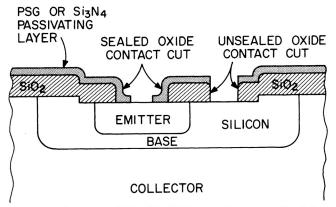

It has been definitely established that the use of these dense films, especially silicon nitride, will provide much more reliable devices. The main advantage is that up to  $500^{\circ}$ C, ion migration through the film is essentially eliminated. The main disadvantages of these films are that processing, especially photomasking, becomes more difficult, and that additional instabilities are encountered. These are discussed below. A typical passivated device structure is shown in Figure 3, where the second dielectric may be phosphosilicate glass, silicon nitride or aluminum oxide. Note the two examples where the edge of the oxide contact cut may or may not be "sealed" with the second dielectric.

Other dielectrics used over thermal oxides have included  $SiO_2$ and other oxides deposited by various techniques. These include evaporation, sputtering, vapor phase reaction and sedimentation. The main purpose of these second layer oxides is to increase the thickness of the original thermal oxide and thus prevent field inversion beneath current-carrying interconnections. In general, these oxides will not prevent ion migration. They may be valuable in providing chip protection of the metallized circuits, and this aspect is discussed below. A general discussion of these deposited oxides is available.<sup>16-17</sup>

An important consideration for the effectiveness of all the above double-layer dielectrics is whether they contribute additional instabilities to the device properties. The advantage gained by the elimination of ion migration may be canceled by additional effects. Four possible charge effects have been found that can be associated with double-dielectric structures. These are indicated in Figure 4, and are shown to be polarization due to dipole orientation, interface trapping, polarization due to conductivity differences and interface charge formation.<sup>2</sup> Many studies have been reported for all these cases and most of the instabilities can be minimized by proper process conditions and control for each type of dielectric. It is not within the scope of this paper to discuss these effects, but they must each be considered in evaluating any given double-dielectric system.

#### Metallization

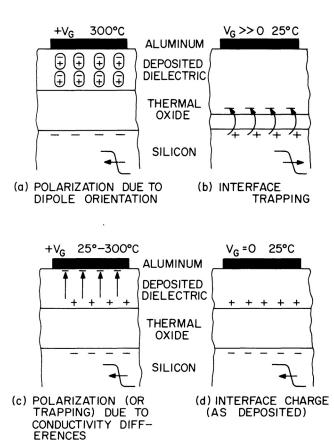

Evaporated metal films were originally used to provide an ohmic contact between the silicon junction areas and a lead wire for connections to outside the package. As geometries got smaller and with the development of integrated circuits, the metal system became a complex array of interconnecting lines and contacts (see Figure 5). More attention had to be paid to effects of the metallization on device characteristics and reliability as well as the effect of the package and/or ambient on the metal integrity itself.

The most commonly used metal for the above applications in semiconductor technology has been aluminum.<sup>18–19</sup> Schnable <sup>19</sup> in his review, discusses advantages and disadvantages of the aluminum metallization system. The advantages are based on its ease of processing (deposition, etching, etc), its high conductivity, and its good adherence and contacting properties. At the same time its reactivity, which accounts for most of these desirable properties, also leads to disadvantages. That is, it can be attacked readily by plastics used for packages and by moisture which is present in nonhermetic packages. It is also subject to electromigration under high current density conditions and microcracking when deposited over steep oxide steps.

The corrosion problem of aluminum interconnections in plastic packages has led to the investigation of other systems. One of the most notable is a part of the Beam Lead Structure (mentioned below) which makes use of a Pt<sub>5</sub>Si<sub>2</sub> contact to the silicon, covered by a Ti-Pt-Au multilayer structure.<sup>20</sup> This is then combined with a Si<sub>2</sub>N<sub>4</sub>-SiO<sub>2</sub> dielectric passivation system.<sup>21</sup> Neither this metal system (especially the platinum) nor the silicon nitride will allow

Figure 3—Typical Double Dielectric Structure Used for Passivating Semiconductor Device. Examples of Both "Sealed" and "Unsealed" Oxide Contact Cut are Indicated.

Figure 4—Four Different Types of Instabilities or Charges Associated With MIOS (Metal-Insulator-Oxide-Semiconductor) Structures.

Figure 5—Comparison of Early and Simple (~1963, 70  $\times$  70 mils, 6 Components) and Recent and Complex (1970, 110  $\times$  140 mils, 2485 Components) Integrated Circuits with Aluminum Interconnections.

sodium penetration up to at least  $300^{\circ}$ C and thus a sealed device structure is obtained. Furthermore, the outer gold layer is very inert to corrosion. As it turns out, however, the nonreactivity of the gold and platinum also result in more difficult processing. Thus the advantages and disadvantages are just the opposite as compared to aluminum.

Other metallization systems have also been reported. These include Mo-Au, W-Au, Cr-Au, and Cr-Ag-Au multilayers and Al-Si or Al-Cu alloys.<sup>22–25</sup> Each of these combinations shows some advantages, but processing difficulties and other problems indicate that no one system satisfies all requirements. In general, the more active the metal, the easier the processing but the more likelihood of corrosion in plastic and nonhermetic packages. One of the problems associated with any nonreactive metal such as platinum, is that its high melting and boiling points require that e.b. evaporation or sputtering be used for the deposition. In either case ionizing radiation is produced and can adversely affect device parameters. Also, these processes are more difficult to operate and control under production conditions.

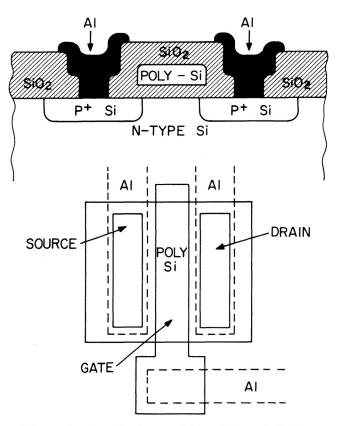

A recent development in the fabrication of gates for MOS devices is the use of a high temperature metal such as molybdenum.<sup>26</sup> Its high melting point and relatively ease of etching allows subsequent high temperature processing such as diffusion and dielectric deposition. It is therefore possible to fabricate self-aligned gate MOS transistors with dielectric passivation over the gate. The same concept has been followed in the fabrication of silicon-gate MOS transistors.<sup>27</sup> The use of silicon as a gate and interconnection material provides additional advantages in that it can be doped for low resistance applications or left undoped, it can be oxidized and it is very compatible with the Si-SiO<sub>2</sub> system. A silicon-gate structure is shown in Figure 6.

### Assembly and Encapsulation

Once the semiconductor device or circuit is fabricated and diced, contacts must be made from the device pad areas to leads going to the outside world and it must then be suitably encapsulated. Miller has presented two good reviews on the subject of "chip-joining techniques" which are the assembly procedures used to mount and connect to devices in chip form.<sup>28–29</sup> He divides these chip-joining schemes into: (a) back-joined configurations [wire bonding <sup>30</sup> and imbedded devices <sup>31</sup>], (b) flip-chip procedures [controlled-collapse,<sup>25</sup> nonmolten pads,<sup>32</sup> and spider bond <sup>33</sup>], and (c) beam leads.<sup>20</sup> It is obvious that device reliability is going to depend on effects on electrical characteristics due to the application of the various metals involved in the schemes, as well as on changes in the contact characteristics of these systems. For purposes of this discussion, the main concern will be the ability of

Figure 6—Cross-Section and Top View of Si-Gate Transistor.

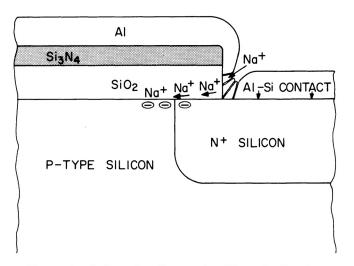

the metal in the contact area to withstand corrosion and to prevent ions from migrating into the passivating dielectric layer. The latter possibility is shown in Figure 7. In the example shown, the Si<sub>a</sub>N<sub>4</sub> layer does not cover the edge of the oxide cut. Thus, sodium can, by penetrating the aluminum, migrate into the oxide region over the junction. Obviously a metal such as platinum, which masks against sodium, is desirable as has been found in the Ti-Pt-Au beam lead system.<sup>21</sup> The degree to which a metal will mask against this migration will determine the amount and nature of masking required by the underlying dielectric film.

Three general types of packages have been used for semiconductor device encapsulation. These are metal, ceramic and plastic. In turn, many types of each have been used, depending on the requirement. Discussions of the various packaging concepts for semiconductor devices are available.<sup>34–38</sup>

In all cases, the possible interactions between the packaging materials and the various parts of the device structure, e.g. dielectric films, metallization, etc, and the subsequent degradation of electrical characteristics have been important aspects in determining the usefulness of any given package. At the same time, however, the fabrication cost and complexity also have been important factors in selecting a package.

For a number of years, the package used to encapsulate transistors and diodes was the metal can. It could be hermetically sealed and thus provided no difficulties in regards to interaction with the device structure. In fact, if it could still be used with integrated circuits, the complex dielectric passivation schemes discussed earlier would not be necessary. Several factors, however, led to the introduction of ceramic hermetic packages and plastic encapsulation. For one, the complexity of the circuits required many leads—considerably more than twelve which was possible with the metal can. Also, automated assembly techniques and the associated low cost were not compatible with the conventional TO-5 or TO-18 header assemblies.

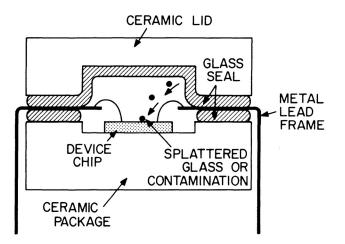

Various types of ceramic packages have thus been introduced which use a variety of lead configurations and sealing methods. Materials used for sealing can have a considerable effect on device properties and reliability. These sealing materials include metals, glasses and plastics. The glasses which can provide the best seals and are easy to work with are also the hardest to control and can have very adverse effects on device properties. Difficulties that have been encountered with glass seals are: (a) device contamination due to impurities vaporizing from the glass during sealing, (b) splattering of glass on the device during sealing, (c) attack of the device metallization or the glass seal itself by moisture, and (d) reduction of the glass components resulting in lead shorts. A cross-section of a typical ceramic structure with a glass seal is shown in Figure 8, and possible splattering of the glass due to improper processing is indicated.

Plastic packages meet the requirements involving low cost and automatic assembly. Unfortunately most plastics are not completely hermetic and the formulations include chemical species detrimental to device reliability. Even so, more and more plastic encapsulated devices are being fabricated and ways to solve the above problems are being worked out. A very good review of plastics for semiconductor devices is given by Licari.<sup>39</sup> In addition, other papers have been written on the subject of device reliability in plastic packages.<sup>40-41</sup>

Two common types of plastics have been used for device encapsulation. These are epoxies and silicones. The epoxies tend to be less susceptible to moisture penetration but are generally not as pure as silicones. The latter are more easily applied by

Figure 7—Sodium Ion Penetration Through Aluminum at Oxide Edge of Semiconductor Device With no Overlap of Silicon Nitride Layer in Contact Cut Region.

Figure 8—Example of Possible Glass Splattering or Contamination From Sealing Glass in Ceramic Package.

transfer-molding techniques which lend themselves to automatic packaging. Other plastics used to a lesser extent have been phenolics and polyesters. As mentioned above, the various components that have to be added to the plastic for required physical and other properties can adversely affect device performance and reliability. An informative discussion of these effects is presented by Olberg.<sup>40</sup>

Often used under the outer plastic packages are so-called "barrier" or "junction" organic coatings. These are of particular importance because of the ability of these films to protect the device against the less-pure outer package. Barrier coatings, applied over the metallized chip by dipping, spraying, eye-dropper, etc, are for the most part high-purity silicones. In addition, recent work has been devoted to the use of "Parylene" polymer films for the protection of device circuits against moisture and other contaminants.<sup>42</sup>

# **Chip** Protection

The above discussions indicate two important failure modes for devices encapsulated in a nonhermetic material such as plastic or subjected to contamination during high temperature sealing in ceramic packages. One is the migration of impurity ions into the passivating dielectric over the active device region, which causes degradation of device characteristics. This failure mode can be minimized by the use of a dense dielectric such as silicon nitride over the surface and contact cut edges of passivating thermal oxide.

The second major failure mechanism involves the metallization system—usually aluminum. The metal may fail due to mechanical damage during assembly, due to corrosion by the action of moisture and/or components in the packaging material or due to electromigration at high current densities. In addition, impurity ions may migrate through the contact pad areas if the oxide cuts have not been overlapped with the dense dielectric. These and other failure mechanisms involving the metallized circuit have led to the concept of chip protection. A relatively thick  $(1-2 \mu)$  dielectric film is deposited over the entire chip after metallization, and openings are then etched for the contacts. Methods of deposition have included sedimentation.<sup>43-44</sup> sputtering.<sup>12-16</sup> vapor deposition <sup>45-47</sup> and other such as evaporation.<sup>16</sup> and spin-on techniques.<sup>48</sup> Dielectrics that have been used are silicon dioxide, Pb-Zn-B and other sedimented glasses, phosphosilicate, borosilicate, and aluminosilicate glass and aluminum oxide. Silicon nitride has not yet found much use for this application due to the higher temperature required for its deposition and because thicker films tend to craze.

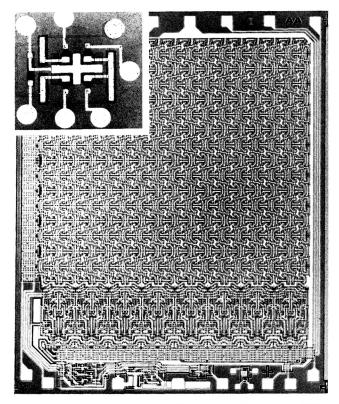

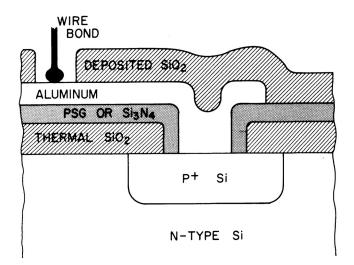

The most commonly used chip protection scheme involves the use of SiO<sub>2</sub> or P<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> deposited by the reaction of SiH<sub>1</sub> (and PH<sub>n</sub>) with  $O_{2.}^{4.5-17}$  A typical structure is shown in Figure 9. The chip protection dielectric, especially the phosphosilicate glass. can provide mechanical protection, corrosion protection and mask against ionic impurities. The one problem area is in the open bonding pad area, especially if the metal is aluminum and the package is plastic. Proposals have been made to deposit other metals such as gold in the pad, as well as to use varnishes and other plastics as barriers.

Mention should be made of aluminum oxide as a chip protection dielectric. It was originally proposed to be deposited by the vapor deposition technique<sup>47</sup> but more recently selective anodization has been reported.<sup>49-50</sup> In the latter case, aluminum is deposited over the entire circuit, a thick anodic Al<sub>2</sub>O<sub>3</sub> coating is prepared in the field regions, and the resulting defined aluminum interconnections are protected by a barrier-type anodization.

Another interesting method for depositing silicon oxides or other

Figure 9—Typical Chip Protection Scheme of Semiconductor Device Structure. Note Edge-Sealed Contact Cut and Deposited Oxide Over Entire Structure. Aluminum Bonding Pad Area is Expoesd, However.

dielectrics over the metallized device is a "spin-on" technique.  $^{48}$  In this case, the oxide if formed by the low temperature decomposition of an organic compound deposited from solution by the conventional spin-on process normally associated with photomasking technology.

### Conclusions

Approaches to providing reliable semiconductor devices in non-hermetic packages has been reviewed and several conclusions are evident. First, the thermal silicon dioxide which is required for stable and controllable device characteristics must be protected by an outer, dense dielectric. Fortunately, both phosphosilicate glass and silicon nitride are available for this purpose, and these are being used successfully.

The second conclusion that may be drawn is that the metallization is subject to mechanical damage during fabrication as well as chemical attack by the packaging materials and moisture. The latter is especially true if the metal is a reactive one such as aluminum. Ways of minimizing this attack include improving the purity and processing of the sealing material used for ceramic packages and providing high purity plastic packages with low permability to moisture. Also, additional benefits may be obtained by the use of organic barrier coatings between the outer package and the device.

The most important consideration, however, will be the selec-tion of a suitable chip protection dielectric film. This is de-posited over the metallized circuit by one of several possible methods and may be one of a variety of compounds. It must have the ability to provide mechanical protection of the metallization during assembly, to protect the metal against corrosion or other chemical attack due to the packaging material and environment and to offer some masking against ionic contamination. A secondary problem of chip protection is the protection of the binding pad areas and lead wire material against corrosion. This may be accomplished by the choice of metal and possibly the additional organic coatings.

In summary, device reliability of the future will depend in part on the best processing and control techniques of the passivating dielectric over the active device, the proper choice of the metallization system and the use of the highest purity, most moisture resistant packaging material. The best insurance, however, for the ultimate in device stability will be an optimum chip protection system which protects the semiconductor circuit from the package and any other form of mechanical or chemical attack.

# References

- 1. Horeni, J. A., "Method of Manufacturing Semiconductor De-vices," U. S. Patent No 3 025 589, March 20, 1962 and No 3 064 167, Nov. 13, 1962. Deal, B. E., "Measurement and Control of Dielectric Film

- Properties During Semiconductor Device Processing," ASTM/ NBS Symposium on Silicon Device Processing, Gaithersburg, Md., June 2-3, 1970. Published in Conference Proceedings. Gray, P. V., "The Silicon-Silicon Dioxide System," Proc.

- 3.

- Gray, P. V., "The Silicon-Silicon Dioxide System," *Proc. IEEE*, vol 57, Sept. 1969, pp 1543-1551. Szedon, J. R. and Handy, R. M., "Characterization, Control and Use of Dielectric Charge Effects in Silicon Technology," 4

- J. Vac. Sci. Technol., vol 6, Jan. 1969, pp 1-12. Schlegel, E. S., "A Bibliography of Metal-Insulator-Semi-conductor Studies," *IEEE Trans. Electron Devices*, vol ED-14, Nov. 1967, pp 728-749; vol ED-15, Dec. 1968, pp 951-954. 5.

- 6. Goetzberger, A. and Sze, S. M., "Metal-Insulator-Semi-conductor (MIS) Physics," in Applied Solid State Science, New York, Academic Press, 1969. Grove, A. S., Physics and Technology of Semiconductor De-

- 7. vices, New York, Wiley & Sons, 1967.

- Kerr, D. R., Logan, J. S., Burkhardt, P. J., and Pliskin, W. A., 8. "Stabilization of SiO<sub>2</sub> Passivation Layers With P<sub>2</sub>O<sub>5</sub>" IBM J. Res. Develop., vol 8, Sept. 1964, pp 376-384. Snow, E. H. and Deal, B. E., "Polarization Phenomena and

- Other Properties of Phosphosilicate Glass Films on Silicon,'

- J. Electrochem. Soc., vol 113, March 1966, pp 263-269. Balk, P. and Eldridge, J. M., "Phosphosilicate Glass Stabiliza-tion of FET Devices," Proc. IEEE, vol 57, Sept. 1969, pp 10. 1558-1563

- Chu, T. L., Szedon, J. R. and Lee, C. H., "The Preparation and C-V Characteristics of Si-Si<sub>2</sub>N<sub>4</sub> and Si-SiO<sub>2</sub>-SI<sub>2</sub>N<sub>4</sub> Struc-tures," *Solid-State Electronics*, vol 10, Oct. 1967, pp 897-905.

Greger, L. V., "Study of Silicon Nitride as a Dielectric Ma-terial for Microelectronic Applications," Final Report, Cont. No AF 33(615)-5386, Wright Patterson AFB, Ohio, Sept. 1967.

- 13. Electrochemical Society, Joint Session (Dielectrics and Insulation and Electronics-Semiconductor Divisions), on Silicon

- Nitride, Oct. 12-13, 1966, Philadelphia, Pa. Tung, S. K. and Caffrey, R. E., "The Deposition and Physical Properties of Aluminosilicate Films," J. Electrochem. Soc., 14.

- Properties of Aluminosilicate Films," J. Electrochem. Soc., vol 107, Jan. 1970, pp 91-95.

15. Norris, P. E. and Zaininger, K. H., "Improved Insulation for IC Technology," Final Report, Cont. No N00039-69-C-0540, Dept. of Navy, Washington, D.C., Feb. 1970.

16. Plishkin, W. A., Kerr, D. R. and Perri, J. A., "Thin Glass Films," in *Physics of Thin Films*, vol 4, New York, Academic Press, 1967.

17. MacKenna, F. L. "Chamically V. D. States".

- MacKenna, E. L., "Chemically Vapor Deposited Dielectrics-Properties and Deposition Methods," Semiconductor/IC Semiconductor/IC Processing and Production Conference, Feb. 9-11, 1971, Anaheim, Calif., To be Published in Conference Proceedings.

- Schnable, G. L. and Keen, R. S., "Aluminum Metallization-Advantages and Limitations for Integrated Circuit Applica-18 tions," Proc. IEEE, vol 57, Sept. 1969, pp 1570-1580. Lane, C. H., "Aluminum Metallization and Contacts for

- 19. Integrated Circuits," AIME Met. Trans., vol 1, March 1970, pp 713-724.

- Lepselter, M. P., "Beam Lead Technology," Bell System Tech. J., vol XLV, Feb. 1966, pp 233-253. 20.

- Schneer, G. H., Van Gelder, W., Hauser, V. E. and Schmidt, P., "A Metal-Insulator—Silicon Junction Seal," *IEEE Trans. Electron Devices*, vol ED-15, May 1968, pp 290-293.

Donovan, R. P., "Integrated Silicon Device Technology; XIII,

- Intraconnections and Isolation," RTI Report No ASD-TDR-63-316, May 1967.

- Blech, I., Sello, H. and Gregor, L. V., "Thin Films in Inte-grated Circuits," in *Handbook of Thin Film Technology*, L. Maissel and R. Glang, Editors; New York, McGraw-Hill, 1970

- 24. Ames, I., d'Henrle, F. M. and Horstmann, R. E., "Reduction of Electromigration in Aluminum Films by Copper Doping,'

- *IBM J. Res. Develop.*, vol 14, July 1970, pp 461-463. Totta, P. A. and Sopher, R. P., SLT Device Metallurgy and its Monolithic Extension," *IBM J. Res. Develop.*, vol 13, 25. May 1969, pp 226-238.

- Brown, D. M., Engeler, W. E., Garfinkel, M. and Gray, P., "Self-Registered Molybdenum—Gate MOSFET," J. Electro-

- Sein-Registereu Moryoleunin-Gate MOSPET, J. Electro-chem. Soc., vol 115, Aug. 1968, pp 874-876.

Faggin, F. and Klein, T., "Silicon Gate Technology," Solid State Electronics, vol 13, Aug., 1970, pp 1125-1144.

Miller, L. F., "A Critique of Chip Joining Techniques," Solid State Technol. vol 13, Aug., 1970, pp 576(2)

- State Technol., vol 13, April 1970, pp 50-62. Miller, L. F., "A Survey of Chip Joining Techniques." Proc.

- 29 IEEE Electronics Components Conference, April 30-May 2, 1969, pp. 60-76.

- Koshinz, E. F., "Semiconductor: Wire Bonding and Face Bonding Considerations and Comparisons," Proc. SAE Micro-30. electronic Packaging Conference, Nov. 1968.

- 31.

- 32.

- Electronic News, Feb. 19, 1968. Matcovich, T. J., "Direct Bonding Processes and Hybrid Cir-cuit Applications," *Elect. Pack. Prod.*, Nov. 1967, p 101. Helda, R., "Spider Bonding Technique with I.C.s," Proc. Int. Elec. Circuit Packaging Symposium, Wescon, Aug. 20-21, 33. 1969

- 34. Harper, C. A., Handbook of Electronic Packaging, New York, McGraw-Hill, 1969.

- Harper, C. A., Handbook of Materials and Processes for 35. Electronics, New York, McGraw-Hill, 1970.

- 36. Fehr, G. K., "Microcircuit Packaging and Assembly-State of The Art," Solid State Technol., vol 13, Aug. 1970, pp 41-47.

- 37. Bower, F. H., "Hermetic Sealing of Integrated Circuit Pack-

- ages," Solid State Technol., vol 13, Aug. 1970, pp 67-70, 75. 38.

- Licari, J. J., Plastic Coatings for Electronics, New York, McGraw-Hill, 1970.

Olberg, R. C., "The Effects of Epoxy Encapsulant Composi-tion on Semiconductor Device Stability," J. Electrochem.

- Soc., vol 118, Jan. 1971, pp 129-133. Tamburrino, A. L. and Kapfer, V. C., "Failure Mechanisms in Plastic Encapsulated Microcircuits," Contract No RADC-TR-41.

- 69-111, Rome Air Dev. Center, May 1969. Lee, S. M., Licari, J. V. and Litant, I., "Electrical Reliability of Parylene Films for Device Passivation," *AIME Met. Trans.*, 42. vol 1, March 1970, pp 701-711.

- Pilskin, W. A. and Conrad, E. E., "Techniques for Obtaining Uniform Thin Glass Films on Substrates," *Electrochem. Technol.*, vol 1, July-Aug. 1964, pp 196-200. 4.3

- 44. Dumesnil, M. and Hewitt, R., "Some Recent Developments in Fused Glass Films on Semiconductor Devices," J. Electro*chem. Soc.*, vol 117, Jan. 1970, pp 100-106. 45. Mowakowski, M., "Development of Glass Passivation Method

for Semiconductor Devices for Saturn System," Final Report, Contract No NAS8-18048, NASA Aug. 1968.

- Schlacter, M. M. et al, "Advantages of Vapor-Plated Phospho-46. silicate Films in Large-Scale Integrated Circuit Arrays," IEEE Trans. Electron Devices, vol ED-17, Dec. 1970, pp 1077-1083.

- Flashen, S. S., Evitts, E. C. and Black, J. R., "Large Area Semiconductor Surface Passivation Production Refinement Program," AD439885, Jan. 1964.

- Technical Data From the Emulsitone Co., Livingston, New 48. Tersev.

- 49. Tsunemitsu, H. and Shiba, H., "A Planar Multi-Layer Inter-connection," Paper 18.4 presented at the IEEE International Electron Devices Meeting, Washington, D.C., Oct. 29-31, 1969.

- 50. McMahon, W. R., "Anodic Processing of Interconnect Systems for Integrated Circuits," Paper No 7.1 presented at the IEEE Intrenational Electron Devices Meeting, Washington, D.C., Oct. 28-30, 1970.

# THE HIGH-REL PLASTIC PACKAGE VERSUS TRANSFER MOLDED ENCAPSULATION

# by

RANDALL D. CLARK AND PAUL E. SMITH U.S. Electronic Service 71C38EI-22

#### Introduction

The advancement of the state-of-the art in electronic packaging has increased the confidence level in plastic packaging in general and has led to the development of a high reliability hermetic plastic package. The metallized plastic package system developed by U.S. Electronic Services has incorporated the desirable features of ceramic and metal packages with the economic advantages of plastic encapsulation. The result is a reliable packaging system at one third, to one half the cost of ceramic packaging and comparable to a transfer molded system.

#### **Process Description**

The High-Rel Plastic Package consists of a metallized base, a plastic lid, and an adhesive for lid and die attach. The specific properties of the plastic are defined in Table I. Using a proprietary metallization technique on the base, 100 microinches of gold is selectively deposited on the metallized pattern for internal wire bonding purposes. The lead frame is copper nickel alloy with tin plating. The patent pending process includes packages ranging from the 14 lead dual-in-line through 48 lead designs as standard product lines. Using the same basic techniques custom packages are made which cover special requirements for more leads and different package configurations.

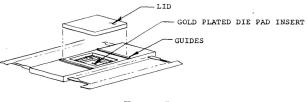

The die attach method utilized is either a gold eutectic system with a gold plated Kovar die pad located in the cavity or by an adhesive, conductive or non-conductive, directly to the Kovar die tab. Figure 1.

The procedure for die attachment is to first clean and dry package thoroughly, using standard ultrasonic cleaning pro-cedures. Using the adhesive die attach a drop of Epotek adhesive is dispensed by hand or automatically  $\frac{1}{3}$  the size of the die onto the Kovar die pad. The die is then placed into position on the Kovar recess using standard die handling techniques. A light pressure is then applied to flow the adhesive and the package is next placed into an air circulating over at 125°C for 45 minutes. If the

### TABLE I

| Molding Compounds<br>Properties | Uses #001<br>Phenolic | Uses #059<br>Epoxy    |

|---------------------------------|-----------------------|-----------------------|

| Thermal Expansion (°C)          | $14.2 	imes 10^{-6}$  | $12.2 \times 10^{-6}$ |

| Thermal Conductivity            |                       |                       |

| $(cal/sec/cm^2/^{\circ}c/cm)$   | $2.6	imes10^{-3}$     | $1.6	imes10^{-3}$     |

| Max Operating Temp (°C)         | 204                   | 220                   |

| Water Absorption (48 hrs)       | .09%                  | .20%                  |

| Dielectric Strength (Volt/mil)  | 370                   | 380                   |

| Flexural Strength (psi)         | 15,000                | 17,500                |

| Tensile Strength (psi)          | 9,250                 | 10,500                |

Figure 1

gold eutectic die attach method is used, the die is eutectically mounted utilizing standard techniques and then while the pad is still hot it is placed into the package cavity where the adhesive for the pad has already been placed. Light pressure is applied to wet the back of the gold plated die pad. The package is then placed into an air circulating oven and cured for 1 hour at 175°C

The technique used on the hermetic plastic package for the external metal leads is not the traditional lead frame approach incorporated in the transfer molded process. From Figure 2, the difference is quite obvious. The hermetic plastic external leads do not penetrate into the die cavity but terminate at the inside edge of the base. The metallized paths connecting the external leads by a solid conductive via (not through plated holes) continue into the cavity. The metallized paths are next sealed by a pro-prietary process leaving only the art work tips and die cavity exposed.

This feature of not having the lead frame penetrate into the die cavity is one of the key distinguishing differences of the High-Rel hermetic plastic package versus the solid transfer molded package. This feature is also a key factor in the greater reliability inherent in the High-Rel plastic package.

The base plastic with the die attached is now ready for internal bonding utilizing any of the accepted bonding procedures used by the microelectronic industry. Upon completion of the visual pre cap inspections required for high reliability applications the package is ready for lid sealing. The lid sealing operation is a straight forward process in which the adhesive is dispensed on the basic plastic's seal area and the lid placed on the adhesive. The package seal is then cured and the completed device is ready for final hermetic and electrical tests.

#### Why Hermetic Plastic?

The advent of mass producing microelectronics via transfer molding has encountered major problems which continue to plague the "non-hermetic" package today. Two of these problem areas

| adhesive seal <sub>7</sub> | lid 7 buried metallized path |  |

|----------------------------|------------------------------|--|

|                            |                              |  |

| die cavity_/               | metal lead                   |  |

| Figure 2                   |                              |  |