## United States Patent [19]

Mundt et al.

#### [54] PROCESS FOR FORMING RETROGRADE DOPANT DISTRIBUTIONS UTILIZING SIMULTANEOUS OUTDIFFUSION OF DOPANTS

- [75] Inventors: Randall S. Mundt; Ray E. Wyatt, both of Colorado Springs, Colo.

- [73] Assignee: NCR Corporation, Dayton, Ohio

- [21] Appl. No.: 677,636

- [22] Filed: Dec. 3, 1984

- [51] Int. Cl.<sup>4</sup> ..... H01L 21/20; H01L 21/225

- [58] Field of Search ...... 29/571, 576 B, 576 W; 148/187, 191, 175; 156/643; 357/42, 50

#### [56]

#### References Cited U.S. PATENT DOCUMENTS

| 3,298,880 | 1/1967  | Takagi et al 148/191 |

|-----------|---------|----------------------|

| 3,635,773 | 1/1972  | Thire 148/191        |

| 3,767,487 | 10/1973 | Steinmaier 148/191   |

| 3,921,283 | 11/1975 | Shappir 29/571       |

| 4,032,372 | 6/1977  | Vora 148/191 X       |

| 4,411,058 | 10/1983 | Chen 29/571          |

| 4,463,493 | 8/1984  | Momose 29/571 X      |

#### [11] Patent Number: 4,578,128

#### [45] Date of Patent: Mar. 25, 1986

| 4,466,171 | 8/1984 | Jochems 29/571 X |

|-----------|--------|------------------|

| 4,516,316 | 5/1985 | Haskell 29/576 B |

| 4,535,529 | 8/1985 | Jochems 29/571   |

#### OTHER PUBLICATIONS

Chen, "Quadruple-Well CMOS for VLSI Technology", IEEE Transactions on Electron Devices, vol. ED-31, No. 7, Jul. 1984, pp. 910-919.

Manoliu et al., "High-Density and Reduced Latchup Susceptibility CMOS Technology for VLIS", IEEE Electron Device Letters, vol. EDL-4, No. 7, Jul. 1983, pp. 233-235.

Primary Examiner-William G. Saba

4

Attorney, Agent, or Firm-Wilbert Hawk, Jr.; Casimer K. Salys

#### [57] ABSTRACT

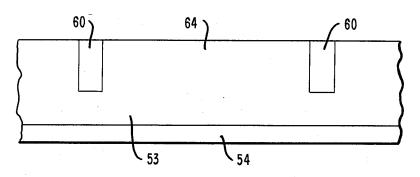

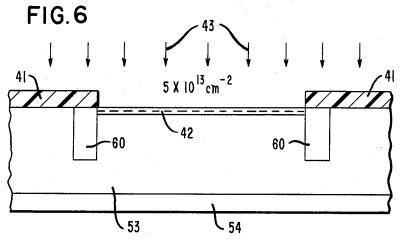

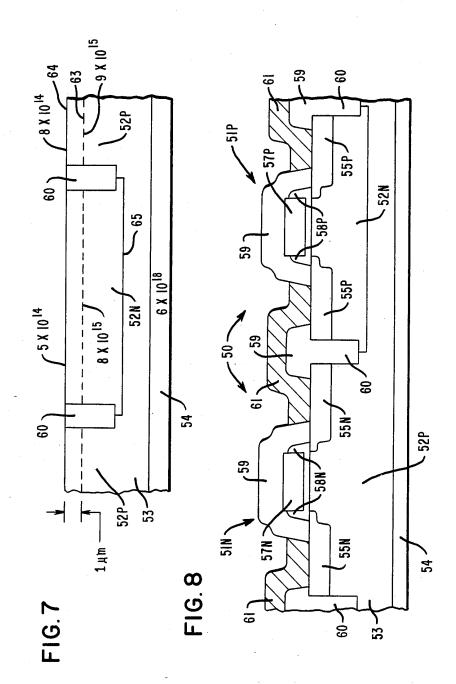

A retrograde dopant distribution is provided in a semiconductor substrate by the combined use of indiffusion and surface outdiffusion and without the use of high energy implants or buried epitaxial layers. The retrograde dopant distribution is provided both in the n-well and the p-well regions to a depth sufficient to accommodate deep trench isolation structures.

#### 8 Claims, 8 Drawing Figures

**IP Bridge Exhibit 2014**

Find authenticated court documents without watermarks at docketalarm.com.

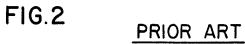

FIG.I

**DOCKET A L A R M** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

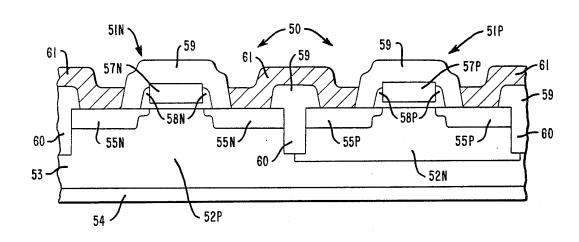

FIG.4

DOCKET A L A R M Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

KF Α ĸ Find authenticated court documents without watermarks at docketalarm.com.

#### PROCESS FOR FORMING RETROGRADE DOPANT DISTRIBUTIONS UTILIZING SIMULTANEOUS OUTDIFFUSION OF DOPANTS 5

1

#### BACKGROUND OF THE INVENTION

The present invention relates to a simplified process for forming retrograde dopant distributions in integrated circuit structures, that is, dopant distributions which increase in a vertically inward or downward direction from the surface of a layer or body such as a semiconductor substrate. As used here in reference to the present invention, the word "retrograde" also connotes a controlled dopant profile.

The potential advantages of a retrograde dopant distribution in semiconductor substrates are several, particularly in CMOS integrated circuit structures. The advantages are well-known and include the potential for tibility to latchup. It is believed there are available basically three approaches for forming a retrograde dopant profile. The techniques, namely, high energy implants (greater than about 200 keV), buried epitaxial layers, tion.

An example of retrograde processing techniques is disclosed in Manoliu et al, "High-Density and Reduced Latchup Susceptibility of CMOS Technology for VLSI", IEEE Electron Device Letters, Vol. EDL-4, No. 30 7, July, 1983, pp. 233-235. Manoliu et al. uses the combination of a first implant in a doped substrate and a later implant in an undoped epitaxial layer. The well formation process is concluded with an anneal cycle. retrograde p-well structure reportedly increases circuit density by reducing the minimum  $n_+ - p^+$  spacing while decreasing latchup susceptibility.

Chen, "Quadruple-Well CMOS for VLSI Technology", IEEE Transactions on Electron Devices, Vol. ED- 40 31, No. 7, July 1984, pp. 910-919, describes a process for forming a retrograde, quadruple-well CMOS structure. The n-well and p-well retrograde doping profiles each require multiple doping steps. Essentially, the structure is a two-well structure in which deep n-type 45 dopant concentration gradient is used to prevent short and p-type wells are separated by respective shallow n-type and p-type wells or channel stops. The shallow wells are implanted through a peripheral field oxide during the deep well implantation. Overall, the Chen process involves, first, forming deep-well windows in a 50 planar field oxide. The p-well region is masked and a high energy phosphorus implant at 290 keV is done in the presence of the mask to define the deep n-well and the adjacent shallow n-type channel stop under the oxide. The n-well is then counter-doped with boron for 55 used in some CMOS structures. The adjacent n-well 17 threshold voltage adjustment.

After the two-implant-step formation of the retrograde n-well, the n-well is masked and a multiple doping sequence is applied to provide the p-well retrograde profile. Initially, a 120 keV boron implant is used to 60 form a relatively deep p-well, and the adjacent shallow p-type channel stop under the oxide. Phosphorus counterdoping adjusts the n-channel threshold voltage. Then, a deep, high energy 340 keV boron implant provides the deep retrograde p-well profile which is used 65 cuits. to eliminate latchup. The counter-doping aspects of the process i.e., the combination of high energy implants and opposite conductivity low energy counter-doping,

DOCKE

are also disclosed in Chen, U.S. Pat. No. 4,411,058, issued Oct. 25, 1983.

The outdiffusion of semiconductor dopants from the surfaces of silicon, mentioned above, is another wellknown phenomenon, one that in the past has produced undesirable results. For example, outdiffusion from the front and rear major surfaces of semiconductor wafers leads to both macro-outdoping and micro-autodoping. Various process techniques are used to eliminate or 10 decrease the effects of outdiffusion, including two-step processing using process interruption and/or high and low temperatures, and sealing of wafer surfaces with a mask such as silicon, silicon dioxide or silicon nitride. Recently, outdiffusion has been used advantageously

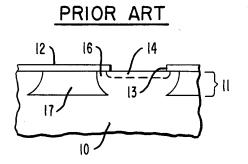

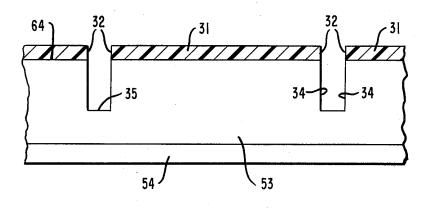

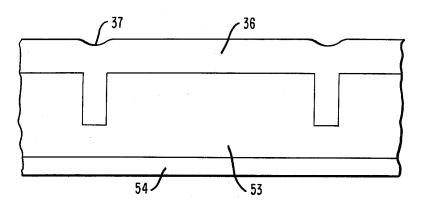

to provide a retrograde dopant distribution, but the process techniques for implementing the outdiffusioncaused retrograde dopant distribution typically are complex. For example, Steinmaier, U.S. Pat. No. 3,767,487 relates to the use of outdiffusion techniques to increased device packing density and decreased suscep- 20 form selected, isolated retrograde surface-adjacent regions which are used as isolation wells for MOS or bi-polar devices. Referring to FIG. 1, the MOS integrated circuit process disclosed in the Steinmaier '487 patent involves forming a five-micron thick n-type epiand outdiffusion, can be used separately or in combina- 25 taxial layer 11 on a p-type semiconductor 10; forming a thermal oxide masking layer 12 over the epitaxial laver having an aperture 13 which defines the p-well or isolation region; depositing a shallow p-well 14 in the surface of the epitaxial layer at the masked apertures using an oxidizing atmosphere to re-cover (not shown) the exposed substrate surface regions; etching the oxide mask to reexpose the epitaxial layer over part of the deposited impurity region beneath the masked windows; and outdiffusing the boron via the mask apertures The specific CMOS structure and epitaxial buried layer 35 13 in a vacuum ampul containing silicon to provide the retrograde concentration in region 14. In particular, the vertical retrograde dopant concentration in region 14, that is, the relatively low surface concentration there, provides a high breakdown voltage for the NMOS device which is subsequently formed in the p-well 14. In addition, in the surface region 16 surrounding the well 14, the mask prevents outdiffusion, thereby providing a surface region 16 of relatively high doping concentration surrounding the retrograde well 14. This horizontal circuits between the epitaxial layer 11 and the subsequently formed NMOS device.

As is evident from the above description, in regard to small geometry, high density structures, the Steinmaier '487 retrograde p-well fabrication process suffers from several disadvantages in addition to complexity. The shallow retrograde p-well 14 does not appear to be capable of providing the desirable retrograde dopant gradient along the deep isolation trenches which are is capped during the outdiffusion step and does not have a retrograde dopant concentration gradient. Furthermore, the lateral dopant concentration gradient at the periphery of the p-well 14 quite obviously limits the minimum dimension of, and spacing between, the wells. In short, the complex processing of the Steinmaier '487 patent is tailored to provide a p-well-only retrograde gradient and a lateral doping gradient that are inconsistent with small geometry, high density integrated cir-

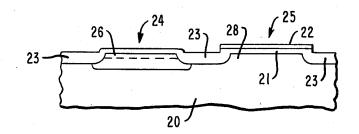

Shappir, U.S. Pat. No. 3,921,283 uses surface outdiffusion in the fabrication of dielectrically isolated MOS-FET semiconductor devices. Referring to FIG. 2, in the

Find authenticated court documents without watermarks at docketalarm.com.

## DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.