# United States Patent [19]

#### Heath et al.

[11] Patent Number:

5,038,320

[45] Date of Patent:

Aug. 6, 1991

#### [54] COMPUTER SYSTEM WITH AUTOMATIC INITIALIZATION OF PLUGGABLE OPTION CARDS

[75] Inventors: Chester A. Heath; John K. Langgood,

both of Boca Raton, Fla.; Ronald E.

Valli, Pittsburgh, Pa.

[73] Assignee: International Business Machines

Corp., Armonk, N.Y.

[21] Appl. No.: 296,387

[22] Filed: Jan. 6, 1989

## Related U.S. Application Data

[63] Continuation of Ser. No. 21,391, Mar. 13, 1987, abandoned

| [51] | Int. Cl.5      | G06F 13/00; G06F 7/04           |

|------|----------------|---------------------------------|

| [52] | U.S. Cl        |                                 |

|      | 364/944.61; 36 | 4/975.2; 364/976.4; 364/945;    |

|      | 26             | 4 /000 S. 264 /000 n. 271 /11 i |

[58] Field of Search ... 364/200 MS File, 900 MS File; 340/825.07, 825.06, 825.52, 825.06; 371/11.1, 11.2, 11.3, 66, 7

# [56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,480,914 | 11/1969 | Schlaeppi 30 | 64/200 |

|-----------|---------|--------------|--------|

| 3,510,843 | 5/1970  | Bennett 30   | 64/200 |

| 3,573,741 | 4/1971  | Gavril 30    | 64/200 |

| 3,818,447 | 6/1974  | Craft 340    | /172.5 |

| 4,003,033 | 1/1977  | O'Keefe 30   | 64/200 |

| 4,015,244 | 3/1977  | Simpson 30   | 64/200 |

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

| 0041406 | 9/1981  | European Pat. Off |

|---------|---------|-------------------|

| 0087368 | 8/1983  | European Pat. Off |

| 0121331 | 3/1984  | European Pat. Off |

| 0121381 | 10/1984 | European Pat. Off |

| 0136178 | 4/1985  | European Pat. Off |

| 0179981 | 6/1985  | European Pat. Off |

| 0171073 | 2/1986  | European Pat. Off |

| 0182044 | 5/1986  | European Pat. Off |

| 0200198 | 11/1986 | European Pat. Off |

3508648 9/1986 Fed. Rep. of Germany . 50-120935 9/1976 Japan .

(List continued on next page.)

#### OTHER PUBLICATIONS

IBM TDB vol. 20, No. 7, Dec. 1977, Input/Output Device Address Recognition Mechanism.

(List continued on next page.)

Primary Examiner—Gareth D. Shaw Assistant Examiner—Paul Kulik Attorney, Agent, or Firm—Winfield J. Brown, Jr.; Robert Lieber

## [57] ABSTRACT

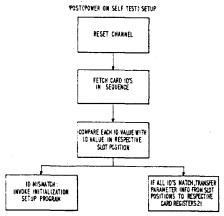

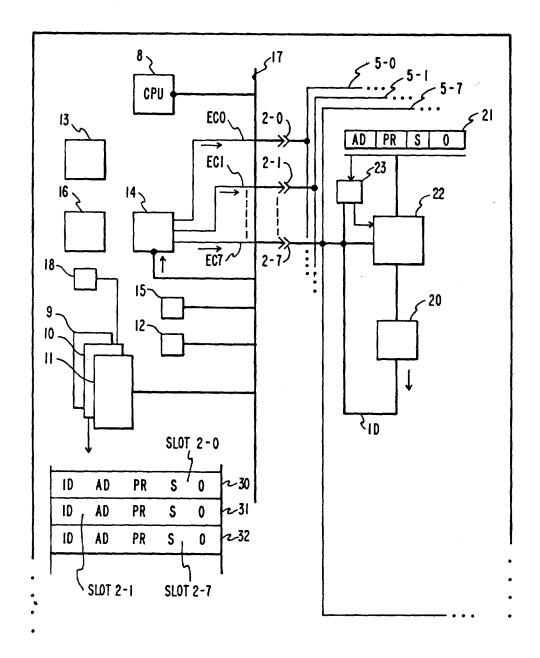

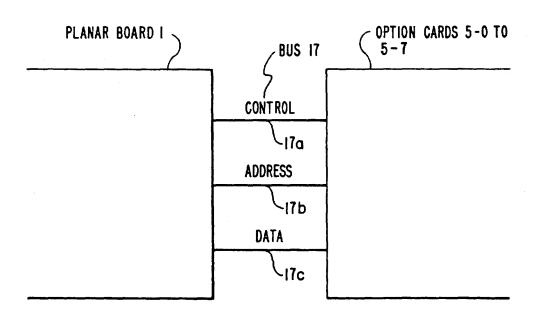

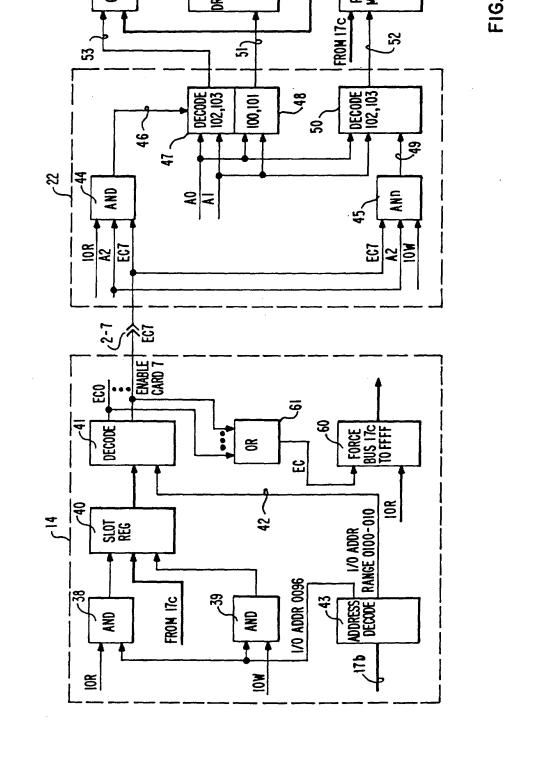

A data processing system includes a planar board having a central processing unit (CPU), a main memory unit, and input/output (I/O) sockets or slots, each adapted to receive a selected one of a plurality of different and/or similar option cards. each card contains (or is connected to) and controls a respective peripheral device; and each card is pre-wired with an ID value corresponding to its card type. Software programmable option registers on each card store parameters such as designated default (or alternate) address information, priority levels, and other system resource parameters. A setup routine, during initial power-on, retrieves and stores the appropriate parameters in the I/O cards and also in slot positions in main memory, one position being assigned to each slot on the board. Each slot position is adapted to hold the parameters associated with the card inserted in its respective slot and the card ID value. That portion of main memory containing the slot positions is adapted to maintain the parameter and ID information by means of battery power when system power fails or is disconnected, i.e., a nonvolatile memory portion. Subsequent power-on routines are simplified by merely transferring parameters from the table to the card option registers if the status of all the slots has not changed since the last power-down, system reset, or channel reset.

## 18 Claims, 7 Drawing Sheets

# Page 2

| U.S. PATE                               | ENT DOCUMENTS                         | 55-56235 4/1980 Japan .                                            |

|-----------------------------------------|---------------------------------------|--------------------------------------------------------------------|

| 4,025,903 5/1977                        | Kaufman 364/200                       | 56-46384 10/1982 Japan .                                           |

|                                         | Moorehead .                           | 2101370 1/1983 United Kingdom .                                    |

| , , , , , , , , , , , , , , , , , , , , |                                       | 2137382 10/1984 United Kingdom .                                   |

|                                         | Calle et al 364/200                   | 2166893 5/1986 United Kingdom .                                    |

|                                         | Fox                                   | 2175716 12/1986 United Kingdom .                                   |

|                                         | Mitchell, Jr 364/200                  | •                                                                  |

|                                         | Taddei 364/200                        |                                                                    |

| 4,191,996 3/1980                        |                                       | OTHER PUBLICATIONS                                                 |

| 4,236.207 11/1980                       | · · · · · · · · · · · · · · · · · · · |                                                                    |

|                                         | Saal 340/147 R                        | IBM TDB vol. 20, No. 8, Jan. 1978, Initial Micropro-               |

| 4,253,144 2/1981                        |                                       | · · · · · · · · · · · · · · · · · · ·                              |

| 4,254,463 3/1981                        |                                       | gram Load by Blocks Via Cycle Steal.                               |

| 4,268,901 5/1981                        |                                       | IBM TDB vol. 22, No. 2, Jul., 1979, Even/Odd Ad-                   |

| 4,293,924 10/1981                       | 2                                     | dresses to Allow Device Adapter Sharing by More                    |

| 4,303,993 12/1981                       | •                                     | Than One Processor.                                                |

|                                         | Felder 364/900                        | IBM TDB vol. 22, No. 5, Oct. 1979, Satellite Station               |

| 4,335,426 6/1982                        |                                       | Address Assignment Method.                                         |

|                                         | Neumann 340/521                       | IBM TDB vol. 22, No. 10, Mar., 1980, Automatic Mod-                |

|                                         | McVey 364/200                         | ule Detection.                                                     |

|                                         | Kaul 364/200                          | IBM TDB vol. 23, No. 8, Jan., 1981, Dynamic Device                 |

|                                         | Chisholm et al 364/200                | Address Assignment Mechanism.                                      |

| 4,400,775 8/1983                        |                                       |                                                                    |

| 4,432,049 2/1984                        |                                       | Electronic Design, Sep. 3, 1981, pp. 141-156, Several              |

|                                         | Witalka 364/200                       | Articles, "Functional Architecture Threatens Central               |

|                                         | Dummermuth 364/900                    | CPUs", etc.                                                        |

|                                         | Wunsch                                | Paper in Euromicro, Input/Output Control 6f IBM                    |

|                                         | Weymouth                              | System/370 Model 125 through Dedicated Input/Out-                  |

|                                         | Calvignac                             | put Processors, by Assmuth et al., pp. 24-40.                      |

|                                         | Ahuja                                 | Technical Disclosure Bulletin (IBM) vol. 27, No. 11                |

|                                         | Ziehm et al                           | "Automatic Domain Configuration Mechanism for a                    |

|                                         | Caprio et al                          | Multi-Device I/O Controller".                                      |

|                                         | Boudreau                              | Wescon Technical Paper Oct. 30-Nov. 2, 1984, "A                    |

|                                         | Mantellina 364/200                    | Standard Protocol for Host Computer-Peripheral In                  |

|                                         | Desai                                 | •                                                                  |

|                                         | Shah et al 364/200                    | terface Allows Upgrading to the Latest Mass Storage                |

|                                         | Crabtree et al                        | Devices".                                                          |

|                                         | Ceccon et al                          | Technical Disclosure Bulletin (IBM) vol. 27, No. 2, Jul            |

|                                         | Brahm                                 | 1984 "Input/Output Channel Address Assignmen                       |

|                                         | Vincent                               | Mechanism".                                                        |

| 4,654,857 3/1987                        |                                       | JP Abstract vol. 10, No. 256 (P-493) (23312) Sep. 2                |

| 4,660,141 4/1987                        |                                       | 1986.                                                              |

| 4,670,855 6/1987                        |                                       | JP Abstract vol. 9, No. 239 (P-391) (1962) Sep. 25                 |

| 4,701,878 10/1987                       | •                                     | 1985.                                                              |

| 4.713,834 12/1987                       |                                       | JP Abstract vol. 9, vol. 9, No. 190 (P-378) (1913) Aug             |

| 4,718,038 1/1988                        |                                       | 7, 1985.                                                           |

| 4,750,136 6/1988                        |                                       | •                                                                  |

| 4,760,553 7/1988                        |                                       | EDN Magazine vol. 26 (1981) Feb., No. 3, Boston, MA                |

| 4,787,025 11/1988                       | Cheselka 364/200                      | New Electronics 19(1986) Jul., No. 14, London, Grea                |

|                                         | Finfrock et al 364/900 X              | Britain.                                                           |

| 4,787,030 11/1988                       | Harter 364/200                        | vol. 22, No. 3, Aug. 1979, IBM Technical Disclosure                |

|                                         | Matelan 364/200                       | Bulletin, Programmable Identification for I/O Device               |

| FOREIGN PA                              | ATENT DOCUMENTS                       | J. M. McVey.<br>vol. 16, No. 1 Jun. 1973, IBM Technical Disclosur- |

| 54-24314 3/1979                         | Japan .                               | Bulletin, Program Controlled I/O Address Assignment                |

| 54-73531 6/1979                         | •                                     | L. J. Rosenberg.                                                   |

|                                         | -                                     | •                                                                  |

Aug. 6, 1991

FIG. I

FIG. 2

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.