# U.S. Patent No. 7,673,072 (072 Patent)

IPR2017-1406 (Intel) IPR2018-0375 (Dell) IPR2017-1707 (Cavium) IPR2018-0329 (Wistron)

\*All citations herein are to the IPR2017-01406 case unless otherwise noted.

#### 072 Patent: Instituted Grounds

- Erickson in view of Tanenbaum96

- 072 Patent: Claims 1, 2-8, 9, 10-14 and 15, 16-21

1. A POSA would have been motivated to combine Tanenbaum96 with Erickson

2. Erickson in view of Tanenbaum96 discloses the limitations of claims 1-21 of the 072 Patent

3. Motion to Amend 072 Patent should be denied

1. A POSA would have been motivated to combine Tanenbaum96 with Erickson

See 036 Patent, Dispute 1, slides 6-53

- 2. The combination of Erickson and Tanenbaum96 discloses the limitations of claims 1-21 of the 072 Patent

- a) The prior art discloses "dividing, by the interface device, the data into segments" (all claims)

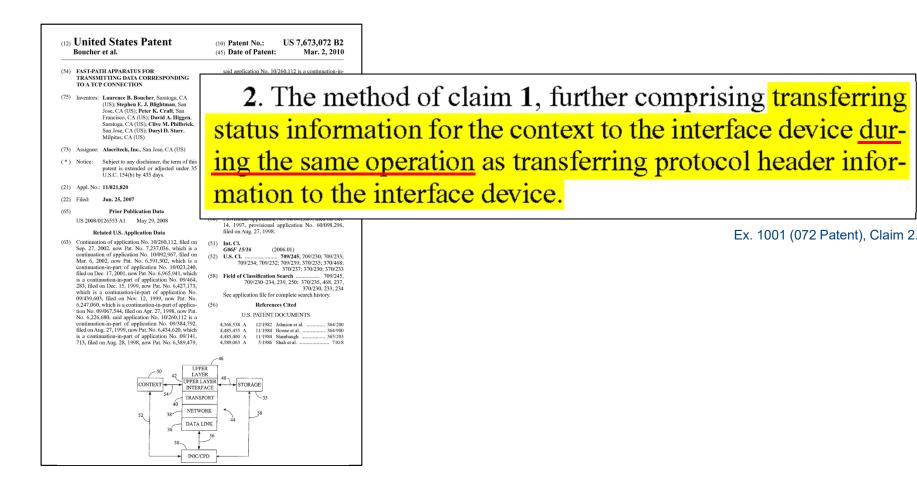

- b) The prior art discloses "transferring status information for the context to the interface device during the same operation as transferring protocol header information to the interface device" (claim 2)

- c) The prior art discloses "receiving, by the interface device, receive packets that correspond to the [context/protocol information], and updating the [context/status information] by the interface device to account for the receive packets" (claims 7, 14, 21)

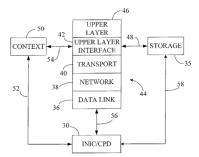

# "Dividing, by the interface device, the data into segments"

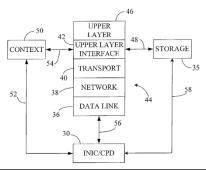

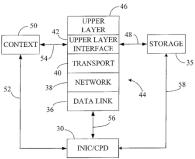

DATA LINK

INIC/CPD

1. A method comprising:

establishing, at a host computer, a transport layer connection, including creating a context that includes protocol header information for the connection;

transferring the protocol header information to an interface device;

transferring data from the network host to the interface device, after transferring the protocol header information to the interface device;

dividing, by the interface device, the data into segments; creating headers for the segments, by the interface device, from a template header containing the protocol header information; and

prepending the headers to the segments to form transmit packets.

Ex. 1001 (072 Patent), Claim 1.

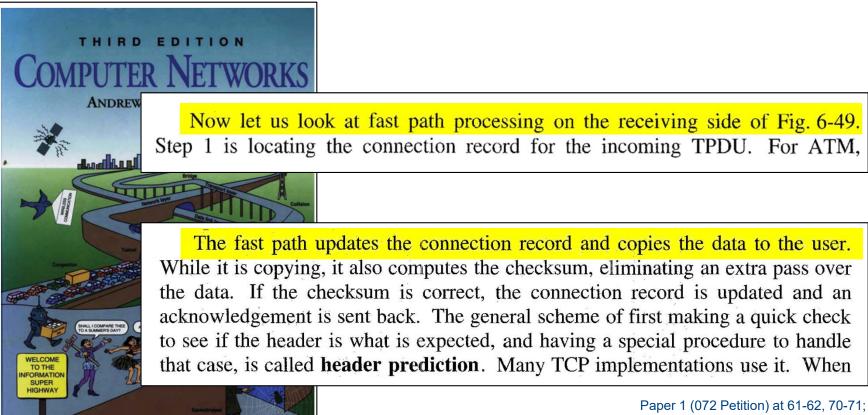

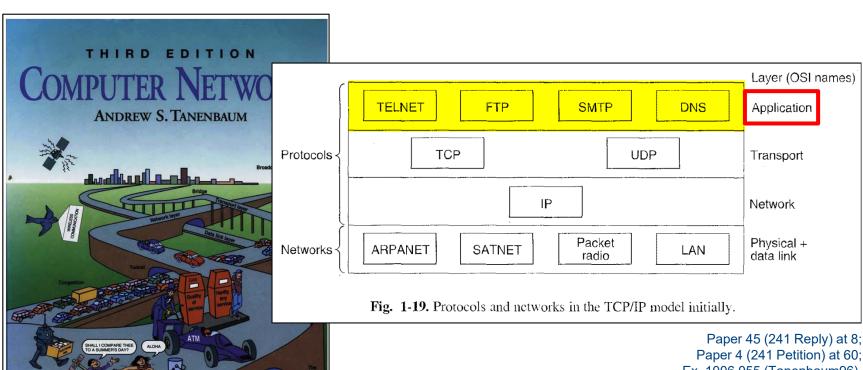

# Tanenbaum96: TCP entity divides data into segments (TCP packets)

THIRD EDITION

A TCP entity accepts user data streams from local processes, breaks them up into pieces not exceeding 64K bytes (in practice, usually about 1500 bytes), and sends each piece as a separate IP datagram. When IP datagrams containing TCP data

Paper 1 (072 Petition) at 43; Paper 46 (072 Reply) at 15; Ex. 1003.100 (072 Horst Decl.); Ex. 1006.540 (Tanenbaum96).

The sending and receiving TCP entities exchange data in the form of segments. A segment consists of a fixed 20-byte header (plus an optional part) followed by zero or more data bytes. The TCP software decides how big segments

Paper 1 (072 Petition) at 43; Paper 46 (072 Reply) at 15; Ex. 1003.100 (072 Horst Decl.); Ex. 1006.543 (Tanenbaum96).

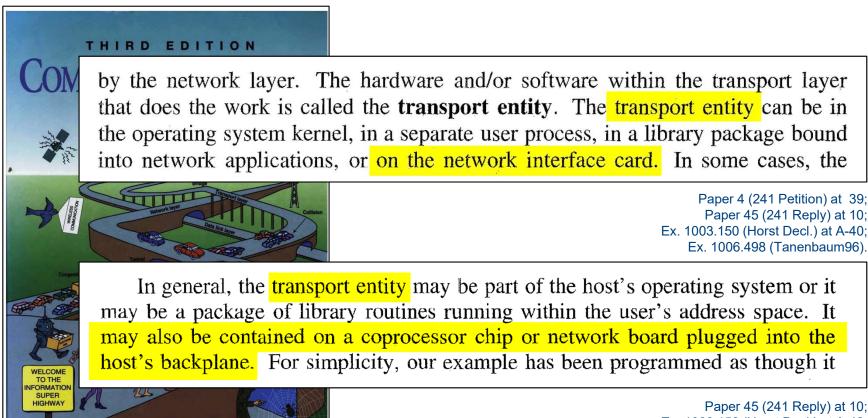

## Tanenbaum96: Transport entity may reside on network interface

by the network layer. The hardware and/or software within the transport layer that does the work is called the **transport entity**. The transport entity can be in the operating system kernel, in a separate user process, in a library package bound into network applications, or on the network interface card. In some cases, the

Paper 1 (072 Petition) at 43-44; Ex. 1003.100 (072 Horst Decl.); Ex. 1006.498 (Tanenbaum96).

In general, the transport entity may be part of the host's operating system or it may be a package of library routines running within the user's address space. It may also be contained on a coprocessor chip or network board plugged into the host's backplane. For simplicity, our example has been programmed as though it

Paper 46 (072 Reply) at 6; Ex. 1006.530 (Tanenbaum96).

### Erickson teaches that its interface device stores and transmits user data

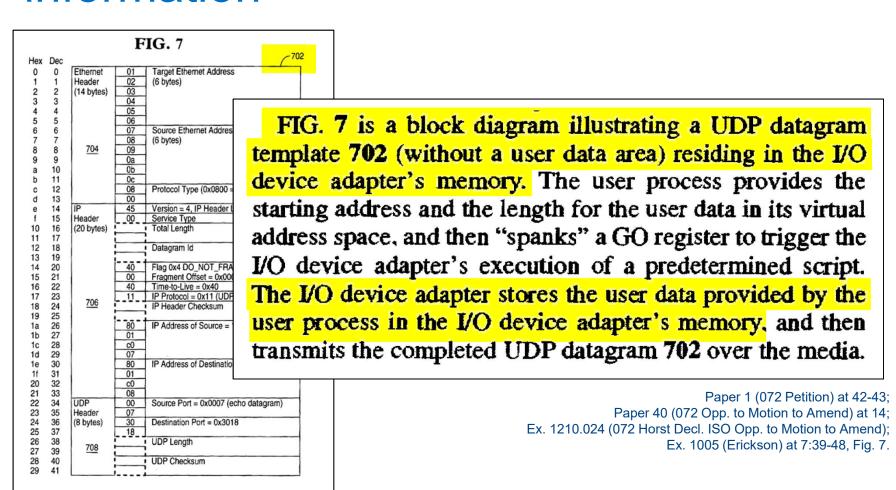

The I/O device adapter stores the user data provided by the

user process in the I/O device adapter's memory, and then

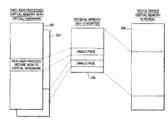

#### United States Patent [19] 5,768,618 [11] Patent Number: [45] Date of Patent:

[54] METHOD FOR PERFORMING SEQUENCE OF ACTIONS IN DEVICE CONNECTED TO COMPUTER IN RESPONSE TO SPECIFIED VALUES BEING WRITTEN INTO SNOOPED SUB PORTIONS OF ADDRESS SPACE

ventors: Gene R. Erickson; Douglas E. Hundley, both of Poway; P. Keith Muller; Curtis H. Stehley, both of San

[73] Assignee: NCR Corporation. Dayton, Ohio

[21] Appl. No.: 577,678 [22] Filed: Dec. 21, 1995

Erickson et al.

[51] Int. CL<sup>6</sup> ...... [52] U.S. Cl. 395/829 arch 395/821, 823, 395/829, 832, 846, 882, 284, 309, 500,

References Cited

#### U.S. PATENT DOCUMENTS

| 4,777,589 | 10/1988 | Boettner et al    | 395/8 |

|-----------|---------|-------------------|-------|

| 5,016,161 | 5/1991  | Van Loo et al     | 395/6 |

| 5,016,166 | 5/1991  | Van Loo et al     | 395/6 |

| 5,127,098 | 6/1992  | Rosenthal et al   | 711/2 |

| 5.280,587 | 1/1994  | Shimodaira et al. | 395/8 |

| 5,420,987 | 5/1995  | Reid et al.       | 395/8 |

| 5,548,778 | \$/1996 | Hirayama          | 395/8 |

| 5,553,244 | 9/1996  | Norcross et al    | 395/2 |

| 5,642,481 | 6/1997  | Pedrizetti 39     | 5/185 |

| 5,671,442 | 9/1997  | Foeney et al      | 395/8 |

|           |         |                   |       |

FOREIGN PATENT DOCUMENTS 551148 7/1993 European Pat. Off. OTHER PUBLICATIONS

"The Performance of Message-Passing Using Restricted Virtual Memory Remapping", by Shim-Yuan Tzou and David P. Anderson. in Software-Practice & Experience, vol. 21(3), 251–267 (Mar. 1991).

transmits the completed UDP datagram 702 over the media. Research Center, Yorktown Heights, New York 10598

Primary Examiner-Moustafa M. Meky Attorney, Agent, or Firm-Merchant, Gould. Smith. Edell. Welter & Schmidt

#### [57] ABSTRACT

A method of controlling an input/output (I/O) device connected to a computer to facilitate fast I/O data transfers. An address space for the I/O device is created in the virtual memory of the computer, wherein the address space comprises virtual registers that are used to directly control the I/O device. In essence, control registers and/or memory of the I/O device are mapped into the virtual address space, and the virtual address space is backed by control registers and/or memory on the I/O device. Thereafter, the I/O device detects writes to the address space. As a result, a pre-defined sequence of actions can be triggered in the I/O device by programming specified values into the data written into the mapped virtual address space.

#### 19 Claims, 7 Drawing Sheets

Paper 1 (072 Petition) at 33, 42-43, 44: Paper 46 (072 Reply) at 15; Ex. 1003.100-.101 (072 Horst. Decl.); Ex. 1005 (Erickson) at 7:39-46.

# Erickson divides the data and transmits data using adapter

for transmission over the media. Instead, the adapter would most likely retrieve the needed user data from the user process' virtual address space using direct memory access (DMA) into the main memory over the bus and retrieving the user data into some portion of the adapter's memory, where it could be referenced more efficiently. The program-

# Erickson's single page embodiment can support TCP

POSA would understand a typical page of virtual address space (4K bytes) would be greater than a typical MSS segment (1500 bytes)

The second script would transfer (via DMA) and transmit one maximum-segment-size (MSS) segment of data "(in practice, usually about 1500 bytes)" (Ex.1006, Tanenbaum at .540) at a time from the block identified by the user data address pointer and length passed to the script, until all of the data from the block was sent. A POSA would understand that typical page sizes in 1996 were larger than 1500 bytes (e.g. 4K pages were common).

Paper 46 (072 Reply) at 16-17; Ex. 1003.103 (072 Horst Decl.).

# I/O traffic would not be a factor in successfully implementing a TCP script

In Erickson, or other network implementations, the bulk of the I/O bus traffic is to transfer data (not control information) between the host memory and the adapter. In Erickson's original UDP scripts as well as all three proposed TCP scripts, additional data movement across the I/O bus is not necessary. Erickson Ex. 1005 at 8:27-37. In two of the proposed TCP scripts, the data transfer is performed by multiple segment-sized DMA operations, while in the third script, the data is transferred with one large DMA operation. Ex. 1003, ¶ 143, Ex.1003.102-.103. The total amount of data transferred would be the same in all cases. The differences in control traffic over the I/O bus for various options is small and certainly not a factor in whether or not TCP could have been successfully implemented.

> Paper 46 (072 Reply) at 16-17; Ex. 1223 (072 Horst Reply Decl.) ¶ 46.

- 2. The combination of Erickson and Tanenbaum96 discloses the limitations of claims 1-7 of the 036 Patent

- a) The prior art discloses "dividing, by the interface device, the data into segments" (all claims)

- b) The prior art discloses "transferring status information for the context to the interface device during the same operation as transferring protocol header information to the interface device" (claim 2)

- c) The prior art discloses "receiving, by the interface device, receive packets that correspond to the [context/protocol information], and updating the [context/status information] by the interface device to account for the receive packets" (claims 7, 14, and 21)

## "transferring status information ... during the same operation as ... protocol header information"

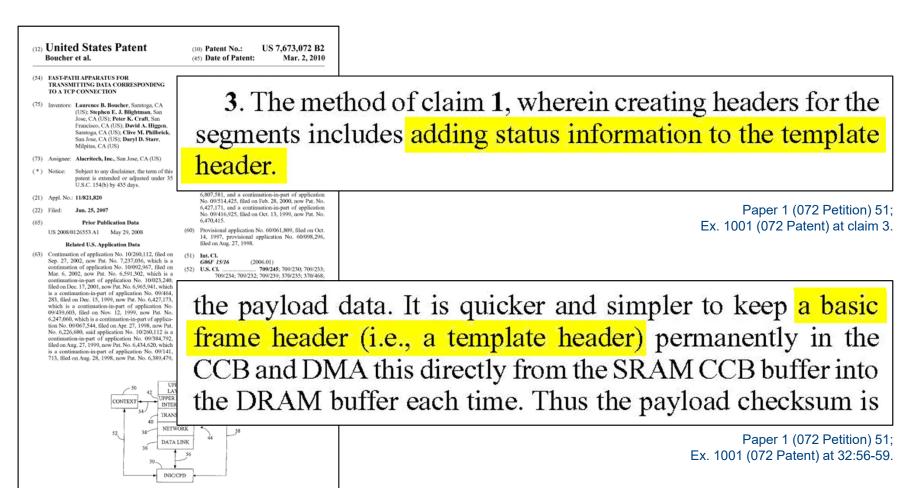

# 072 patent: "Status information" can be "basic frame header" information

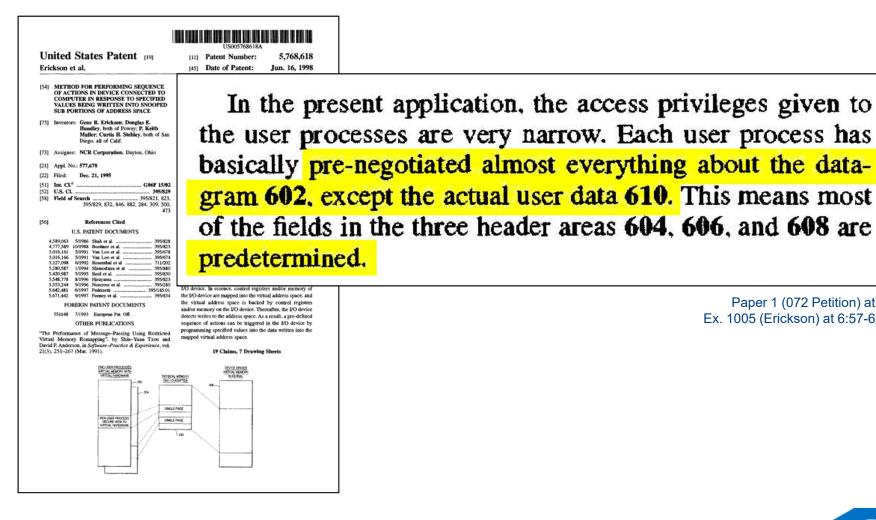

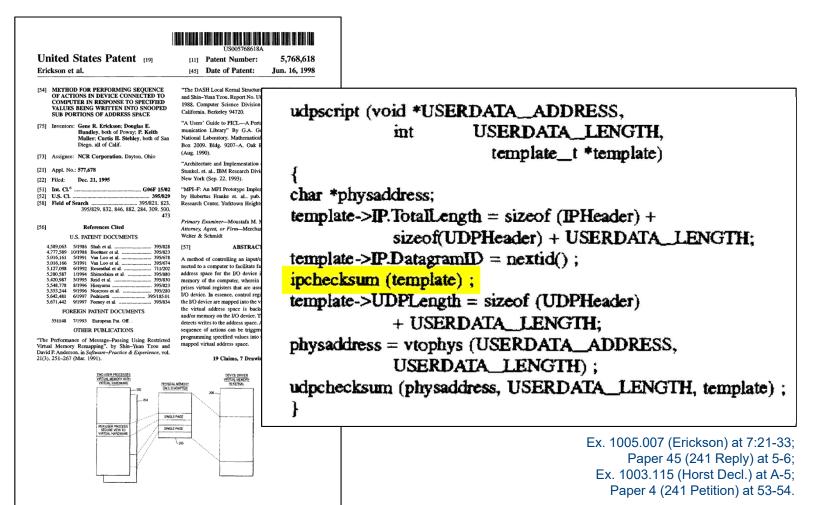

### Erickson teaches "almost everything" about datagram is "pre-negotiated"

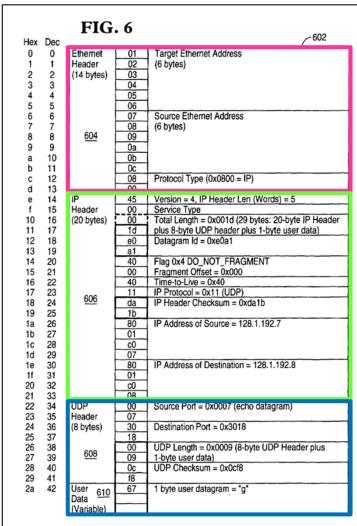

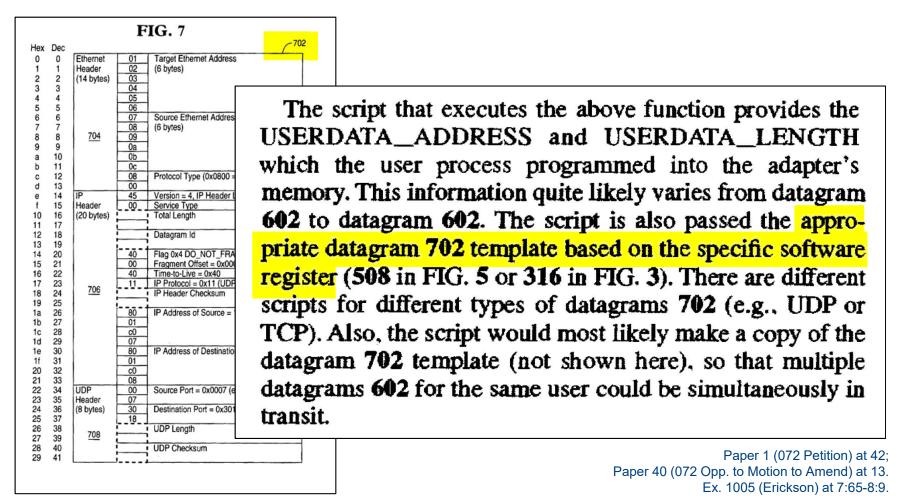

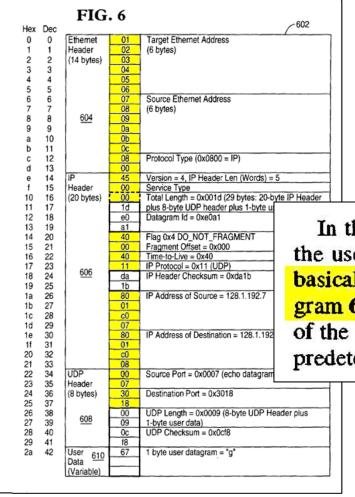

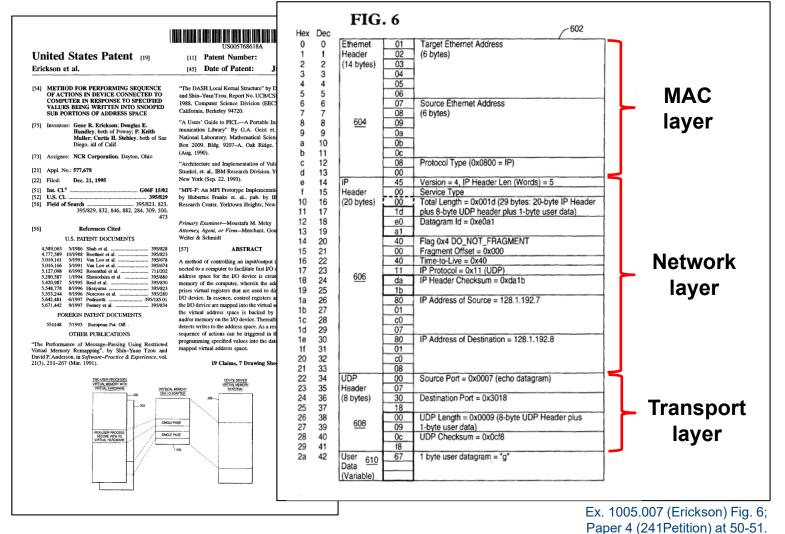

basically pre-negotiated almost everything about the datagram 602, except the actual user data 610. This means most of the fields in the three header areas 604, 606, and 608 are

> Paper 1 (072 Petition) at 53; Ex. 1005 (Erickson) at 6:57-6:62.

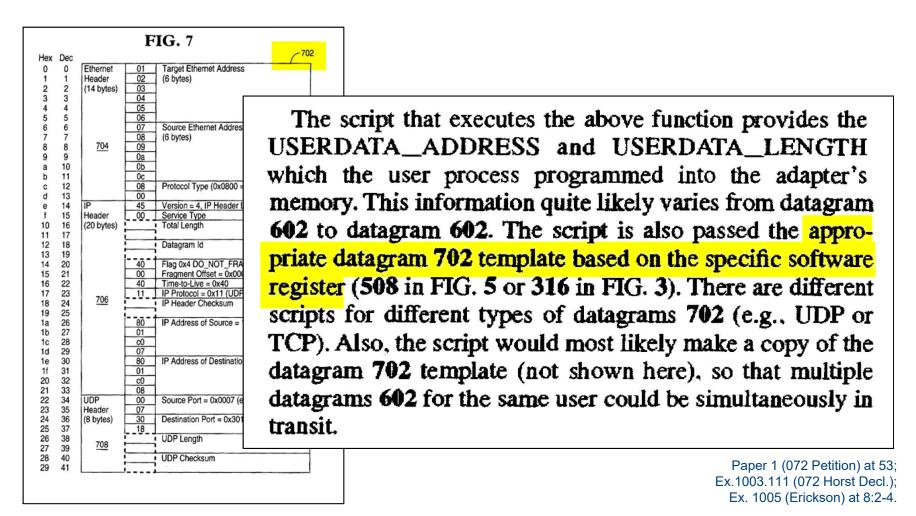

## Erickson's datagram template is a basic frame header including status information

## "Same operation" because protocol header includes status information

5,768,618

In this example, the user process and the device driver has pre-negotiated the following fields from FIG. 6: (1) Ethernet Header 604 (Target Ethernet Address, Source Ethernet Address, and Protocol Type); (2) IP Header 606 (Version, IP header Length, Service Type, Flag, Fragment Offset, Time\_to\_Live, IP Protocol, IP Address of Source, and IP Address of Destination); and (3) UDP Header 608 (Source Port and Destination Port). Only the shaded fields in FIG. 6, and the user data 610, need to be changed on a per-datagram basis.

Paper 1 (072 Petition) at 40, 53; Ex. 1003.074, .112 (072 Horst Decl.); Ex.1005 (Erickson) at 6:63-7:4.

- 2. The combination of Erickson and Tanenbaum96 discloses the limitations of claims 1-7 of the 036 Patent

- a) The prior art discloses "dividing, by the interface device, the data into segments" (all claims)

- b) The prior art discloses "transferring status information for the context to the interface device during the same operation as transferring protocol header information to the interface device" (claim 2)

- c) The prior art discloses "receiving, by the interface device, receive packets that correspond to the [context/protocol information], and updating the [context/status information] by the interface device to account for the receive packets" (claims 7, 14, and 21)

## "Receiving .... and updating ... by the interface device"

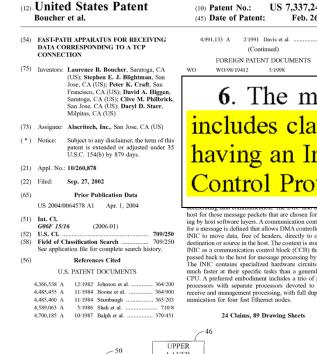

#### (12) United States Patent Boucher et al.

(54) FAST-PATH APPARATUS FOR TRANSMITTING DATA CORRESPONDING TO A TOP CONNECTION

(72) Inventors: Laurence B. Boucher, Saratoga, C.A. (US): Stephen E. J. Blightman, San Jose, C.A (US): Peter K. Craft, San Francisco, C.A (US): David A. Higgen. Saratoga, C.A (US): Clive M. Philibriel. San Jose, C.A (US): Daryl D. Starr, Milotias, C.A (US)

(73) Assignee: Alacritech, Inc., San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of the same of

(\*) Notice: Subject to any disclaimer, the term of the patent is extended or adjusted under a U.S.C. 154(b) by 435 days.

(21) Appl. No.: 11/821,820(22) Filed: Jun. 25, 2007

Prior Publication Data

US 2008/0126553 A1 May 29, 2008

#### Related U.S. Application Data

(63) Continuation of application No. 10/260.112, filed Sep. 27, 2002, now Pat. No. 723/706, which is continuation of application No. 10/092,967, filed Mar. 6, 2002, now Pat. No. 6,591;302, which is continuation-in-part of application No. 10/0023, efficied on Dec. 17, 2001, now Pat. No. 6,965;341, whi is a continuation-in-part of application No. 09/423, filed on Dec. 15, 1999, now Pat. No. 6,6427,17 which is a continuation-in-part of application No. 09/434,003, filed on Nov. 12, 1999, now Pat. No. 6,427,600, which is a continuation-in-part of application No. 10/261,122 continuation-in-part of application No. 10/261,122 continuation-in-part of application No. 09/261, No. 6,222,680, said application No. 10/261,112 continuation-in-part of application No. 09/37, 181, 181 of No. 6,220, No. 6,220, No. 6,220, No. 6,220, No. 8, 2012, No. 8,200, No. 6,220, No. 8, 2012, No. 8,200, No. 9,218, No. 6,230, No. 9,218, No. 6,230, No. 9,218, No. 6,330, No. 9,218, No. 6,330, No. 9, No. 6,330, No. 9, No. 6,330, No. 9, No. 6,330, No. 6,330, No. 9, No. 6,330,

(10) Patent No.:

US 7,673,072 B2

7. The method of claim 1, further comprising receiving, by the interface device, receive packets that correspond to the context, and updating the context by the interface device to account for the receive packets.

No. 00/416 925 filed on Oct 13, 1000, pow Pet No.

14. The method of claim 9, further comprising receiving, by the interface device, receive packets that correspond to the protocol information, and updating the status information by the interface device to account for the receive packets.

21. The method of claim 15, further comprising receiving, by the interface device, receive packets that correspond to the context, and updating the status information by the interface device to account for the receive packets.

## PO ignores the teaching of the combination

Patent Owner argues about each reference separately:

```

70-71, 76; Ex. 2026, ¶ 105.) Accordingly, Erickson does not disclose receiving packets and updating the corresponding context or status information by the interface device. Tanenbaum discloses conventional packet processing including packet reception that, as described above in § VIII.A, is performed entirely on the host. (Ex. 1006.584-589; Ex. 2026, ¶ 106.) Thus, at least the limitation of

```

Paper 34 (072 Response) at 34.

#### • But Petitioner relies on Erickson in view of Tanenbaum96:

Id. at .498 (underlining added, bold in original). Accordingly, it would be obvious to one consulting Tanenbaum96 to implement Erickson's fast path TCP protocol processing for the I/O device adapter to perform "receiving, by the interface device, receive packets that correspond to the context, and updating the context by the interface device to account for the receive packets."

Paper 1 (072 Petition) at 62.

# Obvious to use Tanenbaum96's fast-path connection records with Erickson's adapter

- 3. Motion to Amend 072 Patent should be denied

- a) Patent Owner has improperly expanded the scope of claims 22-29

- b) Patent Owner does not show adequate written description support

- c) Substitute claims 22-29 are indefinite

- d) Substitute claims are obvious

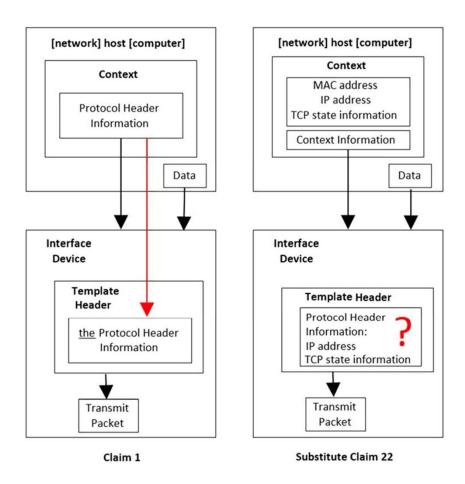

## "Protocol header information" untied to any other information in substitute claim 22

| Original Claim 1                                                                                                                                                                                                                                                                                                                                             | Substitute Claim 22                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1] A method comprising:                                                                                                                                                                                                                                                                                                                                     | [22] A method comprising:                                                                                                                                                                                                                                                                                                                                                                                              |

| [1.1] establishing, at a host computer, a transport layer connection, including creating a context that includes protocol header information for the connection;                                                                                                                                                                                             | [22.1] establishing, at a host computer, a transport layer connection, including creating a context that includes a media access control (MAC) layer address, an Internet Protocol (IP) address and Transmission Control Protocol (TCP) state information protocol header information—for the connection;                                                                                                              |

| [1.2] transferring the protocol header information to an interface device;                                                                                                                                                                                                                                                                                   | [22.2] transferring the context protocol header information to an interface device;                                                                                                                                                                                                                                                                                                                                    |

| [1.3] transferring data from the network host to the interface device, after transferring the protocol header information to the interface device; [1.4] dividing, by the interface device, the data into segments; [1.5] creating headers for the segments, by the interface device, from a template header containing the protocol header information; and | [22.3] transferring data from the network host to the interface device, after transferring the context protocol header information to the interface device; [22.4] dividing, by the interface device, the data into segments; [22.5] creating headers for the segments, by the interface device, from a template header containing the protocol header information including IP address and TCP state information; and |

| [1.6] prepending the headers to the segments to form transmit packets.                                                                                                                                                                                                                                                                                       | [22.6] prepending the headers to the segments to form transmit packets.                                                                                                                                                                                                                                                                                                                                                |

Paper 54 (072 Sur-Reply for Opp. to Motion to Amend) at 3.

## "Protocol header information" untied to "context" would infringe claim 22, but not claim 1

- 3. Motion to Amend 072 Patent should be denied

- a) Patent Owner has improperly expanded the scope of claims 22-29

- b) Patent Owner does not show adequate written description support

- c) Substitute claims 22-29 are indefinite

- d) Substitute claims are obvious

## PO must supply written description support after *Aqua Products*

#### **United States Patent and Trademark Office**

Office of the Chief Administrative Patent Judge

#### MEMORANDUM

**TO:** Patent Trial and Appeal Board

FROM: David P. Ruschke

Chief Administrative Patent Judge

David.Ruschke@uspto.gov

**DATE:** November 21, 2017

RE: Guidance on Motions to Amend in view of Aqua Products

Beyond that change, generally speaking, practice and procedure before the Board will not change. For example, a patent owner still must meet the requirements for a motion to amend under 37 C.F.R. § 42.121 or § 42.221, as applicable. That is, a motion to amend must set forth written description support and support for the benefit of a filing date in relation to each substitute claim, and respond to grounds of unpatentability involved in the trial. Likewise, under 37 C.F.R. § 42.11, all parties have a duty of

## PO identifies same 10 pages and 12 figures for every independent claim limitation

| Claims                                                                                                                                                                                                                                                                                             | Exemplary Support in the '820 Application                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Proposed Claim 22                                                                                                                                                                                                                                                                                  |                                                                                                |

| 422. A method comprising:                                                                                                                                                                                                                                                                          | See below.                                                                                     |

| establishing, at a host computer, a transport layer connection, including creating a context that includes a media access control (MAC) layer address, an Internet Protocol (IP) address and Transmission Control Protocol (TCP) state information protocol header information for the connection; | See, e.g., Ex. 2024 at<br>Abstract, Figs. 1-3, 4A-4D,<br>and 5-12, Pages 7-8, 10-17,<br>Cl. 1. |

| transferring the <u>context</u> <del>protocol header</del> information to an interface device;                                                                                                                                                                                                     | See, e.g., Ex. 2024 at<br>Abstract, Figs. 1-3, 4A-4D,<br>and 5-12, Pages 7-8, 10-17,<br>Cl. 1. |

| transferring data from the network host to the interface device, after transferring the <u>context</u> protocol header information to the interface device;                                                                                                                                        | See, e.g., Ex. 2024 at<br>Abstract, Figs. 1-3, 4A-4D,<br>and 5-12, Pages 7-8, 10-17,<br>Cl. 1. |

| dividing, by the interface device, the data into segments;                                                                                                                                                                                                                                         | See, e.g., Ex. 2024 at<br>Abstract, Figs. 1-3, 4A-4D,<br>and 5-12, Pages 7-8, 10-17,<br>Cl. 1. |

| creating headers for the segments, by the interface device, from a template header containing the protocol header information including IP address and TCP state information; and                                                                                                                  | See, e.g., Ex. 2024 at<br>Abstract, Figs. 1-3, 4A-4D,<br>and 5-12, Pages 7-8, 10-17,<br>Cl. 1. |

| prepending the headers to the segments to form transmit packets.                                                                                                                                                                                                                                   | See, e.g., Ex. 2024 at<br>Abstract, Figs. 1-3, 4A-4D,<br>and 5-12, Pages 7-8, 10-17,<br>Cl. 1. |

Same written description support as 036 Patent

Paper 40 (072 Opp. to Motion to Amend) at 4-5; Paper 62 (072 Corrected Exhibits for Motion to Amend), Appx. A.

## Too late to provide written description support in Reply

PO provides alleged "exemplary" written description support <u>for</u>

<u>the first time</u> in its Reply

#### VII. THE PROPOSED AMENDMENTS ARE SUPPORTED BY THE WRITTEN DESCRIPTION

75. It is my opinion that the proposed amendments are supported by the written description, along with the Application (No. 11/821,820) and Provisional Application (No. 60/061,809).

Paper 47 (072 Reply ISO Motion to Amend) at 6; Ex. 2305 (Almeroth Decl. ISO Reply) at 25.

## Written description support provided by PO is insufficient

- Patent Owner cites to written description support not included in its original motion

- Patent Owner has not identified any written description support for:

- "Transferring the context information to an interface device"

- Creating a "template header" from **any** "protocol header information"

Paper 54 (072 Sur-Reply for Motion to Amend) at 7-8.

- 3. Motion to Amend 072 Patent should be denied

- a) Patent Owner has improperly expanded the scope of claims 22-29

- b) Patent Owner does not show adequate written description support

- c) Substitute claims 22-29 are indefinite

- d) Substitute claims are obvious

#### Claim 22 is indefinite

(22.1) establishing, at a host computer, a transport layer connection, including creating <u>a context</u> that includes a media access control (MAC) layer address, an Internet Protocol (IP) address and Transmission Control Protocol (TCP) state information for the connection;

- (22.2) transferring **the context information** to an interface device;

- (22.3) transferring data from the network host to the interface device, after transferring **the context information** to the interface device;

Paper 40 (072 Opp. to Motion to Amend) at 8-10; Ex. 1210 (072 Horst Decl. ISO Opp. to Motion to Amend) ¶ 18.

Motion to Amend 072 Patent should be denied

#### d) Substitute claims are obvious

- i. Prior art discloses "creating a context that includes a MAC layer address, an IP address, and TCP state information for the connection" (limitation 22.1)

- ii. Prior art discloses "transferring the context information to an interface device" (limitation 22.2)

- iii. Prior art discloses "transferring data ... after transferring the context information to the interface device" (limitation 22.3)

- iv. Prior art discloses "creating headers for the segments, by the interface device, from a template header" containing "TCP state information" (limitation 22.5)

# Erickson: "Pre-negotiated" header that includes "almost everything" for UDP

In the present application, the access privileges given to the user processes are very narrow. Each user process has basically pre-negotiated almost everything about the datagram 602, except the actual user data 610. This means most of the fields in the three header areas 604, 606, and 608 are predetermined.

In this example, the user process and the device driver has pre-negotiated the following fields from FIG. 6: (1) Ethernet Header 604 (Target Ethernet Address, Source Ethernet Address, and Protocol Type); (2) IP Header 606 (Version, IP header Length, Service Type, Flag, Fragment Offset, Time\_to\_Live, IP Protocol, IP Address of Source, and IP Address of Destination); and (3) UDP Header 608 (Source Port and Destination Port). Only the shaded fields in FIG. 6, and the user data 610, need to be changed on a per-datagram basis.

Paper 40 (072 Opp. to Motion to Amend) at 11-12; Ex. 1005 (Erickson) at 6:58-7:3, Fig. 6.

## POSA would have replaced UDP header with TCP header

Motion to Amend 072 Patent should be denied

#### d) Substitute claims are obvious

- Prior art discloses "creating a context that includes a MAC layer address, an IP address, and TCP state information for the connection" (limitation 22.1)

- ii. <u>Prior art discloses "transferring the context information to an interface device" (limitation 22.2)</u>

- iii. Prior art discloses "transferring data ... after transferring the context information to the interface device" (limitation 22.3)

- iv. Prior art discloses "creating headers for the segments, by the interface device, from a template header" containing "TCP state information" (limitation 22.5)

# Erickson discloses transferring "datagram template" to I/O adapter

Motion to Amend 072 Patent should be denied

### d) Substitute claims are obvious

- Prior art discloses "creating a context that includes a MAC layer address, an IP address, and TCP state information for the connection" (limitation 22.1)

- ii. Prior art discloses "transferring the context information to an interface device" (limitation 22.2)

- iii. Prior art discloses "transferring data ... after transferring the context information to the interface device" (limitation 22.3)

- iv. Prior art discloses "creating headers for the segments, by the interface device, from a template header" containing "TCP state information" (limitation 22.5)

## Data is transferred after the context information

Motion to Amend 072 Patent should be denied

### d) Substitute claims are obvious

- Prior art discloses "creating a context that includes a MAC layer address, an IP address, and TCP state information for the connection" (limitation 22.1)

- ii. Prior art discloses "transferring the context information to an interface device" (limitation 22.2)

- iii. Prior art discloses "transferring data ... after transferring the context information to the interface device" (limitation 22.3)

- iv. Prior art discloses "creating headers for the segments, by the interface device, from a template header" containing "TCP state information" (limitation 22.5)

## POSA would have replaced UDP header with TCP header

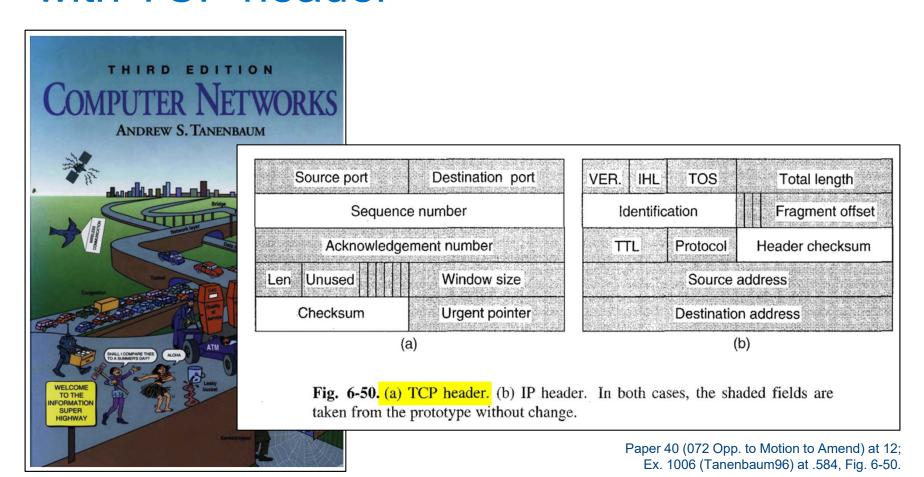

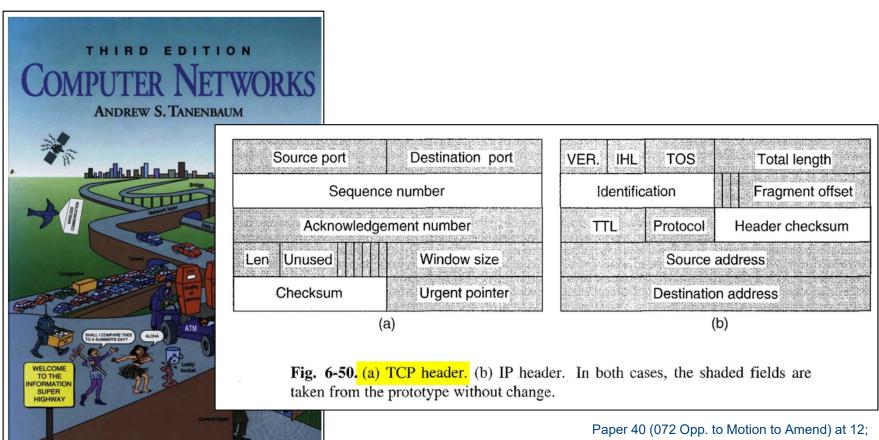

Paper 40 (072 Opp. to Motion to Amend) at 12; Ex. 1006 (Tanenbaum96) at .584, Fig. 6-50.

# U.S. Patent No. 7,337,241 (241 Patent)

IPR2017-1392 (Intel) IPR2018-0372 (Dell) IPR2017-1728 (Cavium) IPR2018-0328 (Wistron)

### 241 Patent: Instituted Grounds

- Erickson in view of Tanenbaum96 and Alteon

- Claims 1, 2-8, 18, 22, and 23

- Erickson in view of Tanenbaum96 (Common to 036 and 072 Patents)\*

- Claims 9, 10-16, 17, 19-21, and 24

- \* This combination is discussed on slides 6-53 (regarding 036 and 072 patents)

Ex. 1005 – U.S. Patent No. 5,768,618 ("Erickson")

Ex. 1006 – Tanenbaum, Andrew S., Computer Networks ("Tanenbaum96")

Ex. 1033 – "Gigabit Ethernet Technical Brief ("Alteon")

- 1. A POSA would be motivated to combine

- a. Erickson and Tannenbaum96

- b. Alteon with Erickson and Tannenbaum96

- 2. The prior art discloses all of the disputed limitations of the 241 Patent

- 3. Alteon is Prior Art

- 4. Motion to Amend 241 Patent

- 1. A POSA would be motivated to combine

- a. Erickson and Tannenbaum96

See 036 Patent, Dispute 1, slides 6-53

- 1. A POSA would be motivated to combine

- a. Erickson and Tannenbaum96

- b. Alteon with Erickson and Tannenbaum96

- i. A POSA would have been motivated to apply Alteon's interrupt reductions to Erickson and Tanenbaum96

- ii. Tanenbaum96 does not teach away from the combination (see slides 33-40)

- iii. Erickson and Alteon are compatible

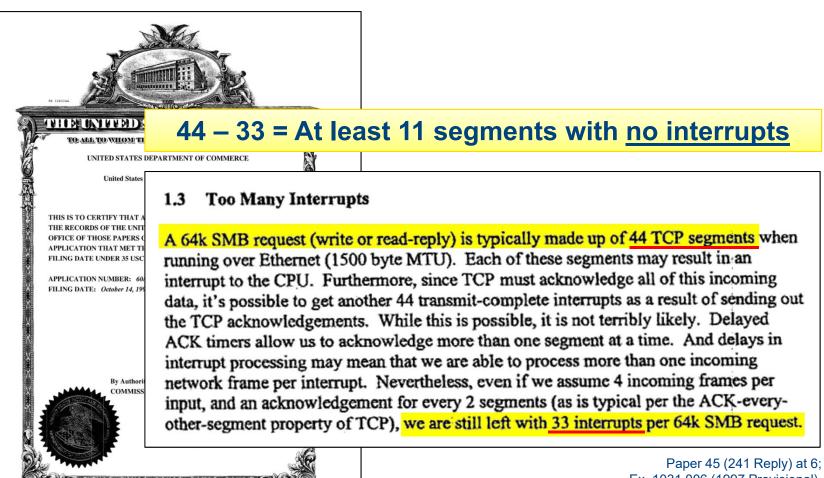

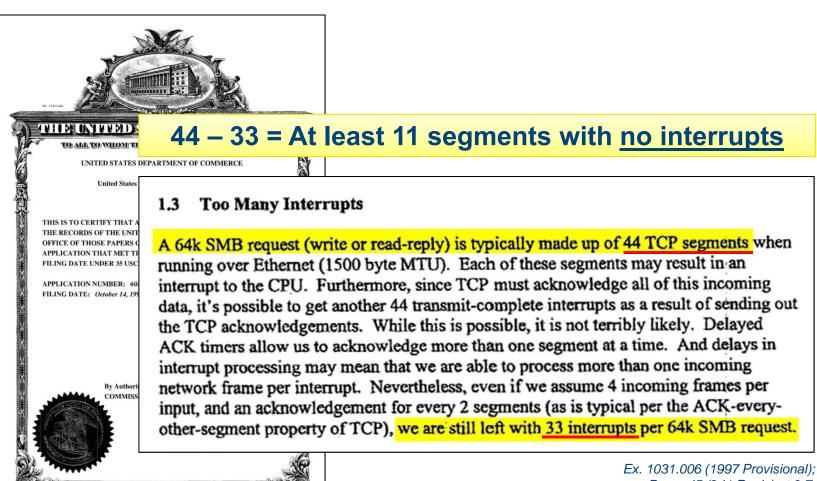

## PO has admitted that using fewer than one interrupt per packet was known

Ex. 1031.006 (1997 Provisional).

## Erickson sought to avoid operating system intervention

169. A chief concern of Erickson is to avoid intervention of the operating system on a "per I/O basis." Ex.1005, Erickson at 3:9-10. Erickson partially addresses this problem by using scripts on the I/O device to process data. Alteon

Ex. 1003.101 (Horst Decl.) at ¶ 169.

Thus, it will be recognized that the present invention increases the efficiency of I/O operations in the following ways:

- 1. Writing information to and from a user address space without intermediate memory-to-memory copies.

- Accessing an I/O device simultaneously from multiple user processes in a single node.

- 3. Eliminating calls to the operating system and the associated context switches on a per I/O basis.

Ex. 1005.010 (Erickson) at 3:1-10.

# Alteon shows that sending fewer interrupts was known and desirable

## Gigabit Ethernet Technical Brief

Using an intelligent adapter with an onboard RISC-based processor specially designed for embedded application processing, Alteon's Gigabit Ethernet technology not only reduces the number of times data is copied among processing entities, it allows a single interrupt to be issued for multiple data packets—radically altering the ratio of interrupts to packets, and eliminating the scalability problems inherent in older adapter designs.

Alteon Gigabit Ethernet adapters have an interrupt timer that determines when to interrupt a host CPU. This allows a single interrupt to be issued for multiple data packets that are sent into the operating system buffer space. It also allows for "adaptive" interrupts; that is, the NIC can alter the number of interrupts issued per second based on network usage.

Alteon Networks, Inc. 6351 San Ignacio Avenue San Jose, CA 95119

1-408-574-5500

First Edition September 1996 Paper 4 (241 Petition) at 47-48; Paper 45 (241 Reply) at 5; Ex. 1033.022-.023 (Alteon).

- 1. A POSA would be motivated to combine

- a. Erickson and Tannenbaum96

- b. Alteon with Erickson and Tannenbaum96

- i. A POSA would have been motivated to apply Alteon's interrupt reductions to Erickson and Tanenbaum96

- ii. <u>Tanenbaum96 does not teach away from the combination</u> (see slides 33-40)

- iii. Erickson and Alteon are compatible

- 1. A POSA would be motivated to combine

- a. Erickson and Tannenbaum96

- b. Alteon with Erickson and Tannenbaum96

- i. A POSA would have been motivated to apply Alteon's interrupt reductions to Erickson and Tanenbaum96

- ii. Tanenbaum96 does not teach away from the combination (see slides 33-40)

- iii. Erickson and Alteon are compatible

## Erickson is not limited to a single page architecture

5,768,618

Jun. 16, 1998

FOREIGN PATENT DOCUMENTS 551148 7/1993 European Pat. Off. .

OTHER PUBLICATIONS

"The Performance of Message-Passing Using Restricted Virtual Memory Remapping", by Shin-Yuan Tzou and David P. Anderson, in Software-Practice & Experience, vol. 21(3), 251–267 (Mar. 1991).

address into a physical address usable by the adapter. In all likelihood, the adapter would have a very limited knowledge of the user process' virtual address space, probably only knowing how to map virtual-to-physical for a very limited range, maybe as small as a single page. Pages in the user process' virtual address space for such buffers would need to be fixed. The udpscript procedure would need to be enhanced if the user data were allowed to span page boundaries. The udpchecksum() procedure generates a checksum

Ex. 1005.012 (Erickson) at 8:16-24; Ex. 1223.024 (Horst Reply Decl.) at ¶¶ 47-49; Paper 45 (241 Reply) at 11-12.

# A single page is sufficient to hold multiple TCP segments

UNITED STATES PATENT AND TRADEMARK OFFICE

embodiments in the specification. However, even if Erickson was limited to a

single page, TCP segments are often smaller than a page. For example, in Ethernet

which is the most common media, TCP segments are typically about 1500 bytes,

which is smaller than a typical page size of 4K bytes. Thus, a POSA could have

implemented a TCP embodiment without making changes to the Erickson

adapter's ability to cross page boundaries.

Title: FAS

DECLA REPLY

*Mail Stop* Patent Tri

P.O. Box 1450 Alexandria, VA 22313-1450

Ex. 1223.023-.024 (Horst Reply Decl.) at ¶ 46; Paper 45 (241 Reply) at 11-12.

<sup>&</sup>lt;sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2017-01728, has been joined as a petitioner in this proceeding. Wistron Corporation, who filed a Petition in Case IPR2018-00328, has been joined as a petitioner in this proceeding.

- 2. The prior art discloses all of the disputed limitations of the 241 Patent

- a) Erickson in view of Tanenbaum96 and Alteon discloses the limitations of claims 1, 2-8, 18, 22, and 23 of the 241 Patent (receive claims)

- b) Erickson in view of Tanenbaum96 discloses the limitations of claims 9, 10-16, 17, 19-21, and 21 of the 241 Patent (transmit claims)

## 241 Patent: Disputes (Receive Claims)

- a) Erickson in view of Tanenbaum96 and Alteon discloses the limitations of claims 1, 2-8, 18, 22, and 23 of the 241 Patent

- i. The prior art discloses validation of network and transport layer headers "without an interrupt dividing the processing" (claim 1)

- ii. The prior art discloses sending the data from each packet to a destination in memory without sending any of the headers (claim 1)

- iii. The prior art discloses processing MAC layer headers without an interrupt (claim 2)

- iv. The prior art discloses processing an upper layer header by a second mechanism (claim 3)

- v. The prior art discloses sorting the packets by classifying each as having IP and TCP headers (claim 6)

### 241 Patent: Claim 1

### (12) United States Patent US 7.337,241 B2 (10) Patent No.: Boucher et al. (45) Date of Patent: Feb. 26, 2008 FAST-PATH APPARATUS FOR RECEIVING 2/1991 Davis et al. 4.991.133 A (Continued) CONNECTION FOREIGN PATENT DOCUMEN Inventors: Laurence B. Boucher, Saratoga, CA WO/98/19412 5/1998 (US): Stephen E. J. Blightman. San (Continued) OTHER PUBLICATIONS Francisco, CA (US): David A. Higgen

(73) Assignee: Alacritech, Inc., San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this second in control is extended as adjusted under 35

patent is extended or adjusted under 35 U.S.C. 154(b) by 879 days.

San Jose, CA (US); Daryl D. Starr,

(21) Appl. No.: 10/260,878

(22) Filed: Sep. 27, 2002

(65) Prior Publication Data

US 2004/0064578 A1 Apr. 1, 2004

| (51) | Int. Cl.                                  |         |

|------|-------------------------------------------|---------|

|      | G06F 15/16 (2006.01)                      |         |

| (52) | U.S. Cl                                   | 709/250 |

| (58) | Field of Classification Search            | 709/250 |

|      | 0 1 2 6 6 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |         |

ILS PATENT DOCUMENTS

6) References Cited

| 1,366,538 | A | 12/1982 | Johnson et al | 364/200 |

|-----------|---|---------|---------------|---------|

| 1,485,455 | A | 11/1984 | Boone et al   | 364/900 |

| 1,485,460 | A | 11/1984 | Stambaugh     | 365/203 |

| 1,589,063 | A | 5/1986  | Shah et al    | 710/8   |

|           |   |         | P. I. I I     |         |

Internet pages entitled "Hardware Assisted Protor (which Eugene Feinberg is working on), 1 page, 1

(Continued)

Primary Examiner—David Wiley (74) Attorney, Agent, or Firm—Mark Laue Law Group LLP

57) ABSTRACT

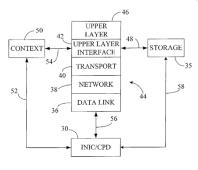

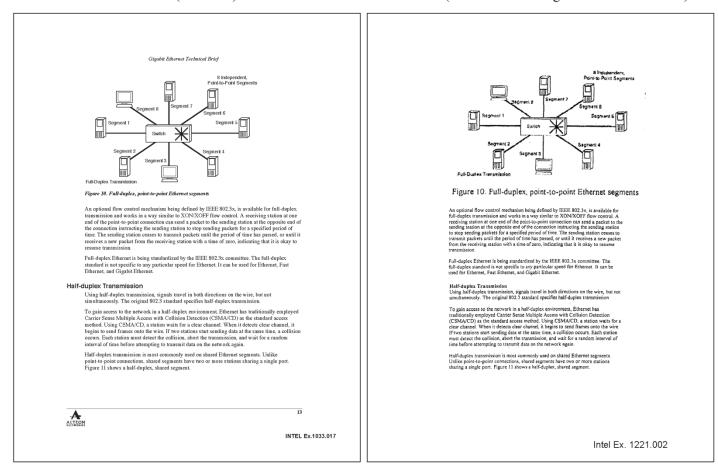

A system for protocol processing in a computant intelligent network interface card (INC)tion processing device (CPD) associated wit puter. The INIC provides a fast-path that a processing for most large multi-packet me accelerating data communication. The INIC host for those message packets that are chos ing by host software layers. A communication for a message is defined that allows DMA co INIC to move data, free of headers, directly destination or source in the host. The context INIC as a communication control block (CC passed back to the host for message procession. The INIC contains specialized hardware cumel faster at their specific tasks than a g CPU. A preferred embodiment includes at a processors with separate processors devote receive and management processing, with fur munication for four fast Ethernet nodes.

24 Claims, 89 Drawing She

1. A method for network communication, the method comprising:

receiving a plurality of packets from the network, each of the packets including a media access control layer header, a network layer header and a transport layer header:

processing the packets by a first mechanism, so that for each packet the network layer header and the transport layer header are <u>validated</u> without an interrupt dividing the processing of the network layer header and the transport layer header;

sorting the packets, dependent upon the processing, into first and second types of packets, so that the packets of the first type each contain data;

sending, by the first mechanism, the data from each packet of the first type to a destination in memory allocated to an application without sending any of the media access control layer headers, network layer

Ex. 1001.142 (241 Patent), Claim 1.

# The prior art combination teaches header validation on the adapter

## The prior art combination teaches header validation on the adapter

## THIRD EDITION COMPUTER NETWORKS ANDREW S. TANENBAUM

The header and data should be separately checksummed, for two reasons. First, to make it possible to checksum the header but not the data. Second, to verify that the header is correct before starting to copy the data into user space. It is desirable to do the data checksum at the time the data are copied to user space, but if the header is incorrect, the copy may be to the wrong process. To avoid an incorrect copy but to allow the data checksum to be done during copying, it is essential that the two checksums be separate.

Ex. 1006.589 (Tanenbaum96); Ex. 1003.059-.060 (Horst Decl.) at ¶ 100; Paper 45 (241 Reply) at 6.

# There is "no reason to interrupt the processing of the host computer"

Trials@uspto.gov 571-272-7822 Paper 11 Entered: November 30, 2017

Regarding the "without interrupt" requirement of claim 17, all processing to generate headers for packets to be sent from the network interface device of Erickson is performed by the processing capability of Erickson's network interface device with no reason to interrupt the processing of the host computer requesting the transmission.

DECISION Institution of Inter Partes Review 37 C.F.R. § 42.108

I. INTRODUCTION

Intel Corporation ("Petitioner") requests inter partes review of claims all claims (1-24) of U.S. Patent No. 7,337,241 B2 ("the "241 patent," Ex. Paper 11 (Institution Decision) at 19; Paper 41 (241 Reply) at 17; Ex. 1003.095-.096 (Horst Decl.) at ¶ 159.

## Priority application admits using fewer than 1 interrupt per packet was known

Paper 45 (241 Reply) at 6-7.

# Alteon teaches using fewer than one interrupt per packet

## Gigabit Ethernet Technical Brief

Using an intelligent adapter with an onboard RISC-based processor specially designed for embedded application processing, Alteon's Gigabit Ethernet technology not only reduces the number of times data is copied among processing entities, it allows a single interrupt to be issued for multiple data packets—radically altering the ratio of interrupts to packets, and eliminating the scalability problems inherent in older adapter designs.

Alteon Gigabit Ethernet adapters have an interrupt timer that determines when to interrupt a host CPU. This allows a single interrupt to be issued for multiple data packets that are sent into the operating system buffer space. It also allows for "adaptive" interrupts; that is, the NIC can alter the number of interrupts issued per second based on network usage.

Alteon Networks, Inc. 6351 San Ignacio Avenue San Jose, CA 95119

1-408-574-5500

Ex. 1033.022-.023 (Alteon); Paper 45 (241 Reply) at 5.

First Edition September 1996

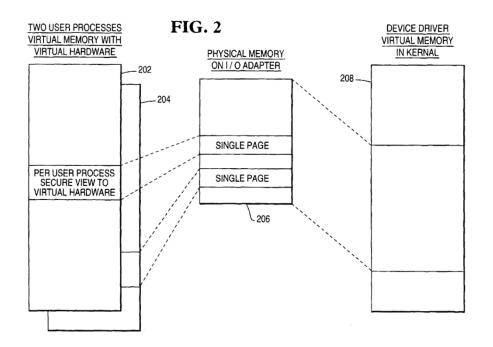

# Erickson teaches transfer without interrupts using polling and snooping

"Incoming data is then written to the virtual memory and detected by polling or "snooping" hardware."

Ex. 1005.003, -.012 (Erickson) at Fig. 2, 8:50-52; Ex. 1223.025-.026 (Horst Reply Decl.) at ¶¶ 50-52; Paper 45 (241 Reply) at 6.

# Dr. Horst explains that snooping and polling do not involve interrupts

### UNITED STATES PATENT AND TRADEMARK OFFICE

hardware'." Ex. 1005 at 8:50-52. Erickson clearly describes how the snooping works to allow the adapter and host to read and write portions of each other's memory, and this type of snooping does not involve interrupts. Erickson's

Title: FAS

DECLAR REPLY

Mail Stop

software, then another context switch back to user space. Instead, Erickson's

polling loop allows the user code to directly poll the STATUS register without any

involvement from the operating system.

U.S. Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450

<sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2017-01728, has been joined as a petitioner in this proceeding. Wistron Corporation, who filed a Petition in Case IPR2018-00328, has been joined as a petitioner in this proceeding.

Ex. 1223.025 (Horst Reply Decl.) at ¶ 50; Ex. 1005.012 (Erickson) at 6:25-31; Paper 45 (241 Reply) at 6.

## 241 Patent: Disputes (Receive Claims)

- a) The combination of Erickson, Tanenbaum96 and Alteon discloses the limitations of claims 1, 2-8, 18, 22, and 23 of the 241 Patent

- i. The prior art discloses validation of network and transport layer headers "without an interrupt dividing the processing" (claim 1)

- ii. The prior art discloses sending the data from each packet to a destination in memory without sending any of the headers (claim 1)

- iii. The prior art discloses processing MAC layer headers without an interrupt (claim 2)

- iv. The prior art discloses processing an upper layer header by a second mechanism (claim 3)

- v. The prior art discloses sorting the packets by classifying each as having IP and TCP headers (claim 6)

### 241 Patent: Claim 1

### (12) United States Patent Boucher et al. (54) FAST-PATH APPARATUS FOR RECEIVING DATA CORRESPONDING TO A TCP (75) Inventors: Laurence B. Boucher, Saratoga, CA (US); Stephen E. J. Blightman, San Jose, CA (US); Peter K. Craft, San Francisco, CA (US); David A. Higgen, Saratoga, CA (US); Clive M. Philbrick, San Jose, CA (US); Daryl D. Starr, Milpitas, CA (US) (73) Assignee: Alacritech, Inc., San Jose, CA (US) Subject to any disclaimer, the term of this (\*) Notice: patent is extended or adjusted under 35 U.S.C. 154(b) by 879 days. (21) Appl. No.: 10/260,878 Sep. 27, 2002 **Prior Publication Data** US 2004/0064578 A1 Apr. 1, 2004 (51) Int. Cl. G06F 15/16 (2006.01) (52) U.S. Cl. (58) Field of Classification Search ....... 709/250 See application file for complete search history. U.S. PATENT DOCUMENTS 4,485,455 A 11/1984 Boone et al. ...... 364/900 4 589 063 A 5/1986 Shah et al. ..... 4,700,185 A 10/1987 Balph et al. ...... 370/451

(10) Patent No.: US 7,337,241 B2

4.991.133 A 2/1991 Davis et al (Continued)

(45) Date of Patent:

FOREIGN PATENT DOCU WO/98/19412 5/1998 (Continued)

OTHER PUBLICATION

Internet pages entitled "Hardware Assisted I (which Eugene Feinberg is working on), 1

Primary Examiner—David Wiley (74) Attorney, Agent, or Firm—Mark L Law Group LLP

ABSTRACT

A system for protocol processing in a co an intelligent network interface card (IN tion processing device (CPD) associated puter. The INIC provides a fast-path th processing for most large multi-packet accelerating data communication. The IN host for those message packets that are a for a message is defined that allows DM. INIC to move data, free of headers, dis destination or source in the host. The con INIC as a communication control block passed back to the host for message proc The INIC contains specialized hardway much faster at their specific tasks than CPU. A preferred embodiment includes processors with separate processors de receive and management processing, wit

24 Claims, 89 Drawing Sl

1. A method for network communication, the method comprising:

receiving a plurality of packets from the network, each of the packets including a media access control layer header, a network layer header and a transport layer header:

processing the packets by a first mechanism, so that for each packet the network layer header and the transport layer header are validated without an interrupt dividing the processing of the network layer header and the transport layer header;

sorting the packets, dependent upon the processing, into first and second types of packets, so that the packets of the first type each contain data;

sending, by the first mechanism, the data from each packet of the first type to a destination in memory allocated to an application without sending any of the media access control layer headers, network layer

Ex. 1001.142 (241 Patent), Claim 1.

# Erickson transfers data to applications in the host directly without headers

1111 Patent Number:

[45] Date of Patent:

### United States Patent [19]

Erickson et al.

[54] METHOD FOR PERFORMING SEQUENCE OF ACTIONS IN DEVICE CONNECTED TO COMPUTER IN RESPONSE TO SPECIFIED VALUES BEING WRITTEN INTO SNOOPED SUB PORTIONS OF ADDRESS SPACE

[75] Inventors: Gene R. Erickson; Douglas E. Hundley, both of Poway; P. Keith Muller; Curtis H. Stehley, both of San Diego, all of Calif.

[73] Assignee: NCR Corporation, Dayton, Ohio

[21] Appl. No.: 577,678

### [56] References Cited

### U.S. PATENT DOCUMENTS

395/829, 832, 846, 882, 284, 309, 500

| 4,289,063 |         | Snan et al       | 393/828  |

|-----------|---------|------------------|----------|

| 4,777,589 | 10/1988 | Boettner et al   | 395/823  |

| 5,016,161 | 5/1991  | Van Loo et al    | 395/678  |

| 5,016,166 | 5/1991  | Van Loo et al    | 395/674  |

| 5,127,098 | 6/1992  | Rosenthal et al  | 711/202  |

| 5,280,587 | 1/1994  | Shimodaira et al | 395/880  |

| 5,420,987 | 5/1995  | Reid et al       | 395/830  |

| 5,548,778 | 8/1996  | Hirayama         | 395/823  |

| 5,553,244 | 9/1996  | Norcross et al   | 395/280  |

| 5,642,481 | 6/1997  | Pedrizetti       | 5/185.01 |

| 5,671,442 | 9/1997  | Feeney et al     | 395/834  |

|           |         |                  |          |

### FOREIGN PATENT DOCUMENTS

551148 7/1993 European Pat. Off. .

OTHER PUBLICATIONS

"The Performance of Message-Passing Using Restricted Virtual Memory Remapping". by Shin-Yuan Tzou and David P. Anderson. in Software-Practice & Experience, vol. 21(3), 251-267 (Mar. 1991).

"The DASH Local Kernal Structure" by David P. A and Shin-Yuan Tzou, Report No. UCB/CSD 88/463. 1988. Computer Science Division (EECS), Unive California, Berkeley 94720.

5,768

Jun. 16,

"A Users' Guide to PICL—A Portable Instrumented munication Library" By G.A. Geist et. al., Oak National Laboratory, Mathematical Sciences Sectio Box 2009. Bldg. 9207–A. Oak Ridge, TN 37831 (Aug. 1990).

"Architecture and Implementation of Vulcan" By C Stunkel, et. al., IBM Research Division, Yorktown New York (Sep. 22, 1993).

"MPI-F: An MPI Prototype Implementation on IBM by Hubertus Franke et. al., pub. by IBM, T.J. Research Center, Yorktown Heights, New York 105

Primary Examiner—Moustafa M. Meky Attorney, Agent, or Firm—Merchant, Gould. Smith Welter & Schmidt

### ABSTRACT

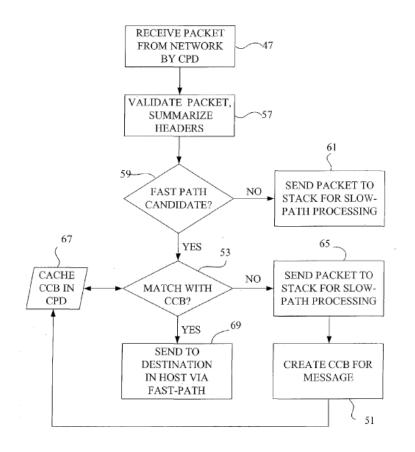

A method of controlling an input/output (I/O) device nected to a computer to facilitate fast I/O data transfal address space for the I/O device is created in the virtual address space for the I/O device is created in the virtual address space comprises virtual registers that are used to directly control the I/O device. In essence, control registers and/or memory of the I/O device are mapped into the virtual address space and the virtual address space is backed by control registers and/or memory on the I/O device. Thereafter, the I/O device detects writes to the address space. As a result, a pre-defined sequence of actions can be triggered in the I/O device by programming specified values into the data written into the mapped virtual address space.

19 Claims, 7 Drawing Sheets

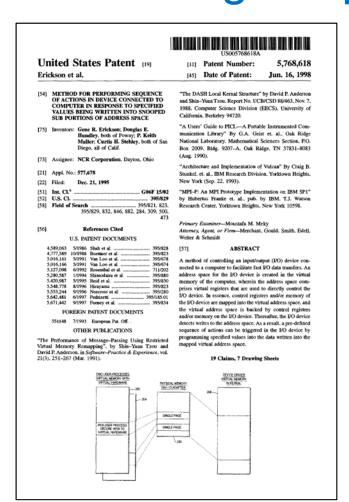

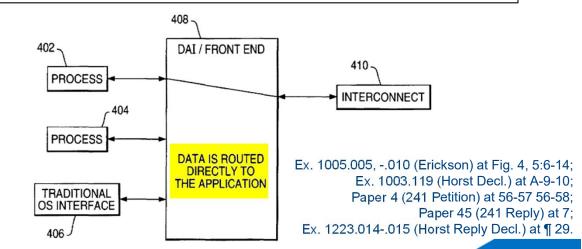

FIG. 4 is a block diagram describing a direct application interface (DAI) and routing of data between processes and an external data connection which is compatible with the present invention. Processes 402 and 404 transmit and receive information directly to and from an interconnect 410 (e.g., I/O device adapter) through the DAI interface 408. The information coming from the interconnect 410 is routed directly to a process 402 or 404 by use of virtual hardware and registers, rather than using a traditional operating system interface 406.

## Alteon transfers data to applications in the host without headers

### Gigabi **Techni**

### **Achievina**

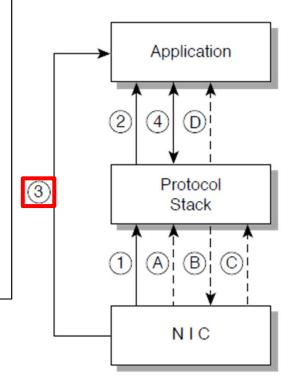

### Table 4. Steps in Data Reception using Second Generation NIC

### **Data Steps Control Steps**

- 1. The NIC moves the first 64 bytes of the packet A. The NIC notifies the stack that it has moved 64 to the protocol stack through a pre-allocated buffer. The first 64 bytes includes the header information and some data.

- bytes of data by issuing an interrupt.

- 2. The protocol stack moves any data from the initial 64 bytes (minus the header) to the

- B. The protocol stack analyzes the headers and tells the NIC where in application memory to put the remaining data from the packet.

- 3. The NIC moves the rest of the data into application memory. If application memory is not accessible, then an intermediate buffer is used and the data is copied to the application memory by the host in Step 4.

application memory.

- C. The NIC tells the stack that it has finished moving the rest of the data packet into application memory by issuing an interrupt.

- 4. The protocol stack performs a checksum on the packet in the application memory space.

- D. The protocol stack informs the application that data has arrived.

Alteon Networks, Inc. 6351 San Ignacio Avenue San Jose, CA 95119

1-408-574-5500

First Edition September 1996

Paper 4 (241 Petition) at 57; Ex. 1003.124 (Horst Decl.) at A-15;

Ex. 1033.021 (Alteon).

## 241 Patent: Disputes (Receive Claims)

- a. The combination of Erickson, Tanenbaum96 and Alteon discloses the limitations of claims 1, 2-8, 18, 22, and 23 of the 241 Patent

- i. The prior art discloses validation of network and transport layer headers "without an interrupt dividing the processing" (claim 1)

- ii. The prior art discloses sending the data from each packet to a destination in memory without sending any of the headers (claim 1)

- iii. The prior art discloses processing MAC layer headers without an interrupt (claim 2)

- iv. The prior art discloses processing an upper layer header by a second mechanism (claim 3)

- v. The prior art discloses sorting the packets by classifying each as having IP and TCP headers (claim 6)

### 241 Patent: Claim 2

- (54) FAST-PATH APPARATUS FOR RECEIVING DATA CORRESPONDING TO A TCP CONNECTION

- (75) Inventors: Laurence B. Boucher, Saratoga, CA (US); Stephene L. J. Bilghtman, San Jose, CA (US); Peter K. Craft, San Francisco, CA (US); David A. Higgen, Saratoga, CA (US); Clive M. Philbrick, San Jose, CA (US); Clive M. Philbrick, San Jose, CA (US)

- (73) Assignee: Alacritech, Inc., San Jose, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 879 days.

- (21) Appl. No.: 10/260,878

- (22) Filed: Sep. 27, 2002

- (65) **Prior Publication Data**US 2004/0064578 A1 Apr. 1, 2004

- - References Cited

### U.S. PATENT DOCUMENTS

| 4,366,538 | Α | 12/1982 | Johnson et al | 364/200 |

|-----------|---|---------|---------------|---------|

| 4,485,455 | A | 11/1984 | Boone et al   | 364/900 |

| 4,485,460 | A | 11/1984 | Stambaugh     | 365/203 |

| 4,589,063 | A | 5/1986  | Shah et al    | 710/8   |

| 4.700.185 | Α | 10/1987 | Balph et al.  | 370/451 |

(10) Patent No.: US 7,337,241 B2 (45) Date of Patent: Feb. 26, 2008

2. The method of claim 1, wherein processing the packets by a first mechanism further comprises:

processing the media access control layer header for each packet without an interrupt dividing the processing of the media access control layer header and the network layer header.

for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasts than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

### 24 Claims, 89 Drawing Sheets

Ex. 1001.142 (241 Patent), Claim 2.

## Erickson teaches that the MAC layer header is processed on the adapter

|        |     | FIG        | . 6       |                                                    |

|--------|-----|------------|-----------|----------------------------------------------------|

| Hex    | Dec |            |           | _602                                               |

| 0      | 0   | Ethernet   | 01        | Target Ethernet Address                            |

| 1      | 1   | Header     | 02        | (6 bytes)                                          |

| 2      | 2   | (14 bytes) | 03        | to plyings                                         |

| 3      | 3   | (14 Dyles) | 03        | 1                                                  |

| 4      | 4   |            | 05        | 1                                                  |

|        | -   |            | 06        | 1                                                  |

| 5<br>6 | 5   |            | 07        | Source Ethernet Address                            |

| 7      | 7   |            | 08        | (6 bytes)                                          |

| 8      | 8   | 604        | 09        | (U D)(es)                                          |

| 9      | 9   | 904        | 0a        | 1                                                  |

|        |     |            |           |                                                    |

| a      | 10  |            | 0b        |                                                    |

| b      | 11  |            | 0c        | Protocol Type (0x0800 = IP)                        |

| C      | 12  |            | 08        | Protocol Type (uxusuu = IP)                        |

| d      | 13  | IP         | 00        | Version - 4 ID Heades Len (Marde) - 5              |

| e      | 14  |            | 45        | Version = 4, IP Header Len (Words) = 5             |

| f      | 15  | Header     | 00        | Service Type                                       |

| 10     | 16  | (20 bytes) | 00        | Total Length = 0x001d (29 bytes: 20-byte IP Header |

| 11     | 17  | 1          | 1d        | plus 8-byte UDP header plus 1-byte user data)      |

| 12     | 18  | l          | e0_       | Datagram Id = 0xe0a1                               |

| 13     | 19  |            | <u>a1</u> |                                                    |

| 14     | 20  | 1          | 40        | Flag 0x4 DO_NOT_FRAGMENT                           |

| 15     | 21  |            | 00        | Fragment Offset = 0x000                            |

| 16     | 22  |            | 40        | Time-to-Live = 0x40                                |

| 17     | 23  | 606        | 11        | IP Protocol = 0x11 (UDP)                           |

| 18     | 24  | 000        | da        | IP Header Checksum = 0xda1b                        |

| 19     | 25  |            | 1b        |                                                    |

| 1a     | 26  | 1          | 80        | IP Address of Source = 128.1.192.7                 |

| 1b     | 27  |            | 01_       | ]                                                  |

| 1c     | 28  |            | c0        | ]                                                  |

| 1d     | 29  | 1          | 07_       |                                                    |

| 1e     | 30  |            | 80        | IP Address of Destination = 128.1.192.8            |

| 1f     | 31  |            | 01        | 1                                                  |

| 20     | 32  |            | c0        | ]                                                  |

| 21     | 33  |            | 08        |                                                    |

| 22     | 34  | UDP        | 00        | Source Port = 0x0007 (echo datagram)               |

| 23     | 35  | Header     | 07        |                                                    |

| 24     | 36  | (8 bytes)  | 30        | Destination Port = 0x3018                          |

| 25     | 37  |            | 18        |                                                    |

| 26     | 38  | 000        | 00        | UDP Length = 0x0009 (8-byte UDP Header plus        |

| 27     | 39  | 608        | 09        | 1-byte user data)                                  |

| 28     | 40  |            | 0c        | UDP Checksum = 0x0cf8                              |

| 29     | 41  |            | f8        | 1                                                  |

| 2a     | 42  | User 610   | 67        | 1 byte user datagram = "g"                         |

|        |     | Data 610   |           | 1                                                  |

|        |     | (Variable) |           | 1                                                  |

|        |     |            |           |                                                    |

Ex. 1005.007 (Erickson), Fig. 6.

## 241 Patent: Disputes (Receive Claims)

- a) The combination of Erickson, Tanenbaum96 and Alteon discloses the limitations of claims 1, 2-8, 18, 22, and 23 of the 241 Patent

- i. The prior art discloses validation of network and transport layer headers "without an interrupt dividing the processing" (claim 1)

- ii. The prior art discloses sending the data from each packet to a destination in memory without sending any of the headers (claim 1)

- iii. The prior art discloses processing MAC layer headers without an interrupt (claim 2)

- iv. The prior art discloses processing an upper layer header by a second mechanism (claim 3)

- v. The prior art discloses sorting the packets by classifying each as having IP and TCP headers (claim 6)

### 241 Patent: Claim 3

### (12) United States Patent Boucher et al.

- (54) FAST-PATH APPARATUS FOR RECEIVING DATA CORRESPONDING TO A TCP CONNECTION

- (75) Inventors: Laurence B. Boucher, Saratoga, CA (US); Stephen E. J. Blightman, San Jose, CA (US); Peter K. Craft, San Francisco, CA (US); David A. Higgen, Saratoga, CA (US); Citwe M. Philbrick, San Jose, CA (US); Daryl D. Starr, Milpitas, CA (US)

- (73) Assignee: Alacritech, Inc., San Jose, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 879 days.

- (21) Appl. No.: 10/260,878

- (22) Filed: Sep. 27, 2002

- (65) **Prior Publication Data**US 2004/0064578 A1 Apr. 1, 2004

- | Int. Cl. | G06F 15/16 | (2006.01) | 709/250 | (58) | Field of Classification Search | 709/250 | See application file for complete search history.

- 56) References Cited

### U.S. PATENT DOCUMENTS

| 4,366,538 | Α | 12/1982 | Johnson et al | 364/200 |

|-----------|---|---------|---------------|---------|

| 4,485,455 | Α | 11/1984 | Boone et al   | 364/900 |

| 4,485,460 | Α | 11/1984 | Stambaugh     | 365/203 |

| 4,589,063 | Α | 5/1986  | Shah et al    | 710/8   |

|           |   | 10/1007 | D. I. I I     | 270/451 |

(10) Patent No.:

US 7,337,241 B2

(45) Date of Patent:

Feb. 26, 2008

3. The method of claim 1, further comprising:

processing an upper layer header of at least one of the packets by a second mechanism, thereby determining the destination, wherein the upper layer header corresponds to a protocol layer above the transport layer.

puter. The INIC provides a fast-path that avoids protocol processing for most large multi-packer messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the BNIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

### 24 Claims, 89 Drawing Sheets

Ex. 1001.142 (241 Patent), Claim 3.

## Tanenbaum96: The processing of application headers

NFORMATION SUPER

Paper 4 (241 Petition) at 60; Ex. 1006.055 (Tanenbaum96).

### 241 Patent: Disputes (Receive Claims)

- a) The combination of Erickson, Tanenbaum96 and Alteon discloses the limitations of claims 1, 2-8, 18, 22, and 23 of the 241 Patent

- i. The prior art discloses validation of network and transport layer headers "without an interrupt dividing the processing" (claim 1)

- ii. The prior art discloses sending the data from each packet to a destination in memory without sending any of the headers (claim 1)

- iii. The prior art discloses processing MAC layer headers without an interrupt (claim 2)

- iv. The prior art discloses processing an upper layer header by a second mechanism (claim 3)

- v. The prior art discloses sorting the packets by classifying each as having IP and TCP headers (claim 6)

### 241 Patent: Claim 6

US 7,337,241 B2 (10) Patent No.: Feb. 26, 2008 4,991,133 A 2/1991 Davis et al. .....

6. The method of claim 1, wherein sorting the packets includes classifying each of the packets of the first type as having an Internet Protocol (IP) header and a Transmission Control Protocol (TCP).

host for those message packets that are chosen for proces ing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex com-

Ex. 1001.143 (241 Patent), Claim 6.

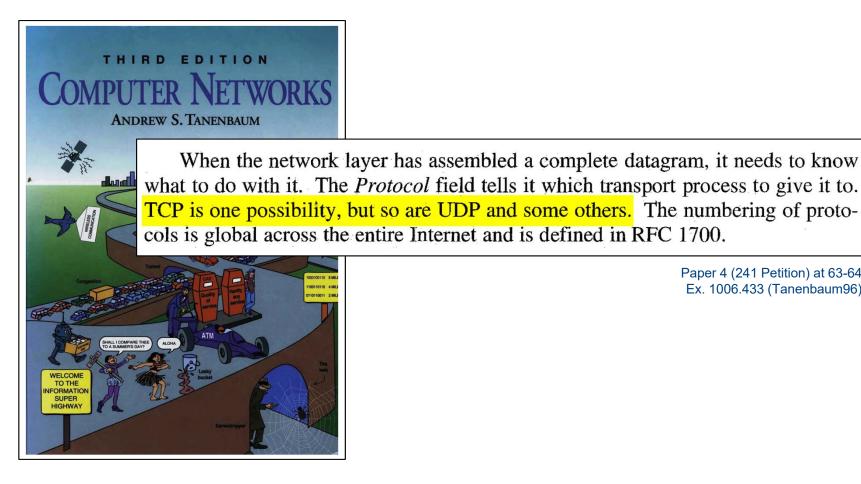

## Tanenbaum96: Parsing the header to determine packet's protocol

Paper 4 (241 Petition) at 63-64; Ex. 1006.433 (Tanenbaum96).

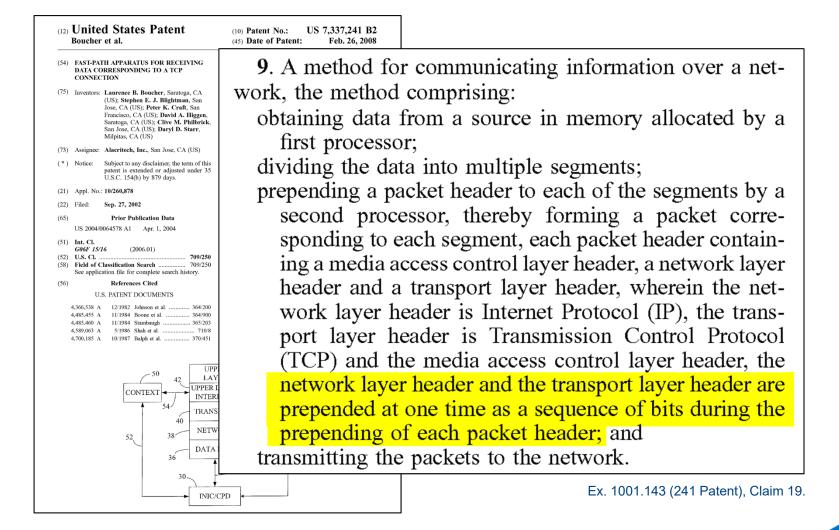

### 241 Patent: Disputes (Transmit Claims)

- b) Erickson in view of Tanenbaum96 discloses the limitations of claims 9, 10-16, 17, 19-21, and 21 of the 241 Patent

- i. The prior art discloses "prepending the MAC, network, and transport layer headers at one time as a sequence of bits" (claim 9)

- ii. The prior art discloses prepending each packet header without an interrupt dividing the prepending of the MAC, IP, and TCP headers (claim 17)

- iii. The prior art discloses dividing the data into multiple segments and prepending a packet header to each of the segments by a second processor/mechanism (claims 9 and 17)

### 241 Patent: Claim 19

# Erickson teaches the use of a template to create headers

It would have been obvious to prepend the populated header to the data at one time

In the present application, the access privileges given to the user processes are very narrow. Each user process has basically pre-negotiated almost everything about the datagram 602, except the actual user data 610. This means most of the fields in the three header areas 604, 606, and 608 are predetermined.

Ex. 1005.007, .011 (Erickson) at Fig. 6, 6:57-62

Paper 45 (241 Reply) at 13-14;

Paper 4 (241 Petition) at 73-74;

Ex. 1003.075-79,.136-.141 (Horst Decl.) at ¶¶ 131-136, A-16 – A-31.

## Dr. Almeroth's interpretation would result in an invalid packet

3

2

1

708 plus the user data." (*Id.* at 8:24-26.) When building a packet for transmission, *Erickson* thus appears to first prepends the Ethernet header 704 to the user data, then prepends the IP header 706 to the Ethernet header, and finally prepends the UDP header 708 to the IP header. In other words, due to the serial nature of the execution of the udpscript() procedure, *Erickson* appears to also likely builds the UDP datagram *in a traditional serial fashion*, rather than prepending the MAC, transport, and network headers "at one time" as required by claim 9.

| Hex Dec  | FIG        | . 6 | _602                                               |

|----------|------------|-----|----------------------------------------------------|

|          | Ethernet   | 01  | Target Ethernet Address                            |

|          | Header     | 02  | (6 bytes)                                          |

|          | (14 bytes) | 03  | (0 0)(00)                                          |

|          | (14 dyled) | 04  | 1                                                  |

|          |            | 05  | 1                                                  |

| (1)      |            | 06  |                                                    |

|          |            | 07  | Source Ethernet Address                            |

|          |            | 08  | (6 bytes)                                          |

|          | 604        | 09  | (,,                                                |

|          |            | 0a  |                                                    |

|          | Ü          | 0b  | 1                                                  |

|          |            | 0c  | 1                                                  |

|          |            | 08  | Protocol Type (0x0800 = IP)                        |

|          |            | 00  |                                                    |

|          | IP         | 45  | Version = 4, IP Header Len (Words) = 5             |

|          | Header     | 00  | Service Type                                       |

|          | (20 bytes) | 00  | Total Length = 0x001d (29 bytes: 20-byte IP Header |

| _        |            | 1d  | plus 8-byte UDP header plus 1-byte user data)      |

|          |            | e0  | Datagram Id = 0xe0a1                               |

| (2)      |            | a1  |                                                    |

| <b>(</b> |            | 40  | Flag 0x4 DO_NOT_FRAGMENT                           |

|          |            | 00_ | Fragment Offset = 0x000                            |

|          |            | 40  | Time-to-Live = 0x40                                |

|          | 606        | 11  | IP Protocol = 0x11 (UDP)                           |

|          | 000        | da  | IP Header Checksum = 0xda1b                        |

|          |            | 1b  |                                                    |

|          |            | 80  | IP Address of Source = 128.1.192.7                 |

|          |            | 01  |                                                    |

|          |            | c0  |                                                    |

|          |            | 07  | IP Address of Destination = 128.1.192.8            |

|          |            | 80  | IP Address of Destination = 128.1.192.8            |

|          |            | cO  |                                                    |

|          |            | 08  |                                                    |

|          | UDP        | 00  | Source Port = 0x0007 (echo datagram)               |

|          | Header     | 07  | Source Fort = 0x0007 (echo datagram)               |

| (3)      | (8 bytes)  | 30  | Destination Port = 0x3018                          |

|          | to olitest | 18  | Destination of a 0x0010                            |

|          |            | 00  | UDP Length = 0x0009 (8-byte UDP Header plus        |

|          | 608        | 09  | 1-byte user data)                                  |

|          |            | 0c  | UDP Checksum = 0x0cf8                              |

|          |            | f8  |                                                    |

|          | User 610   | 67  | 1 byte user datagram = "g"                         |

|          | Data 510   |     |                                                    |

|          | (Mariahla) |     |                                                    |

Ex. 2026.068 (Almeroth) at ¶ 134; Ex. 1005.007 (Erickson) Fig. 6, 7:50-64; Paper 45 (241 Reply) at 13-14.

# Erickson teaches the use of a template to create headers

Trials@uspto.gov

Entered: November 30, 2017

UNITED STATES PATENT AND TRADEN

BEFORE THE PATENT TRIAL AND APP.

INTEL CORPORATION, Petitioner.

v.

ALACRITECH, INC., Patent Owner.

Case IPR2017-01392 Patent 7,337,241 B2

Before STEPHEN C. SIU, DANIEL N. FISHMAN, WILLIAM M. FINK, Administrative Patent Judges.

FISHMAN, Administrative Patent Judge.

packet. Id. at 7:46–47; see also id. at 6:48–56. We agree with Petitioner

that the header and data to be transmitted, both stored in the memory of the

manners—either the header is prepended to the data or the data is appended

network interface device, would be combined in one of two obvious

to the header. Given the small number of known solutions to combining the

header and data, it would have been obvious to try prepending the header to

the data to transmit the packet. KSR Int'l Co. v. Teleflex Inc., 550 U.S. 398,

DECISION Institution of Inter Partes Review 37 C.F.R. § 42.108

I. INTRODUCTION

Intel Corporation ("Petitioner") requests inter partes review of claims all claims (1-24) of U.S. Patent No. 7,337,241 B2 ("the '241 patent," Ex. Paper 11 (Institution Decision) at 17-18.

### 241 Patent: Disputes (Transmit Claims)

- b) Erickson in view of Tanenbaum96 discloses the limitations of claims 9, 10-16, 17, 19-21, and 21 of the 241 Patent

- The prior art discloses "prepending the MAC, network, and transport layer headers at one time as a sequence of bits" (claim 9)

- ii. The prior art discloses prepending each packet header without an interrupt dividing the prepending of the MAC, IP, and TCP headers (claim 17)