# Intel Corporation, Cavium, Inc., Wistron Corporation, and Dell Inc.

V.

## Alacritech, Inc.

Case Nos.: IPR2017-01309, IPR2017-01718, IPR2018-00327, and IPR2018-00371

U.S. Patent No. 7,237,036

Case Nos.: IPR2017-01406, IPR2017-01707, IPR2018-00329, and IPR2018-00375

U.S. Patent No. 7,673,072

Patent Owner's Demonstratives

Hearing: September 13, 2018

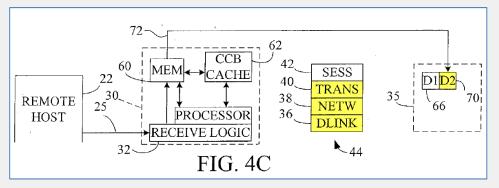

### Overview of the '036 Patent

data from the message to be processed via a fast-path which

accesses message data directly at its source or delivers it

to its intended destination. This fast-path bypasses

(21) Appl. No.: 10/260,112

(22) Filed:

Sep. 27, 2002 Prior Publication Data

tative control instructions for a given message that allow US 2004/0073703 A1 Apr. 15, 200

Related U.S. Application Data

(63) Continuation of application No. 10/092 Mar. 6, 2002, now Pat. No. 6,591,300

(Continued)

(60) Provisional application No. 60/098,296 27, 1998, provisional application No filed on Oct. 14, 1997.

G06F 13/38 G06F 15/17

(2006.01) (2006.01)

709/245; 709/236; 709/230; (52) U.S. Cl. ... 370/474; 370/396; 370/469

(58) Field of Classification Search 709/245 709/236, 230, 202; 370/474, 230, 396, 469; 707/2-4, 10; 712/19, 52

See application file for complete search history.

much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes

(74) Attornev, Agent, or Firm-Mark Lauer, Silicon E

22 Claims, 89 Drawing Sheets

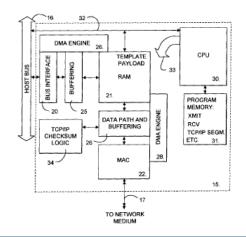

'036 Patent (IPR2017-01391 Ex. 1001)

Ex. 1001.096 ('036 Patent)

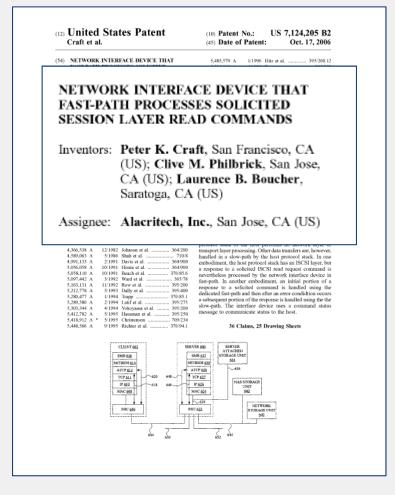

### Overview of the '072 Patent

(45) **Da**i

said

part

2001

2001

part (

2000

09/67

6.807

No. 0 6,427

6,470

Provi

(51) Int. 0

(52) U.S. O

(58) Field

See a

4,366,53

4,485,46

60

55

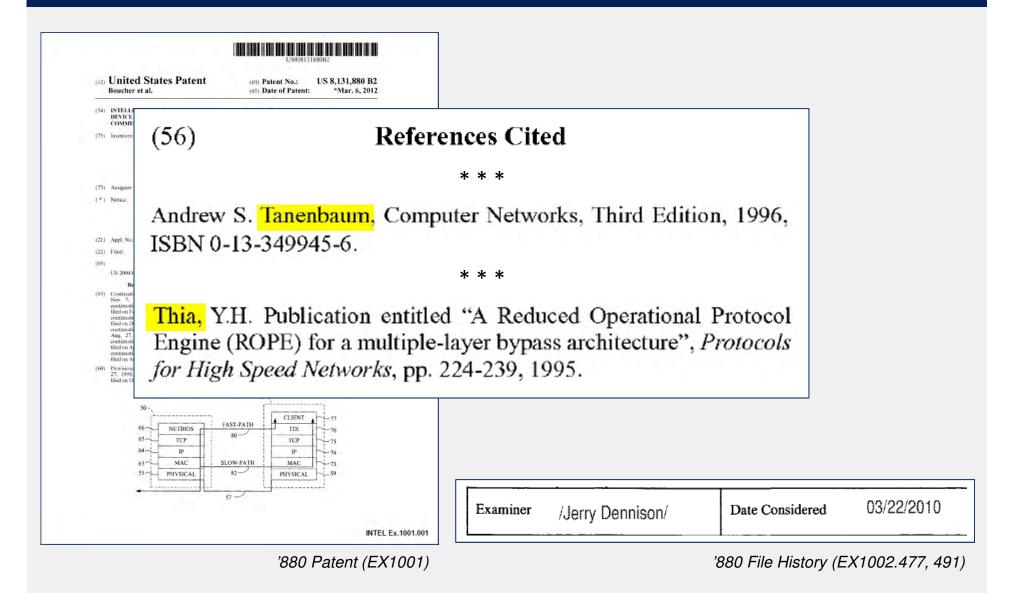

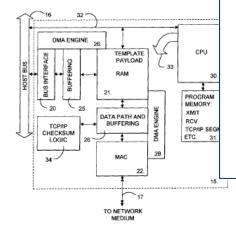

(12) United States Patent Boucher et al.

(54) FAST-PATH APPARATUS FOR TRANSMITTING DATA CORRESPONDING TO A TCP CONNECTION

(75) Inventors: Laurence B. Boucher, Saratoga, CA (US); Stephen E. J. Blightman, San Jose, CA (US); Peter K. Craft, San Francisco, CA (US); David A. Higgen, Saratoga, CA (US); Clive M. Philbrick, San Jose, CA (US); Davyl D. Starr, Milpitas, CA (US)

(73) Assignce: Alacritech, Inc., San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 435 days.

(21) Appl. No.: 11/821,820(22) Filed: Jun. 25, 2007

(65) Prior Publication Data

US 2008/0126553 A1 May 29, 2008

### Related U.S. Application Data

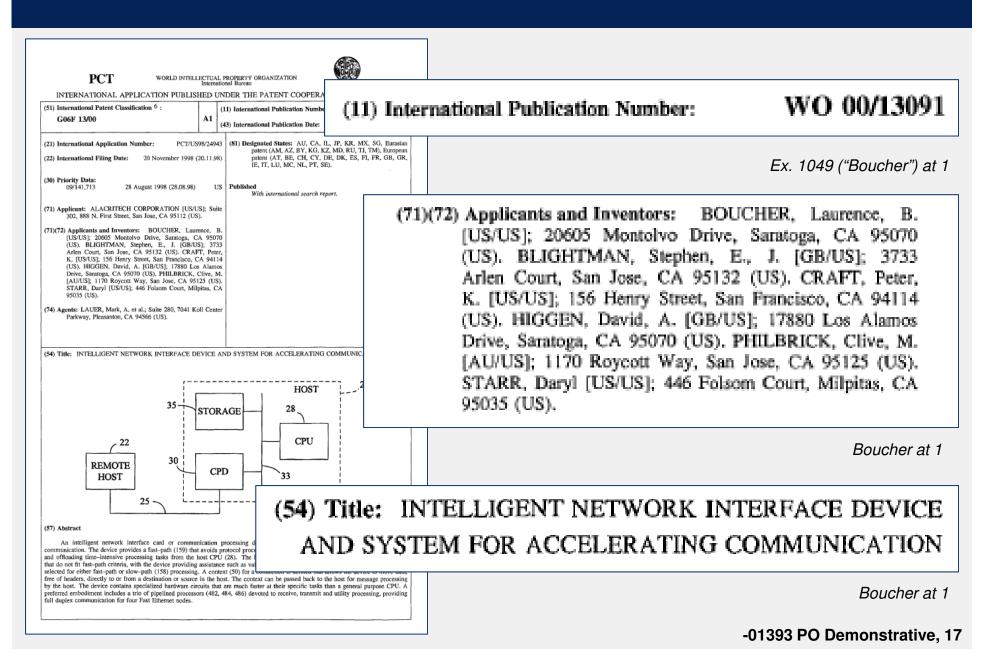

(63) Continuation of application No. 10/260,112, filed on Sep. 27, 2002, now Pat. No. 7,237,036, which is a continuation of application No. 10/092,967, filed on Mar. 6, 2002, now Pat. No. 6,591,302, which is a continuation-in-part of application No. 10/023,240, filed on Dec. 17, 2001, now Pat. No. 6,965,941, which is a continuation-in-part of application No. 09/464, 283, filed on Dec. 15, 1999, now Pat. No. 6,427,173, which is a continuation-in-part of application No. 09/439,603, filed on Nov. 12, 1999, now Pat. No. 6,247,060, which is a continuation-in-part of application No. 09/067,544, filed on Apr. 27, 1998, now Pat. No. 6,226,680, said application No. 10/260,112 is a continuation-in-part of application No. 09/384,792, filed on Aug. 27, 1999, now Pat. No. 6,434,620, which is a continuation-in-part of application No. 09/141, 713, filed on Aug. 28, 1998, now Pat. No. 6,389,479,

(54)

# FAST-PATH APPARATUS FOR TRANSMITTING DATA CORRESPONDING TO A TCP CONNECTION

2001, how Pat. No. 7,076,508, and a continuation-inport of application No. 99/801,488, filed on Mar. 7, 2001, now Pat. No. 6,687,758, and a continuation-inpart of application No. 09/789,366, filed on Feb. 20, 2001, now Pat. No. 6,757,746, and a continuation-in-

Ex. 1001.001 ('072 Patent)

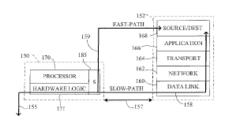

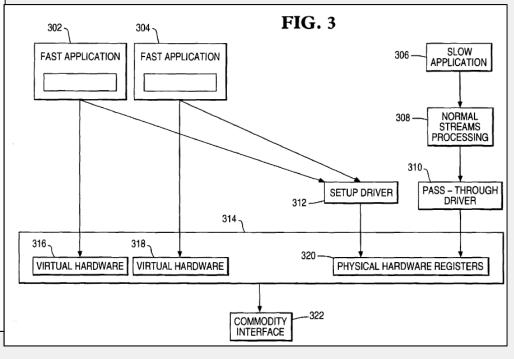

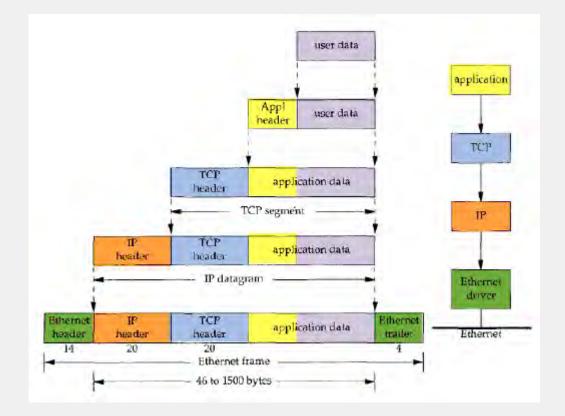

The transmit case works in much the same fashion. In slow-path mode the packets are given to the INIC with all of the headers attached. The INIC simply sends these packets out as if it were a dumb NIC. In fast-path mode, the host gives raw data to the INIC which it must carve into MSS sized segments, add headers to the data, perform checksums on the segment, and then send it out on the wire.

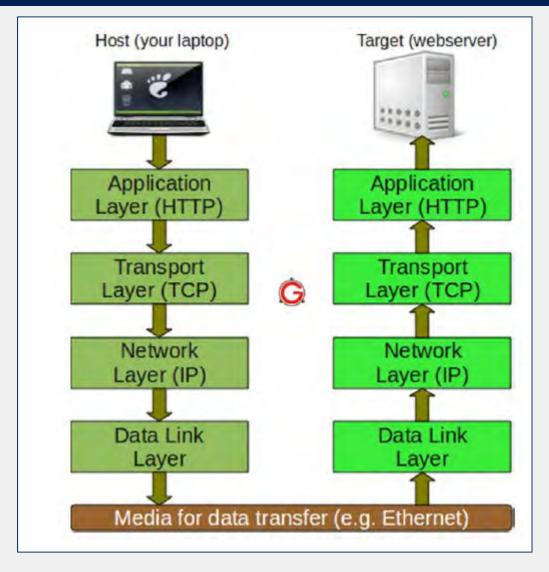

CONTEXT

40

UPFER

LAYER

LAYER

UPFER LAYER

UPFER LAYER

NETFACE

TRANSPORT

NETWORK

36

DATA LINK

36

DATA LINK

36

NETWORK

36

N

'072 Patent (IPR2017-01406 Ex. 1001)

Ex. 1001.112 ('072 Patent)

## Challenged Claims of the '036 Patent (Claims 1-7)

- 1. A device for use with a first apparatus that is connectable to a second apparatus, the first apparatus containing a memory and a first processor operating a stack of protocol processing layers that create a context for communication, the context including a media access control (MAC) layer address, an Internet Protocol (IP) address and Transmission Control Protocol (TCP) state information, the device comprising:

- a communication processing mechanism connected to the first processor, said communication processing mechanism containing a second processor running instructions to process a message packet such that the context is employed to transfer data contained in said packet to the first apparatus memory and the TCP state information is updated by said second processor.

Ex. 1001.142-43 ('036 Patent)

## Challenged Claims of the '072 Patent (Claims 1-21)

### 1. A method comprising:

establishing, at a host computer, a transport layer connection, including creating a context that includes protocol header information for the connection;

transferring the protocol header information to an interface device;

transferring data from the network host to the interface device, after transferring the protocol header information to the interface device;

dividing, by the interface device, the data into segments; creating headers for the segments, by the interface device, from a template header containing the protocol header information; and

prepending the headers to the segments to form transmit packets.

Ex. 1001.142 ('072 Patent)

## Challenged Claims of the '072 Patent (Claims 1-21)

### 9. A method comprising:

creating, at a computer, a context including protocol information and status information for a network connection, the protocol information providing a template header for the network connection;

transferring the protocol information and status information to an interface device;

transferring data from the computer to the interface device, after transferring the protocol information and status information to the interface device;

dividing, by the interface device, the data into segments; creating headers for the segments, by the interface device, from the template header;

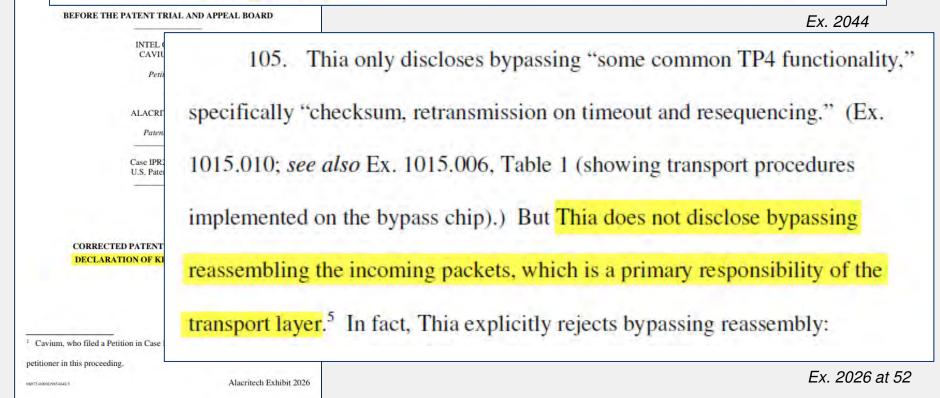

prepending the headers to the segments to form packets; and

transmitting the packets on a network.

Ex. 1001.142 ('072 Patent)

## Challenged Claims of the '072 Patent (Claims 1-21)

### 15. A method comprising:

establishing, at a computer, a Transmission Control Protocol (TCP) connection corresponding to a context that includes status information and Internet Protocol (IP) addresses and TCP ports for the connection;

transferring the context to an interface device;

transferring data from the network host to the interface device;

dividing, by the interface device, the data into segments; creating headers for the segments, by the interface device, from a template header that includes the IP addresses and TCP ports; and

prepending the headers to the segments to form transmit packets.

Ex. 1001.142 ('072 Patent)

## Overview of Instituted Grounds

## '036 Patent

| <b>Challenged Claims</b> | 103(a) References      |

|--------------------------|------------------------|

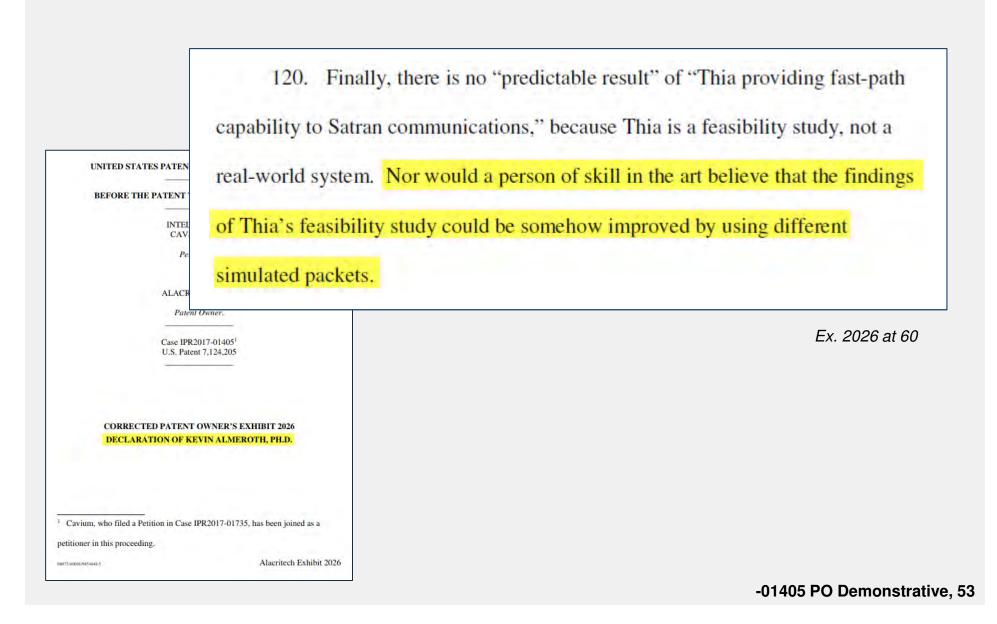

| 1-7                      | Erickson and Tanenbaum |

## '072 Patent

| Challenged Claims | 103(a) References      |

|-------------------|------------------------|

| 1-21              | Erickson and Tanenbaum |

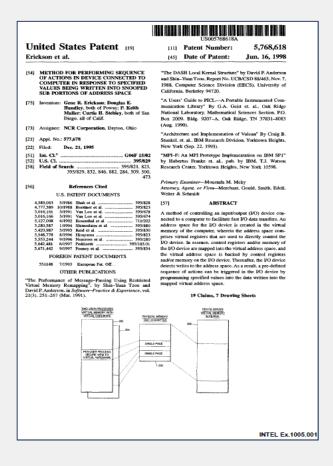

### Overview of Erickson

### United States Patent [19]

[54] METHOD FOR PERFORMING SEQUENCE

OF ACTIONS IN DEVICE CONNECTED TO COMPUTER IN RESPONSE TO SPECIFIED VALUES BEING WRITTEN INTO SNOOPED SUB PORTIONS OF ADDRESS SPACE [75] Inventors: Gene R. Erickson; Douglas E.

Hundley, both of Poway; P. Keith Muller; Curtis H. Stehley, both of San Diego, all of Calif.

[73] Assignee: NCR Corporation. Dayton. Ohio

[21] Appl. No.: 577,678 1221 Filed: Dec. 21, 1995

Erickson et al.

[51] Int. CL6 ... . G06F 15/02 [52] U.S. Cl. .

. 395/821, 823, 395/829, 832, 846, 882, 284, 309, 500,

### References Cited U.S. PATENT DOCUMENTS

| 4,589,063 | 5/1986  | Shah et al       | 395/82  |

|-----------|---------|------------------|---------|

| 4,777,589 | 10/1988 | Boettner et al.  | 395/82  |

| 5,016,161 | 5/1991  | Van Loo et al    | 395/67  |

| 5,016,166 | 5/1991  | Van Loo et al    | 395/67  |

| 5,127,098 | 6/1992  | Rosenthal et al  | 711/200 |

| 5,280,587 | 1/1994  | Shimodaira et al | 395/88  |

| 5,420,987 | 5/1995  | Reid et al.      | 395/83  |

| 5,548,778 | 8/1996  | Hirayama         | 395/82  |

| 5,553,244 |         | Norcross et al.  |         |

| 5,642,481 | 6/1997  | Pedrizetti       | 5/185.0 |

| 5,671,442 | 9/1997  | Forney et al     | 395/83- |

FOREIGN PATENT DOCUMENTS

551148 7/1993 European Pat. Off. OTHER PUBLICATIONS

"The Performance of Message-Passing Using Restricted Virtual Memory Remapping", by Shin-Yuan Tzou and David P. Anderson, in Software-Practice & Experience, vol. 21(3), 251-267 (Mar. 1991).

United States Patent [19]

[54]

5,768,618 **Patent Number:** [11]

**Date of Patent:**

Jun. 16, 1998

"The DASH Local Kernal Structure" by David P. Anderson and Shin-Yuan Tzou, Report No. UCB/CSD 88/463, Nov. 7, 1988, Computer Science Division (EECS), University of California, Berkeley 94720.

Erickson et al.

"A Users' Guide to PICL.-A Portable Instrumented Communication Library" By G.A. Geist et. al., Oak Ridge National Laboratory, Mathematical Sciences Section, P.O. Box 2009. Bldg. 9207-A. Oak Ridge, TN 37831-8083

"Architecture and Implementation of Vulcan" By Craig B. Stunkel, et. al., IBM Research Division, Yorktown Heights, New York (Sep. 22, 1993).

"MPI-F: An MPI Prototype Implementation on IBM SP1" by Hubertus Franke et. al., pub. by IBM, T.J. Watson Research Center, Yorktown Heights, New York 10598.

Primary Examiner-Moustafa M. Meky Attorney, Agent, or Firm-Merchant, Gould, Smith, Edell, Welter & Schmidt

### ABSTRACT

A method of controlling an input/output (I/O) device connected to a computer to facilitate fast I/O data transfers. An address space for the I/O device is created in the virtual memory of the computer, wherein the address space comprises virtual registers that are used to directly control the I/O device. In essence, control registers and/or memory of the I/O device are mapped into the virtual address space, and the virtual address space is backed by control registers and/or memory on the I/O device. Thereafter, the I/O device detects writes to the address space. As a result, a pre-defined sequence of actions can be triggered in the I/O device by programming specified values into the data written into the mapped virtual address space.

### 19 Claims, 7 Drawing Sheets

Erickson (Ex. 1005)

METHOD FOR PERFORMING SEQUENCE OF ACTIONS IN DEVICE CONNECTED TO COMPUTER IN RESPONSE TO SPECIFIED VALUES BEING WRITTEN INTO SNOOPED SUB PORTIONS OF ADDRESS SPACE

Ex. 1005.004

### Overview of Erickson

# United States Patent [19] Erickson et al. [54] METHOD FOR PERFORMING SEQUENCE OF ACTIONS IN DEVICE CONNECTED TO COMPUTER IN RESPONSE TO SPECIFIED VALUES BEING WITTEN INTO SNOOPED SUB PORTIONS OF ADDRESS SPACE

[75] Inventors: Gene R. Erickson; Dougfas E. Hundley, both of Poway; P. Keith Muller; Curtis H. Stehley, both of San Diego, all of Calif.

[73] Assignee: NCR Corporation. Dayton. Ohio

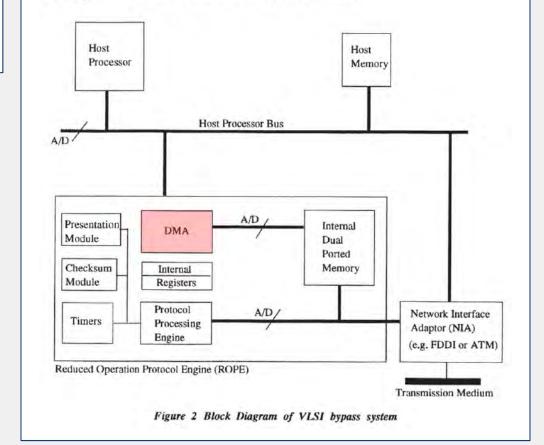

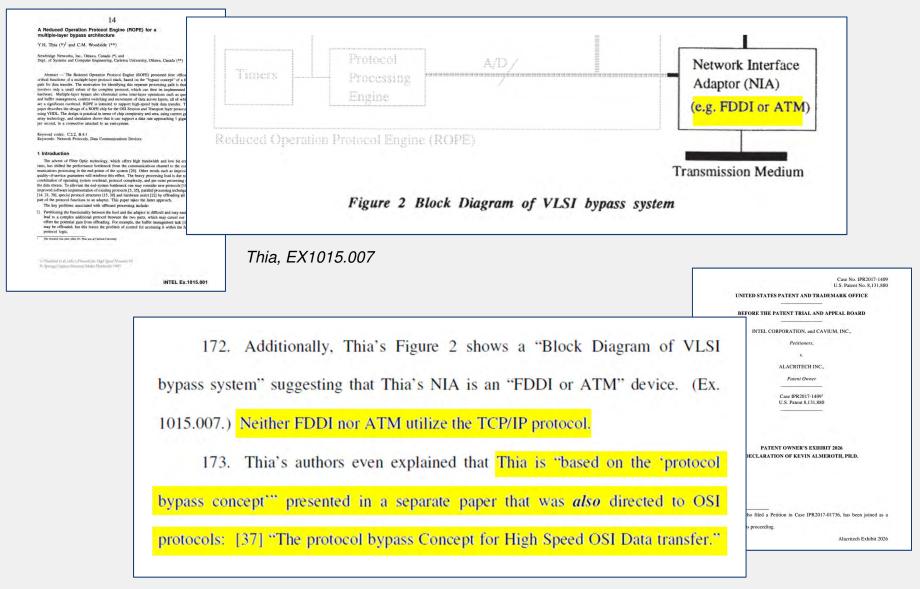

[21] Appl. No.: 577,678

| [22] | Filed: I             | ec. 21, 1995 |           |        |       |

|------|----------------------|--------------|-----------|--------|-------|

| [51] | Int. CL <sup>6</sup> |              |           | G06F   | 15/02 |

| [52] | U.S. Cl              |              |           | 39     | 5/829 |

| [58] | Field of Sea         |              |           |        |       |

| -    |                      | 205/020 021  | 044 000 0 | 04 200 | F00   |

### 6) References Cited U.S. PATENT DOCUMENTS

| 4,589,063 | 5/1986  | Shah et al       | 395/828  |

|-----------|---------|------------------|----------|

| 4,777,589 | 10/1988 | Boettner et al   | 395/823  |

| 5,016,161 | 5/1991  | Van Loo et al    | 395/678  |

| 5,016,166 | 5/1991  | Van Loo et al    | 395/674  |

| 5,127,098 | 6/1992  | Rosenthal et al  | 711/202  |

| 5,280,587 | 1/1994  | Shimodaira et al | 395/880  |

| 5,420,987 | 5/1995  | Reid et al.      | 395/830  |

| 5,548,778 | 8/1996  | Hirayama         | 395/823  |

| 5,553,244 | 9/1996  | Norcross et al.  | 395/280  |

| 5,642,481 | 6/1997  | Pedrizetti       | 5/185.01 |

| 5,671,442 | 9/1997  | Forney et al     | 395/834  |

|           |         |                  |          |

#### FOREIGN PATENT DOCUMENTS

551148 7/1993 European Pat. Off. .

OTHER PUBLICATIONS

"The Performance of Message-Passing Using Restricted Virtual Memory Remapping". by Shin-Yuan Tzou and David P. Anderson, in Software-Practice & Experience, vol. 21(3), 251-267 (Mar. 1991).

"The DASH Local Kernal Struct and Shin-Yuan Tzou, Report No. 1988, Computer Science Division California, Berkeley 94720.

[11] Patent Number:

[45] Date of Patent:

"A Users' Guide to PICL.—A Pomunication Library" By G.A. (

National Laboratory, Mathematic

Box 2009, Bldg, 9207-A. Oak

(Aug. 1990).

"Architecture and Implementation Stunkel, et. al., IBM Research Div New York (Sep. 22, 1993).

"MPI-F: An MPI Prototype Impl by Hubertus Franke et. al., pu Research Center, Yorktown Heigh

Primary Examiner—Moustafa M. Attorney, Agent, or Firm—Merch Welter & Schmidt

[57] ABSTRAC

A method of controlling an input nected to a computer to facilitate address space for the I/O device memory of the computer, whereit perises virtual registers that are us I/O device. In essence, control re the I/O device are mapped into the virtual address space is bax and/or memory on the I/O device, cleectes writes to the address space sequence of actions can be triggly programming specified values into mapped virtual address space.

19 Claims, 7 Deax

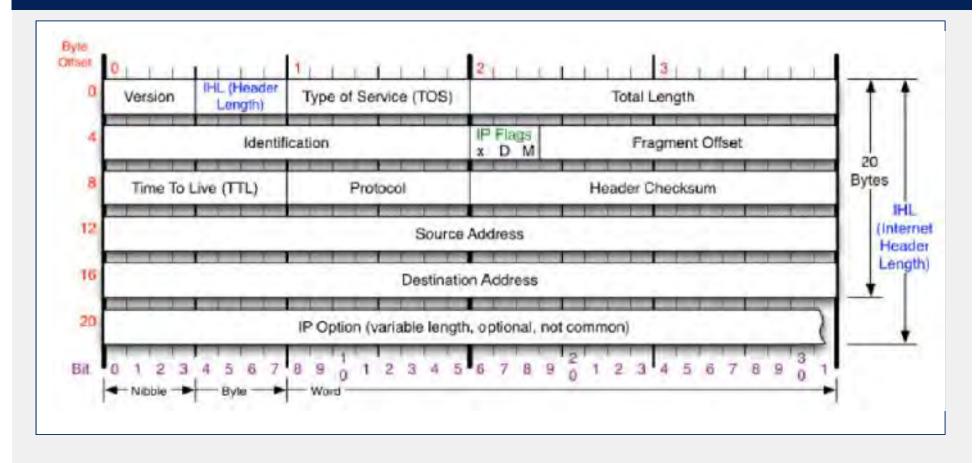

Within the udpscript procedure described above, the nextid() function provides a monotonically increasing 16-bit counter required by the IP protocol. The ipchecksum() function performs a checksum for the IP Header 706 portion of the datagram 702. The vtophys() function performs a translation of the user-provided virtual address into a physical address usable by the adapter. In all likelihood, the adapter would have a very limited knowledge of the user process' virtual address space, probably only knowing how to map virtual-to-physical for a very limited range, maybe as small as a single page. Pages in the user process' virtual address space for such buffers would need to be fixed. The udpscript procedure would need to be enhanced if the user data were allowed to span page boundaries. The udpchecksum() procedure generates a checksum value for both the UDP Header 708 plus the user data (not shown).

Ex. 1005 at 8:20-24

Erickson (Ex. 1005)

### Overview of Erickson

[75] Inventors: Gene R. Erickson; Douglas E. Hundley, both of Powny; P. Keith Muller; Curtis H. Stehley, both of San Diego, all of Calif.

[73] Assignee: NCR Corporation. Dayton, Ohio

| [22] | Filed:   | Dec. 2 | 1, 1995              |               |

|------|----------|--------|----------------------|---------------|

| [51] | Int. CL  | 5      |                      | . G06F 15/02  |

| [52] | U.S. Cl. |        |                      | 395/829       |

| [58] | Field of |        |                      |               |

| -    |          | 395/8  | 29, 832, 846, 882, 2 | 84, 309, 500, |

#### References Cited

[21] Appl. No.: 577,678

#### U.S. PATENT DOCUMENTS 4,589,063 5/1986 Shah et al. ...

| 4,777,589 | 10/1988 | Boettner et al 395/823   |

|-----------|---------|--------------------------|

| 5,016,161 | 5/1991  | Van Loo et al            |

| 5,016,166 | 5/1991  | Van Loo et al 395/674    |

| 5,127,098 | 6/1992  | Rosenthal et al 711/202  |

| 5,280,587 | 1/1994  | Shimodaira et al 395/880 |

| 5,420,987 | 5/1995  | Reid et al               |

| 5,548,778 | 8/1996  | Hirayama 395/823         |

| 5,553,244 | 9/1996  | Norcross et al 395/280   |

| 5,642,481 | 6/1997  | Pedrizetti 395/185.01    |

| 5,671,442 | 9/1997  | Fomey et al              |

|           |         |                          |

### FOREIGN PATENT DOCUMENTS 551148 7/1993 European Pat. Off. .

OTHER PUBLICATIONS

The Performance of Message-Passing Using Restricted Virtual Memory Remapping", by Shin-Yuan Tzou and David P. Anderson, in Software-Practice & Experience, vol. 21(3), 251-267 (Mar. 1991).

"A Users' Guide to PICL-A Portable Instrumen munication Library" By G.A. Geist et. al., Oa National Laboratory, Mathematical Sciences Sect Box 2009. Bldg. 9207-A. Oak Ridge, TN 378

"Architecture and Implementation of Vulcan" By Stunkel, et. al., IBM Research Division, Yorktown New York (Sep. 22, 1993).

"MPI-F: An MPI Prototype Implementation on II by Hubertus Franke et. al., pub. by IBM, T.J. Research Center, Yorktown Heights, New York 10

Primary Examiner-Moustafa M. Meky Attorney, Agent, or Firm-Merchant, Gould. Smi Welter & Schmidt

### ABSTRACT

A method of controlling an input/output (I/O) dev nected to a computer to facilitate fast I/O data tran address space for the I/O device is created in th memory of the computer, wherein the address spi prises virtual registers that are used to directly or I/O device. In essence, control registers and/or me the I/O device are mapped into the virtual address s the virtual address space is backed by control and/or memory on the I/O device. Thereafter, the I/ detects writes to the address space. As a result, a presequence of actions can be triggered in the I/O of programming specified values into the data writte mapped virtual address space.

19 Claims, 7 Drawing Sheets

FIG. 7 is a block diagram illustrating a UDP datagram template 702 (without a user data area) residing in the LO device adapter's memory. The user process provides the starting address and the length for the user data in its virtual address space, and then "spanks" a GO register to trigger the I/O device adapter's execution of a predetermined script. The I/O device adapter stores the user data provided by the user process in the I/O device adapter's memory, and then transmits the completed UDP datagram 702 over the media.

An example of programming that triggers the I/O device adapter is provided below:

```

udpscript (void *USERDATA_ADDRESS,

USERDATA LENGTH.

template_t *template)

char *physaddress;

template->IP. TotalLength = sizeof (IPHeader) +

sizeof(UDPHeader) + USERDATA_LENGTH:

template -> IP.DatagramID = nextid();

ipchecksum (template);

template->UDPLength = sizeof (UDPHeader)

+ USERDATA_LENGTH;

physaddress = vtophys (USERDATA_ADDRESS,

USERDATA_LENGTH);

udpchecksum (physaddress, USERDATA_LENGTH, template);

```

Ex. 1005.012

Erickson (Ex. 1005)

### Overview of Tanenbaum

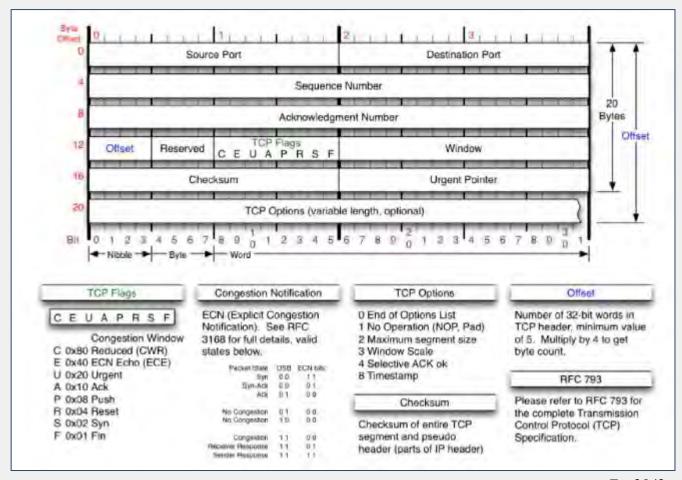

### 6.6.4. Fast TPDU Processing

The moral of the story above is that the main obstacle to fast networking is protocol software. In this section we will look at some ways to speed up this software. For more information, see (Clark et al., 1989; Edwards and Muir, 1995; and Chandranmenon and Varghese, 1995).

Ex. 1006.583

INTEL Ex.1006.001

Tanenbaum (Ex. 1006)

### Overview of Tanenbaum

## THIRD EDITION

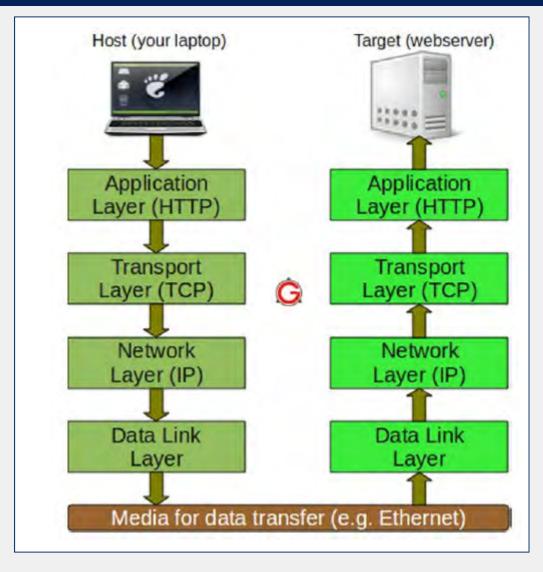

by the network layer. The hardware and/or software within the transport layer that does the work is called the **transport entity**. The transport entity can be in the operating system kernel, in a separate user process, in a library package bound into network applications, or on the network interface card. In some cases, the

Ex. 1006.498

INTEL Ex.1006.001

Tanenbaum (Ex. 1006)

# '036 Patent: the Combination Fails to Suggest "the TCP State Information Is Updated by Said Second Processor"

- 1. A device for use with a first apparatus that is connectable to a second apparatus, the first apparatus containing a memory and a first processor operating a stack of protocol processing layers that create a context for communication, the context including a media access control (MAC) layer address, an Internet Protocol (IP) address and Transmission Control Protocol (TCP) state information, the device comprising:

- a communication processing mechanism connected to the first processor, said communication processing mechanism containing a second processor running instructions to process a message packet such that the context is employed to transfer data contained in said packet to the first apparatus memory and the TCP state information is updated by said second processor.

Ex. 1001.142-43 ('036 Patent)

# '036 Patent: the Combination Fails to Suggest "the TCP State Information Is Updated by Said Second Processor"

Robert Horst Petitioner's Expert

| 14 | Q. But when the total length field, the datagram        |

|----|---------------------------------------------------------|

| 15 | ID field, the IP checksum field, the UDP checksum field |

| 16 | are modified or initialized, that modification is done  |

| 17 | on the I/O device, right?                               |

| 18 | A. Right. This script is run on the I/O device.         |

| 19 | So those changes to the header are done on the I/O      |

| 20 | device.                                                 |

Ex. 2028 (Horst Dep. Tr.) at 125:14-20

# '036 Patent: the Combination Fails to Suggest "the TCP State Information Is Updated by Said Second Processor"

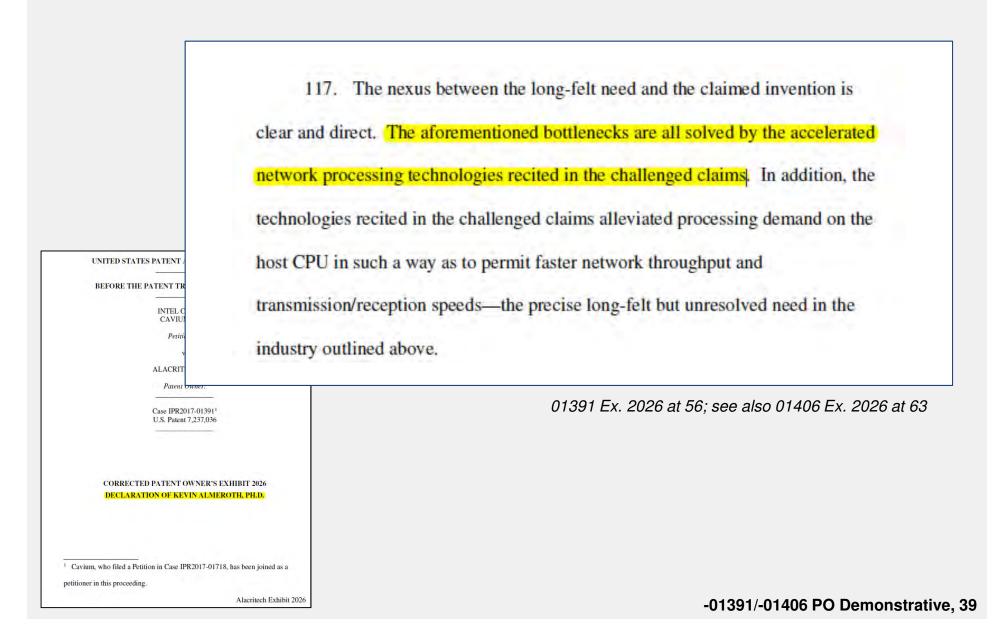

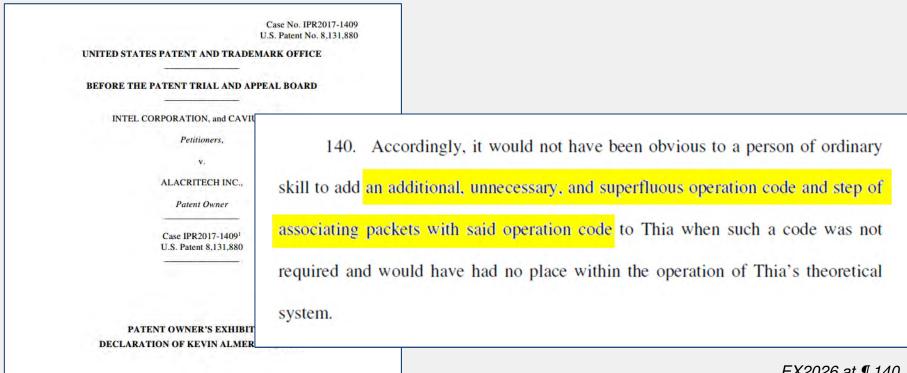

112. Moreover, the claimed updating is performed when the data is

transferred to the first apparatus memory, i.e., on the **receiving side** of the system.

UNITED STATES PATENT AND TRADEMARK

BEFORE THE PATENT TRIAL AND APPEAL

INTEL CORP. and CAVIUM, INC.,

Petitioners,

ALACRITECH INC.,

Patent Owner.

Case IPR2017-014061 U.S. Patent 7,673,072 At best, therefore, the combination of Erickson and Tanenbaum would disclose a

system that updates a header template on transmit side by the network interface

device and updated a connection record on the receive side by the host CPU. The

combination does not show or suggest the claim approach, whereby the processor

of the network interface device updates TCP state information created or

maintained by the host CPU.

CORRECTED PATENT OWNER'S EXHIBIT 2026

DECLARATION OF KEVIN ALMEROTH, Ph.D.

Ex. 2026 at 53

petitioner in this proceeding.

Alacritech Exhibit 2026

Almeroth Decl. (Ex. 2026)

<sup>&</sup>lt;sup>1</sup> Cavium, who filed a Petition in Case IPR2017-01707, has been joined as a

dividing, by the interface device, the data into segments; creating headers for the segments, by the interface device, from a template header containing the protocol header information; and prepending the headers to the segments to form transmit packets.

Ex. 1001.142 ('072 Patent), Claim 1

dividing, by the interface device, the data into segments; creating headers for the segments, by the interface device, from the template header;

prepending the headers to the segments to form packets; and

transmitting the packets on a network.

Ex. 1001.142 ('072 Patent), Claim 9

dividing, by the interface device, the data into segments; creating headers for the segments, by the interface device, from a template header that includes the IP addresses and TCP ports; and prepending the headers to the segments to form transmit packets.

Ex. 1001.142 ('072 Patent), Claim 15

FIG. 7 is a block diagram illustrating a UDP datagram template 702 (without a user data area) residing in the I/O device adapter's memory. The user process provides the starting address and the length for the user data in its virtual address space, and then "spanks" a GO register to trigger the I/O device adapter's execution of a predetermined script. The I/O device adapter stores the user data provided by the user process in the I/O device adapter's memory, and then transmits the completed UDP datagram 702 over the media.

An example of programming that triggers the I/O device adapter is provided below:

Ex. 1005.012

Erickson (Ex. 1005)

UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND AP

INTEL CORPORATION

Petitioner

V.

ALACRITECH, INC.

Patent Owner

Case IPR. No. Unassigned

U.S. Patent No. 7,673,072

Title: FAST-PATH APPARATUS FOR RECEIVING I

A TCP CONNECTION

### Erickson in view of Tanenbaum96

[1.4] dividing, by the interface device, the data into segments;

The "dividing, by the interface device, the data into segments" limitation is met by the foregoing obvious TCP script for Erickson. Erickson's senduserdatagram (Ex.1005, Erickson at 7:23-32) user process triggers the I/O adapter to send each segment, by "spanking" the GO register. The adapter calculates the TCP checksum, transmits the packet, updates the shared state in Hardware Register 504, and waits for GO to be set again for the next segment. Repeated invocations of the TCP script (by repeatedly spanking the GO register) with pointers to data for consecutive segments result in the interface device dividing the user data stream into TCP segments.

Declaration of Robert Horst, Ph.D. in Support of Petition for *Inter Partes* Review of U.S. Patent No. 7,673,072

Ex. 1003 at A-12

INTEL Ex.1003.001

Horst Decl. (Ex. 1003)

UNITED STATES PATENT AND TRADEMARK OF

BEFORE THE PATENT TRIAL AND APPEAL BOA

INTEL CORPORATION Petitioner

V.

ALACRITECH, INC. Patent Owner

Case IPR. No. Unassigned

U.S. Patent No. 7,673,072

Title: FAST-PATH APPARATUS FOR RECEIVING DATA COI

A TCP CONNECTION

Declaration of Robert Horst, Ph.D. in Support of Petition for *Inter Partes* Review of U.S. Patent No. 7,673,072

### Erickson in view of Tanenbaum96

[1.4] dividing, by the interface device, the data into segments;

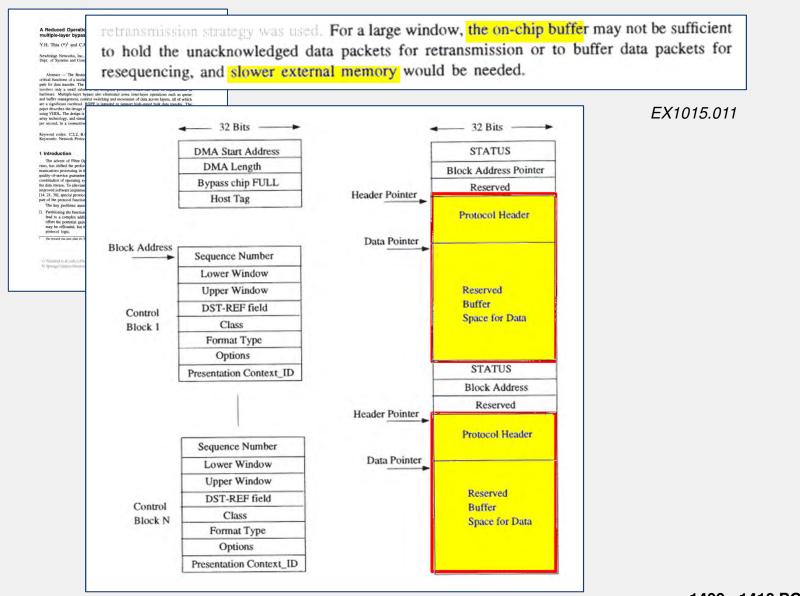

met by a second obvious TCP script for Erickson. This alternative script builds on the single segment script, but requires only one "spank" of the GO register for a multi-segment send. As Erickson assumes, this script would sequentially transfer an amount of data that does not exceed the limited range the adapter is able to map, possibly a single page:

"In all likelihood the adapter would have a very limited knowledge of the user process' virtual address space, probably only knowing how to map virtual-to-physical for a very limited range. maybe as small as a single page." (Ex.1005, Erickson at 8:22-24).

The second script would transfer (via DMA) and transmit one maximum-segmentsize (MSS) segment of data "(in practice, usually about 1500 bytes)" (Ex.1006, Tanenbaum at .540) at a time from the block identified by the user data address pointer and length passed to the script, until all of the data from the block was sent. A POSA would understand that typical page sizes in 1996 were larger than 1500 bytes (e.g. 4K pages were common).

The "dividing the data into multiple segments" limitation is also met by a third obvious TCP script for Erickson. Like the second alternative script, this third alternative script builds on the single segment script, but requires only one "spank" of the GO register for a multi-segment send. Instead of transferring one MSS-sized segment of user data at a time, the adapter would DMA all of the user data identified by the user data address pointer and length in one large transfer. The adapter would then repeatedly extract one segment of data at a time from the transferred block, encapsulate it in a packet, and transmit.

INTEL Ex.1003.001

Ex. 1003 at A-13

Horst Decl. (Ex. 1003)

Robert Horst Petitioner's Expert

| 16 | Q. You also state at the bottom of A-78, you say       |

|----|--------------------------------------------------------|

| 17 | that "It would also be obvious to create the following |

| 18 | TCP script for Ericsson," and you go on to page A-77   |

| 19 | sorry. That's A-39 of A-78, now on A-40 of A-78. You   |

| 20 | referred to this as an alternative script. Do you see  |

| 21 | that?                                                  |

| 22 | A. Yes.                                                |

| 23 | Q. Okay. The alternative script is not disclosed       |

| 24 | in Ericsson itself, though, right?                     |

| 2  | A. The TCP scripts are not disclosed in Ericsson.      |

| 3  | Q. (By Mr. Mack) The TCP script is not disclosed;      |

| 4  | but this alternative that you're describing at the top |

| 5  | of page A-40 is also not disclosed, right?             |

| 6  | MR. CONSTANT: Objection to form.                       |

| 7  | A. The script itself was not disclosed, but the        |

| 8  | combination of Ericcson and Tanenbaum would make a     |

| 9  | script like this obvious.                              |

| 10 | Q. (By Mr. Mack) And then beginning in the next        |

| 11 | paragraph you refer to a third TCP script. Do you see  |

| 12 | that?                                                  |

| 13 | A. Yes.                                                |

| 14 | Q. That's, yet, another script that's not              |

| 15 | disclosed in Ericsson, right?                          |

| 16 | MR. CONSTANT: Objection, form.                         |

| 17 | A. Yes.                                                |

Ex. 2028 (Horst Dep. Tr.) at 98:16-99:17

Robert Horst Petitioner's Expert

| 14 | Q. So after the GO register is spanked,           |

|----|---------------------------------------------------|

| 15 | if there are multiple segments to be transmitted  |

| 16 | the adapter would access the I/O bus for multiple |

| 17 | times to do the DMA; is that correct?             |

| 18 | MR. CONSTANT: Objection. Form.                    |

| 19 | A. The each individual segment would              |

| 20 | require a DMA transfer to get that data to the    |

| 21 | adapter, yes.                                     |

| 22 | Q. And in order to do a DMA transfer,             |

| 23 | the adapter need to access the I/O bus; is that   |

| 24 | correct?                                          |

| 25 | A. Yes, that's the path through which             |

| 2  | the data gets from the host to the adapter.       |

Ex. 2029 (Horst Dep. Tr.) at 99:19-100:2

Robert Horst Petitioner's Expert

| 21 | Q. And if adding up all this access is        |

|----|-----------------------------------------------|

| 22 | to I/O bus, can you tell if the third         |

| 23 | transcript if the third script is faster than |

| 24 | the slow path?                                |

| 25 | A. Again, without knowing the details,        |

| 2  | there's no way to know which one is faster.   |

Ex. 2029 (Horst Dep. Tr.) at 97:21-98:2

Within the udpscript procedure described above, the nextid() function provides a monotonically increasing 16-bit counter required by the IP protocol. The ipchecksum() function performs a checksum for the IP Header 706 portion of the datagram 702. The vtophys() function performs a translation of the user-provided virtual address into a physical address usable by the adapter. In all likelihood, the adapter would have a very limited knowledge of the user process' virtual address space, probably only knowing how to map virtual-to-physical for a very limited range, maybe as small as a single page. Pages in the user process' virtual address space for such buffers would need to be fixed. The udpscript procedure would need to be enhanced if the user data were allowed to span page boundaries. The udpchecksum() procedure generates a checksum value for both the UDP Header 708 plus the user data (not shown).

Ex. 1005 at 8:20-24

Erickson (Ex. 1005)

UNITED STATES PATENT AND TRADEMARK

BEFORE THE PATENT TRIAL AND APPEAL B

INTEL CORP. and CAVIUM, INC.,

Petitioners,

ALACRITECH INC.,

Patent Owner.

Case IPR2017-01406<sup>1</sup> U.S. Patent 7,673,072

CORRECTED PATENT OWNER'S EXHIBIT DECLARATION OF KEVIN ALMEROTH, P.

99. Because Erickson's network adapter has "very limited knowledge" of the user process's virtual address space (and operates on fixed, single pages, as described above), the modification proposed by Petitioner and its expert would be technically infeasible and extremely difficult to implement without significantly changing Erickson to become a different system—one that supported a different memory access scheme and supported different protocols. For these reasons, the combination of Erickson and Tanenbaum would not provide a POSA with a reasonable expectation of success to make or use an implementation that supported dividing data segments.

Ex. 2026 at 48-49

06973-00001/9871367.1

Alacritech Exhibit 2026

Almeroth Decl. (Ex. 2026)

Cavium, who filed a Petition in Case IPR2017-01707, has been joined as a petitioner in this proceeding.

### No Motivation to Combine – Dr. Horst's Admission

### IP Storage and the CPU Consumption Myth

Robert Horst 3ware, Inc. 701 E. Middlefield Rd. Mountain View, CA 94043

#### Abstract

This paper addresses a key issue that arises when attaching storage devices directly to IP networks: the perceived need for hardware acceleration of the TCP/IP networking stack. While many implicitly assume that acceleration is required, the evidence shows that this conclusion is not well founded. In the past, network accelerators have had mixed success, and the current economic justification for hardware acceleration is poor given the low cost of host CPU cycles. The I/O load for many applications is dominated by disk latency, not transfer rate, and hardware protocol accelerators have little effect on the I/O performance in these environments. Application benchmarks were run on an IP storage subsystem to measure performance and CPU utilization on Email, database, file serving, and backup applications. The results show that good performance can be obtained without protocol acceleration.

### 1. Introduction

The growing popularity of gigabit Ethernet has prompted increasing interest in using standard IP networks to attach storage devices to servers. These Ethernet Storage Area Networks (E-SANs), have significant advantages in cost and management case compared with Fibre Channel SANs. Some IP storage products are already on the market, and work to standardize the protocols is progressing in the IP Storage working group of the IETF [1].

Networks customized to storage networking, such as Fiber Channel, were developed largely due to the perception that standard networking protocols are too heavyweight for attaching storage. Conventional wisdom says that IP storage is impractical without special purpose NICs to accelerate the TCP/IP protocol stack. This papers shows that the need for hardware acceleration is largely a myth. Several different lines of reasoning show that the future of storage networking will rely heavily on storage devices connected to servers without special purpose hardware accelerators.

conclusion is not well founded. In the past, network accelerators have had mixed success, and the current economic justification for hardware acceleration is poor given the low cost of host CPU cycles. The I/O load for many applications is dominated by disk latency, not transfer rate, and hardware protocol accelerators have little effect on the I/O performance in these environments. Application benchmarks were run on an IP storage subsystem to measure performance and CPU utilization on Email, database, file serving, and backup applications. The results show that good performance can be obtained without protocol acceleration.

new protocols proposed for IP storage, iSCSI and iFCP, are far from stable, and even after the standards have been formally approved, there will likely be a long series of enhancements and bug fixes. It seems extremely

Ex. 2300.001

0-7695-1432-4/01 \$10.00 @ 2001 IEEE

194

Horst 2001 Paper (Ex. 2300)

### No Motivation to Combine – Dr. Horst's Admission

### IP Storage and the CPU Consumption Myth

Robert Horst 3ware, Inc. 701 E. Middlefield Rd. Mountain View, CA 94043

### Abstract

This paper addresses a key issue that arises when attaching storage devices directly to IP networks: the perceived need for hardware acceleration of the TCP/IP networking stack. While many implicitly assume that acceleration is required, the evidence shows that this conclusion is not well founded. In the past, network accelerators have had mixed success, and the current economic justification for hardware acceleration is poor given the low cost of host CPU cycles. The I/O load for many applications is dominated by disk latency, not transfer rate, and hardware protocol accelerators have little effect on the I/O performance in these environments. Application benchmarks were run on an IP storage subsystem to measure performance and CPU utilization on Email, database, file serving, and backup applications. The results show that good performance can be obtained without protocol acceleration.

### 1. Introduction

The growing popularity of gigabit Ethernet has prompted increasing interest in using standard IP networks to attach storage devices to servers. These Ethernet Storage Area Networks (E-SANs), have significant advantages in cost and management case compared with Fibre Channel SANs. Some IP storage products are already on the market, and work to standardize the protocols is progressing in the IP Storage working group of the IETF [1].

Networks customized to storage networking, such as Fiber Channel, were developed largely due to the perception that standard networking protocols are too heavyweight for attaching storage. Conventional wisdom says that IP storage is impractical without special purpose NICs to accelerate the TCP/IP protocol stack. This papers shows that the need for hardware acceleration is largely a myth. Several different lines of reasoning show that the future of storage networking will rely heavily on storage devices connected to servers without special purpose hardware accelerators.

### 2. The Histo

There are n accelerators to of CPU. Some exa been successfu communications unmet expectatio

Examples of date from the emany systems, the I/O processor to However, it has be of architecture to rapid pace of tech

A specific rec I/O) initiative. processor, such serve as an I/O p from its attached started, the i960 task, but its perfe as the main CPU some point ar Somewhere in be or without the and support cost usually a differe and it usually environment. costly, and even for inventing an the processors. kills the front-er

generation of en the cycle.

Some may argue that the problem was that the accelerators should have been optimized hardware instead of embedded programmable processors. Unfortunately, every protocol worthy of acceleration continues to evolve, and it is difficult to stay ahead of the moving target. The new protocols proposed for IP storage, iSCSI and iFCP, are far from stable, and even after the standards have been formally approved, there will likely be a long series of enhancements and bug fixes. It seems extremely

some point an accelerator becomes a decelerator. Somewhere in between, performance is about equal with or without the attached processor, but the development and support costs become a burden. The accelerator is usually a different CPU architecture than the main CPU, and it usually has a different software development environment. Maintaining two such environments is costly, and even if they were identical, there is overhead for inventing and testing the software interface between the processors. The software development cost eventually kills the front-end processor architecture, until the next generation of engineers rediscovers the idea and repeats the cycle.

as the main CPU. If the performance does not keep up, at

Ex. 2300.001

0-7695-1432-4/01 \$10.00 © 2001 IEEE

194

Horst 2001 Paper (Ex. 2300)

### No Motivation to Combine – Tanenbaum Teaching Away

A tempting way to go fast is to build fast network interfaces in hardware. The difficulty with this strategy is that unless the protocol is exceedingly simple, hardware just means a plug-in board with a second CPU and its own program. To avoid having the network coprocessor be as expensive as the main CPU, it is often a slower chip. The consequence of this design is that much of the time the main (fast) CPU is idle waiting for the second (slow) CPU to do the critical work. It is a myth to think that the main CPU has other work to do while waiting. Furthermore, when two general-purpose CPUs communicate, race conditions can occur, so elaborate protocols are needed between the two processors to synchronize them correctly. Usually, the best approach is to make the protocols simple and have the main CPU do the work.

Ex. 1006.588-89

INTEL Ex.1006.001

Tanenbaum (Ex. 1006)

### No Motivation to Combine – Tanenbaum Teaches Away

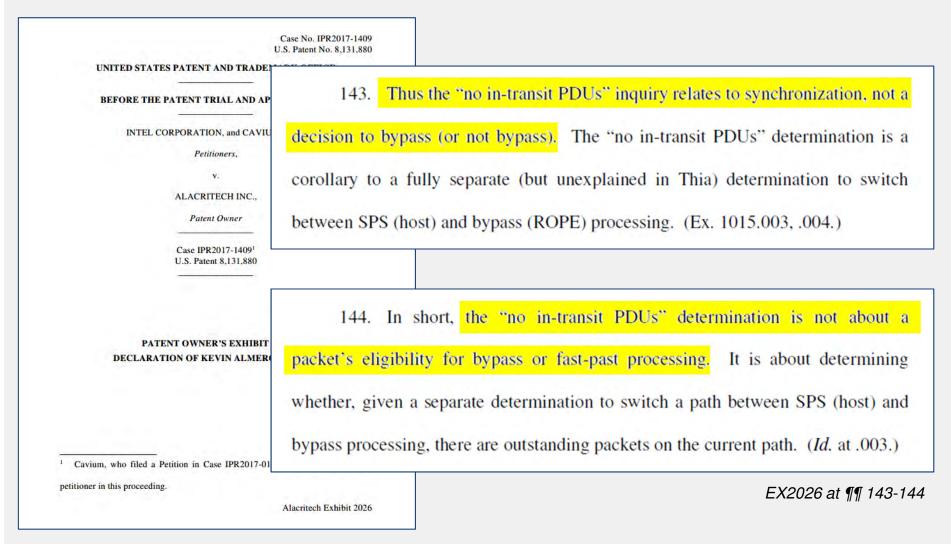

87. (Id. at .588-89.) Accordingly, based on the above passage,

Tanenbaum identifies myriad difficulties with implementing TCP header bypass in

a chip separate from the host CPU and advises against attempting such an

implementation. These difficulties are precisely the issues that were solved by the

invention of the '036 patent. At the very least, Tanenbaum teaches that integration

of transport entity functions in the NIC is complicated and non-trivial, but does not

provide any insight or suggestion of how the complications may be overcome.

Instead, Tanenbaum suggests a "Fast TPDU Processing" method that is

implemented and performed on the host-precisely the opposite of the '036

invention.

CORRECTED PATENT OWNER'S EXHIBIT 2026 DECLARATION OF KEVIN ALMEROTH, PH.D.

UNITED STATES PATENT AND TRADEMARK OFFI

BEFORE THE PATENT TRIAL AND APPEAL BOAR

INTEL CORP. and

CAVIUM, INC.,

Petitioners,

ALACRITECH INC.,

Patent Owner.

Case IPR2017-013911 U.S. Patent 7,237,036

Ex. 2026 at 39

Alacritech Exhibit 2026

Almeroth Decl. (Ex. 2026)

Cavium, who filed a Petition in Case IPR2017-01718, has been joined as a petitioner in this proceeding.

## No Motivation to Combine - Speed

Furthermore, the premise of Patent Owner's argument—that the combination must be predictably "faster" than the prior art—is also wrong. The principal reason for offloading TCP/IP is not to make the network "faster." Ex. 1223, ¶ 44. Offloading TCP/IP protocol processing is intended to lower the processing load on the host computer's main CPU, which readily occurs with

offload to a second processor, a well-known approach. *Id*.

Case IPR2017-01391<sup>1</sup>

U.S. Patent No. 7,237,036

Title: FAST-PATH APPARATUS FOR RECEIVING DATA CORRESPONDING A TCP CONNECTION

PETITIONER'S REPLY TO PATENT OWNER'S RESPONSE TO PETITION FOR INTER PARTES REVIEW OF U.S. PATENT NO. 7,237,036

Mail Stop "PATENT BOARD" Patent Trial and Appeal Board U.S. Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450

UNITED STATES PAT

BEFORE THE PATEN

INTEL CO

Petition Reply, Paper 41

Petitioner Reply, Paper 41 at 13

<sup>&</sup>lt;sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2017-01718, has been joined as a petitioner in this proceeding. Wistron Corporation, which filed a Petition in Case IPR2018-00327, has been joined as a petitioner in this proceeding.

transmission mechanism is much more complex than UDP and must support congestion control in the form of a sliding transmission window, retransmissions, and ordered, reliable delivery, it would not have been at all apparent to a POSITA that a TCP implementation of *Erickson*'s simplistic approach of using a local script to update header fields would be successful or operable to maintain and exchange the much more complex state information required by TCP.

POSITA would put where in the system." In addition, because the TCP

<sup>1</sup> Cavium, who filed a Petition in Case IPR2017-01718, has been joined as a petitioner in this proceeding.

CORRECTED PATENT OWNER'S EXHIBIT 2026 DECLARATION OF KEVIN ALMEROTH, PH.D.

Alacritech Exhibit 2026

Almeroth Decl. (Ex. 2026)

-01391/-01406 PO Demonstrative, 31

Ex. 2026.43

Ex. 2042

Robert Horst Petitioner's Expert

```

16

Q. (By Mr. Mack) Right. The pseudocode that we

17

looked at earlier, that was a UDP script, right?

A. Yes.

18

19

Q. And TCP is a different protocol that UDP,

20

right?

21

A. Yes.

Q. TCP is connection oriented, right?

22

23

A. Yes.

Q. There's a three-way TCP handshake in order to

24

establish a TCP connection?

25

2

A. Yes.

3

Q. And how are UDP connections established?

4

A. UDP is connectionless.

Q. So would you say the UDP connection process is

simpler than the TCP connection process?

6

7

A. Yes.

8

Q. And UDP doesn't support retransmission, does

9

10

A. The UDP protocol itself doesn't do

retransmission like TCP does.

11

12

Q. And UDP also doesn't support flow control, does

13

it?

14

A. It doesn't support the type of flow control

15

that TCP does, no.

16

Q. And TCP and UDP have different header sizes.

17

right?

18

A. I believe so, yes.

```

Ex. 2028 (Horst Dep. Tr.) at 96:16-97:18

Robert Horst Petitioner's Expert

```

Q. And UDP doesn't include sequence numbers in the

header, right?

A. Right.

Q. And TCP does include sequence numbers, right?

A. Yes.

9

Q. Are there any other differences between TCP and

UDP that you can think of?

10

A. TCP has a number of other features that are not

11

12

in UDP.

13

Q. Would you say that TCP is a more complicated

protocol than UDP?

14

15

A. Yes.

```

Ex. 2028 (Horst Dep. Tr.) at 98:4-15

Robert Horst Petitioner's Expert

```

21

O. So what does it take to determine

22

this Window field for a TCP header?

23

MR. CONSTANT: Objection. Form.

24

A. I don't really understand the

25

The determination of how the Window

2

field works is a fairly complex process,

3

described in my report, described in Tanenbaum.

4

There's not a short answer to that question.

5

O. Does the sender need to determine the

Window field before it send out the TCP packet?

MR. CONSTANT: Objection. Form.

Asked and answered.

A. The Window field is a part of the TCP

10

header, so the Window field does have to be

11

determined before the packet is sent out.

```

Ex. 2600 (Horst Dep. Tr.) at 13:21-14:11

Robert Horst Petitioner's Expert

| 16 | Q. You just mentioned trade-off. What            |

|----|--------------------------------------------------|

| 17 | do you mean by trade-off, what trade-off?        |

| 18 | MR. CONSTANT: Objection. Form.                   |

| 19 | A. Trade-offs means at every step of a           |

| 20 | design you have to evaluate alternatives and     |

| 21 | decide which alternative is the best one to use. |

| 22 | Q. So in the in the design of network            |

| 23 | protocol offload, what trade-off is involved?    |

| 24 | MR. CONSTANT: Objection. Form.                   |

| 25 | A. There are trade-offs on what kind of          |

| 2  | a processor to use and in what kind of which     |

| 3  | portions of the protocol to offload, all the     |

| 4  | things that I talked about in the background     |

| 5  | section of my report.                            |

```

18

Q. You also mentioned about what should

19

be offloaded is also a trade-off to be

20

considered. Why that is a trade-off to be

21

considered?

22

MR. CONSTANT: Objection. Form.

23

A. When more of the protocol is

offloaded, there's more complexity in the

24

25

software that's run on the network interface

2

card, so it's -- it may be more difficult, but in

3

some cases it could be higher performance. So

4

there's trade-offs on the performance versus the

5

complexity.

```

Ex. 2029 (Horst Dep. Tr.) at 16:19-17:7, 17:18-18:5

## Secondary Considerations: Long-Felt Need

#### 1. Introduction

As data transmission speeds have increased dramatically in recent years, the processing of protocols has become one of the major bottlenecks in data communications. Current experimental networks provide a bandwidth in the Gb/s range. New multimedia applications require that networks guarantee the quality

Ex. 2031 at 1 (1993 IBM Research Division ACM SIGCOMM article)

#### 1 Introduction

Many researchers have observed that the performance of remote applications have not kept pace with modern communication network speeds. Part of this imbalance is attributed to the protocols used by the remote applications, namely, UDP/IP and TCP/IP. It is now widely believed that the problems with these protocols are not inherent in the protocols themselves but in their particular implementations [Dalt93, Whet95]. The following factors are cited as contributors to the poor performance of UDP/IP and TCP/IP:

Ex. 2032 at 1 (1995 Univ. of Berkeley paper)

## Secondary Considerations: Long-Felt Need

#### Abstract

The communication speed in wide-, metropolitan-, and local-area networking has increased over the past decade from Kbps lines to Gbps lines; i.e., six orders of magnitude, while the processing speed of commercial CPUs that can be employed as communications processor has changed only two to three orders of magnitude. This discrepancy in speed translates to "bottlenecks" in the communications process, because the software that supports some of the high-level functionality of the communication process is now several order of magnitude slower than the transmission media. Moreover, the overhead introduced by the operating system (OS) on the communication pro-

Ex. 2033 at 1 (1990 IEEE article from AT&T Bell Labs)

#### Abstract

Server network performance is increasingly dominated by poorly scaling operations such as I/O bus crossings, cache misses and interrupts. Their overhead prevents performance from scaling even with increased CPU, link or I/O bus bandwidths. These operations can be reduced by redesigning the host/adapter interface to exploit additional processing on the adapter. Offloading processing to the adapter is beneficial not only because it allows more cycles to be applied but also of the changes it enables in the host/adapter interface. As opposed to other approaches such as RDMA, TCP offload provides benefits without requiring changes to either the transport protocol or API.

Ex. 2034 at 1 (2005 USENIX Conference paper from IBM)

## Secondary Considerations: Long-Felt Need

## Secondary Considerations: Industry Praise

Our measurement shows that an Alacritech NIC is able to sustain network bandwidth comparable to that of Native NT for large messages, which is close to wire-speed. Its accumulated host processor utilization, while lower than native NT's, is higher than that with our offload implementation. Its performance degrades when messages are smaller than 2k bytes because it has no means of aggregating out-going messages (i.e. no Nagel Algorithm).

Ex. 2039 at 4 (2001 HP Labs research paper)

## Secondary Considerations: Industry Praise

"The ANX 1500 is an evolutionary advancement of Alacritech's long standing leadership in protocol acceleration, which is now applied not just to protocols, but to the optimization of all storage system interactions," said Jeff Boles, a technology analyst with Taneja Group. "The ANX 1500 substantially augments the performance of existing NAS investments from the best place possible – from right in the customer's Ethernet network – without reconfiguration or changes in management for the existing infrastructure. We think Alacritech is setting the stage for a next generation of solutions that will accelerate storage from outside the storage array, and more cost effectively share an investment in performance across many storage systems and clients. I've talked to early-stage customers using the product, and they believe it's gamechanging."

Ex. 2040 at 3 (Shoreline Ventures Press Release)

## Secondary Considerations: Industry Praise

121. The industry universally praised commercial embodiments of the features described in the challenged claims. HP found that the "Alacritech NIC is able to sustain network bandwidth comparable to that of Native NT for large messages, which is close to wire-speed" and "achiev[e] lower processor utilization than native NT's TCP/IP protocol stack for transmission of large enough messages." (Ex. 2039 at ¶ 4.) HP found that the test performance of the Alacritech iNIC "raises challenging questions for [HP's] choice of implementation technology because "the Alacritech approach is definitely better than our offload." *Id*.

UNITED STATES PATENT AND TRADE

BEFORE THE PATENT TRIAL AND AI

INTEL CORP. and

CAVIUM, INC.,

Petitioners,

v.

ALACRITECH INC.,

Patent Owner.

Case IPR2017-013911 U.S. Patent 7,237,036

CORRECTED PATENT OWNER'S EXHIBIT 2026

DECLARATION OF KEVIN ALMEROTH, PH.D.

Cavium, who filed a Petition in Case IPR2017-01718, has been joined as a petitioner in this proceeding.

Alacritech Exhibit 2026

01391 Ex. 2026 at 58; see also 01406 Ex. 2026 at 65

## Secondary Considerations: Failure of Others

To this day, TCP offload has never firmly caught on in the commercial world (except sometimes as a stopgap to add TCP support to immature systems [16]), and has been scorned by the academic community and Internet purists. This paper starts by analyzing why TCP offload has repeatedly failed.

Ex. 2041 at 2 (2003 HP Labs paper presented at HotOS IX conference)

TCP offload has been unsuccessful in the past for two kinds of reasons: fundamental performance issues, and difficulties resulting from the complexities of deploying TCP offload in practice.

Id. at 2

## Secondary Considerations: Failure of Others

offload were mismatched to the applications in question." *Id.* The TCP offload described above is a form of network processing offload that is described by the challenged claims, and this failure of others therefore has a direct nexus to the claimed inventions.

UNITED STATES PATENT AND TRADEMA

BEFORE THE PATENT TRIAL AND APPEAL BOARD

INTEL CORP. and CAVIUM, INC.,

Petitioners,

ALACRITECH INC.,

Patent Owner.

Case IPR2017-013911 U.S. Patent 7,237,036

CORRECTED PATENT OWNER'S EXHIBIT 2026 DECLARATION OF KEVIN ALMEROTH, PH.D.

Cavium, who filed a Petition in Case IPR2017-01718, has been joined as a petitioner in this proceeding.

Alacritech Exhibit 2026

01391 Ex. 2026 at 59; 01406 Ex. 2026 at 66

A tempting way to go fast is to build fast network interfaces in hardware. The difficulty with this strategy is that unless the protocol is exceedingly simple, hardware just means a plug-in board with a second CPU and its own program. To avoid having the network coprocessor be as expensive as the main CPU, it is often a slower chip. The consequence of this design is that much of the time the main (fast) CPU is idle waiting for the second (slow) CPU to do the critical work. It is a myth to think that the main CPU has other work to do while waiting. Furthermore, when two general-purpose CPUs communicate, race conditions can occur, so elaborate protocols are needed between the two processors to synchronize them correctly. Usually, the best approach is to make the protocols simple and have the main CPU do the work.

Ex. 1006 at 588-589

INTEL Ex.1006.001

IP Storage and the CPU Consumption Myth

CPU.

unm

of are

rapid

1/0)

task, as th

Som

usua

envir

the p

kills

the c

acce

Robert Horst 3ware, Inc. 701 E. Middlefield Mountain View, CA

#### Abstract

This paper addresses a key issue that arises when attaching storage devices directly to IP networks: the perceived need for hardware acceleration of the TCP/IP networking stack. While many implicitly assume that acceleration is required, the evidence shows that this conclusion is not well founded. In the past, network accelerators have had mixed success, and the current economic justification for hardware acceleration is poor given the low cost of host CPU cycles. The I/O load for many applications is dominated by disk latency, not transfer rate, and hardware protocol accelerators have little effect on the I/O performance in these environments. Application benchmarks were run on an IP storage subsystem to measure performance and CPU utilization on Email, database, file serving, and backup applications. The results show that good performance can be obtained without protocol acceleration.

#### 1. Introduction

The growing popularity of gigabit Ethernet has prompted increasing interest in using standard IP networks to attach storage devices to servers. These Ethernet Storage Area Networks (E-SANs), have significant advantages in cost and management case compared with Fibre Channel SANs. Some IP storage products are already on the market, and work to standardize the protocols is progressing in the IP Storage working group of the IETF [1].

Networks customized to storage networking, such as Fiber Channel, were developed largely due to the perception that standard networking protocols are too heavyweight for attaching storage. Conventional wisdom says that IP storage is impractical without special purpose NICs to accelerate the TCP/IP protocol stack. This papers shows that the need for hardware acceleration is largely a myth. Several different lines of reasoning show that the future of storage networking will rely heavily on storage devices connected to servers without special purpose hardware accelerators.

conclusion is not well founded. In the past, network accelerators have had mixed success, and the current economic justification for hardware acceleration is poor given the low cost of host CPU cycles. The I/O load for many applications is dominated by disk latency, not transfer rate, and hardware protocol accelerators have little effect on the I/O performance in these environments. Application benchmarks were run on an IP storage subsystem to measure performance and CPU utilization on Email, database, file serving, and backup applications. The results show that good performance can be obtained without protocol acceleration.

and it is difficult to stay ahead of the moving target. The new protocols proposed for IP storage, iSCSI and iFCP, are far from stable, and even after the standards have been formally approved, there will likely be a long series of enhancements and bug fixes. It seems extremely

Ex. 2300 at 194 (2001 paper by Petitioner's expert, Dr. Horst)

0-7695-1432-4/01 \$10.00 © 2001 IEEE

194

#### IP Storage and the CPU Consumption Myth

Robert Horst 3ware, Inc. 701 E. Middlefield Rd. Mountain View, CA 94043

#### Abstract

This paper addresses a key issue that arises when attaching storage devices directly to IP networks: the perceived need for hardware acceleration of the TCP/IP networking stack. While many implicitly assume that acceleration is required, the evidence shows that this conclusion is not well founded. In the past, network accelerators have had mixed success, and the current economic justification for hardware acceleration is poor given the low cost of host CPU cycles. The I/O load for many applications is dominated by disk latency, not transfer rate, and hardware protocol accelerators have little effect on the I/O performance in these environments. Application benchmarks were run on an IP storage subsystem to measure performance and CPU utilization on Email, database, file serving, and backup applications The results show that good performance can be obtained without protocol acceleration.

#### 1. Introduction

The growing popularity of gigabit Ethernet has prompted increasing interest in using standard IP networks to attach storage devices to servers. These Ethernet Storage Area Networks (E-SANs), have significant advantages in cost and management case compared with Fibre Channel SANs. Some IP storage products are already on the market, and work to standardize the protocols is progressing in the IP Storage working group of the iETF [1].

Networks customized to storage networking, such as Fiber Channel, were developed largely due to the perception that standard networking protocols are too heavyweight for attaching storage. Conventional wisdom says that IP storage is impractical without special purpose NICs to accelerate the TCP/IP protocol stack. This papers shows that the need for hardware acceleration is largely a myth. Several different lines of reasoning show that the future of storage networking will rely heavily on storage devices connected to servers without special purpose hardware accelerators.

#### 2. The Historical A

There are many hist accelerators to offload pre CPU. Some examples, su been successful, but communications processe unmet expectations.

Examples of front-er date from the early days many systems, the primar I/O processor to offload However, it has become ir of architecture to deliver a rapid pace of technology of

A specific recent exar I/O) initiative. The idea processor, such as an Inti serve as an I/O processor from its attached I/O dev started, the i960 embedde task, but its performance as the main CPU. If the p some point an acceler Somewhere in between a or without the attached and support costs becon usually a different CPU at and it usually has a environment. Maintain costly, and even if they for inventing and testing the processors. The softy kills the front-end proce generation of engineers : the cycle.

Some may argue that accelerators should have be of embedded programmal every protocol worthy of a and it is difficult to stay a new protocols proposed if are far from stable, and every formally approved, there enhancements and bug fixes. It seems ex

as the main CPU. If the performance does not keep up, at some point an accelerator becomes a decelerator. Somewhere in between, performance is about equal with or without the attached processor, but the development and support costs become a burden. The accelerator is usually a different CPU architecture than the main CPU, and it usually has a different software development environment. Maintaining two such environments is costly, and even if they were identical, there is overhead for inventing and testing the software interface between the processors. The software development cost eventually kills the front-end processor architecture, until the next generation of engineers rediscovers the idea and repeats the cycle.

fixes. It seems extremely

0-7695-1432-4/01 \$10.00 © 2001 IEEE

13

Ex. 2300 at 194

(Ex. 2300 at 194.) (emphasis added). This level of skepticism and teaching away

is directly related to the heart of the claimed invention - offloading network

UNITED STATES PATENT AN

processing, and therefore has a direct nexus to the challenged claims.

BEFORE THE PATENT TRIAL AND APPEAL BOARD

INTEL CORP. and CAVIUM, INC.,

Petitioners.

V.

ALACRITECH INC.,

Patent Owner.

Case IPR2017-013911 U.S. Patent 7,237,036

CORRECTED PATENT OWNER'S EXHIBIT 2026

Alacritech Exhibit 2026

01391 Ex. 2026 at 61; see also 01406 Ex. 2026 at 68

<sup>&</sup>lt;sup>1</sup> Cavium, who filed a Petition in Case IPR2017-01718, has been joined as a petitioner in this proceeding.

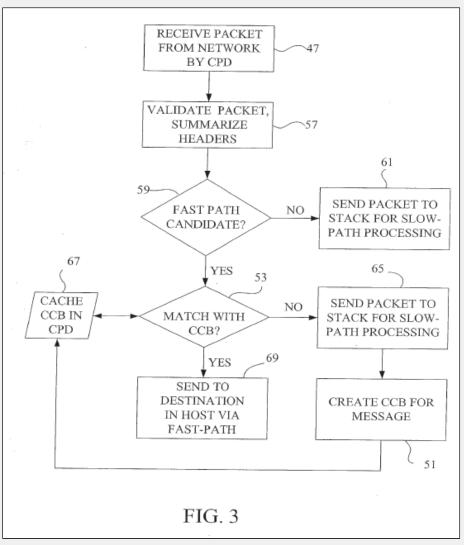

## '036 Patent – Contingent Motion to Amend (Proposed Claim 23 – Substitute for Claim 1)

#### **Proposed Claim 23**

23. A device for use with a first apparatus that is connectable to a second apparatus, the first apparatus containing a memory and a first processor operating a stack of protocol processing layers that create a context for communication, the context including a media access control (MAC) layer address, an Internet Protocol (IP) address and Transmission Control Protocol (TCP) state information, the device comprising:

a communication processing mechanism connected to the first processor,

said communication processing mechanism containing a second processor

running instructions <u>on the second processor</u>, <u>wherein the second processor</u> <u>determining whether an incoming message packet should be processed by the second processor</u>,

if the incoming message packet should be processed by the second processor, to processing the a incoming message packet, without involving the stack of processing protocol processing layers, such that the context is employed to transfer data contained in said packet to the first apparatus memory and the TCP state information is updated by said second processor,

if the incoming message packet should not be processed by the second processor, passing the incoming message packet to the first processor for further processing.

## Support for Proposed Claim 23 (Substitute for Claim 1)

Ex. 2020.152

# Proposed Claim 23 (Substitute for Claim 1) Is Valid Over the Prior Art

Filed: Ap

UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

INTEL CORP. and CAVIUM, INC., Petitioner,

V.

ALACRITECH, INC., Patent Owner.

Case IPR2017-01391

U.S. Patent No. 7,237,036<sup>1</sup>

Title: FAST-PATH APPARATUS FOR RECEIVING DATA

CORRESPONDING A TCP CONNECTION

PETITIONER'S RESPONSE IN OPPOSITION TO PATENT OW CONTINGENT MOTION TO AMEND UNDER 37 C.F.R. § 42.121

Mail Stop "PATENT BOARD" Patent Trial and Appeal Board U.S. Patent and Trademark Office P.O. Box 1450 Alexandria. VA 22313-1450

petitioner in this proceeding.

<sup>1</sup> Cavium, Inc., which filed a Petition in Case IPR2017-01718, has been joined as a

Accordingly, adapting Erickson to include the "header prediction" described in Tanenbaum96 discloses running instructions on the second processor (running scripts on the processor on the network interface card), wherein the second processor determining whether an incoming message packet should be processed

described inTanenbaum96 to determine if the incoming message packet should be processed by the second processor) as a fast path packet.

by the second processor (Erickson's I/O adapter with the header prediction

Petitioner Opposition to Motion to Amend, Paper 36 at 15-16

# Proposed Claim 23 (Substitute for Claim 1) Is Valid Over the Prior Art

Case No. IPR2017-0 U.S. Patent No. 7,237

UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

INTEL CORPORATION, and CAVIUM, INC.,

Petitioners,

٧.

ALACRITECH INC.,

Patent Owner

Case IPR2017-01391<sup>1</sup> U.S. Patent 7,237,036 63. I understand that Petitioner alleges Erickson discloses a slow path for both incoming and outgoing message packets. Opp., 20. However, the amended element is not only about using a slow path, but using a slow path after the determination. Erickson only discloses a prior art slow path.

64. I understand that Petitioner further alleges that based upon a second processor's determination using header prediction on Tanenbaum96 (which, as noted above, is not done on a second processor) to classify packets according to the slow or fast path, it is obvious to use a first processor to process incoming packets on a slow path. Opp., 21. In my opinion, this argument is misplaced. The critical inquiry of the amendment is when to use the slow path, which according to the amendment, is after the determination limitation. In my opinion, neither reference discloses this limitation. *Id*.

DECLARATION OF KEVIN ALMEROTH, PH.D. IN SUPPORT OF

PATENT OWNER'S REPLY IN SUPPORT OF CONTINGENT MOTION

TO AMEND UNDER TO 37 C.F.R. § 42.121

Ex. 2305.22

Alacritech Exhibit 2305

Almeroth Decl. (Ex. 2305)

Cavium, who filed a Petition in Case IPR2017-01718, has been joined as a petitioner in this proceeding.

## '072 Patent – Contingent Motion to Amend (Proposed Claim 22 – Substitute for Claim 1)

#### **Proposed Claim 22**

#### 22. A method comprising:

establishing, at a host computer, a transport layer connection, including creating a context that includes <u>a media access control (MAC) layer</u> <u>address, an Internet Protocol (IP) address and Transmission Control Protocol (TCP) state information protocol header information</u> for the connection;

transferring the **context** protocol header information to an interface device;

transferring data from the network host to the interface device, after transferring the **context** protocol header information to the interface device;

dividing, by the interface device, the data into segments;

creating headers for the segments, by the interface device, from a template header containing the protocol header information including IP address and TCP state information; and

prepending the headers to the segments to form transmit packets.

#### Support for Proposed Claim 22 (Substitute for Claim 1)

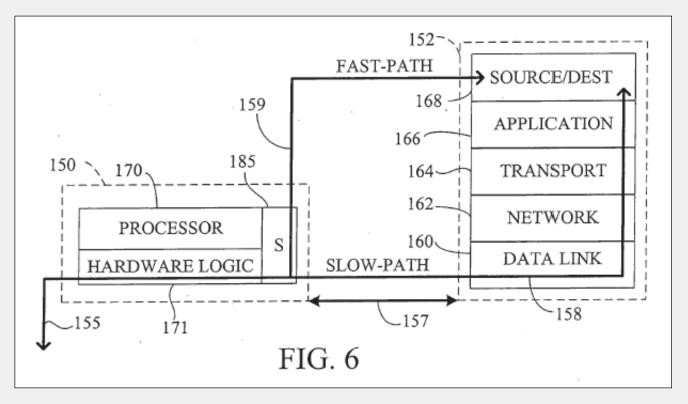

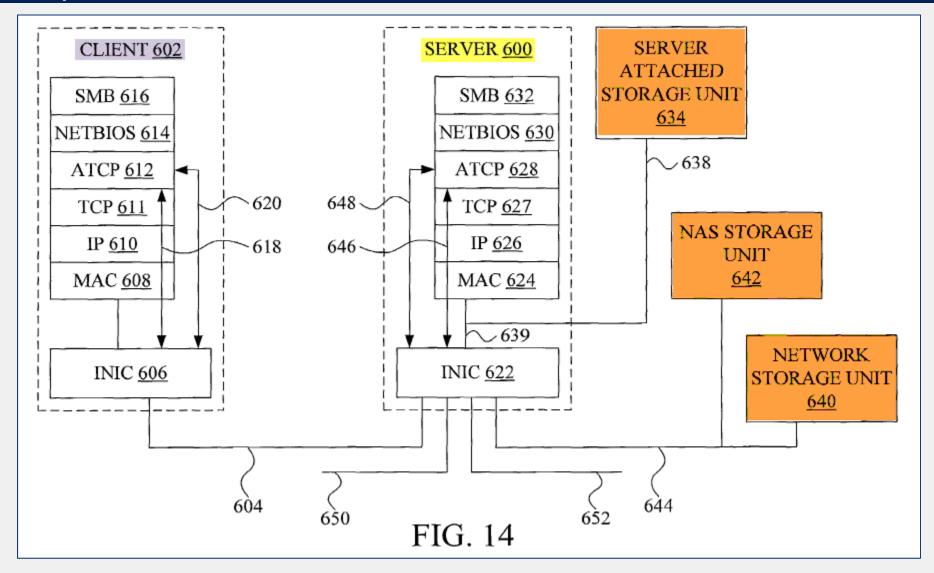

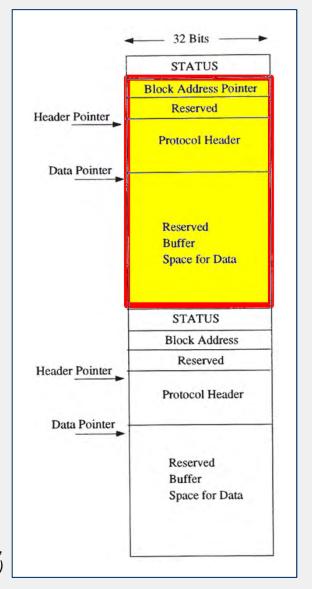

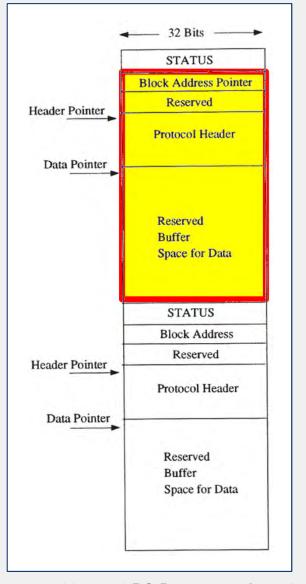

Ex. 2024.154 Fig. 6

#### Support for Proposed Claim 22 (Substitute for Claim 1)

#### 2.1.4 The TCB cache

Consider a situation in which a TCP connection is being handled by the card and a fragmented TCP segment for that connection arrives. In this situation, it will be necessary for the card to turn control of this connection over to the host.

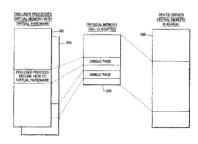

This introduces the notion of a Transmit Control Block (TCB) cache. A TCB is a structure that contains the entire context associated with a connection. This includes the source and destination IP addresses and source and destination TCP ports that define the connection. It also contains information about the connection itself such as the current send and receive sequence numbers, and the first-hop MAC address, etc. The complete set of TCBs exists in host memory, but a subset of these may be "owned" by the card at any given time. This subset is the TCB cache. The INIC can own up to 256 TCBs at any given time.

Ex. 2019 at 6

# Proposed Claim 22 (Substitute for Claim 1) Is Valid Over the Prior Art

Case No. IF U.S. Patent

UNITED STATES PATENT AND TRADEMARK OFF

BEFORE THE PATENT TRIAL AND APPEAL BOA

INTEL CORP., CAVIUM, INC., and WISTRON CORPORATION,

ALACRITECH INC.,

Patent Owner

Case IPR2017-01406<sup>1</sup> U.S. Patent 7,673,072 67. I understand that Petitioner then argues that Erickson, in view of Tanenbaum96, discloses this limitation because Erickson discloses transferring the elements to the network interface device. Opp., 13. Petitioner is again incorrect. As noted above (and in the Corrected Response), Erickson is only concerns UDP; there is no teaching regarding TCP. Also, neither reference

processor. See Corrected Response, 24-33, 33-34, 45; see also id., 16-19.

discloses transferring the context information to an interface device or second

Ex. 2305.67

DECLARATION OF KEVIN ALMEROTH, PH.D. IN SUPPORT OF PATENT OWNER'S REPLY IN SUPPORT OF CONTINGENT MOTION TO AMEND UNDER TO 37 C.F.R. § 42.121

Wistron Corporation, which filed a Petition in Case IPR2018-00329, has been joined as a settioner in this proceeding.

Alacritech Exhibit 2305

# Intel Corporation, Cavium, Inc., Wistron Corporation, and Dell Inc. v. Alacritech, Inc.

Case Nos.: IPR2017-01392, IPR2017-01728, IPR2018-00328, IPR2018-00372

U.S. Patent No. 7,337,241

Patent Owner's Demonstratives

**Hearing: September 13, 2018**

#### Overview of the '241 Patent

(12) United States Patent Boucher et al.

- (10) Patent No.: US 7,337,241 B2

- (45) **Date of Patent:** Feb. 26, 2008

- (54) FAST-PATH APPARATUS FOR RECEIVING DATA CORRESPONDING TO A TCP CONNECTION

- 4,991,133 A 2/1991 Davis et al. ...... 364/900 (Continued)

Corrected POR at 10.

-01392 PO Demonstrative, 2

#### Overview of Interrupt Processing

#### **CHAPTER 10**

#### Interrupt Handling

Although some devices can be controlled using nothing but their I/ real devices are a bit more complicated than that. Devices have t external world, which often includes things such as spinning disk

#### UNITED STATES PATENT AND TRADEMARK OFFICE

#### BEFORE THE PATENT TRIAL AND APPEAL BOARD

INTEL CORP. and CAVIUM, INC.,

Petitioners

V.

ALACRITECH INC.,

Patent Owner.

Case IPR2017-013921 U.S. Patent 7,337,241

CORRECTED PATENT OWNER'S EXHIBIT 2026

DECLARATION OF KEVIN ALMEROTH, PH.D.

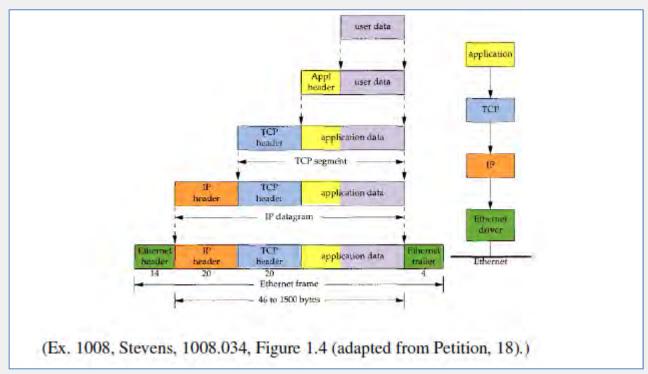

Because the processing of each layer typically involves a copy and data manipulation operation (for example a checksum computation operation), the host CPU must be "interrupted" at least one time per layer in order to process the data and construct (transmit side) or deconstruct (receive side) the packet. An interrupt is a signal to the processor emitted by hardware or software indicating an event that needs immediate attention. One popular textbook I am familiar with, Linux Device Drivers by A. Rubini and J. Corbert, was published in June 2001 and explains "[a]n interrupt is simply a signal that the hardware can send when it wants the processor's attention." (Ex. 2004 at 258 (emphasis in original)). The purpose of the interrupt is to "let the processor know when something has happened." (Id.) While computers attempt to run multiple processes simultaneously, a single processor can operate on only one task at a time. However, not all tasks need work done by the processor all of the time—some tasks are stalled waiting, for example, on input from a user or for a packet to arrive. Interrupts are used to inform the

processor as to which tasks are ready for work to be done by the processor. An

petitioner in this proceeding.

73-00001/98:03806 Alacritech Exhibit 2026

Ex. 2026 at 31 (citing Ex. 2004).

-01392 PO Demonstrative, 3

Cavium, who filed a Petition in Case IPR2017-01728, has been joined as a

#### Overview of Interrupt Processing

#### Overview of the '241 Patent

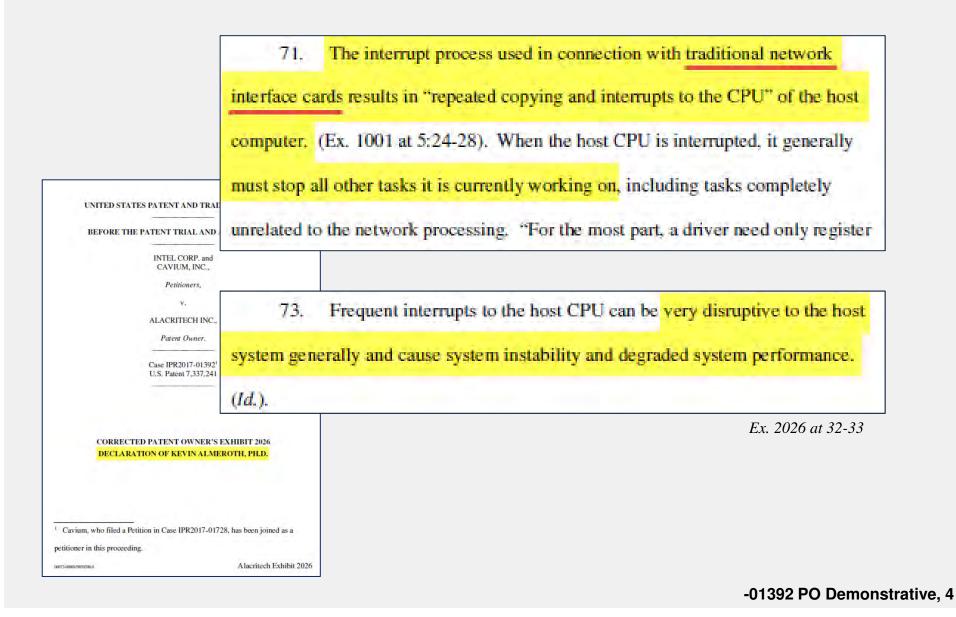

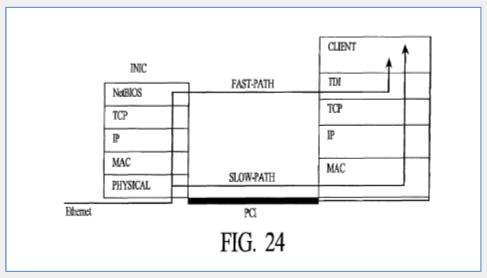

directly to its intended destination. This fast-path bypasses conventional protocol processing of headers that accompany the data. The fast-path employs a specialized microprocessor designed for processing network communication, avoiding the delays and pitfalls of conventional software layer processing, such as repeated copying and interrupts to the CPU. In effect, the fast-path replaces the states that are

'241 Patent, Ex. 1001, 5:22-28.

'241 Patent, Ex. 1001, Fig. 24.

-01392 PO Demonstrative, 5

#### Overview of the '241 Patent

Interrupt reduction in the present invention is obtained by:

- Transmit and receive fast-paths functioning at an upper layer (session or higher)

- All interactions between the NIC and host use *full transfer sizes*

can be sent to the network by the fast-path. Both the input and output fast-paths attain a huge reduction in interrupts by functioning at an upper layer level, i.e., session level or higher, and interactions between the network microprocessor and the host occur using the full transfer sizes which that upper layer wishes to make. For fast-path communications, an interrupt only occurs (at the most) at the beginning and end of an entire upper-layer message transaction, and there are no interrupts for the sending or receiving of each lower layer portion or packet of that transaction.

'241 Patent, Ex. 1001, 11:37-46.

This arrangement permits (at most) one interrupt at the beginning and end

of an entire upper-layer message transaction (regardless of size)

-01392 PO Demonstrative, 6

#### Challenged Claims of the '241 Patent (Claims 1-24)

1. A method for network communication, the method comprising:

receiving a plurality of packets from the network, each of the packets including a media access control layer header, a network layer header and a transport layer header;