### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (51) International Patent Classification <sup>7</sup> : |    | (11) International Publication Number: | WO 00/62182                |  |  |

|---------------------------------------------------------|----|----------------------------------------|----------------------------|--|--|

| G06F 15/76                                              | A2 | (43) International Publication Date:   | 19 October 2000 (19.10.00) |  |  |

| (72) Inventors: and                                     |    |                                        |                            |  |  |

GB

(21) International Application Number: PCT/GB00/01332 7 April 2000 (07.04.00) (22) International Filing Date:

| (30) Priority Data: |                         |    |

|---------------------|-------------------------|----|

| 9908199.4           | 9 April 1999 (09.04.99) | GB |

| 9908201.8           | 9 April 1999 (09.04.99) | GB |

| 9908203.4           | 9 April 1999 (09.04.99) | GB |

| 9908204.2           | 9 April 1999 (09.04.99) | GB |

| 9908205.9           | 9 April 1999 (09.04.99) | GB |

| 9908209.1           | 9 April 1999 (09.04.99) | GB |

| 9908211.7           | 9 April 1999 (09.04.99) | GB |

| 9908214.1           | 9 April 1999 (09.04.99) | GB |

| 9908219.0           | 9 April 1999 (09.04.99) | GB |

| 9908222.4           | 9 April 1999 (09.04.99) | GB |

| 9908225.7           | 9 April 1999 (09.04.99) | GB |

| 9908226.5           | 9 April 1999 (09.04.99) | GB |

| 9908227.3           | 9 April 1999 (09.04.99) | GB |

| 9908228.1           | 9 April 1999 (09.04.99) | GB |

| 9908229.9           | 9 April 1999 (09.04.99) | GB |

(71) Applicant (for all designated States except US): PIXELFU-SION LIMITED [GB/GB]; 2440 The Quadrant, Aztec West, Almondsbury, Bristol BS32 4AQ (GB).

9 April 1999 (09.04.99)

- (75) Inventors/Applicants (for US only): STUTTARD, Dave [GB/GB]; 28 St Georges Avenue, St George, Bristol BS5 8DD (GB). WILLIAMS, Dave [GB/GB]; 45 Railton Jones Close. Stoke Gifford, Gloucestershire BS34 8XY (GB). O'DEA, Eamon [IE/GB]; 32 Richmond Park Road, Clifton, Bristol BS8 3AP (GB). FAULDS, Gordon [GB/GB]; 21 High Furlong, Cam, Nr Dursley, Gloucestershire GL11 5UZ (GB). RHODES, John [GB/GB]; 40 Ormonds Close, Bradley Stoke, Bristol BS32 0DX (GB). CAMERON, Ken [GB/GB]; 29 Little Meadow, Bristol BS32 8AT (GB). ATKIN, Phil [GB/GB]; 2440 The Quadrant, Aztec West, Almondsbury, Bristol BS32 4AQ (GB). WINSER, Paul [GB/GB]; 8 Oakleigh House, Bridge Road, Leigh Woods, Bristol BS8 3PB (GB). DAVID, Russell [GB/GB]; 8 Rowan Drive, Wootton Bassett, Wiltshire SN4 7ES (GB). McCONNELL, Ray [GB/GB]; Flat 11, 1 Clifton Road, Clifton, Bristol BS8 1AE (GB). DAY, Tim [GB/GB]; 33 Rosebery Avenue, St Werburghs, Bristol BS2 9TW (GB). GREER, Trey [GB/GB]; 330 Sunset Creek Circle, Chapel Hill, NC 27516 (US).

- (74) Agent: VIGARS, Christopher, Ian; Haseltine Lake & Co, Imperial House, 15-19 Kingsway, London WC2B 6UD (GB).

- (81) Designated States: AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW, ARIPO patent (GH, GM, KE, LS, MW, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

### **Published**

Without international search report and to be republished upon receipt of that report.

### (54) Title: PARALLEL DATA PROCESSING APPARATUS

#### (57) Abstract

9908230.7

A data processing apparatus comprises a SIMD (single instruction multiple data) array (10) of processing elements. The processing elements are operably divided into a plurality of processing blocks, the processing blocks being operable to process respective groups of data items.

IG Fy 1004

## $FOR\ THE\ PURPOSES\ OF\ INFORMATION\ ONLY$

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

|    | •                        | <b>L</b> | •                   | 1.0 | 1                     |    |                          |

|----|--------------------------|----------|---------------------|-----|-----------------------|----|--------------------------|

| AL | Albania                  | ES       | Spain               | LS  | Lesotho               | SI | Slovenia                 |

| AM | Armenia                  | FI       | Finland             | LT  | Lithuania             | SK | Slovakia                 |

| AT | Austria                  | FR       | France              | LU  | Luxembourg            | SN | Senegal                  |

| AU | Australia                | GA       | Gabon               | LV  | Latvia                | SZ | Swaziland                |

| AZ | Azerbaijan               | GB       | United Kingdom      | MC  | Monaco                | TD | Chad                     |

| BA | Bosnia and Herzegovina   | GE       | Georgia             | MD  | Republic of Moldova   | TG | Togo                     |

| BB | Barbados                 | GH       | Ghana               | MG  | Madagascar            | TJ | Tajikistan               |

| BE | Belgium                  | GN       | Guinea              | MK  | The former Yugoslav   | TM | Turkmenistan             |

| BF | Burkina Faso             | GR       | Greece              |     | Republic of Macedonia | TR | Turkey                   |

| BG | Bulgaria                 | HU       | Hungary             | ML  | Mali                  | TT | Trinidad and Tobago      |

| ВJ | Benin                    | IE       | Ireland             | MN  | Mongolia              | UA | Ukraine                  |

| BR | Brazil                   | IL       | Israel              | MR  | Mauritania            | UG | Uganda                   |

| BY | Belarus                  | IS       | Iceland             | MW  | Malawi                | US | United States of America |

| CA | Canada                   | IT       | Italy               | MX  | Mexico                | UZ | Uzbekistan               |

| CF | Central African Republic | JP       | Japan               | NE  | Niger                 | VN | Viet Nam                 |

| CG | Congo                    | KE       | Kenya               | NL  | Netherlands           | YU | Yugoslavia               |

| CH | Switzerland              | KG       | Kyrgyzstan          | NO  | Norway                | zw | Zimbabwe                 |

| CI | Côte d'Ivoire            | KP       | Democratic People's | NZ  | New Zealand           |    |                          |

| CM | Cameroon                 |          | Republic of Korea   | PL  | Poland                |    |                          |

| CN | China                    | KR       | Republic of Korea   | PT  | Portugal              |    |                          |

| CU | Cuba                     | KZ       | Kazakstan           | RO  | Romania               |    |                          |

| CZ | Czech Republic           | LC       | Saint Lucia         | RU  | Russian Federation    |    |                          |

| DE | Germany                  | LI       | Liechtenstein       | SD  | Sudan                 |    |                          |

| DK | Denmark                  | LK       | Sri Lanka           | SE  | Sweden                |    |                          |

| EE | Estonia                  | LR       | Liberia             | SG  | Singapore             |    |                          |

|    |                          |          |                     |     |                       |    |                          |

WO 00/62182 PCT/GB00/01332

-1-

### PARALLEL DATA PROCESSING APPARATUS

The present invention relates to parallel data processing apparatus, and in particular to SIMD (single instruction multiple data) processing apparatus.

### BACKGROUND OF THE INVENTION

Increasingly, data processing systems are required to process large amounts of data. In addition, users of 10 such systems are demanding that the speed of data processing is increased. One particular example of the need for high speed processing of massive amounts of data is in the computer graphics field. In computer graphics, large amounts of data are produced that 15 relate to, for example, geometry, texture, and colour of objects and shapes to be displayed on a screen. Users of computer graphics are increasingly demanding more lifelike and faster graphical displays which increases the amount of data to be processed and 20 increases the speed at which the data must be processed.

A previously proposed processing architecture for processing large amounts of data in a computer system uses a Single Instruction Multiple Data (SIMD) array of processing elements. In such an array all of the processing elements receive the same instruction stream, but operate on different respective data items.

30 Such an architecture can thereby process data in parallel, but without the need to produce parallel instruction streams. This can be an efficient and relatively simple way of obtaining good performance from a parallel processing machine.

35

5

However, the SIMD architecture can be inefficient when a system has to process a large number of relatively small data item groups. For example, for a SIMD array processing data relating to a graphical display screen, for a small graphical primitive such as a triangle, only relatively few processing elements of the array will be enabled to process data relating to the primitive. In that case, a large proportion of the processing elements may remain unused while data is being processed for a particular group.

-2-

It is therefore desirable to produce a system which can overcome or alleviate this problem.

#### 15 SUMMARY OF THE INVENTION

5

10

20

According to one aspect of the present invention, there is provided a data processing apparatus comprising a SIMD (single instruction multiple data) array of processing elements, wherein the processing elements are operably divided into a plurality of processing blocks, the processing blocks being operable to process respective groups of data items.

- According to another aspect of the present invention, 25 there is provided a data processing apparatus comprising an array of processing elements, which are operable to process respective data items in accordance with a common received instruction, wherein the processing elements are operably divided into a 30 plurality of processing blocks having at least one processing element, the processing blocks being operable to process respective groups of data items.

- 35 Various further aspects of the present invention are

-3-

exemplified by the attached claims.

### BRIEF DESCRIPTION OF THE DRAWINGS

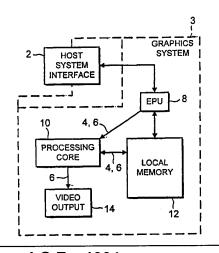

| 5  | Figure 1 is a block diagram illustrating a graphics     |

|----|---------------------------------------------------------|

|    | data processing system;                                 |

|    | Figure 2 is a more detailed block diagram illustrating  |

|    | the graphics data processing system of Figure 1;        |

|    | Figure 3 is a block diagram of a processing core of the |

| 10 | system of Figure 2;                                     |

|    | Figure 4 is a block diagram of a thread manager of the  |

|    | system of Figure 3;                                     |

|    | Figure 5 is a block diagram of a array controller of    |

|    | the system of Figure 3;                                 |

| 15 | Figure 6 is a block diagram of an instruction issue     |

|    | state machine of the channel controller of Figure 3;    |

|    | Figure 7 is a block diagram of a binning unit of the    |

|    | system of Figure 3:                                     |

- system of Figure 3;

- Figure 8 is a block diagram of a processing block of the system of Figure 3; 20

- Figure 9 is a flowchart illustrating data processing using the system of Figures 1 to 8; Figure 10 is a more detailed block diagram of a thread processor of the thread manager of Figure 4;

- Figure 11 is a block diagram of a processor unit of the 25 processing block of Figure 8; Figure 12 is a block diagram illustrating a processing

- element interface; Figure 13 is a block diagram illustrating a block I/O

- Figure 14 is a block diagram of part of the processor unit of Figure 11; and

- Figure 15 is a block diagram of another part of the processor unit of Figure 11.

30

interface:

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.