| Under the Paperwork Reduction Act of 1995, no pers                                                                                                                                                                                                      | ons are required to                     | U.S. Patent and Tradem                                                          | PTO/SB/122 (11-08)<br>ved for use through 11/30/2011. OMB 0651-0035<br>ark Office; U.S. DEPARTMENT OF COMMERCE<br>unders it disalays a valid OMB control number |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                         |                                         | Application Number                                                              | na                                                                                                                                                              |

| CHANGE OF<br>CORRESPONDENCE ADD                                                                                                                                                                                                                         | RESS                                    | Filing Date                                                                     | herewith                                                                                                                                                        |

| Application                                                                                                                                                                                                                                             |                                         | First Named Inventor                                                            | Steven Morein                                                                                                                                                   |

| Address to:                                                                                                                                                                                                                                             |                                         | Art Unit                                                                        | na                                                                                                                                                              |

| Commissioner for Patents<br>P.O. Box 1450                                                                                                                                                                                                               |                                         | Examiner Name                                                                   | na                                                                                                                                                              |

| Alexandria, VA 22313-1450                                                                                                                                                                                                                               |                                         | Attorney Docket Number                                                          | 00100.36.0001                                                                                                                                                   |

| Please change the Correspondence Add                                                                                                                                                                                                                    | ress for the at                         | oove-identified patent applica                                                  | tion to:                                                                                                                                                        |

| The address associated with Customer Number:                                                                                                                                                                                                            |                                         | 29153                                                                           | 7                                                                                                                                                               |

| OR                                                                                                                                                                                                                                                      |                                         | <u> </u>                                                                        |                                                                                                                                                                 |

| Firm or<br>Individual Name                                                                                                                                                                                                                              |                                         | a                                                                               |                                                                                                                                                                 |

| Address                                                                                                                                                                                                                                                 |                                         |                                                                                 | te de la companya de                                                  |

| City                                                                                                                                                                                                                                                    |                                         | State                                                                           | Zip                                                                                                                                                             |

| Country                                                                                                                                                                                                                                                 |                                         |                                                                                 |                                                                                                                                                                 |

| Telephone                                                                                                                                                                                                                                               |                                         | Email                                                                           |                                                                                                                                                                 |

| This form cannot be used to change the or<br>data associated with an existing Custome                                                                                                                                                                   | data associate<br>er Number use         | d with a Customer Number.<br>• "Request for Customer Nun                        | To change the<br>ber Data Change" (PTO/SB/124).                                                                                                                 |

| I am the:                                                                                                                                                                                                                                               |                                         |                                                                                 |                                                                                                                                                                 |

| Applicant/Inventor                                                                                                                                                                                                                                      |                                         |                                                                                 |                                                                                                                                                                 |

| Assignee of record of the e<br>Statement under 37 CFR 3                                                                                                                                                                                                 |                                         | osed. (Form PTO/SB/96).                                                         |                                                                                                                                                                 |

| Attorney or agent of record                                                                                                                                                                                                                             | . Registration                          | Number <u>34,414</u>                                                            |                                                                                                                                                                 |

|                                                                                                                                                                                                                                                         |                                         | lication transmittal letter in a<br>R 1.33(a)(1). Registration Nu               |                                                                                                                                                                 |

| Signature /Christopher J. Reckamp/                                                                                                                                                                                                                      | <u> </u>                                |                                                                                 |                                                                                                                                                                 |

| Typed or Printed<br>Name Christopher J. Reckamp                                                                                                                                                                                                         |                                         |                                                                                 |                                                                                                                                                                 |

| Date May 17, 2011                                                                                                                                                                                                                                       |                                         | Telephone<br>312-609-7599                                                       |                                                                                                                                                                 |

| NOTE: Signatures of all the inventors or assignees of recor<br>forms if more than one signature is required, see below*.                                                                                                                                | d of the entire inter                   |                                                                                 | uired. Submit multiple                                                                                                                                          |

| *Total of 1forms are submitted.                                                                                                                                                                                                                         |                                         |                                                                                 |                                                                                                                                                                 |

| This collection of information is required by 37 CFR 1.33. T<br>to process) an application. Confidentiality is governed by<br>including gathering, preparing, and submitting the complete<br>the amount of time you require to complete this form and/o | 35 U.S.C. 122 and<br>d application form | 1 37 CFR 1.11 and 1.14. This collect<br>to the USPTO. Time will vary dependent. | tion is estimated to take 3 minutes to complete, ding upon the individual case. Any comments on                                                                 |

including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

If you need assistance in completing the form, call 1-800-PTO-9199 and select option 2.

**LG Ex. 1002 LG v. ATI IPR2017-01225** LG Ex. 1002, pg 1 Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it contains a valid OMB control number.

| Application Da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ta Shoot 37 CED 1 76                                        | Attorney Docket Number | 00100.36.0001 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------|---------------|--|--|

| Application Data Sheet 37 CFR 1.76                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             | Application Number     |               |  |  |

| Title of Invention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER |                        |               |  |  |

| The application data sheet is part of the provisional or nonprovisional application for which it is being submitted. The following form contains the bibliographic data arranged in a format specified by the United States Patent and Trademark Office as outlined in 37 CFR 1.76. This document may be completed electronically and submitted to the Office in electronic format using the Electronic Filing System (EFS) or the document may be printed and included in a paper filed application. |                                                             |                        |               |  |  |

## Secrecy Order 37 CFR 5.2

Portions or all of the application associated with this Application Data Sheet may fall under a Secrecy Order pursuant to 37 CFR 5.2 (Paper filers only. Applications that fall under Secrecy Order may not be filed electronically.)

## **Applicant Information:**

$\square$

| Applic              | Applicant 1 Remove                                                                                           |              |           |                    |                      |               |       |             |           |        |              |                       |        |

|---------------------|--------------------------------------------------------------------------------------------------------------|--------------|-----------|--------------------|----------------------|---------------|-------|-------------|-----------|--------|--------------|-----------------------|--------|

| -                   |                                                                                                              | Authority 🖲  | Inventor  | OL                 | egal                 | Representativ | e und | er 35 l     | J.S.C. 11 | 7      | OParty of In | terest under 35 U.S.  | C. 118 |

| Prefix              |                                                                                                              | /en Name     | ł         |                    |                      | Middle Na     | me    |             |           | Fam    | ily Name     |                       | Suffix |

|                     | Ste                                                                                                          | phen         |           |                    |                      | L.            |       |             |           | More   | ein          |                       |        |

| Resid               | dence                                                                                                        | e Informatio | า (Select | One)               | $\odot$              | US Residenc   | y (   |             | on US Res | sidenc | y 🔿 Activ    | e US Military Service |        |

| City                | Car                                                                                                          | mbridge      |           |                    | St                   | ate/Province  | e N   | /IA         | Countr    | y of F | Residence i  | US                    |        |

| Citizer             | nshij                                                                                                        | p under 37 C | FR 1.41(I | <b>b)</b> i        | US                   | 3             |       |             |           |        |              |                       |        |

|                     | Mailing Address of Applicant:                                                                                |              |           |                    |                      |               |       |             |           |        |              |                       |        |

| Addre               | ess 1                                                                                                        |              | 10 Maga   | zine               |                      |               |       |             |           |        |              |                       |        |

| Addre               | ess 2                                                                                                        |              | Apt. 801  |                    |                      |               |       |             |           |        |              |                       |        |

| City                |                                                                                                              | Cambridge    |           |                    |                      |               |       | Stat        | e/Provir  | nce    | MA           |                       |        |

| Posta               | l Cod                                                                                                        | le           | 02139     |                    |                      |               | Cou   | intryi      | US        |        |              |                       |        |

| Annlic              | Applicant 2 Remove                                                                                           |              |           |                    |                      |               |       |             |           |        |              |                       |        |

|                     | Applicant Authority Inventor Clegal Representative under 35 U.S.C. 117 Party of Interest under 35 U.S.C. 118 |              |           |                    |                      |               |       |             |           |        |              |                       |        |

| Prefix Given Name   |                                                                                                              |              |           |                    | Middle Name          |               |       | Family Name |           |        | Suffix       |                       |        |

|                     | Lau                                                                                                          | irent        |           |                    |                      |               |       |             | Lefebvre  |        |              |                       |        |

| Resid               | lence                                                                                                        | e Informatio | n (Select | One)               | 0                    | US Residenc   | y (   | No          | on US Res | sidenc | y 🔿 Active   | e US Military Service |        |

| City                | Lach                                                                                                         | ngnaie       |           |                    | Co                   | ountry Of Re  | sider | ncei        | CA        |        |              |                       |        |

| Citizer             | nshij                                                                                                        | p under 37 C | FR 1.41(I | b)i                | CA                   | ١             |       |             | 1         |        |              |                       |        |

| Mailin              | g Ad                                                                                                         | ldress of Ap | plicant:  |                    |                      |               |       |             |           |        |              |                       |        |

| Addre               | ess 1                                                                                                        |              | 124 Pare  | encher             | е                    |               |       |             |           |        |              |                       |        |

| Addre               | ess 2                                                                                                        |              |           |                    |                      |               |       |             |           |        |              |                       |        |

| City                |                                                                                                              | Lachgnaie    |           |                    |                      |               |       | Stat        | e/Provir  | nce    | QC           |                       |        |

| Postal Code J6W 6A5 |                                                                                                              |              |           | <b>Countryi</b> CA |                      |               |       |             |           |        |              |                       |        |

| Applic              | rant                                                                                                         | 3            |           |                    |                      |               |       |             | 1         |        |              | Remove                |        |

|                     |                                                                                                              |              | Inventor  | OL                 | egal                 | Representativ | e und | er 35 l     | J.S.C. 11 | 7      | OParty of In | terest under 35 U.S.  | C. 118 |

| Prefix              |                                                                                                              | /en Name     | I         |                    |                      | Middle Na     | me    |             |           | Fam    | ily Name     |                       | Suffix |

|                     | And                                                                                                          | drew         |           |                    |                      | E.            |       |             |           | Grub   | er           |                       |        |

| Resid               | lence                                                                                                        | e Informatio | n (Select | One)               | $\overline{\bullet}$ | US Residenc   | y (   |             | on US Res | sidenc | y 🔿 Active   | e US Military Service |        |

| City                | Arli                                                                                                         | ngton        |           |                    | St                   | ate/Province  | e N   | ЛА          | Countr    | y of F | Residence i  | US                    |        |

PTC/SB/14 (11-08) Approved for use through 09/30/2010. OMB 0651-0032 U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it contains a valid OMB control number

| Attorney Docket Number 00100.36.0001 |                                           |          |       |                       |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

|--------------------------------------|-------------------------------------------|----------|-------|-----------------------|-------------|----------|------------------------------------------------------------|------------------------------------|--------------------|---------------------|--------------|---------------|----------------------|---------|

| Application Data Sheet 37 CFR 1.76   |                                           |          |       |                       |             |          |                                                            | 00100.                             | 00.0001            |                     |              |               |                      |         |

| ••                                   |                                           |          |       |                       | Applica     | ation N  | lumbe                                                      | r                                  |                    |                     |              |               |                      |         |

| Title of                             | Inve                                      | ention   | GRA   | APHICS PI             | ROCE        | SSING A  | RCHITEC                                                    | TURE                               | EMPL               | OYING A             | UNIFIEI      | D SHADER      |                      |         |

|                                      |                                           |          |       |                       | • • : 1     |          |                                                            |                                    |                    |                     |              |               |                      |         |

|                                      |                                           |          |       | FR 1.41(              | b) i        | US       |                                                            |                                    |                    |                     |              |               |                      |         |

| Mailing                              | g Ac                                      | ldress o | f Ap  | plicant:              |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

| Addres                               | ss 1                                      |          |       | 215 Plea              | isant S     | treet    |                                                            |                                    |                    |                     |              |               |                      |         |

| Addres                               | ss 2                                      |          |       |                       |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

| City                                 |                                           | Arlingto | n     |                       |             |          |                                                            |                                    | Stat               | e/Provin            | ice          | MA            |                      |         |

| Postal                               | Co                                        | de       |       | 02476                 |             |          |                                                            | Cou                                | intry <sup>i</sup> | US                  | US           |               |                      |         |

| Applic                               | Applicant 4                               |          |       |                       |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

| Applic                               | ant                                       | Authorit | ty 💿  | Inventor              |             | egal Rep | resentativ                                                 | e und                              | er 35 l            | J.S.C. 117          | 7            | )Party of Ini | terest under 35 U.S. | .C. 118 |

| Prefix                               |                                           | ven Nam  |       |                       |             | M        | Middle Name Fan                                            |                                    |                    | Family              | amily Name S |               | Suffix               |         |

|                                      | An                                        | di       |       |                       |             |          | Skende                                                     |                                    |                    |                     |              |               |                      |         |

| Resid                                | enc                                       | e Inform | atior | ו (Select             | One)        | 🕑 US     | JS Residency 🚫 Non US Residency 🚫 Active US Military Servi |                                    |                    | US Military Service | ;            |               |                      |         |

| City                                 | Sh                                        | rewsbury |       |                       |             | State/   | Province                                                   | vince MA Country of Residence i US |                    |                     | US           |               |                      |         |

| Citizen                              | nshi                                      | p under  | 37 C  | FR 1.41(              | <b>b)</b> i | US       |                                                            |                                    |                    |                     |              |               |                      |         |

| Mailing                              | g Ac                                      | ldress o | f Ap  | plicant:              |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

| Addres                               | ss 1                                      |          |       | 49 Sheri              | dan Dr      | ive, #11 |                                                            |                                    |                    |                     |              |               |                      |         |

| Addres                               | Address 2                                 |          |       |                       |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

| City                                 | City Shrewsbury State/Province MA         |          |       |                       |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

| Postal                               | Postal Code 01545 Country <sup>i</sup> US |          |       |                       |             |          |                                                            |                                    |                    |                     |              |               |                      |         |

|                                      |                                           |          |       | Listed -<br>m by sele |             |          |                                                            | nform                              | ation              | blocks i            | may be       |               | Add                  |         |

## **Correspondence Information:**

| Enter either Customer Number or complete the Correspondence Information section below.<br>For further information see 37 CFR 1.33(a). |                          |                        |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|--|--|--|--|

| An Address is being provided for the correspondence Information of this application.                                                  |                          |                        |  |  |  |  |

| Customer Number                                                                                                                       | 29153                    |                        |  |  |  |  |

| Email Address                                                                                                                         | creckamp@vedderprice.com | Add Email Remove Email |  |  |  |  |

## **Application Information:**

| Title of the Invention                  | GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER |   |                                           |  |  |

|-----------------------------------------|-------------------------------------------------------------|---|-------------------------------------------|--|--|

| Attorney Docket Number                  | 00100.36.0001                                               |   | Small Entity Status Claimed               |  |  |

| Application Type                        | Nonprovisional                                              |   |                                           |  |  |

| Subject Matter                          | Utility                                                     |   |                                           |  |  |

| Suggested Class (if any)                |                                                             |   | Sub Class (if any)                        |  |  |

| Suggested Technology C                  | enter (if any)                                              |   |                                           |  |  |

| Total Number of Drawing Sheets (if any) |                                                             | 5 | Suggested Figure for Publication (if any) |  |  |

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it contains a valid OMB control number.

| Application Da     | ta Sheet 37 CFR 1.76                                        | Attorney Docket Number | 00100.36.0001 |  |  |

|--------------------|-------------------------------------------------------------|------------------------|---------------|--|--|

|                    |                                                             | Application Number     |               |  |  |

| Title of Invention | GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER |                        |               |  |  |

## **Publication Information:**

| Request Early Publication (Fee required at time of Request 37 CFR 1.219)                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Request Not to Publish. I hereby request that the attached application not be published under 35 U.S.                                                                                                                                                                      |

| C. 122(b) and certify that the invention disclosed in the attached application has not and will not be the subject of an application filed in another country, or under a multilateral international agreement, that requires publication at eighteen months after filing. |

### **Representative Information:**

| this information in the Applie<br>Enter either Customer | Representative information should be provided for all practitioners having a power of attorney in the application. Providing this information in the Application Data Sheet does not constitute a power of attorney in the application (see 37 CFR 1.32). Enter either Customer Number or complete the Representative Name section below. If both sections are completed the Customer Number will be used for the Representative Information during processing. |                          |                                     |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------|--|--|--|--|

| Please Select One:                                      | <ul> <li>Customer Number</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             | O US Patent Practitioner | C Limited Recognition (37 CFR 11.9) |  |  |  |  |

| Customer Number                                         | 29153                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |                                     |  |  |  |  |

## **Domestic Benefit/National Stage Information:**

| This section allows for the applicant to either claim benefit under 35 U.S.C. 119(e), 120, 121, or 365(c) or indicate National Stage entry from a PCT application. Providing this information in the application data sheet constitutes the specific reference required by 35 U.S.C. 119(e) or 120, and 37 CFR 1.78(a)(2) or CFR 1.78(a)(4), and need not otherwise be made part of the specification. |                 |                          |                          |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|--------------------------|--|--|--|

| Prior Application Status                                                                                                                                                                                                                                                                                                                                                                               | Pending         |                          | Remove                   |  |  |  |

| Application Number                                                                                                                                                                                                                                                                                                                                                                                     | Continuity Type | Prior Application Number | Filing Date (YYYY-MM-DD) |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | Continuation of | 12791597                 | 2010-06-01               |  |  |  |

| Additional Domestic Benefi<br>by selecting the <b>Add</b> buttor                                                                                                                                                                                                                                                                                                                                       | Add             |                          |                          |  |  |  |

## **Foreign Priority Information:**

| This section allows for the applicant to claim benefit of foreign priority and to identify any prior foreign application for which priority is not claimed. Providing this information in the application data sheet constitutes the claim for priority as required by 35 U.S.C. 119(b) and 37 CFR 1.55(a). |                      |                                 |                  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------|------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                             |                      |                                 | Remove           |  |  |  |

| Application Number                                                                                                                                                                                                                                                                                          | Country <sup>i</sup> | Parent Filing Date (YYYY-MM-DD) | Priority Claimed |  |  |  |

|                                                                                                                                                                                                                                                                                                             |                      |                                 | 🔿 Yes 🔿 No       |  |  |  |

| Additional Foreign Priority Data may be generated within this form by selecting the Add button.                                                                                                                                                                                                             |                      |                                 |                  |  |  |  |

### Assignee Information:

Providing this information in the application data sheet does not substitute for compliance with any requirement of part 3 of Title 37 of the CFR to have an assignment recorded in the Office.

Assignee 1

Remove

#### PTO/SB/14 (11-08)

Approved for use through 09/30/2010. OMB 0651-0032 U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it contains a valid OMB control number.

| Application Da                     | ta Shoot 37 CED 1 76                                        | Attorney Docket Number | 00100.36.0001 |  |

|------------------------------------|-------------------------------------------------------------|------------------------|---------------|--|

| Application Data Sheet 37 CFR 1.76 |                                                             | Application Number     |               |  |

| Title of Invention                 | GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER |                        |               |  |

| If the Assignee is an Organization check here.                                      |                           |                              |         |  |  |  |

|-------------------------------------------------------------------------------------|---------------------------|------------------------------|---------|--|--|--|

| Organization Name                                                                   | ATI Technologies ULC      | 1 Technologies ULC           |         |  |  |  |

| Mailing Address Infor                                                               | mation:                   |                              |         |  |  |  |

| Address 1                                                                           | 1 Commerce Valley Drive E | 1 Commerce Valley Drive East |         |  |  |  |

| Address 2                                                                           |                           |                              |         |  |  |  |

| City                                                                                | Markham                   | State/Province               | ON      |  |  |  |

| Country <sup>i</sup> CA                                                             |                           | Postal Code                  | L3T 7X6 |  |  |  |

| Phone Number                                                                        | 905-882-2600              | Fax Number                   |         |  |  |  |

| Email Address                                                                       |                           |                              |         |  |  |  |

| Additional Assignee Data may be generated within this form by selecting the Add Add |                           |                              |         |  |  |  |

### Signature:

| A signature of the applicant or representative is required in accordance with 37 CFR 1.33 and 10.18. Please see 37 CFR 1.4(d) for the form of the signature. |                          |           |         |                     |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|---------|---------------------|------------|

| Signature                                                                                                                                                    | /Christopher J. Reckamp/ |           |         | Date (YYYY-MM-DD)   | 2011-05-17 |

| First Name                                                                                                                                                   | Christopher              | Last Name | Reckamp | Registration Number | 34414      |

This collection of information is required by 37 CFR 1.76. The information is required to obtain or retain a benefit by the public which is to file (and by the USPTO to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.14. This collection is estimated to take 23 minutes to complete, including gathering, preparing, and submitting the completed application data sheet form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. **SEND TO: Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.**

## **Privacy Act Statement**

| Electronic Patent Application Fee Transmittal |               |                     |                |                  |                         |

|-----------------------------------------------|---------------|---------------------|----------------|------------------|-------------------------|

| Application Number:                           |               |                     |                |                  |                         |

| Filing Date:                                  |               |                     |                |                  |                         |

| Title of Invention:                           | GR            | APHICS PROCESSIN    | G ARCHITECTU   | RE EMPLOYING A U | INIFIED SHADER          |

| First Named Inventor/Applicant Name:          | Ste           | phen L. Morein      |                |                  |                         |

| Filer:                                        | Ch            | ristopher J. Reckam | p/Christine Wr | ght              |                         |

| Attorney Docket Number:                       | 00100.36.0001 |                     |                |                  |                         |

| Filed as Large Entity                         | 1             |                     |                |                  |                         |

| Utility under 35 USC 111(a) Filing Fees       |               |                     |                |                  |                         |

| Description                                   |               | Fee Code            | Quantity       | Amount           | Sub-Total in<br>USD(\$) |

| Basic Filing:                                 |               |                     |                |                  |                         |

| Utility application filing                    |               | 1011                | 1              | 330              | 330                     |

| Utility Search Fee                            |               | 1111                | 1              | 540              | 540                     |

| Utility Examination Fee                       |               | 1311                | 1              | 220              | 220                     |

| Pages:                                        |               |                     |                |                  |                         |

| Claims:                                       |               |                     |                |                  |                         |

| Independent claims in excess of 3             |               | 1201                | 4              | 220              | 880                     |

| Miscellaneous-Filing:                         |               |                     |                |                  |                         |

| Petition:                                     |               |                     |                |                  |                         |

| Description                       | Fee Code | Quantity  | Amount | Sub-Total in<br>USD(\$) |

|-----------------------------------|----------|-----------|--------|-------------------------|

| Patent-Appeals-and-Interference:  |          |           |        |                         |

| Post-Allowance-and-Post-Issuance: |          |           |        |                         |

| Extension-of-Time:                |          |           |        |                         |

| Miscellaneous:                    |          |           |        |                         |

|                                   | Tot      | al in USD | (\$)   | 1970                    |

| Electronic Acl                       | knowledgement Receipt                                       |

|--------------------------------------|-------------------------------------------------------------|

| EFS ID:                              | 10111290                                                    |

| Application Number:                  | 13109738                                                    |

| International Application Number:    |                                                             |

| Confirmation Number:                 | 2020                                                        |

| Title of Invention:                  | GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER |

| First Named Inventor/Applicant Name: | Stephen L. Morein                                           |

| Customer Number:                     | 29153                                                       |

| Filer:                               | Christopher J. Reckamp/Christine Wright                     |

| Filer Authorized By:                 | Christopher J. Reckamp                                      |

| Attorney Docket Number:              | 00100.36.0001                                               |

| Receipt Date:                        | 17-MAY-2011                                                 |

| Filing Date:                         |                                                             |

| Time Stamp:                          | 17:29:16                                                    |

| Application Type:                    | Utility under 35 USC 111(a)                                 |

# Payment information:

| Submitted with Payment                                                                                                       | yes             |  |

|------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| Payment Type                                                                                                                 | Deposit Account |  |

| Payment was successfully received in RAM                                                                                     | \$1970          |  |

| RAM confirmation Number                                                                                                      | 4141            |  |

| Deposit Account                                                                                                              | 220259          |  |

| Authorized User                                                                                                              |                 |  |

| The Director of the USPTO is hereby authorized to charge indicated fees and credit any overpayment as follows:               |                 |  |

| Charge any Additional Fees required under 37 C.F.R. Section 1.16 (National application filing, search, and examination fees) |                 |  |

| Charge any Additional Fees required under 37 C.F.R. Section 1.17 (Patent application and reexamination processing fees)      |                 |  |

Charge any Additional Fees required under 37 C.F.R. Section 1.19 (Document supply fees)

Charge any Additional Fees required under 37 C.F.R. Section 1.20 (Post Issuance fees)

Charge any Additional Fees required under 37 C.F.R. Section 1.21 (Miscellaneous fees and charges)

| File Listing       | <b>J•</b>                          |                              |                                              |                     | _                   |

|--------------------|------------------------------------|------------------------------|----------------------------------------------|---------------------|---------------------|

| Document<br>Number | Document Description               | File Name                    | File Size(Bytes)/<br>Message Digest          | Multi<br>Part /.zip | Pages<br>(if appl.) |

| 1                  |                                    | 260001 Application of        | 76796                                        |                     | 17                  |

| 1                  |                                    | 360001_Application.pdf       | 5a2195ef350dfe96b37393d43d086ca74d1<br>5a3a1 | yes                 | 17                  |

|                    | Multip                             | art Description/PDF files in | .zip description                             |                     |                     |

|                    | Document Des                       | cription                     | Start                                        | E                   | nd                  |

|                    | Specificati                        | on                           | 1                                            | 1                   | 2                   |

|                    | Claims                             |                              | 13                                           | 1                   | 6                   |

|                    | Abstract                           | t                            | 17                                           | 1                   | 7                   |

| Warnings:          |                                    |                              | 1 1                                          |                     |                     |

| Information:       |                                    |                              |                                              |                     |                     |

| 2                  | Drawings-only black and white line | 360001_Drawings.pdf          | 100418                                       | no                  | 5                   |

| 2                  | drawings                           | Socoon_Drawings.pdf          | 7e6a5c9ce489409aee520309316318a7b7d<br>231f2 | 10                  | 5                   |

| Warnings:          |                                    |                              |                                              |                     |                     |

| Information:       |                                    |                              | · · · · · · · · · · · · · · · · · · ·        |                     |                     |

| 3                  | Oath or Declaration filed          | 360001_Declaration.pdf       | 1711262                                      | no                  | 2                   |

|                    |                                    |                              | 16d034719fb41ea904d604c9522d66d3012<br>96b4e | 110                 |                     |

| Warnings:          |                                    |                              |                                              |                     |                     |

| Information:       |                                    |                              |                                              |                     |                     |

| 4                  | Change of Address                  | 360001_Change.pdf            | 52028                                        | no                  | 1                   |

|                    |                                    |                              | acc3daf05193121879d529dab5b36dbed67<br>ae54e |                     |                     |

| Warnings:          |                                    |                              |                                              |                     |                     |

| Information:       |                                    |                              |                                              |                     |                     |

| 5                  | Application Data Sheet             | 360001_ADS.pdf               | 1032318                                      |                     |                     |

| 5                  | Application Data sheet             | 500001_AD3.pdi               | 0457161c63792567d97d4613dade7a99db<br>6d9934 | no                  | 5                   |

| Warnings:          |                                    |                              |                                              |                     |                     |

| Information:       |                                    |                              |                                              |                     |                     |

| 6                  | Eas Warkshart (PTO 075)            | foo info adf                 | 36605                                        |                     | -<br>-              |

| o                  | Fee Worksheet (PTO-875)            | fee-info.pdf                 | c9542301783d22714df47e76295ef00c9373<br>37ec | no                  | 2                   |

| Warnings:          |                                    |                              | 1                                            |                     |                     |

| Information: |                              |         |

|--------------|------------------------------|---------|

|              | Total Files Size (in bytes): | 3009427 |

This Acknowledgement Receipt evidences receipt on the noted date by the USPTO of the indicated documents, characterized by the applicant, and including page counts, where applicable. It serves as evidence of receipt similar to a Post Card, as described in MPEP 503.

#### New Applications Under 35 U.S.C. 111

If a new application is being filed and the application includes the necessary components for a filing date (see 37 CFR 1.53(b)-(d) and MPEP 506), a Filing Receipt (37 CFR 1.54) will be issued in due course and the date shown on this Acknowledgement Receipt will establish the filing date of the application.

#### National Stage of an International Application under 35 U.S.C. 371

If a timely submission to enter the national stage of an international application is compliant with the conditions of 35 U.S.C. 371 and other applicable requirements a Form PCT/DO/EO/903 indicating acceptance of the application as a national stage submission under 35 U.S.C. 371 will be issued in addition to the Filing Receipt, in due course.

#### New International Application Filed with the USPTO as a Receiving Office

If a new international application is being filed and the international application includes the necessary components for an international filing date (see PCT Article 11 and MPEP 1810), a Notification of the International Application Number and of the International Filing Date (Form PCT/RO/105) will be issued in due course, subject to prescriptions concerning national security, and the date shown on this Acknowledgement Receipt will establish the international filing date of the application.

## GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER RELATED APPLICATIONS

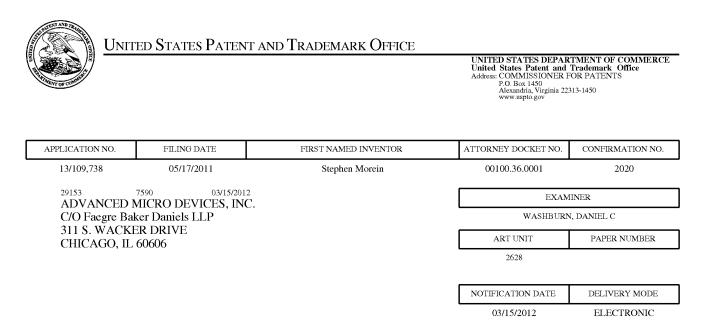

[0001] This application is a continuation of co-pending U.S. Application Serial No. 12/791,597, filed June 1, 2010, entitled "GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER", having as inventors Steven Morein et al., owned by instant assignee and is incorporated herein by reference, which is a continuation of co-pending U.S. Application Serial No. 11/842,256, filed August 21, 2007, entitled "GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER", having as inventors Steven Morein et al., owned by instant assignee and is incorporated herein by reference, which is a continuation of U.S. Application Serial No. 11/117,863, filed April 29, 2005, which has issued into U.S. Patent No. 7,327,369, entitled "GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER", having as inventors Steven Morein et al., and owned by instant assignee and is incorporated herein by reference which is a continuation of U.S. Application Serial No. 10/718,318, filed on November 20, 2003, which has issued into U.S. Patent No. 6,897,871, entitled "GRAPHICS PROCESSING ARCHITECTURE EMPLOYING A UNIFIED SHADER", having as inventors Steven Morein et al., and owned by instant assignee and is incorporated herein by reference.

#### **FIELD OF THE INVENTION**

**[0002]** The present invention generally relates to graphics processors and, more particularly, to a graphics processor architecture employing a single shader.

### **BACKGROUND OF THE INVENTION**

[0003] In computer graphics applications, complex shapes and structures are formed through the sampling, interconnection and rendering of more simple objects, referred to as

primitives. An example of such a primitive is a triangle, or other suitable polygon. These primitives, in turn, are formed by the interconnection of individual pixels. Color and texture are then applied to the individual pixels that comprise the shape based on their location within the primitive and the primitives orientation with respect to the generated shape; thereby generating the object that is rendered to a corresponding display for subsequent viewing.

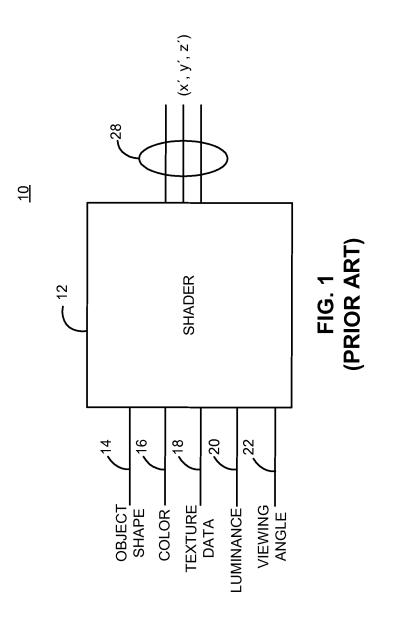

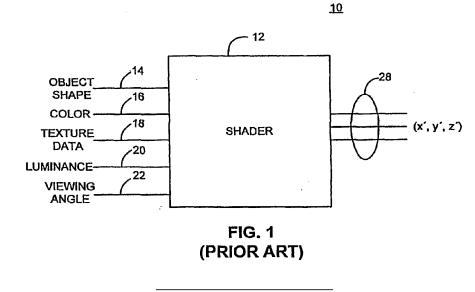

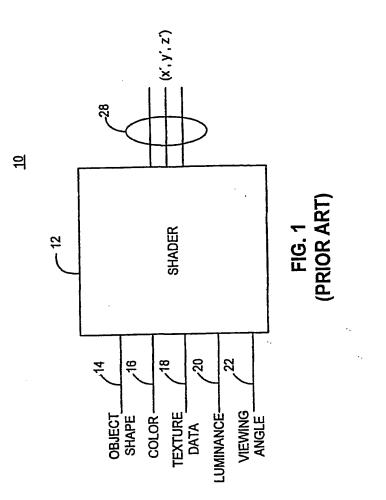

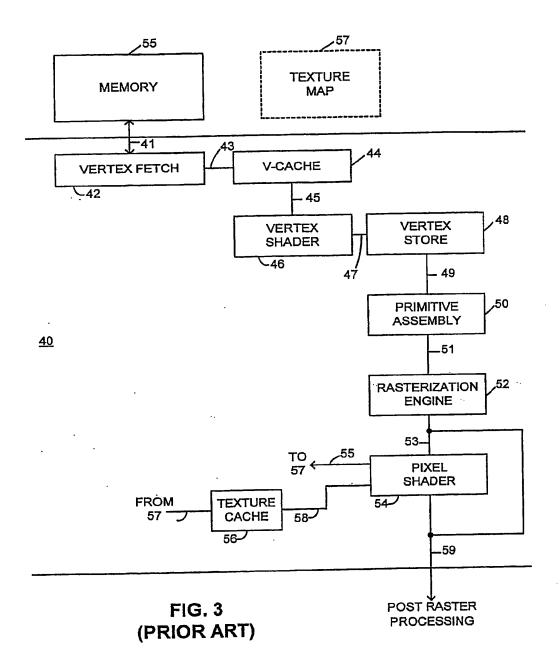

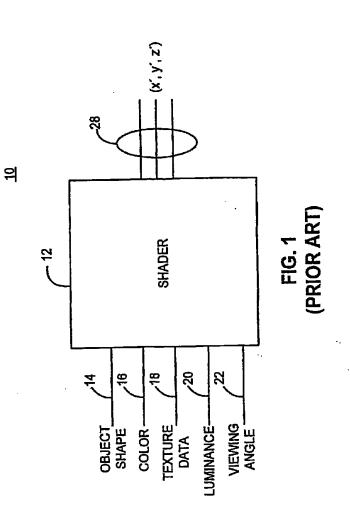

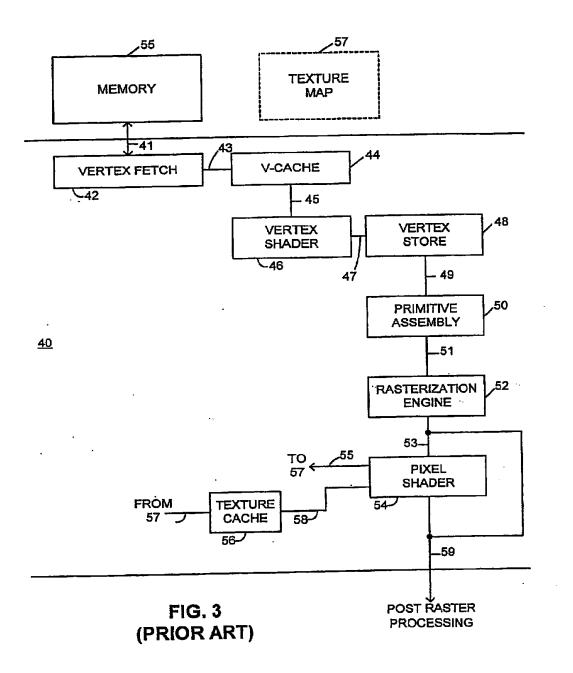

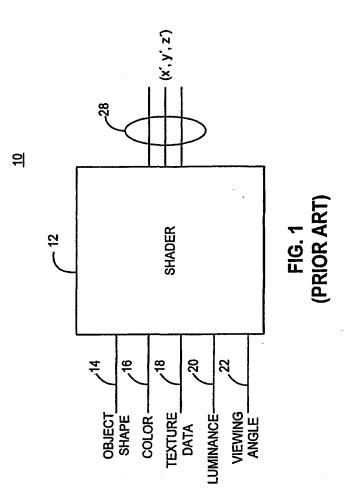

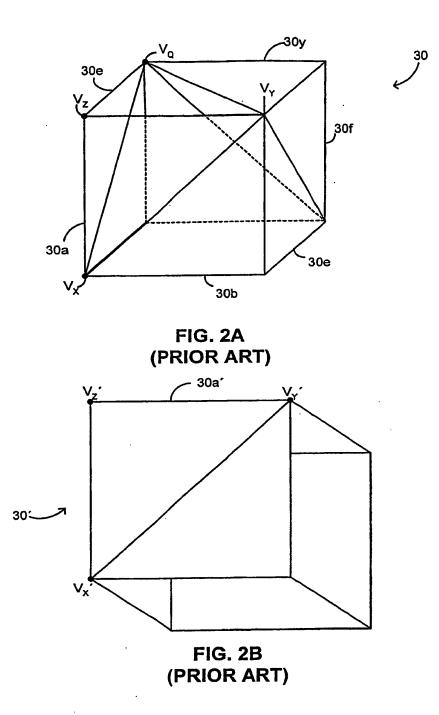

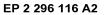

**[0004]** The interconnection of primitives and the application of color and textures to generated shapes are generally performed by a graphics processor. Conventional graphics processors include a series of shaders that specify how and with what corresponding attributes, a final image is drawn on a screen, or suitable display device. As illustrated in FIG. 1, a conventional shader 10 can be represented as a processing block 12 that accepts a plurality of bits of input data, such as, for example, object shape data (14) in object space (x,y,z); material properties of the object, such as color (16); texture information (18); luminance information (20); and viewing angle information (22) and provides output data (28) representing the object with texture and other appearance properties applied thereto (x', y', z').

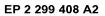

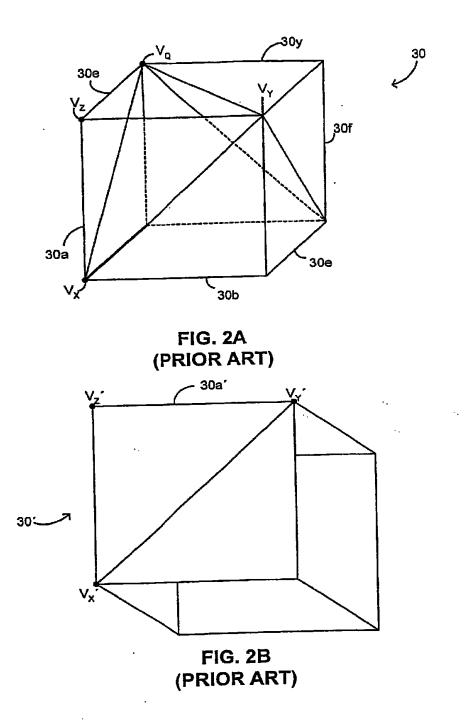

**[0005]** In exemplary fashion, as illustrated in FIGS. 2A-2B, the shader accepts the vertex coordinate data representing cube 30 (FIG. 2A) as inputs and provides data representing, for example, a perspectively corrected view of the cube 30' (FIG. 2B) as an output. The corrected view may be provided, for example, by applying an appropriate transformation matrix to the data representing the initial cube 30. More specifically, the representation illustrated in FIG. 2B is provided by a vertex shader that accepts as inputs the data representing, for example, vertices  $V_X$ ,  $V_Y$  and  $V_Z$ , among others of cube 30 and providing angularly oriented vertices  $V_{X'}$ ,  $V_{Y'}$  and  $V_{Z'}$ , including any appearance attributes of corresponding cube 30'.

**[0006]** In addition to the vertex shader discussed above, a shader processing block that operates on the pixel level, referred to as a pixel shader is also used when generating an object for display. Generally, the pixel shader provides the color value associated with each pixel of a rendered object. Conventionally, both the vertex shader and pixel shader are separate components that are configured to perform only a single transformation or operation. Thus, in order to perform a position and a texture transformation of an input, at least two shading operations and hence, at least two shaders, need to be employed. Conventional graphics processors require the use of both a vertex shader and a pixel shader in order to generate an object. Because both types of shaders are required, known graphics processors are relatively large in size, with most of the real estate being taken up by the vertex and pixel shaders.

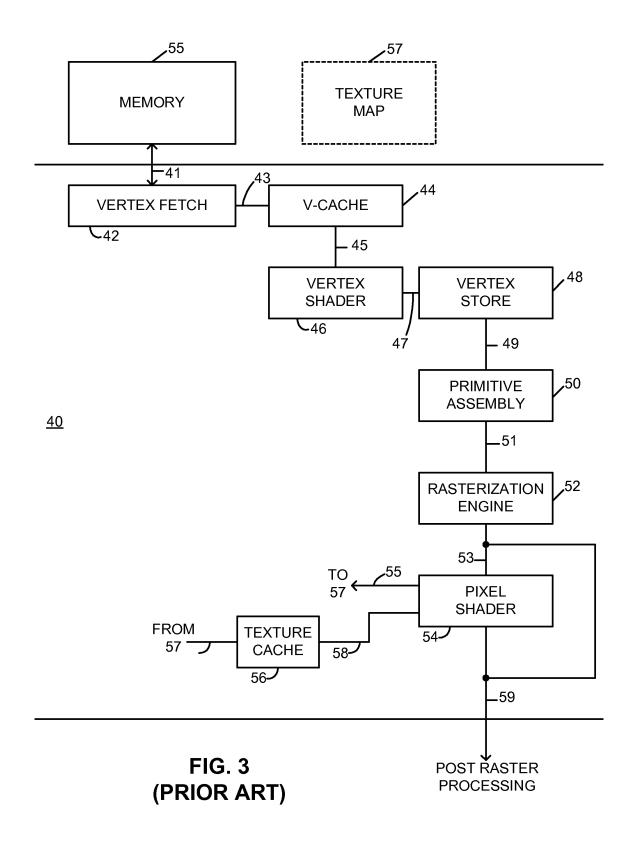

**[0007]** In addition to the real estate penalty associated with conventional graphics processors, there is also a corresponding performance penalty associated therewith. In conventional graphics processors, the vertex shader and the pixel shader are juxtaposed in a sequential, pipelined fashion, with the vertex shader being positioned before and operating on vertex data before the pixel shader can operate on individual pixel data.

[0008] Thus, there is a need for an improved graphics processor employing a shader that is both space efficient and computationally effective.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

[0009] The present invention and the associated advantages and features thereof, will become better understood and appreciated upon review of the following detailed description of the invention, taken in conjunction with the following drawings, where like numerals represent like elements, in which:

[0010] FIG. 1 is a schematic block diagram of a conventional shader;

[0011] FIGS. 2A-2B are graphical representations of the operations performed by the shader illustrated in FIG. 1;

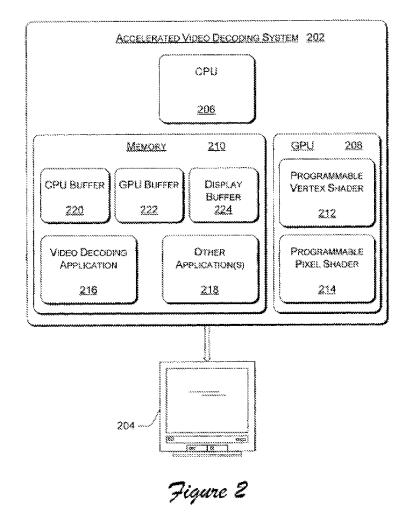

[0012] FIG. 3 is a schematic block diagram of a conventional graphics processor architecture;

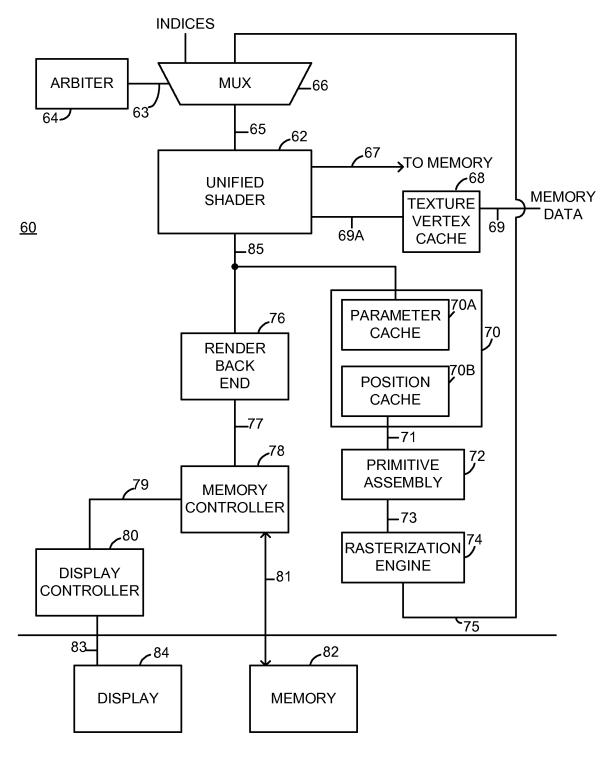

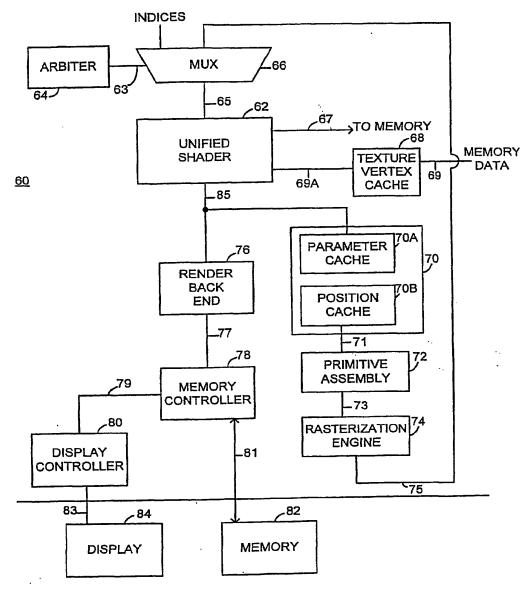

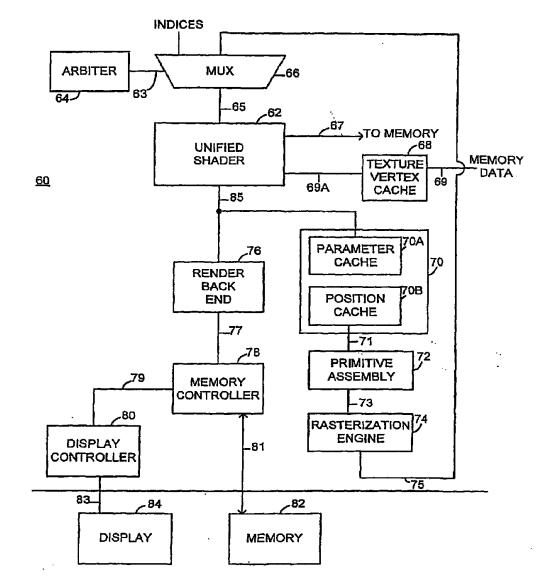

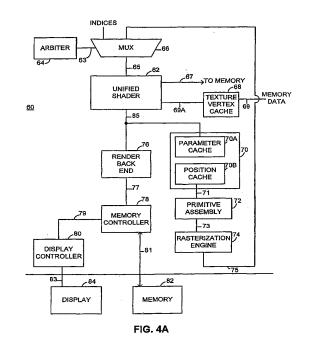

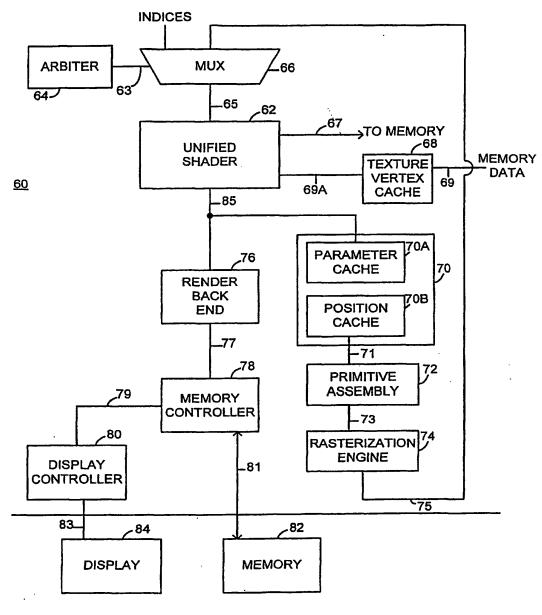

[0013] FIG. 4A is a schematic block diagram of a graphics processor architecture according to the present invention;

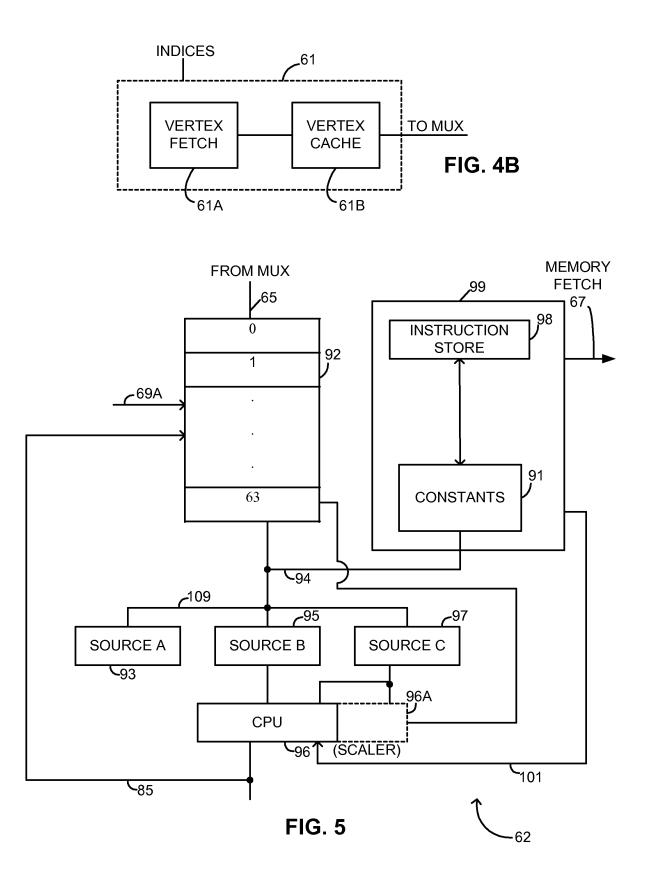

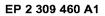

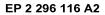

[0014] FIG. 4B is a schematic block diagram of an optional input component to the graphics processor according to an alternate embodiment of the present invention; and

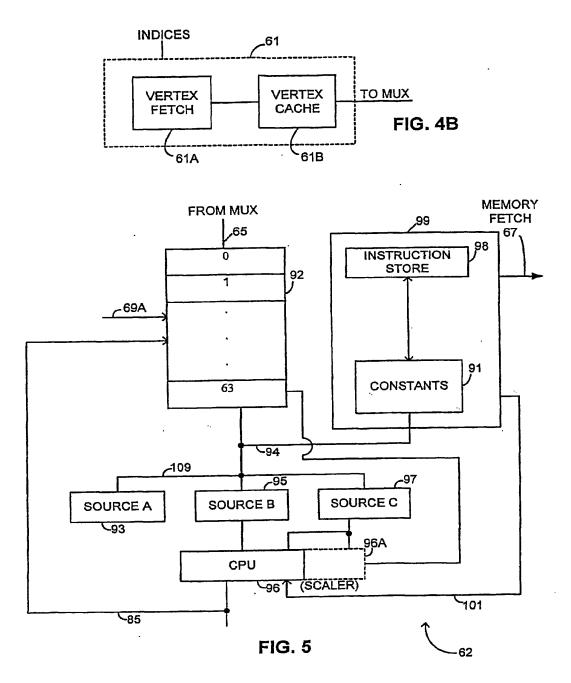

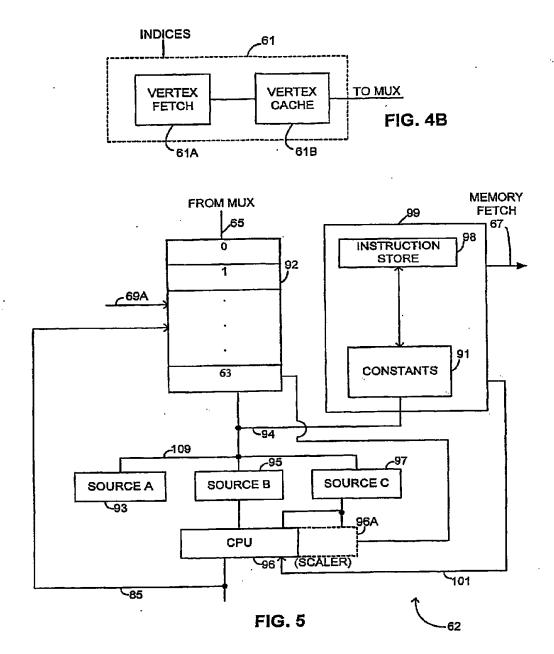

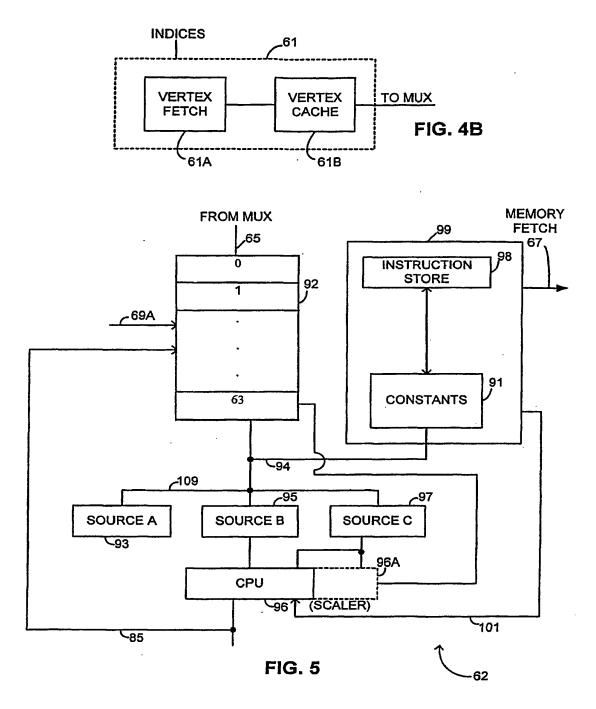

[0015] FIG. 5 is an exploded schematic block diagram of the unified shader employed in the graphics processor illustrated in FIG. 4A.

#### DETAILED DESCRIPTION OF THE INVENTION

**[0016]** Briefly stated, the present invention is directed to a graphics processor that employs a unified shader that is capable of performing both the vertex operations and the pixel operations in a space saving and computationally efficient manner. In an exemplary embodiment, a graphics processor according to the present invention includes an arbiter circuit for selecting one of a plurality of inputs for processing in response to a control signal; and a shader, coupled to the arbiter, operative to process the selected one of the plurality of inputs, the shader including means for performing vertex operations and pixel operations, and wherein the shader performs one of the vertex operations or pixel operations based on the selected one of the plurality of inputs.

**[0017]** The shader includes a general purpose register block for storing at least the plurality of selected inputs, a sequencer for storing logical and arithmetic instructions that are used to perform vertex and pixel manipulation operations and a processor capable of executing

both floating point arithmetic and logical operations on the selected inputs according to the instructions maintained in the sequencer. The shader of the present invention is referred to as a "unified" shader because it is configured to perform both vertex and pixel operations. By employing the unified shader of the present invention, the associated graphics processor is more space efficient than conventional graphics processors because the unified shader takes up less real estate than the conventional multi-shader processor architecture.

[0018] In addition, according to the present invention, the unified shader is more computationally efficient because it allows the shader to be flexibly allocated to pixels or vertices based on workload.