#### Case 8:16-cv-00300-CJC-RAO Document 11 Filed 02/26/16 Page 1 of 3 Page ID #:137

|                                                                                                                                                                                                                                                                                                                                                                                                      | POS-010                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| ATTORNEY OR PARTY WITHOUT ATTORNEY (Name, State Bar number, and address):<br>Steven Cherensky (Bar No. 168275)<br>Tensegrity Law Group LLP<br>555 Twin Dolphin Drive, Suite 650<br>Redwood Shores, CA 94065<br>TELEPHONE NO: 650-802-6000 FAX NO. (Optional): 650-802-6001<br>E-MAIL ADDRESS (Optional): Steven.Cherensky@tensegritylawgroup.com<br>ATTORNEY FOR (Name): Polaris Innovations Limited | FOR COURT USE ONLY                             |

| UNITED STATES DISTRICT COURT, CENTRAL DISTRICT OF CALIFORNIA<br>STREET ADDRESS: 411 West Fourth Street                                                                                                                                                                                                                                                                                               |                                                |

| MAILING ADDRESS: 411 West Fourth Street, Room 1053                                                                                                                                                                                                                                                                                                                                                   |                                                |

| CITY AND ZIP CODE: Santa Ana, CA 92701-4516<br>BRANCH NAME:                                                                                                                                                                                                                                                                                                                                          |                                                |

| PLAINTIFF/PETITIONER: Polaris Innovations Limited                                                                                                                                                                                                                                                                                                                                                    | CASE NUMBER:                                   |

| DEFENDANT/RESPONDENT: Kingston Technology Company, Inc.                                                                                                                                                                                                                                                                                                                                              | 8:16-cv-300 CJC (RAOx)                         |

| PROOF OF SERVICE OF SUMMONS                                                                                                                                                                                                                                                                                                                                                                          | Ref. No. or File No.:<br>Polaris-Kingston      |

| (Separate proof of service is required for each par                                                                                                                                                                                                                                                                                                                                                  | ty served.)                                    |

| 1. At the time of service I was at least 18 years of age and not a party to this action.                                                                                                                                                                                                                                                                                                             |                                                |

| <ol> <li>I served copies of:</li> <li>a. ✓ summons</li> </ol>                                                                                                                                                                                                                                                                                                                                        |                                                |

| b. V complaint                                                                                                                                                                                                                                                                                                                                                                                       |                                                |

| c. Alternative Dispute Resolution (ADR) package                                                                                                                                                                                                                                                                                                                                                      |                                                |

| d. Civil Case Cover Sheet (served in complex cases only)                                                                                                                                                                                                                                                                                                                                             |                                                |

| e. cross-complaint                                                                                                                                                                                                                                                                                                                                                                                   |                                                |

| f. f. other (specify documents): see attached list of ADDITIONAL                                                                                                                                                                                                                                                                                                                                     | DOCUMENTS SERVED                               |

| <ol> <li>a. Party served (specify name of party as shown on documents served):<br/>Kingston Technology Company, Inc.</li> </ol>                                                                                                                                                                                                                                                                      |                                                |

| b. X Person (other than the party in item 3a) served on behalf of an entity or a<br>under item 5b on whom substituted service was made) (specify name an<br>ACCEPTED BY LYNANNE GARES (MANAGING AG                                                                                                                                                                                                   | d relationship to the party named in item 3a): |

| Address where the party was served: | CORP | ORATION | SERV. | ICE | COMPANY       |    |       |

|-------------------------------------|------|---------|-------|-----|---------------|----|-------|

|                                     | 2711 | CENTERV | VILLE | RD. | , WILMINGTON, | DE | 19808 |

5. I served the party (check proper box)

4.

| a XX | xx | by personal service. I personally delivered the docur   | ments listed in item | 2 to the party or person authorized to |  |

|------|----|---------------------------------------------------------|----------------------|----------------------------------------|--|

|      |    | receive service of process for the party (1) on (date): |                      | (2) at (time): 12:30pm                 |  |

| b.                                                                                 |  | by substituted service. | On (date): | at (time): | I left the documents listed in item 2 with or |

|------------------------------------------------------------------------------------|--|-------------------------|------------|------------|-----------------------------------------------|

| in the presence of (name and title or relationship to person indicated in item 3): |  |                         |            | em 3):     |                                               |

(1) **(business)** a person at least 18 years of age apparently in charge at the office or usual place of business of the person to be served. I informed him or her of the general nature of the papers.

| (2) | (home) a competent member of the household (at least 18 years of age) at the dwelling house or usual |

|-----|------------------------------------------------------------------------------------------------------|

|     | place of abode of the party. I informed him or her of the general nature of the papers.              |

(3) (physical address unknown) a person at least 18 years of age apparently in charge at the usual mailing address of the person to be served, other than a United States Postal Service post office box. I informed him or her of the general nature of the papers.

(4) I thereafter mailed (by first-class, postage prepaid) copies of the documents to the person to be served at the place where the copies were left (Code Civ. Proc., § 415.20). I mailed the documents on (date): from (city): or a declaration of mailing is attached.

|       | (                |                             |                     |                       | -       |

|-------|------------------|-----------------------------|---------------------|-----------------------|---------|

| (5) [ | I attach a decla | ration of diligence stating | actions taken first | to attempt personal s | ervice. |

Form Adopted for Mandatory Use Judicial Council of California POS-010 [Rev. January 1, 2007]

PROOF OF SERVICE OF SUMMONS

Page 1 of 2 Code of Civil Procedure, § 417.10

### Case 8:16-cv-00300-CJC-RAO Document 11 Filed 02/26/16 Page 2 of 3 Page ID #:138

| PLAINTIFF/PETITIONER: Polaris Innovations Limited                                                                                                                                                                                                                                                                                            | CASE NUMBER:                                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| LEFENDANT/RESPONDENT: Kingston Technology Company, Inc.                                                                                                                                                                                                                                                                                      | 8:16-cv-300 CJC (RAOx)                                                                               |  |  |  |

|                                                                                                                                                                                                                                                                                                                                              |                                                                                                      |  |  |  |

| 5. c. by mail and acknowledgment of receipt of service. I mailed the documen address shown in item 4, by first-class mail, postage prepaid,                                                                                                                                                                                                  | ts listed in item 2 to the party, to the                                                             |  |  |  |

| (1) on ( <i>date</i> ): (2) from ( <i>city</i> ):                                                                                                                                                                                                                                                                                            |                                                                                                      |  |  |  |

| <ul> <li>(3) with two copies of the Notice and Acknowledgment of Receipt and to me. (Attach completed Notice and Acknowledgement of Receipt (4)</li> <li>(4) to an address outside California with return receipt requested. (C</li> </ul>                                                                                                   | ot.) (Code Civ. Proc., § 415.30.)                                                                    |  |  |  |

| d. <b>by other means</b> (specify means of service and authorizing code section):                                                                                                                                                                                                                                                            |                                                                                                      |  |  |  |

| <ul> <li>Additional page describing service is attached.</li> <li>6. The "Notice to the Person Served" (on the summons) was completed as follows: <ul> <li>aas an individual defendant.</li> <li>bas the person sued under the fictitious name of (specify):</li> </ul> </li> </ul>                                                          |                                                                                                      |  |  |  |

| c as occupant.<br>d. XXX On behalf of ( <i>specify</i> ): KINGSTON TECHNOLOGY COMPANY                                                                                                                                                                                                                                                        | L TNC                                                                                                |  |  |  |

| under the following Code of Civil Procedure section:                                                                                                                                                                                                                                                                                         |                                                                                                      |  |  |  |

| X416.10 (corporation)415.95 (busined)416.20 (defunct corporation)416.60 (minor)416.30 (joint stock company/association)416.70 (ward of)416.40 (association or partnership)416.90 (author)416.50 (public entity)415.46 (occup)other:115.46 (occup)                                                                                            | r conservatee)<br>ized person)                                                                       |  |  |  |

| 7. Person who served papers<br>a. Name: KEVIN S . DUNN                                                                                                                                                                                                                                                                                       |                                                                                                      |  |  |  |

| b. Address: PO BOX 1360, WILMINGTON, DE 19899<br>c. Telephone number: 302-475-2600                                                                                                                                                                                                                                                           |                                                                                                      |  |  |  |

| d. The fee for service was: \$89.00                                                                                                                                                                                                                                                                                                          |                                                                                                      |  |  |  |

| <ul> <li>e. I am:</li> <li>(1) xx not a registered California process server.</li> <li>(2) exempt from registration under Business and Professions Code section 2</li> <li>(3) a registered California process server:</li> <li>(i) owner employee independent contractor.</li> <li>(ii) Registration No.:</li> <li>(iii) County:</li> </ul> | 22350(b).                                                                                            |  |  |  |

| 8. XX I declare under penalty of perjury under the laws of the State of California that the                                                                                                                                                                                                                                                  | e foregoing is true and correct.                                                                     |  |  |  |

| or                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |  |  |  |

| 9. I am a California sheriff or marshal and I certify that the foregoing is true and o                                                                                                                                                                                                                                                       | 9. <b>I am a California sheriff or marshal and I</b> certify that the foregoing is true and correct. |  |  |  |

| Date: 2/25/16                                                                                                                                                                                                                                                                                                                                |                                                                                                      |  |  |  |

| KEVIN S. DUNN                                                                                                                                                                                                                                                                                                                                |                                                                                                      |  |  |  |

| (NAME OF PERSON WHO SERVED PAPERS/SHERIFF OR MARSHAL)                                                                                                                                                                                                                                                                                        | (SIGNATURE )                                                                                         |  |  |  |

#### UNITED STATES DISTRICT COURT CENTRAL DISTRICT OF CALIFORNIA SOUTHERN DIVISION

| POLARIS INNOVATIONS LIMITED, )<br>an Irish limited company, | Case No. 8:16-cv-300 CJC (RAOx) |

|-------------------------------------------------------------|---------------------------------|

| Plaintiff, )<br>vs.                                         | ADDITIOANL DOCUMENTS<br>SERVED  |

| KINGSTON TECHNOLOGYCOMPANY, INC., a Delawarecorporation,    |                                 |

| Defendant.                                                  |                                 |

- REPORT ON THE FILING OR DETERMINATION OF AN ACTION REGARDING A PATENT OR TRADEMARK

- PLAINTIFF'S APPLICATION FOR LEAVE TO FILE UNDER SEAL CERTIFICATION AND NOTICE OF INTERESTED PARTIES

- [PROPOSED] ORDER GRANTING PLAINTIFF'S APPLICATION FOR LEAVE TO FILE UNDER SEAL CERTIFICATION AND NOTICE OF INTERESTED PARTIES

- REDACTED VERSION OF CERTIFICATION AND NOTICE OF INTERESTED PARTIES (Local Rule 7.1-1)

- NOTICE OF ASSIGNMENT TO UNITED STATES JUDGES

- NOTICE TO PARTIES OF COURT-DIRECTED ADR PROGRAM

- ORDER GRANTING PLAINTIFF'S APPLICATION FOR LEAVE TO FILE UNDER SEAL CERTIFICATION AND NOTICE OF INTERESTED PARTIES

|          | Case 8:16-cv-00300 Document 1 File                                                                   | ed 02/19/16 Page 1 of 38 Page ID #:1 |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| 1        | MATTHEW D. POWERS (Bar No. 104795)                                                                   |                                      |  |  |  |  |

| 2        | matthew.powers@tensegritylawgroup.com<br>STEVEN CHERENSKY (Bar No. 168275)                           |                                      |  |  |  |  |

| 3        | steven.cherensky@tensegritylawgroup.com                                                              |                                      |  |  |  |  |

| 4        | AZRA M. HADZIMEHMEDOVIC (Bar No. 239088)<br>azra@tensegritylawgroup.com<br>TENSEGRITY LAW GROUP, LLP |                                      |  |  |  |  |

| 5        |                                                                                                      |                                      |  |  |  |  |

| 6        | 555 Twin Dolphin Drive, Suite 650<br>Redwood Shores, CA 94065                                        |                                      |  |  |  |  |

| 7        | Telephone: (650) 802-6000                                                                            |                                      |  |  |  |  |

| 8        | Fax: (650) 802-6001                                                                                  |                                      |  |  |  |  |

| 9        | Attorneys for Plaintiff,<br>Polaris Innovations Limited                                              |                                      |  |  |  |  |

| 10       | Polaris Innovations Limitea                                                                          |                                      |  |  |  |  |

| 11       | INITED STATES                                                                                        | DISTRICT COURT                       |  |  |  |  |

| 12       |                                                                                                      | DISTRICT COURT                       |  |  |  |  |

| 13       |                                                                                                      | CT OF CALIFORNIA                     |  |  |  |  |

| 14       | SOUTHERN DIVISION                                                                                    |                                      |  |  |  |  |

| 15       |                                                                                                      |                                      |  |  |  |  |

| 16<br>17 | POLARIS INNOVATIONS LIMITED, )<br>an Irish limited company,                                          | Case No. 8:16-cv-300                 |  |  |  |  |

| 18       | Plaintiff,                                                                                           | )<br>COMPLAINT FOR PATENT            |  |  |  |  |

| 19       | ) COMPLAINT FOR FATENT<br>) INFRINGEMENT AND DEMAND                                                  |                                      |  |  |  |  |

| 20       | VS.                                                                                                  | FOR JURY TRIAL                       |  |  |  |  |

| 21       | KINGSTON TECHNOLOGY                                                                                  |                                      |  |  |  |  |

| 22       | COMPANY, INC., a Delaware ()<br>corporation, ()                                                      |                                      |  |  |  |  |

| 23       |                                                                                                      |                                      |  |  |  |  |

| 24       | Defendant.                                                                                           |                                      |  |  |  |  |

| 25       |                                                                                                      |                                      |  |  |  |  |

| 26       |                                                                                                      |                                      |  |  |  |  |

| 27       |                                                                                                      |                                      |  |  |  |  |

| 28       |                                                                                                      |                                      |  |  |  |  |

|          | COMPLAINT FOR PATENT INFRINGEMENT                                                                    |                                      |  |  |  |  |

Plaintiff Polaris Innovations Limited ("Polaris" or "Plaintiff") hereby alleges for its Complaint against Defendant Kingston Technology Company, Inc. ("Kingston" or "Defendant") as follows:

# **JURISDICTION**

1. This is an action for patent infringement arising under the patent laws of the United States, Title 35 of the United States Code. This Court has subject matter jurisdiction of this action pursuant to 28 U.S.C. §§ 1331 and 1338(a).

2. This Court has personal jurisdiction over Kingston. Kingston is headquartered in the Central District of California, has systematic and continuous contacts with the forum, and conducts substantial business within this district. Upon information and belief, Kingston has committed and continues to commit acts of patent infringement, including making, selling, offering to sell, directly or through intermediaries, subsidiaries and/or agents, infringing products within this district, including to customers in this district.

## VENUE

3. Venue is proper in this Court pursuant to 28 U.S.C. §§ 1391 and 1400(b) because Kingston is subject to personal jurisdiction in this district, and because a substantial part of the events giving rise to Polaris's claims occurred in this district, and Kingston, which is headquartered in Fountain Valley, California, has a regular and established place of business within this district.

## THE PARTIES

4. Polaris Innovations Limited is a corporation organized and existing under the laws of Ireland, with its principal place of business at Polaris Innovations Limited, 29 Earlsfort Terrace, Dublin 2, Republic of Ireland.

5. On information and belief, Kingston Technology Company, Inc. is a corporation organized and existing under the laws of Delaware with its principal place of business at 17600 Newhope Street, Fountain Valley, California, 92708.

**COMPLAINT FOR PATENT INFRINGEMENT**

1

2

3

4

5

27 28

2 3

4

5

6

7

8

11

13

1

## NATURE OF THE ACTION

6. This is a patent infringement action by Polaris to end Kingston's unauthorized, willful, and infringing manufacture, use, sale, offering for sale, and/or importation of products and methods incorporating Polaris's patented inventions.

7. Polaris holds all substantial rights and interest in the Asserted Patents described below, including the exclusive right to sue Kingston for infringement and recover damages.

9 8. Kingston makes, uses, sells, offers for sale, and imports products and 10 methods that infringe the Asserted Patents. Polaris seeks monetary damages and prejudgment interest for Kingston's past and ongoing infringement of the Asserted 12 Patents.

### THE ASSERTED PATENTS

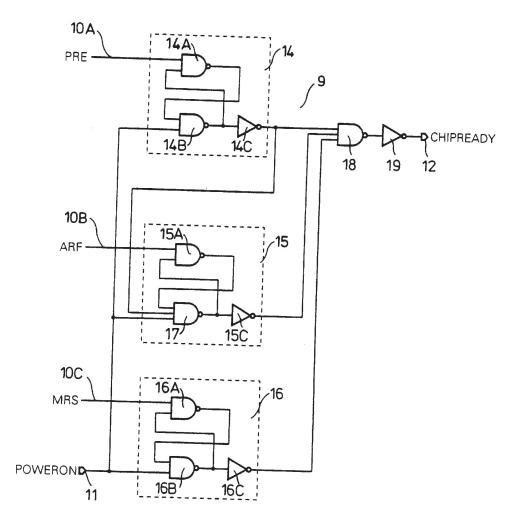

14 9. On December 5, 2000, the United States Patent and Trademark Office 15 duly and legally issued U.S. Patent No. 6,157,589 ("the 589 Patent"), entitled 16 "Dynamic semiconductor memory device and method for initializing a dynamic semiconductor memory device." A copy of the 589 Patent is attached hereto as Ex. 1.

10. Polaris owns all substantial right, title, and interest in the 589 Patent, and holds the right to sue and recover damages for infringement thereof, including past infringement.

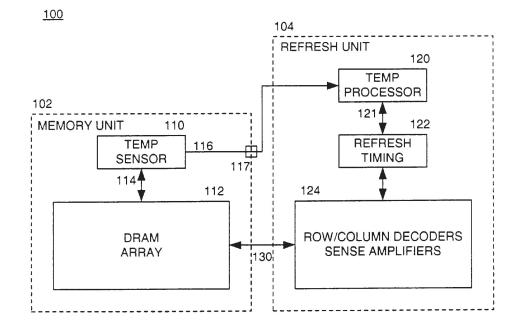

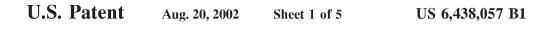

On August 20, 2002, the United States Patent and Trademark Office 11. 23 duly and legally issued U.S. Patent No. 6,438,057 B1 ("the 057 Patent"), entitled 24 "DRAM refresh timing adjustment device, system and method." A copy of the 057 25 Patent is attached hereto as Ex. 2.

26 12. Polaris owns all substantial right, title, and interest in the 057 Patent, 27 and holds the right to sue and recover damages for infringement thereof, including 28 past infringement.

#### **COMPLAINT FOR PATENT INFRINGEMENT**

17

6

### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 4 of 38 Page ID #:4

13. On February 1, 2005, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 6,850,414 B2 ("the 414 Patent"), entitled "Electronic printed circuit board having a plurality of identically designed, housing-encapsulated semiconductor memories." A copy of the 414 Patent is attached hereto as Ex. 3.

14. Polaris owns all substantial right, title, and interest in the 414 Patent, and holds the right to sue and recover damages for infringement thereof, including past infringement.

15. On April 17, 2007, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 7,206,978 B2 ("the 978 Patent"), entitled "Error detection in a circuit module." A copy of the 978 Patent is attached hereto as Ex. 4.

13 16. Polaris owns all substantial right, title, and interest in the 978 Patent,

14 and holds the right to sue and recover damages for infringement thereof, including

15 past infringement.

16 17. On January 1, 2008, the United States Patent and Trademark Office

17 duly and legally issued U.S. Patent No. 7,315,454 B2 ("the 454 Patent"), entitled

18 "Semiconductor memory module." A copy of the 454 Patent is attached hereto as

19 Ex. 5.

18. Polaris owns all substantial right, title, and interest in the 454 Patent, and holds the right to sue and recover damages for infringement thereof, including past infringement.

19. On February 19, 2008, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 7,334,150 B2 ("the 150 Patent"), entitled "Memory module with a clock signal regeneration circuit and a register circuit for temporarily storing the incoming command and address signals." A copy of the 150 Patent is attached hereto as Ex. 6.

28

1

2

3

4

5

6

7

8

9

10

11

12

20

21

22

23

24

25

26

27

20. Polaris owns all substantial right, title, and interest in the 150 Patent,

#### **COMPLAINT FOR PATENT INFRINGEMENT**

and holds the right to sue and recover damages for infringement thereof, including past infringement.

## **COUNT I:**

## **INFRINGEMENT OF U.S. PATENT NO. 6,157,589**

21. Polaris incorporates and realleges paragraphs 1-20 above as if fully set forth herein.

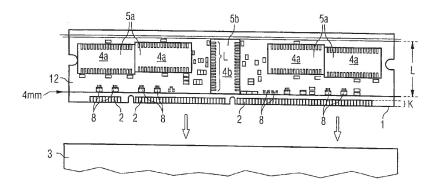

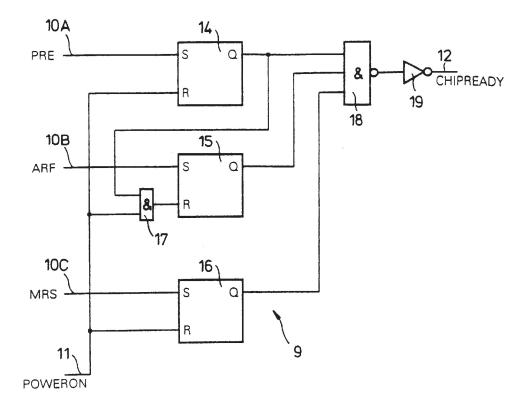

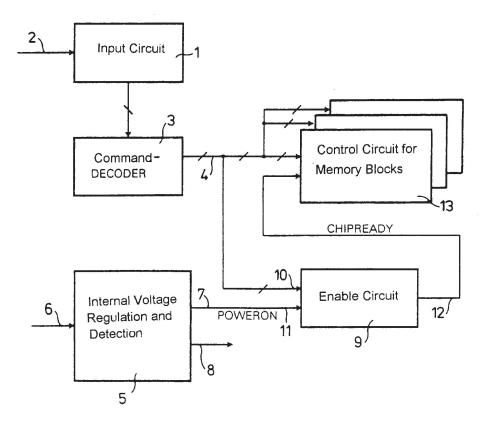

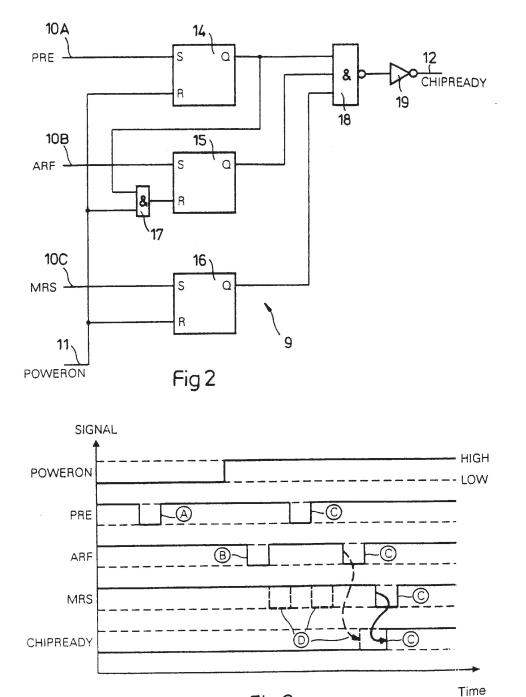

22. On information and belief, Kingston has willfully infringed and continues to willfully infringe one or more claims of the 589 Patent, including, but not limited to, Claims 11 and 12, pursuant to 35 U.S.C. § 271(a), literally or under the doctrine of equivalents, by making, using, selling, offering to sell in the United States without authority, and/or importing into the United States without authority, solid-state drives (SSDs) performing the claimed methods for initializing a dynamic semiconductor memory device. These products, the "589 Patent Infringing Products," including by way of a non-limiting example only, Kingston's SSDs with model number SM2280S3/120G, perform the methods for initializing a dynamic semiconductor memory device as required by the claims of the 589 Patent. 23. By way of example, the front and back views of a representative 589 Patent Infringing Product (SM2280S3/120G) that performs the claimed methods are shown in the image below.

COMPLAINT FOR PATENT INFRINGEMENT

### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 6 of 38 Page ID #:6

24. The front image of this representative 589 Infringing Product (SM2280S3/120G) is annotated below for illustration.

# DRAM chip (Nanya NT5CC128M16FP-D1)

Controller chip (Phison PS3108)

Specifically, the 589 Patent Infringing Products, such as SM2280S3/120G, include memory chip a dynamic random access (DRAM) (labeled Nanya NT5CC128M16FP in the photo above) and a controller chip (labeled Phison PS3108 in the photo above). See generally 2Gb DDR3 SDRAM H-Die datasheet, Technology Datasheet"), available Nanya ("Nanya at http://www.nanya.com/NanyaAdmin/GetFiles.ashx?ID=1199 (last visited February 3, 2016). On information and belief, when Kingston, its customers, and other third parties turn on the 589 Patent Infringing Products, the controller chip supplies, via an initialization circuit, a supply voltage stable signal (for example, the Active Low Asynchronous Reset signal, <u>*RESET*</u>, see Nanya Datasheet at 8) once a supply voltage has been stabilized (for example, at the time labeled Tb, see Nanya Datasheet, Fig. 3 at 13, and as described in Step 1 of the initialization sequence, 25 Nanya Datasheet at 11) after the switching-on operation of the dynamic 26 semiconductor memory device (for example, in the "Reset Procedure" state which 27 follows the "Power ON" state, Nanya Datasheet, Fig. 2 at 10). The controller chip 28 also supplies, via an enable circuit of the initialization circuit, an enable signal (for

example, the Clock Enable signal, CKE, Nanya Datasheet, Table 3 at 7, which the 2 DRAM waits for as described in Step 2 of the initialization sequence, Nanya Datasheet at 11), the initialization circuit receiving the supply voltage stable signal 3 4 (for example, as described in Step 2 of the Reset and Initialization Procedure, 5 Nanya Datasheet at 11) and further command signals (for example, the "Command") signals, Nanya Datasheet, Fig. 3 at 13) externally applied to the dynamic 6 7 semiconductor memory device, after an identification of a predetermined proper 8 initialization sequence of the further command signals (for example, the Mode 9 Register Set ("MRS") and/or ZQ Calibration ("ZQCL") commands issued in Steps 10 6-10 of the initialization sequence, Nanya Datasheet at 12-14) the enable signal 11 being generated (for example, as shown on the CKE line, Nanya Datasheet, Fig. 3 12 at 13, and as described in Step 3 of the initialization sequence, Nanya Datasheet at 13 11) and effecting an unlatching of a control circuit (for example, the control 14 circuits contained in the DRAM chip which prepare the SDRAM for receiving 15 valid commands during normal operation as described in Steps 10 and 12 of the 16 initialization sequence, Nanya Datasheet at 12) provided for a proper operation of 17 the dynamic semiconductor memory device. See id.

25. On information and belief, the controller provides at least one of a preparation command signal for word line activation, a refresh command signal, and a loading configuration register command signal as the further command signals (for example, the MRS command, which acts both as a preparation command signal and as a loading configuration register command signal, see Nanya Datasheet at 12-14).

18

19

20

21

22

1

On information and belief, Kingston has induced and continues to 26. induce infringement of one or more claims of the 589 Patent, including, but not limited to, Claims 11 and 12, pursuant to 35 U.S.C. § 271(b), by encouraging its customers and other third parties to perform the claimed method for initializing a dynamic semiconductor memory device. This performance of the claimed method

**COMPLAINT FOR PATENT INFRINGEMENT**

6

#### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 8 of 38 Page ID #:8

for initializing a dynamic semiconductor memory device, constitutes infringement, 1 2 literally or under the doctrine of equivalents, of one or more claims of the 589 3 Patent by such customers or third parties. Kingston's acts of inducement include: 4 providing its customers with the 589 Patent Infringing Products and intending its 5 customers to use the 589 Infringing Products with hardware, software, and other infrastructure that enable and/or make use of these products; advertising these 6 7 products through its and third-party websites (for own example. 8 http://www.kingston.com/ssd); encouraging customers and other third parties to 9 communicate directly with Kingston representatives about these products (for 10 example, through the "Ask an Expert" feature on its website); and providing 11 instructions on how to use these products. For example, Kingston's documentation 12 supplied with the representative 589 Patent Infringing Product instructs users to 13 install the product in a computer system and restart the computer system, and thus 14 to perform the claimed methods. See Kingston Technology SSDNow Series Solid 15 State Drive Getting Started. No. 4402105-001.B00, available at 16 http://media.kingston.com/support/downloads/SSD mSATA Installguide.pdf (last 17 visited on February 3, 2016).

18 Kingston proceeded in this manner despite its actual knowledge of the 27. 19 589 Patent and its knowledge that the specific actions it actively induced on the 20 part of its customers and other third parties constitute infringement of the 589 21 Patent at least as of February 1, 2016 when Polaris placed Kingston on notice of 22 infringement of the 589 Patent and identified Kingston's infringing products. At 23 the very least, because Kingston has been and remains on notice of the 589 Patent 24 and the accused infringement, it has been and remains willfully blind regarding the 25 infringement it has induced and continues to induce.

26 28. On information and belief, Kingston has contributed to and continues

27 to contribute to infringement of one or more claims of the 589 Patent, including,

28 but not limited to, Claims 11 and 12, pursuant to 35 U.S.C. § 271(c) by, without

**COMPLAINT FOR PATENT INFRINGEMENT**

7

### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 9 of 38 Page ID #:9

authority, selling and/or offering to sell within the United States, importing, and/or 1 2 supplying components of systems that perform the claimed methods for initializing 3 a dynamic semiconductor memory device, including without limitation the 589 4 Patent Infringing Products. These components supplied by Kingston are key 5 components to building computer systems such as laptops or desktop computers. 6 When, for example, these products are installed on a computing device and used 7 for storage, the claimed dynamic semiconductor memory device is used, and/or the 8 claimed methods performed, thereby infringing, literally or under the doctrine of 9 equivalents, one or more claims of the 589 Patent. Kingston supplied and continues 10 to supply these components, including without limitation the 589 Patent Infringing 11 Products, with the knowledge of the 589 Patent and with the knowledge that these 12 components constitute material parts of the claimed inventions of the 589 Patent. 13 Kingston knows that these components are especially made and/or especially 14 adapted for use as claimed in the 589 Patent. Further, Kingston knows that there is 15 no substantial non-infringing use of these components.

16 29. Polaris has suffered damages as a result of Kingston's infringement of

17 the 589 Patent.

18 30. Kingston's infringement of the 589 Patent has been and continues to 19 be willful, deliberate, and in disregard of Polaris's patent rights. At least as of 20 February 1, 2016, when Polaris placed Kingston on notice of infringement of the 21 589 Patent and identified Kingston's infringing products, Kingston has had actual 22 knowledge of infringement of the 589 Patent and has proceeded to infringe the 589 23 Patent with full and complete knowledge of that patent and its applicability to 24 Kingston's products without taking a license under the 589 Patent. Despite 25 knowledge of the 589 Patent, Kingston has acted and is acting despite an 26 objectively high likelihood that its actions constitute patent infringement. This 27 objective risk was and is known to Kingston, and is also so obvious that it should 28 have been known to Kingston. Such willful and deliberate conduct entitles Polaris

COMPLAINT FOR PATENT INFRINGEMENT

to increased damages under 35 U.S.C. § 284 and to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

1

2

3

4

5

6

18

19

20

21

22

23

24

25

26

27

28

## **COUNT II:**

## **INFRINGEMENT OF U.S. PATENT NO. 6,438,057**

31. Polaris incorporates and realleges paragraphs 1-20 above as if fully set forth herein.

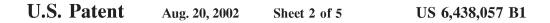

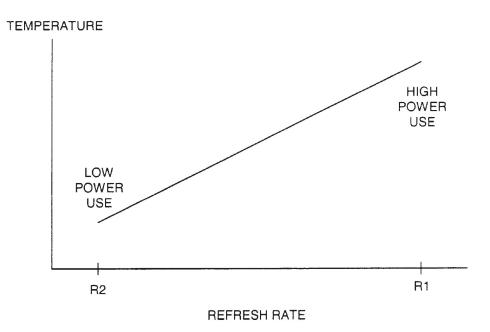

32. On information and belief, Kingston has willfully infringed and 7 8 continues to willfully infringe one or more claims of the 057 Patent, including, but 9 not limited to, Claims 1 and 2, pursuant to 35 U.S.C. § 271(a), literally or under the 10 doctrine of equivalents, by making, using, selling, and/or offering to sell in the 11 United States without authority and/or importing into the United States without 12 authority, Double Data Rate 3 (DDR3) Dual In-line Memory Module (DIMM) 13 products, devices, systems, and/or components of systems that support the Extended Temperature Range (85°C to 95°C). These products, the "057 Patent 14 15 Infringing Products," including by way of a non-limiting example only, Kingston's 16 memory module product with model number KVR16R11D4/16, include the 17 temperature-based refresh rate adjustment required by the claims of the 057 Patent.

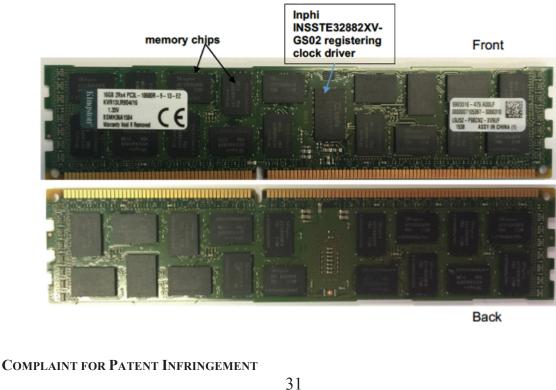

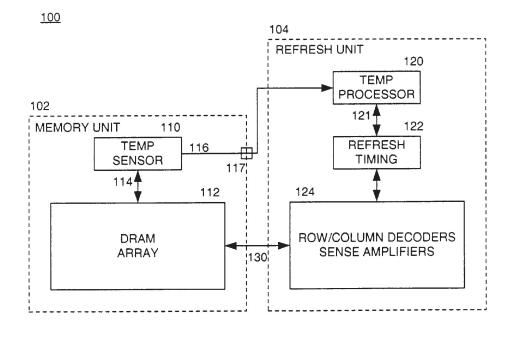

33. By way of example, the front and back views of a representative 057 Patent Infringing Product (KVR16R11D4/16) that uses the claimed temperaturebased refresh rate adjustment are shown in the image below.

COMPLAINT FOR PATENT INFRINGEMENT

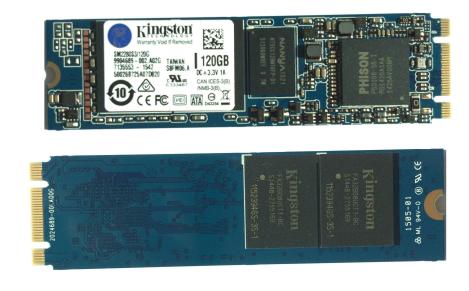

Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 11 of 38 Page ID #:11 Atmel AT30TSE002B SPD/TS (T2B H2W 5FH) 1 Front 2 3 4 5 6 7 8 9 10 Back 34. The schematic diagram of this representative 057 Infringing Product 11 (KVR16R11D4/16) is reproduced from publicly available Kingston documentation 12 and annotated below for illustration. 13 14 MODULE DIMENSIONS: Temperature Sensor 15 Front Detail E 128.95 16 ÷ 17 18 mmmmmii 2× R0.75 Mz Detail D 19 DRAM Array Contact Pin Back 20 21 22 23 24 Kingston Value RAM Memory Module Specifications, Doc. No. 25 VALUERAM1123-001.A00 (Apr. 25, 2012) ("KVR16R11D4/16 Datasheet") at 2, 26 available at http://www.kingston.com/dataSheets/KVR16R11D4 16.pdf (last 27 visited February 3, 2016) (annotations added). Specifically, the 057 Patent 28 Infringing Products, such as KVR16R11D4/16, are apparatuses comprising a **COMPLAINT FOR PATENT INFRINGEMENT** 10

#### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 12 of 38 Page ID #:12

semiconductor package of the memory module including at least one contact pin 1 2 (one example shown in the blue box in the diagram above) and at least one 3 dynamic random access memory (DRAM) array comprising one or more DRAM 4 chips (shown in the green box in the diagram above), such as "DDR3-1600 CL11 5 SDRAM" in KVR16R11D4/16, see KVR16R11D4/16 Datasheet at 1. On information and belief, all 057 Patent Infringing Products that support the 6 7 Extended Temperature Range comprise at least one temperature sensor (an 8 example shown in the orange box above) in thermal communication with the 9 DRAM array, operable to produce a signal indicative of a temperature of the 10 DRAM array or the equivalent, and coupled to at least one connection pin such that 11 the signal may be provided to external circuitry. For example, the representative 12 057 Patent Infringing Product (KVR16R11D4/16) comprises an Atmel 13 AT30TSE002B integrated temperature sensor with SEEPROM (annotated in the product image above). See AT30TSE002B Integrated Temperature Sensor with 14 15 SEEPROM Datasheet") datasheet ("Atmel at 1. available at 16 http://www.atmel.com/images/doc8711.pdf (last visited February 3, 2016). This 17 AT30TSE002B temperature sensor is in thermal communication with the DRAM 18 array, operable to produce a signal indicative of a temperature of the DRAM array 19 (for example, the Temperature Alert signal output by the EVENT pin) or the 20 equivalent, and coupled to at least one connection pin (for example, the EVENT 21 pin), such that the signal may be provided to external circuitry (for example, the 22 controller). See Atmel Datasheet at 1-4, 11, 16-18. Further, the DRAM array on the 23 057 Infringing Products is refreshed at a rate that decreases as the temperature of 24 the DRAM array decreases and that increases as the temperature of the DRAM 25 array increases. See, e.g., KVR16R11D4/16 Datasheet at 1 ("Average Refresh 26 Period 7.8µs at lower than TCASE 85°C, 3.9µs at 85°C < TCASE  $\leq$  95°C").

35. On information and belief, at least one temperature sensor of one or

more of the 057 Infringing Products includes at least one diode having a forward

**COMPLAINT FOR PATENT INFRINGEMENT**

11

voltage drop that varies as a function of the temperature of the DRAM array, and the signal corresponds to the forward voltage drop of the at least one diode. *See*, *e.g.*, Atmel Datasheet at 3 ("Band Gap Temperature Sensor") and 11 ("a band gap type temperature sensor").

1

2

3

4

19

20

21

22

23

24

25

26

27

28

5 36. On information and belief, Kingston has induced and continues to induce infringement of one or more claims of the 057 Patent, including, but not 6 limited to, Claims 1, 2, 6, 7, 8, 9, 10, 11, 13, 14, 15, 16, and 17, pursuant to 35 7 8 U.S.C. § 271(b) by inducing its customers and other third parties to make, use, sell, 9 offer to sell, import into the United States without authorization infringing 10 products that comprise an 057 Infringing Product as described above and a refresh 11 unit and/or chip performing the temperature-based refresh rate adjustment (the 12 "057 Infringing Systems"), and by inducing its customers and other third parties to 13 perform the claimed method of the temperature-based refresh rate adjustment. This 14 making, using, selling, offering to sell, importing into the United States without 15 authorization one or more of the 057 Infringing Systems, and performance of the 16 claimed method constitute infringement, literally or under the doctrine of 17 equivalents, of one or more claims of the 057 Patent by such customers or third 18 parties as further explained below.

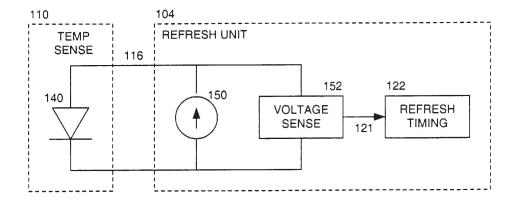

37. Specifically, on information and belief, the 057 Infringing Systems comprise one of the 057 Infringing Products, as described in the paragraph 34 *supra*, and a refresh unit (for example, a unit performing the temperature-based refresh rate adjustment in the controller, not shown in the images above) operable to refresh the DRAM array at a rate that varies in response to the signal (such as the Temperature Alert signal output by the EVENT pin). *See*, *e.g.*, KVR16R11D4/16 Datasheet at 1 ("Average Refresh Period 7.8µs at lower than TCASE 85°C, 3.9µs at 85°C < TCASE ≤ 95°C").

38. On information and belief, such refresh unit of the 057 Infringing Systems further includes a refresh timing unit operable to establish the rate at

**COMPLAINT FOR PATENT INFRINGEMENT**

which the DRAM array is refreshed in response to the signal (such as the Temperature Alert signal output by the EVENT pin). *Id.*

1

2

3

4

5

6

7

8

9

10

11

12

39. On information and belief, such refresh timing unit of one or more of the 057 Infringing Systems further includes a refresh timing unit operable to decrease the rate at which the DRAM array is refreshed as the signal (such as the Temperature Alert signal output by the EVENT pin) indicates that the temperature of the DRAM array decreases. *Id*.

40. On information and belief, such refresh timing unit of one or more of the 057 Infringing Systems further includes a refresh timing unit operable to increase the rate at which the DRAM array is refreshed as the signal (such as the Temperature Alert signal output by the EVENT pin) indicates that the temperature of the DRAM array increases. *Id*.

41. On information and belief, at least one temperature sensor of one or

more of the 057 Infringing Systems further includes at least one diode having a

forward voltage drop that varies as a function of the temperature of the DRAM

array, and the signal corresponds to the forward voltage drop of the at least one

diode. *See, e.g.*, Atmel Datasheet at 3 ("Band Gap Temperature Sensor") and 11

("a band gap type temperature sensor").

42. On information and belief, the refresh unit of one or more of the 057

Infringing Systems is operable to sense the forward voltage drop of the diode to

determine the temperature of the DRAM array. *Id*.

43. On information and belief, one or more of the 057 Infringing Systems

comprise at least one DRAM chip including a DRAM array and at least one

temperature sensor in thermal communication with the DRAM array, at least one

temperature sensor being operable to produce a signal indicative of a temperature

of the DRAM array; the DRAM chip further includes at least one connection pin

operable to provide the signal to external circuitry. *See* paragraph 34 *supra*. Such

057 Infringing Systems further comprise at least one refresh chip (such as a chip in

**COMPLAINT FOR PATENT INFRINGEMENT**

#### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 15 of 38 Page ID #:15

the controller performing the temperature-based refresh rate adjustment, not shown in the images above) operable to refresh the DRAM array at a rate that varies in response to the signal, wherein the refresh chip is operable to (i) decrease the rate at which the DRAM array is refreshed as the signal indicates that the temperature of the DRAM array decreases; and (ii) increase the rate at which the DRAM array is refreshed as the signal indicates that the temperature of the DRAM array increases. *Id*.

44. On information and belief, at least one temperature sensor of the 057 Infringing Systems as described in paragraph 43 further includes at least one diode having a forward voltage drop that varies as a function of the temperature of the DRAM array, and the signal corresponds to the forward voltage drop of the at least one diode. *See*, *e.g.*, Atmel Datasheet at 3 ("Band Gap Temperature Sensor") and 11 ("a band gap type temperature sensor").

45. On information and belief, the refresh chip in the 057 Infringing

Systems is operable to sense the forward voltage drop of the diode to determine the

temperature of the DRAM array. *Id.*

17 46. On information and belief, Kingston's customers and other third 18 parties perform the claimed method of temperature-based refresh rate adjustment 19 by using the 057 Infringing System. Such method comprises sensing a temperature 20 of a dynamic random access memory (DRAM) array; outputting a signal indicative 21 of the temperature of the DRAM array to external circuitry; and refreshing 22 contents of the DRAM array at a rate that (i) decreases as the temperature of the 23 DRAM array decreases; and (ii) increases as the temperature of the DRAM array 24 increases. See paragraphs 34 and 37 supra.

47. On information and belief, the steps of the claimed method performed

by Kingston's customers and other third parties for sensing the temperature of the

DRAM array also comprises sensing a forward voltage drop of a diode that is in

thermal communication with the DRAM array. *See* paragraphs 35, 41, 42, 44 *supra*.

**COMPLAINT FOR PATENT INFRINGEMENT**

1

2

3

4

5

6

7

8

9

10

11

12

13

### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 16 of 38 Page ID #:16

2 3

21

22

23

24

25

26

27

28

1

48 Kingston's acts of active inducement of direct infringement by its customers and other third parties include: providing its customers with the 057 Infringing Products and intending its customers to use these infringing memory 4 module products with hardware and software and other infrastructure, including a 5 controller that comprises a refresh unit and/or chip to make and use the 057 6 Infringing Systems; advertising its infringing memory module products through its 7 own and third-party websites (for example, 8 http://www.kingston.com/us/memory/search/MemoryType/Default.aspx?Memory 9 Type=DIMM,3,,); encouraging customers and other third parties to communicate 10 regarding these products directly with Kingston representatives (for example, 11 through the "Ask an Expert" feature on its website); and providing its customers 12 and other third parties with instructions on how to combine these infringing 13 memory module products with hardware and software and other infrastructure to 14 make and use the 057 Infringing System, and to perform the claimed method. For 15 example, Kingston's user manual, supplied with the representative 057 Patent 16 Infringing Product, instructs the users to install and use the product in a computer 17 system, thus instructing the users to make and use the 057 Infringing System and 18 enable the users to perform the claimed method. See Ex. 7, Kingston Technology 19 Installation Guide. Doc. 4402092-001.D00: Warranty and see also. KVR16R11D4/16 Datasheet. 20

49 Kingston proceeded in this manner despite its actual knowledge of the 057 Patent and its knowledge that the specific actions it actively induced on the part of its customers and other third parties constitute infringement of the 057 Patent at least as of February 1, 2016, when Polaris placed Kingston on notice of infringement of the 057 Patent and identified Kingston's infringing products. At the very least, because Kingston has been and remains on notice of the 057 Patent and the accused infringement, it has been and remains willfully blind regarding the infringement it has induced and continues to induce.

**COMPLAINT FOR PATENT INFRINGEMENT**

### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 17 of 38 Page ID #:17

50. On information and belief, Kingston has contributed to and continues to contribute to infringement of one or more claims of the 057 Patent, including, but not limited to, Claims 1, 2, 6, 7, 8, 9, 10, 11, 13, 14, 15, 16, and 17, pursuant to 35 U.S.C. § 271(c) by, without authority, selling, offering to sell within the United States, importing, and/or supplying components of the 057 Infringing Systems, and apparatuses for use in the claimed methods of the temperature-based refresh rate adjustment, including without limitation the 057 Patent Infringing Products. These components and apparatuses supplied by Kingston, including without limitation the 057 Patent Infringing Products, are key components for temperature-based refresh rate adjustment, thus constituting material parts of the claimed inventions of the 057 Patent. Kingston supplied and continues to supply these components and apparatuses, including without limitation the 057 Patent Infringing Products, with the knowledge of the 057 Patent and with the knowledge that these components constitute material parts of the claimed inventions of the 057 Patent. Kingston knows that these components and apparatuses are especially made and/or especially adapted for use as claimed in the 057 Patent to support the Extended Temperature Range (85°C to 95°C) of DDR3 memory module products. Further, Kingston knows that there is no substantial non-infringing use of these components for temperature-based refresh rate adjustment.

20 51. Polaris has suffered damages as a result of Kingston's infringement of

21 the 057 Patent.

52. Kingston's infringement of the 057 Patent has been and continues to

be willful, deliberate, and in disregard of Polaris's patent rights. At least as of

February 1, 2016, when Polaris placed Kingston on notice of infringement of the

057 Patent and identified Kingston's infringing products, Kingston has had actual

knowledge of infringement of the 057 Patent and has proceeded to infringe the 057

Patent with full and complete knowledge of that patent and its applicability to

Kingston's products without taking a license under the 057 Patent. Despite

**COMPLAINT FOR PATENT INFRINGEMENT**

1 knowledge of the 057 Patent, Kingston has acted and is acting despite an 2 objectively high likelihood that its actions constitute patent infringement. This 3 objective risk was and is known to Kingston, and is also so obvious that it should 4 have been known to Kingston. Such willful and deliberate conduct entitles Polaris 5 to increased damages under 35 U.S.C. § 284 and to attorneys' fees and costs 6 incurred in prosecuting this action under 35 U.S.C. § 285.

### **COUNT III:**

### **INFRINGEMENT OF U.S. PATENT NO. 6,850,414**

53. Polaris incorporates and realleges paragraphs 1-20 above as if fully set forth herein.

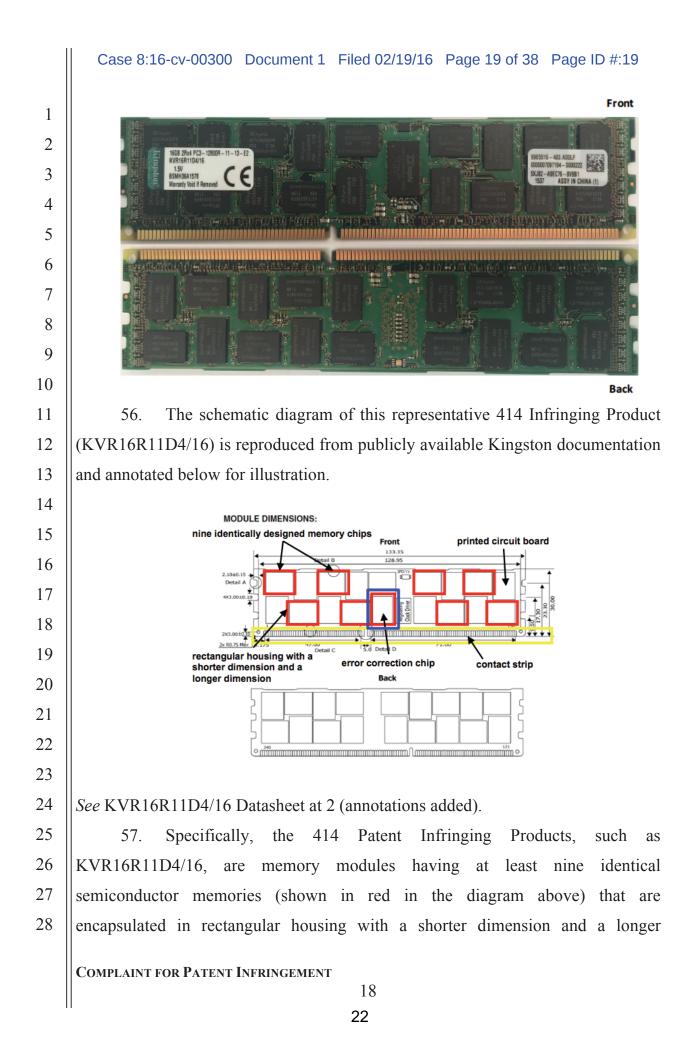

11 54. On information and belief, Kingston has willfully infringed and 12 continues to willfully infringe one or more claims of the 414 Patent, including, but 13 not limited to, Claims 1, 4, and 8, pursuant to 35 U.S.C. § 271(a), literally or under 14 the doctrine of equivalents, by making, using, selling, and/or offering to sell in the 15 United States without authority and/or importing into the United States without 16 authority, memory products, devices, systems, and/or components of systems that 17 include the claimed arrangements and configurations of the memory chips (the 18 "414 Patent Infringing Products"), including, for example, Kingston's memory 19 module products with model number KVR16R11D4/16.

55. By way of example, the front and back views of a representative 414 Patent Infringing Product (KVR16R11D4/16) that uses the claimed arrangement and configuration of the memory chips are shown in the image below.

28

20

21

7

8

9

10

COMPLAINT FOR PATENT INFRINGEMENT

#### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 20 of 38 Page ID #:20

dimension, each of which are individually connected to an electronic printed circuit board, the front and back sides of which are illustrated above. The electronic printed circuit board has a contact strip (one example shown in the yellow box in the diagram above) for insertion into another electronic unit. One of the semiconductor memories is connected as an error correction chip (shown in blue above in the diagram above) with its housing being oriented perpendicular to the contact strip, while the longer dimensions of eight other semiconductor memories are oriented parallel with the contact strip. *See* KVR16R11D4/16 Datasheet at 2.

58. In addition, one or more of the 414 Patent Infringing Products has a height of 1 to 1.2 inches perpendicular to said contact strip. *See id*.

59. Further, one or more of the 414 Patent Infringing Products has a width of 5.25 inches. *See id*.

14 60 On information and belief, Kingston has induced and continues to 15 induce infringement of one or more claims of the 414 Patent, including, but not 16 limited to, Claims 1, 4, and 8, pursuant to 35 U.S.C. § 271(b) by inducing its 17 customers and other third parties to use without authorization the infringing 18 products that use the claimed arrangement and configuration of the memory chips, 19 including but not limited to the 414 Patent Infringing Products. The use, without 20 authorization, of the infringing products that comprise the claimed arrangement 21 and configuration of the memory chips constitutes infringement, literally or under 22 the doctrine of equivalents, of one or more claims of the 414 Patent by such 23 customers or third parties. Kingston's acts of inducement include: providing its 24 customers with the 414 Patent Infringing Products and intending its customers to 25 use the 414 Infringing Products with hardware, software and other infrastructure 26 that enable and/or make use of these products; advertising these products through 27 and third-party websites (for its own example, 28 http://www.kingston.com/us/memory/search/MemoryType/Default.aspx?Memory

1

2

3

4

5

6

7

8

9

10

11

12

13

Type=DIMM,3,,); encouraging customers and other third parties to communicate directly with Kingston representatives about these products (for example, through the "Ask an Expert" feature on its website); and providing instructions on how to use these products. For example, Kingston's documentation accompanying the representative 414 Patent Infringing Product provides the users with instructions on how to install the product in a computer system and enables the users to use the product. See Ex. 7, Kingston Technology Warranty and Installation Guide, Doc. 4402092-001.D00; see also, KVR16R11D4/16 Datasheet.

Kingston proceeded in this manner despite its actual knowledge of the 61. 414 Patent and its knowledge that the specific actions it actively induced on the part of its customers and other third parties constitute infringement of the 414 Patent at least as of February 1, 2016 when Polaris placed Kingston on notice of infringement of the 414 Patent and identified Kingston's infringing products. At the very least, because Kingston has been and remains on notice of the 414 Patent and the accused infringement, it has been and remains willfully blind regarding the infringement it has induced and continues to induce.

17 62. Polaris has suffered damages as a result of Kingston's infringement of the 414 Patent.

19 63. Kingston's infringement has been and continues to be willful, 20 deliberate and in disregard of Polaris's patent rights. At least as of February 1, 21 2016, when Polaris placed Kingston on notice of infringement of the 414 Patent 22 and identified Kingston's infringing products, Kingston has had actual knowledge 23 of infringement of the 414 Patent and has proceeded to infringe the 414 Patent with 24 full and complete knowledge of that patent and its applicability to Kingston 25 products without taking a license under the 414 Patent. Despite knowledge of the 26 414 Patent, Kingston has acted and is acting despite an objectively high likelihood 27 that its actions constitute patent infringement. This objective risk was and is known 28 to Kingston, and is also so obvious that it should have been known to Kingston.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

18

Such willful and deliberate conduct entitles Polaris to increased damages under 35 U.S.C. § 284 and to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## **COUNT IV:**

### **INFRINGEMENT OF U.S. PATENT NO. 7,206,978**

64. Polaris incorporates and realleges paragraphs 1-20 above as if fully set forth herein.

65. On information and belief, Kingston has willfully infringed and continues to willfully infringe one or more claims of the 978 Patent, including, but not limited to, Claims 1, 2, 3, 5, 10, 11, and 12, pursuant to 35 U.S.C. § 271(a), literally or under the doctrine of equivalents, by making, using, selling, and/or offering to sell in the United States and/or importing into the United States without authority, claimed memory module products, devices, systems, and/or components of systems (the "978 Patent Infringing Products"), including, for example, Kingston's memory module products with model number KVR21R15D4/16.

66. By way of example, the front and back views of a representative 978 Patent Infringing Product (KVR21R15D4/16) are shown in the image below.

Front Fr

### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 23 of 38 Page ID #:23

2

The 978 Patent Infringing Products, such as KVR21R15D4/16, are 67. 1 circuit modules comprising a module board, the front and back sides of which are shown above. A plurality of circuit units, each consisting of a single integrated 3 4 circuit memory chip, is arranged on the module board (in the above example, 36 5 integrated memory chips are arranged on the module board). See, e.g., Kingston 6 KVR21R15D4/16 16GB 2Rx4 2G x 72-Bit PC4-2133 CL15 Registered w/Parity 7 288-Pin DIMM Specification, Doc. No. VALUERAM1447-001.C00 (Feb. 24, 8 2015) ("KVR21R15D4/16 Datasheet") 1. available at at 9 http://www.kingston.com/dataSheets/KVR21R15D4 16.pdf (last visited February 10 3, 2016). Further, on information and belief, the 978 Patent Infringing Products 11 comprise a main bus having a plurality of lines, branching into a plurality of sub-12 buses having a plurality of lines, each of the sub-buses being connected to one of 13 the plurality of the circuit units. Further, upon information and belief, each circuit 14 unit (in the example above, each dynamic random access memory, or "DRAM," 15 chip) in the 978 Patent Infringing Products comprises an indication signal 16 generating unit for providing an indication signal based on a combination of the 17 signals received on the plurality of lines of the sub-bus connected to the respective 18 circuit unit (in the example above, each memory chip combines the PAR 19 (command and address parity) input signal with the command and address input 20 signals to determine whether there is an error and generate the appropriate 21 indication signal). See, e.g., KVR21R15D4/16 Datasheet at 1 ("CA parity 22 (Command/Address Parity) mode is supported"). Each circuit unit also comprises 23 an indication signal output for outputting the indication signal (in the example 24 above, the ALERT n pin on each memory chip).

25 26

27

28

68. In addition, one or more 978 Patent Infringing Products comprise means for providing a check signal to each of the circuit units, the structure of which is the same as or equivalent to that disclosed in the patent specification (in the example above, the PAR (command and address parity) input on each dynamic

random access memory chip). See, e.g., KVR21R15D4/16 Datasheet at 1 ("CA parity (Command/Address Parity) mode is supported"). Upon information and belief, this indication signal generating unit generates said indication signal based on a combination of the signals on the plurality of lines of the respective sub-bus and the check signal so that the indication signal represents an error signal (in the example above, each memory chip combines the PAR input signal with the command and address input signals to determine whether there is an error and generate the appropriate indication signal).

In addition, on information and belief, one or more 978 Patent 9 69. 10 Infringing Products comprise an error reporting means, the structure of which is the same as or equivalent to that disclosed in the patent specification, being 12 connected to the indication signal outputs of the circuit units, and wherein each 13 error reporting means is configured to drive a module error out signal (in the 14 example above, the ALERT n outputs are connected to each other by traces on the 15 printed circuit board, and buffered by a register, they drive the ALERT n signal 16 for the entire module). See, e.g., KVR21R15D4/16 Datasheet at 1 ("CA parity 17 (Command/Address Parity) mode is supported").

18 70. In addition, on information and belief, one or more 978 Patent 19 Infringing Products comprise an indication reporting means, the structure of which 20 is the same as or equivalent to that disclosed in the patent specification, being 21 connected to the indication signal outputs of the circuit units and wherein each 22 indication reporting means is configured to drive a module indication out signal (in 23 the example above, the ALERT n outputs are connected to each other by traces on 24 the printed circuit board, and buffered by a register, they drive the ALERT n 25 signal for the entire module).

26 In addition, on information and belief, one or more 978 Patent 71. 27 Infringing Products comprise a DIMM, wherein the circuit units are memory units, 28 wherein the main bus is a memory main bus, and the sub-busses are memory sub-

**COMPLAINT FOR PATENT INFRINGEMENT**

1

2

3

4

5

6

7

8

11

### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 25 of 38 Page ID #:25

buses (in the example above, the module is a DIMM, the circuit units are DRAM memory chips and the traces providing address and command signals to the memory chips form a memory main bus and memory sub-buses). *See*, *e.g.*, KVR21R15D4/16 Datasheet at 1.

1

2

3

72. In addition, on information and belief, one or more 978 Patent Infringing Products comprise a main bus that is a command/address bus (in the example above, the traces providing address and command signals to the dynamic random access memory chips form a memory main bus and memory sub-buses).

73. In addition, on information and belief, one or more 978 Patent Infringing Products comprise means for providing a check signal that is a parity signal, the structure of which is the same as or equivalent to that disclosed in the patent specification (in the example above, the PAR input on each dynamic random access memory chip receives a parity signal from the module board).

74 On information and belief, Kingston has induced and continues to induce infringement of one or more claims of the 978 Patent, including, but not limited to, Claims 1, 2, 3, 5, 10, 11, and 12, pursuant to 35 U.S.C. § 271(b) by inducing its customers and other third parties to use without authorization the infringing products comprising the claimed arrangement of circuit units, including but not limited to the 978 Patent Infringing Products. This use, without authorization, of the infringing products comprising the claimed arrangement of circuit units constitutes infringement, literally or under the doctrine of equivalents, of one or more claims of the 978 Patent by such customers or third parties. Kingston's acts of inducement include: providing its customers with the 978 Patent Infringing Products and intending its customers to use the 978 Infringing Products with hardware, software, and other infrastructure that enable and/or make use of 26 these products; advertising these products through its own and third-party websites 27 (for example, http://www.kingston.com/us/memory/search/MemoryType/De 28 fault.aspx?MemoryType=DIMM,3,,); encouraging customers and other third

**COMPLAINT FOR PATENT INFRINGEMENT**

parties to communicate directly with Kingston representatives about these products (for example, through the "Ask an Expert" feature on its website); and providing instructions on how to use these products. For example, Kingston's documentation accompanying the representative 978 Patent Infringing Product provides the users with instructions on how to install the product in a computer system and enables the users to use the product. *See* Ex. 7, Kingston Technology Warranty and Installation Guide, Doc. 4402092-001.D00; *see also*, KVR21R15D4/16 Datasheet.

75. Kingston proceeded in this manner despite its actual knowledge of the 978 Patent and its knowledge that the specific actions it actively induced on the part of its customers and other third parties constitute infringement of the 978 Patent at least as of February 1, 2016, when Polaris placed Kingston on notice of infringement of the 978 Patent and identified Kingston's infringing products. At the very least, because Kingston has been and remains on notice of the 978 Patent and the accused infringement, it has been and remains willfully blind regarding the infringement it has induced and continues to induce.

76. Polaris has suffered damages as a result of Kingston's infringement of the 978 Patent.

18 77. Kingston's infringement of the 978 Patent has been and continues to 19 be willful, deliberate, and in disregard of Polaris's patent rights. At least as of 20 February 1, 2016, when Polaris placed Kingston on notice of infringement of the 21 978 Patent and identified Kingston's infringing products, Kingston has had actual 22 knowledge of infringement of the 978 Patent and has proceeded to infringe the 978 23 Patent with full and complete knowledge of that patent and its applicability to 24 Kingston's products without taking a license under the 978 Patent. Despite 25 knowledge of the 978 Patent, Kingston has acted and is acting despite an 26 objectively high likelihood that its actions constitute patent infringement. This 27 objective risk was and is known to Kingston, and is also so obvious that it should 28 have been known to Kingston. Such willful and deliberate conduct entitles Polaris

COMPLAINT FOR PATENT INFRINGEMENT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

to increased damages under 35 U.S.C. § 284 and to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## COUNT V:

## **INFRINGEMENT OF U.S. PATENT NO. 7,315,454**

78. Polaris incorporates and realleges paragraphs 1-20 above as if fully set forth herein.

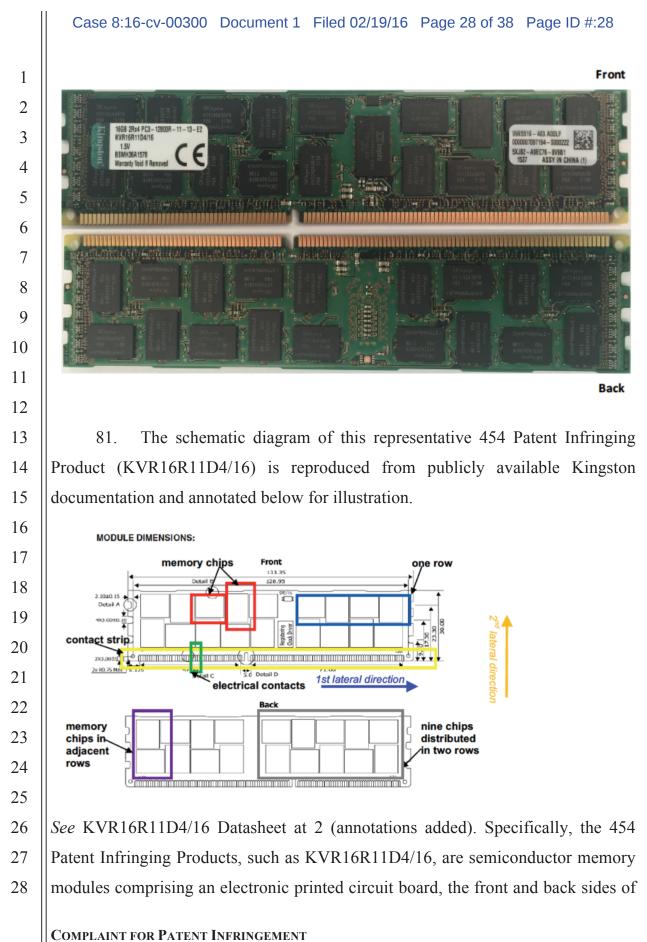

79. On information and belief, Kingston has willfully infringed and continues to willfully infringe one or more claims of the 454 Patent, including, but not limited to, Claims 1, 2, 3, 4, and 7, pursuant to 35 U.S.C. § 271(a), literally or under the doctrine of equivalents, by making, using, selling, and/or offering to sell in the United States and/or importing into the United States without authority, memory module products, devices, systems, and/or components of systems that include the claimed arrangements and configurations of the memory chips (the "454 Patent Infringing Products"), including, for example, Kingston's memory module products with model number KVR16R11D4/16.

80. By way of example, the front and back views of a representative 454 Patent Infringing Product (KVR16R11D4/16) that uses the claimed arrangement and configuration of the memory chips are shown in the image below.

23

24

25

26

27

28

1

2

#### Case 8:16-cv-00300 Document 1 Filed 02/19/16 Page 29 of 38 Page ID #:29