## United States Patent [19]

**Iyer**

| [11] | Patent Number:  | 4,638,347     |

|------|-----------------|---------------|

| [45] | Date of Patent: | Jan. 20, 1987 |

| [54]                          | GATE ELECTRODE SIDEWALL ISOLATION<br>SPACER FOR FIELD EFFECT<br>TRANSISTORS |                                                           |  |

|-------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|--|

| [75]                          | Inventor:                                                                   | Subramanian S. Iyer, Mt. Kisco, N.Y.                      |  |

| [73]                          | Assignee:                                                                   | International Business Machines Corporation, Armonk, N.Y. |  |

| [21]                          | Appl. No.:                                                                  | 763,897                                                   |  |

| [22]                          | Filed:                                                                      | Aug. 9, 1985                                              |  |

| Related U.S. Application Data |                                                                             |                                                           |  |

| [63]                          | Continuation of Ser. No. 447,543, Dec. 7, 1982, abandoned.                  |                                                           |  |

| [51]<br>[52]                  | Int. Cl. <sup>4</sup>                                                       |                                                           |  |

| [58]                          | Field of Sea                                                                | arch 357/54, 59, 23.3, 23.9, 357/23.1                     |  |

| [56]                          | References Cited                                                            |                                                           |  |

|                               | U.S. I                                                                      | PATENT DOCUMENTS                                          |  |

4,023,195 5/1977 Richman ...... 198/399

### OTHER PUBLICATIONS

IBM Tech. Discl. Bulletin, vol. 24, No. 1A, Jun. 1981, pp. 57-60, vol. 21, No. 3, Aug. 1978, pp. 1250-1251, vol. 24, No. 7A, Dec. 1981, pp. 3415-3416.

Primary Examiner-Martin H. Edlow Assistant Examiner—Charles S. Small, Jr. Attorney, Agent, or Firm-Pollock, Vande Sande & Priddy

#### **ABSTRACT** [57]

A sidewall isolation structure for field effect transistor which includes a first electrical insulating layer and a second electrical insulating layer contiguous with the first layer. The second electrical insulating material is etched above or below the surface level of the first insulating layer to provide recesses in the sidewall isolation structure, and method for the preparation thereof.

11 Claims, 8 Drawing Figures

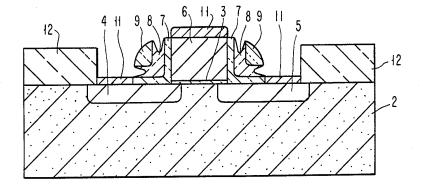

FIG. 1

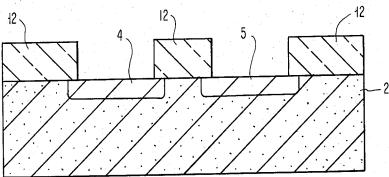

FIG. 2

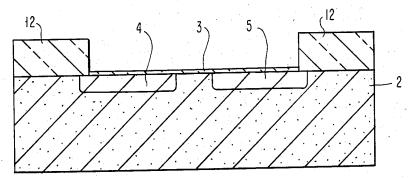

FIG. 3

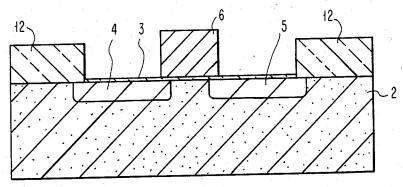

FIG. 7

FIG. 8

20

### GATE ELECTRODE SIDEWALL ISOLATION SPACER FOR FIELD EFFECT TRANSISTORS

This application is a continuation of application Ser. 5 No. 447,543, filed Dec. 7, 1982, now abandoned.

### DESCRIPTION

### 1. Technical Field

The present invention is concerned with certain side- 10 wall isolation structures for field effect transistors. In particular, the present invention is concerned with a sidewall isolation structure for field effect transistors which structure contains a plurality of electrical insulating materials. The present invention is also concerned 15 with a process for fabricating the sidewall isolation structure and, particularly, for fabricating a sidewall isolation structure having a plurality of insulating mate-

### 2. Background Art

The metallic type electrical connections to the source, drain, and gate regions of a field effect transistor can be achieved by various processes. One such procedure involves the selective reaction of a metal such as titanium, cobalt, palladium, or nickel with exposed sili- 25 con to obtain self-aligned contacts to the source, drain, and gate regions of the device. Achieving self-alignment is significant in the fabrication of field effect transistors since one of the most crucial steps in preparing FET devices is a lithographic masking step which re- 30 quires high precision in registration (i.e., relative maskto-mask alignment) and extreme care in execution.

With respect to the above procedure for achieving self-alignment of metallic type contacts to the source, drain, and gate regions of a FET device, it is important 35 to maintain the electrical isolation of the gate from the source and drain regions. This is accomplished by providing an isolation or electrical insulation layer on the sidewalls of the gate (which can be referred to as "spacer") and between the gate and semiconductor 40 substrate. To obtain self-aligned contacts, a metal is deposited over the entire region (the source, drain, gate, and over the sidewall isolation between the gate and the source and drain regions). Subsequent to this, the metal is reacted with the available exposed silicon which it 45 contacts to form a metallic silicide. Since the sidewalls are of an isolation material such as an oxide or nitride, reaction between the metal and the sidewall should not occur to form silicide. Subsequent to this, the unreacted metal on the sidewall isolation can then be selectively 50 etched away.

However, it has been observed in attempting to prepare devices by the procedure discussed above, that although free silicon is not present on the sidewalls, nonetheless, metallic silicides have formed thereon. 55 resulting in a recess below the surface level of the first This, in turn, causes electrical leakage between the source, drain, and gate areas across the spacer paths. It is not entirely understood as to what causes the silicide formation on the sidewalls, but it is believed that possidue to the temperature of the silicide formation and this leads to silicide formation there. This is particularly noticeable when employing metals such as cobalt and titanium to form the silicide.

### DISCLOSURE OF INVENTION

In order to prevent possible diffusion paths on the silicon over the spacer and thereby eliminating electri-

cal leakage across the spacer, the present invention provides a discontinuous metal film over the sidewall isolation layer rather than a continuous metal film as obtained in accordance with the above discussed tech-

Providing a discontinuous film over the sidewall isolation spacer prevents the formation of a continuous silicon diffusion path over the spacer. This prevents the formation of a continuous silicide film over the spacer and thereby precludes electrical leakage across the spacer after the unreacted metal has been selectively etched away.

This discontinuous path is created by recessing the sidewall isolation layer so that metal deposited thereon would be discontinuous over the isolation region. In particular, the sidewall isolation is fabricated of at least two different materials and the composite isolation region is then selectively etched in order to create a recess

In particular, the present invention is concerned with a sidewall isolation structure for field effect transistors which structure comprises a first electrical insulating material and a second and different electrical insulating material. The second electrical insulating material is contiguous with and preferably embedded in the first electrical insulating material. Moreover, the second electrical insulating material is etched above or preferably below the surface level of the first electrical insulating material to provide a recess in the sidewall isolation structure. This, in turn, prevents the formation of a continuous metal film over the sidewall isolation struc-

Another aspect of the present invention is a process for preparing sidewall isolation for field effect transistors. The process comprises providing a first electrical insulating layer over at least the sidewalls of an electrically conductive region. A second and different electrical insulating layer is provided adjacent the first electrical insulating layer on at least the sidewalls of the conductive region.

Although the present invention can be practiced with only two layers, it is preferred to provide a third electrical insulating layer adjacent the second and different insulating layer on at least the sidewalls. The third electrical insulating layer, if provided, can have substantially the same or a different etch rate as does the second insulating layer or the first insulating layer. However, it is preferred that such a third layer have an etch rate substantially the same as that of the first electrical insulating layer. The layers are then etched whereby the second layer is etched at a rate different than the first layer to thereby provide recesses in the sidewall isolation. Preferably the second layer is etched at a rate faster than the first layer and third layer, if present, and third layers.

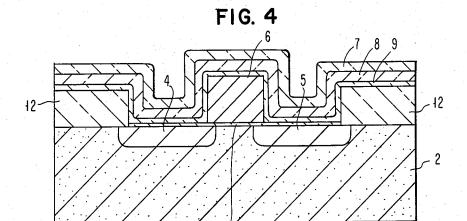

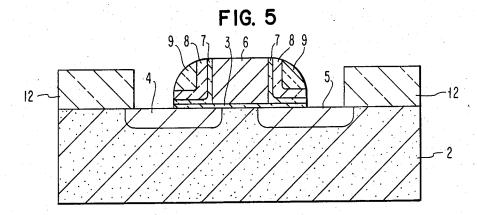

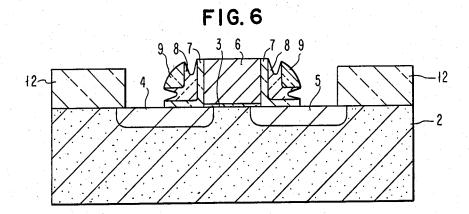

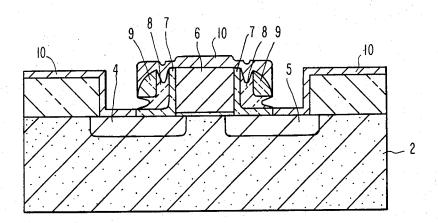

### BRIEF DESCRIPTION OF DRAWINGS

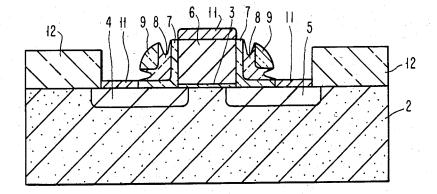

FIGS. 1-8 are cross-sectional views of a simplified bly silicon is diffused through the metal on the sidewall 60 field effect transistor in various stages of fabrication according to the present invention.

### BEST AND VARIOUS MODES FOR CARRYING **OUT INVENTION**

For convenience, the discussion of the fabrication steps is directed to the preferred aspect of employing a p-type silicon substrate as the semiconductive substrate and n-type impurities. This leads to the n-channel FET

# DOCKET A L A R M

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.