| OIPE HO           |  |

|-------------------|--|

| ( MAR 2 0 2007 H) |  |

| 2 BAR BAR BAR     |  |

DEPLAREF

Docket No.: 071971-001

2007 HAR 21 PH 4: PATENT

# IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

| In re Application of                                | : Customer Number: 20277  |

|-----------------------------------------------------|---------------------------|

| Mizuki SEGAWA, et al.                               | Confirmation Number: 5361 |

| Application No.: 10/995,283<br>Patent No. 7,126,174 | Group Art Unit: 2822      |

| Issue Date: October 24, 2006                        | Examiner: POTTER, Roy K.  |

| Filed: November 24, 2004                            |                           |

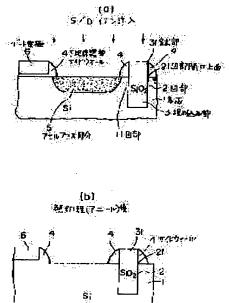

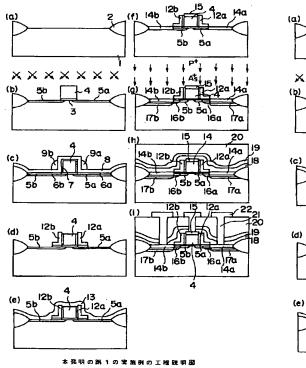

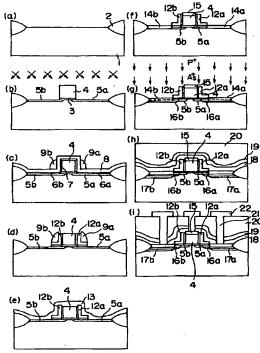

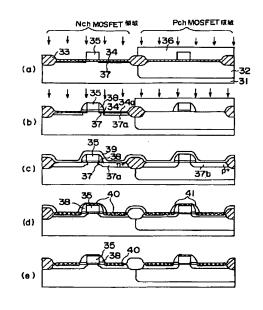

For: SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

#### **REQUEST FOR REFUND**

Mail Stop Request for Refund Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

Sir:

A refund in the amount of \$120.00 is hereby requested in the above-identified application

for the following reason:

The Petition for Extension of Time in the amount of \$120.00 filed on February 20, 2007

was inadvertently filed in this case.

Please immediately credit Deposit Account number 500417 in this amount.

Respectfully submitted,

McDERMOTT WILL & EMERY LLP

Ramyar M. Facid Registration No. 46,692 Please recognize our Customer No. 20277 as our correspondence address Holusteen Date: 04/05/2007 MGEBREM1 02/26/2007 ANONDAF1 00000045 500417 01 FC:1251 120.00 CR 10995283

600 13<sup>th</sup> Street, N.W. Washington, DC 20005-3096 Phone: 202.756.8000 RMF:MaM Facsimile: 202.756.8087 **Date: March 20, 2007**

WDC99 1363893-1.071971.0012

Global Foundaries US v. Godo Kaisha Global Ex. 1021

Page 1 of 262

# ATTENTION ATTENTION ATTENTION

| Method of Refund:                 |

|-----------------------------------|

| ACH/EFT                           |

| Credit Card                       |

| Deposit Account # <u>50-04</u>    |

| Treasury Check                    |

| Patent/TM/App/Serial # 10 995,283 |

| Program Area Lech Center 2822     |

| Date Processed 3 27 2007          |

|                                   |

ATTENTION ATTENTION ATTENTION

•

₹ / -

UNITED STATES PATENT AND TRADEMARK OFFICE

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandra, Virgina 22313-1450 www.upto.gov

**CONFIRMATION NO. 5361**

### \*BIBDATASHEET\*

Bib Data Sheet

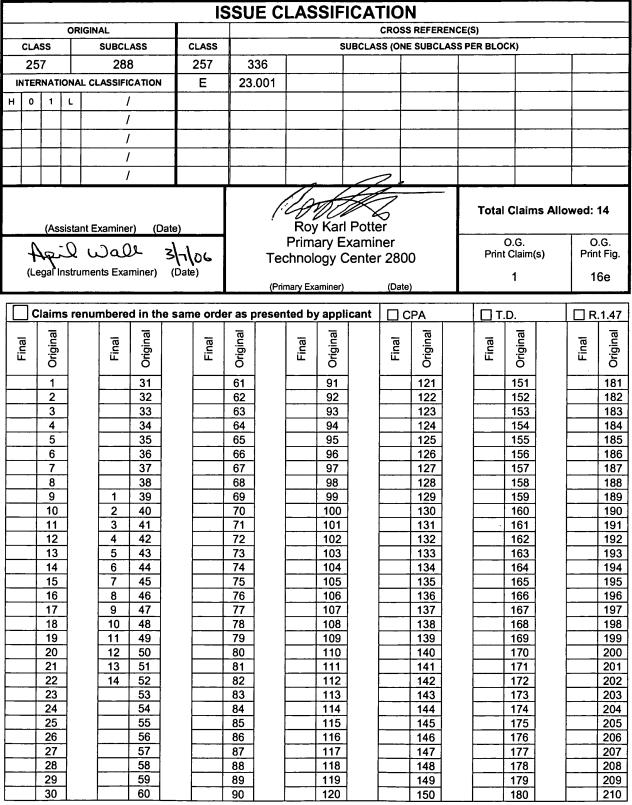

| <b>SERIAL NUMB</b><br>10/995,283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ER      | FILING OR 371(c)<br>DATE<br>11/24/2004<br>RULE | c             | 257                          | GRO | <b>UP ART</b><br>2822 | UNIT              | D  | <b>ATTORNEY</b><br>OCKET NO.<br>71971-012 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------|---------------|------------------------------|-----|-----------------------|-------------------|----|-------------------------------------------|

| RULE         APPLICANTS         Mizuki Segawa, Osaka, JAPAN;         Isao Miyanaga, Osaka, JAPAN;         Toshiki Yabu, Osaka, JAPAN;         Takashi Nakabayashi, Osaka, JAPAN;         Takashi Uehara, Osaka, JAPAN;         Takashi Uehara, Osaka, JAPAN;         Takashi Uehara, Osaka, JAPAN;         Takashi Ukeda, Osaka, JAPAN;         Takaaki Ukeda, Osaka, JAPAN;         Masatoshi Arai, Osaka, JAPAN;         Masatoshi Arai, Osaka, JAPAN;         Takayuki Yamada, Osaka, JAPAN;         Masatoshi Arai, Osaka, JAPAN;         Michikazu Matsumoto, Osaka, JAPAN;         JAPAN 7:0100 0009/02.157 07/11/2001 PAT 6,709,950         which is a DIV of 08/685,726 07/24/1996 PAT 6 |         |                                                |               |                              |     |                       |                   |    |                                           |

| Foreign Priority claime<br>35 USC 119 (a-d) con<br>met<br>Verified and<br>Acknowledged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ditions | Allowance                                      | ter<br>itials | STATE OR<br>COUNTRY<br>JAPAN | DRA | ETS<br>WING<br>1      | TOT<br>CLAI<br>14 | MS | INDEPENDENT<br>CLAIMS<br>1                |

| ADDRESS<br>20277                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                                                |               |                              |     |                       |                   |    |                                           |

| TITLE<br>SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                                |               |                              |     |                       |                   |    |                                           |

| FILING FEE       FEES: Authority has been given in Paper         No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                |               |                              |     | essing Ext. of        |                   |    |                                           |

| ۲ |        | Page 2 of 2 |

|---|--------|-------------|

|   | Credit |             |

| ·, ·,                                                                                                        |                                                                                                      | PART I                                                | B - FEE(S) TRANSN                                                                                                                                                              | AITTAL                                                                                                                         |                                                                                                                           |                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                              |                                                                                                      |                                                       | P.C<br>Ale<br>or <u>Fax</u> (57                                                                                                                                                | mmissioner for Pate<br>). Box 1450<br>xandria, Virginia 2<br>1)-273-2885                                                       | 2313-1450                                                                                                                 |                                                                                                                                                             |

| annronriate All further                                                                                      | correspondence includir<br>ed below or directed oth                                                  | ig the Patent, advance o                              | rders and notification of r                                                                                                                                                    | naintenance fees will be                                                                                                       | mailed to the current                                                                                                     | hould be completed where<br>correspondence address as<br>rate "FEE ADDRESS" for                                                                             |

| CURRENT CORRESPOND                                                                                           | ENCE ADDRESS (Note: Use BI                                                                           | ock 1 for any change of hidderss                      | Feed<br>Feed                                                                                                                                                                   | s) Transmittal. This certif                                                                                                    | icate cannot be used f<br>, such as an assignme                                                                           | r domestic mailings of the<br>or any other accompanying<br>nt or formal drawing, must                                                                       |

| McDermott Wi<br>600 13th Street,<br>Washington, DC                                                           |                                                                                                      | AUG 3 0                                               | Stat                                                                                                                                                                           | Certificate<br>reby certify that this Fee(<br>se Postal Service with suf<br>essed to the Mail Stop<br>smitted to the USPTO (57 | of Mailing or Trans.<br>s) Transmittal is being<br>ficient postage for firs<br>ISSUE FEE address<br>1) 273-2885, on the d | deposited with the United<br>t class mail in an envelope<br>above, or being facsimile<br>ate indicated below.                                               |

| "CUSTOMER N                                                                                                  | IO • 20277"                                                                                          |                                                       | -<br>                                                                                                                                                                          |                                                                                                                                |                                                                                                                           | (Depositor's name)<br>(Signature)                                                                                                                           |

| COSTORER P                                                                                                   | 10.: 20277                                                                                           |                                                       |                                                                                                                                                                                |                                                                                                                                |                                                                                                                           | (Date)                                                                                                                                                      |

| APPLICATION NO.                                                                                              | FILING DATE                                                                                          | <del></del>                                           | FIRST NAMED INVENTOR                                                                                                                                                           | ATTO                                                                                                                           | RNEY DOCKET NO.                                                                                                           | CONFIRMATION NO.                                                                                                                                            |

| 10/995,283                                                                                                   | 11/24/2004                                                                                           |                                                       | Mizuki Segawa                                                                                                                                                                  |                                                                                                                                | 71971-012                                                                                                                 | 5361                                                                                                                                                        |

| APPLN. TYPE                                                                                                  | SMALL ENTITY                                                                                         | ISSUE FEE DUE                                         | PUBLICATION FEE DUE                                                                                                                                                            | PREV. PAID ISSUE FEE                                                                                                           | TOTAL FEE(S) DUE                                                                                                          | DATE DUE                                                                                                                                                    |

| nonprovisional                                                                                               | NO                                                                                                   | \$1400                                                | \$300                                                                                                                                                                          | \$0                                                                                                                            | \$1700                                                                                                                    | 10/17/2006                                                                                                                                                  |

| EXAM                                                                                                         | INER                                                                                                 | ART UNIT                                              | CLASS-SUBCLASS                                                                                                                                                                 | · ·                                                                                                                            |                                                                                                                           |                                                                                                                                                             |

| POTTER, R                                                                                                    |                                                                                                      | 2822                                                  | 257-288000                                                                                                                                                                     |                                                                                                                                |                                                                                                                           |                                                                                                                                                             |

| Address form PTO/SE                                                                                          | ondence address (or Cha<br>3/122) attached.<br>ication (or "Fee Address'<br>2 or more recent) attach | nge of Correspondence<br>Indication form              | or agents OR, alternativ<br>(2) the name of a single<br>registered attorney or a                                                                                               | 3 registered patent attorn<br>rely,<br>e firm (having as a membe<br>gent) and the names of up<br>meys or agents. If no nam     | EMERY<br>er a 2                                                                                                           | MOTT WILL &                                                                                                                                                 |

| PLEASE NOTE: Unl<br>recordation as set fort<br>(A) NAME OF ASSIG<br>MATSUSI                                  | ess an assignee is ident<br>h in 37 CFR 3.11. Comp<br>GNEE<br>HITA ELECTRIC                          | fod holow, no orgionas                                | (B) RESIDENCE: (CITY)                                                                                                                                                          | ttent. If an assignee is id<br>assignment<br>and STATE OR COUNT<br>01 FC:1501<br>SAKA, 03 FFA:04<br>03 FFA:04                  | ERHE1 00000089 5<br>RY<br>1400.00 DA<br>.300.00 DA<br>.12.00 DA                                                           | becument has been filed for<br>19995283                                                                                                                     |

| a. The following fee(s) a<br>Issue Fee<br>Publication Fee (N<br>Advance Order - #                            | o small entity discount p                                                                            | ermitted)                                             | b. Payment of Fee(s): (Plea<br>A check is enclosed.<br>Payment by credit car<br>The Director is hereby<br>overpayment, to Depo                                                 | d. Form PTO-2038 is atta                                                                                                       | ched.                                                                                                                     |                                                                                                                                                             |

| 5. Change in Entity Stat                                                                                     | tus (from status indicated<br>s SMALL ENTITY statu                                                   | -                                                     |                                                                                                                                                                                | ger claiming SMALL ENT                                                                                                         | · · · · · · · · · · · · · · · · · · ·                                                                                     |                                                                                                                                                             |

| NOTE: The Issue Fee and<br>interest as shown by the r                                                        | d Publication Fee (if requ<br>ecords of the United Sta                                               | ired) will not be accepte<br>tes Patent and Trademark | d from anyone other than the office.                                                                                                                                           | ne applicant; a registered a                                                                                                   | ttorney or agent; or th                                                                                                   | e assignee or other party in                                                                                                                                |

| Authorized Signature                                                                                         |                                                                                                      | F                                                     |                                                                                                                                                                                | Date                                                                                                                           | 30, 2006                                                                                                                  |                                                                                                                                                             |

| Typed or printed name                                                                                        |                                                                                                      | Fogarty                                               |                                                                                                                                                                                | • —                                                                                                                            | 36,139                                                                                                                    |                                                                                                                                                             |

| submitting the completed<br>this form and/or suggesti<br>Box 1450, Alexandria, V<br>Alexandria, Virginia 223 | application form to the<br>ons for reducing this but<br>irginia 22313-1450. DO<br>13-1450.           | den, should be sent to th<br>NOT SEND FEES OR         | on is required to obtain or r<br>1.14. This collection is est<br>depending upon the indiv<br>e Chief Information Office<br>COMPLETED FORMS TO<br>spond to a collection of infe | r, U.S. Patent and Tradem<br>THIS ADDRESS. SEND                                                                                | ark Office, U.S. Depa<br>TO: Commissioner f                                                                               | by the USPTO to process)<br>g gathering, preparing, and<br>ne you require to complete<br>rtment of Commerce, P.O.<br>for Patents, P.O. Box 1450,<br>number. |

UNITED STATES PATENT AND TRADEMARK OFFICE

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandria, Virginia 22313-1450 www.uspto.gov

### NOTICE OF ALLOWANCE AND FEE(S) DUE

7590 07/17/2006

McDermott Will & Emery LLP 600 13th Street, N.W. Washington, DC 20005-3096

| EXAMINER              |     |  |  |  |  |  |

|-----------------------|-----|--|--|--|--|--|

| POTTER, ROY KARL      |     |  |  |  |  |  |

| ART UNIT PAPER NUMBER |     |  |  |  |  |  |

| 2822                  |     |  |  |  |  |  |

| DATE MAILED: 07/17/20 | 006 |  |  |  |  |  |

APPLICATION NO.FILING DATEFIRST NAMED INVENTORATTORNEY DOCKET NO.CONFIRMATION NO.10/995,28311/24/2004Mizuki Segawa71971-0125361

TITLE OF INVENTION: SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

| APPLN. TYPE    | SMALL ENTITY | ISSUE FEE DUE | PUBLICATION FEE DUE | PREV. PAID ISSUE FEE | TOTAL FEE(S) DUE | DATE DUE   |

|----------------|--------------|---------------|---------------------|----------------------|------------------|------------|

| nonprovisional | NO           | \$1400        | \$300               | \$0                  | \$1700           | 10/17/2006 |

THE APPLICATION IDENTIFIED ABOVE HAS BEEN EXAMINED AND IS ALLOWED FOR ISSUANCE AS A PATENT. <u>PROSECUTION ON THE MERITS IS CLOSED</u>. THIS NOTICE OF ALLOWANCE IS NOT A GRANT OF PATENT RIGHTS. THIS APPLICATION IS SUBJECT TO WITHDRAWAL FROM ISSUE AT THE INITIATIVE OF THE OFFICE OR UPON PETITION BY THE APPLICANT. SEE 37 CFR 1.313 AND MPEP 1308.

THE ISSUE FEE AND PUBLICATION FEE (IF REQUIRED) MUST BE PAID WITHIN <u>THREE MONTHS</u> FROM THE MAILING DATE OF THIS NOTICE OR THIS APPLICATION SHALL BE REGARDED AS ABANDONED. <u>THIS STATUTORY PERIOD CANNOT BE EXTENDED</u>. SEE 35 U.S.C. 151. THE ISSUE FEE DUE INDICATED ABOVE DOES NOT REFLECT A CREDIT FOR ANY PREVIOUSLY PAID ISSUE FEE IN THIS APPLICATION. IF AN ISSUE FEE HAS PREVIOUSLY BEEN PAID IN THIS APPLICATION (AS SHOWN ABOVE), THE RETURN OF PART B OF THIS FORM WILL BE CONSIDERED A REQUEST TO REAPPLY THE PREVIOUSLY PAID ISSUE FEE TOWARD THE ISSUE FEE NOW DUE.

#### HOW TO REPLY TO THIS NOTICE:

I. Review the SMALL ENTITY status shown above.

PTOL-85 (Rev. 07/06) Approved for use through 04/30/2007.

| If the SMALL ENTITY is shown as YES, verify your current<br>SMALL ENTITY status:                                                                                                           | If the SMALL ENTITY is shown as NO:                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A. If the status is the same, pay the TOTAL FEE(S) DUE shown above.                                                                                                                        | A. Pay TOTAL FEE(S) DUE shown above, or                                                                                                                                                                              |

| B. If the status above is to be removed, check box 5b on Part B -<br>Fee(s) Transmittal and pay the PUBLICATION FEE (if required)<br>and twice the amount of the ISSUE FEE shown above, or | B. If applicant claimed SMALL ENTITY status before, or is now claiming SMALL ENTITY status, check box 5a on Part B - Fee(s) Transmittal and pay the PUBLICATION FEE (if required) and 1/2 the ISSUE FEE shown above. |

II. PART B - FEE(S) TRANSMITTAL, or its equivalent, must be completed and returned to the United States Patent and Trademark Office (USPTO) with your ISSUE FEE and PUBLICATION FEE (if required). If you are charging the fee(s) to your deposit account, section "4b" of Part B - Fee(s) Transmittal should be completed and an extra copy of the form should be submitted. If an equivalent of Part B is filed, a request to reapply a previously paid issue fee must be clearly made, and delays in processing may occur due to the difficulty in recognizing the paper as an equivalent of Part B.

III. All communications regarding this application must give the application number. Please direct all communications prior to issuance to Mail Stop ISSUE FEE unless advised to the contrary.

IMPORTANT REMINDER: Utility patents issuing on applications filed on or after Dec. 12, 1980 may require payment of maintenance fees. It is patentee's responsibility to ensure timely payment of maintenance fees when due.

#### PART B - FEE(S) TRANSMITTAL

#### Complete and send this form, together with applicable fee(s), to: Mail Mail Stop ISSUE FEE

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                   |                                                                                                      | P.0<br>Al                                                                     | ommissioner fo<br>O. Box 1450<br>exandria, Virgi<br>71)-273-2885 |                                                                                       |                                                                        |                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| INSTRUCTIONS: This<br>appropriate. All further<br>indicated unless correcte<br>maintenance fee notificat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | d below or directed ot                                                                                                                                                                                            | for transmitting the ISSU<br>ng the Patent, advance o<br>herwise in Block 1, by (a                   | JE FEE and PUBLICAT<br>rders and notification of<br>a) specifying a new corre | ION FEE (if requi<br>maintenance fees w<br>spondence address;    | ired). Bl<br>vill be m<br>; and/or                                                    | ocks 1 through 5 sh<br>nailed to the current<br>(b) indicating a separ | ould be completed where<br>correspondence address as<br>rate "FEE ADDRESS" for                                |

| CURRENT CORRESPONDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fee<br>pap                                                                                                                                                                                                        | e(s) Transmittal. Thi<br>ers. Each additiona                                                         | is certific<br>I paper, :                                                     | cate cannot be used for                                          | r domestic mailings of the<br>or any other accompanying<br>at or formal drawing, must |                                                                        |                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7590 07/17                                                                                                                                                                                                        | 7/2006                                                                                               | fia v                                                                         |                                                                  |                                                                                       | of Mailing or Transr                                                   | nissian                                                                                                       |

| McDermott Will & Emery LLP<br>600 13th Street, N.W.<br>Washington, DC 20005-3096                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                   |                                                                                                      | I ha<br>Sta<br>add<br>trar                                                    | ereby certify that th                                            | is Fee(s)                                                                             | Transmittal is being                                                   | deposited with the United<br>t class mail in an envelope<br>above, or being facsimile<br>the indicated below. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                   |                                                                                                      |                                                                               |                                                                  |                                                                                       |                                                                        | (Depositor's name)                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                   |                                                                                                      |                                                                               |                                                                  |                                                                                       |                                                                        | (Signature)<br>(Date)                                                                                         |

| APPLICATION NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FILING DATE                                                                                                                                                                                                       |                                                                                                      | FIRST NAMED INVENTOR                                                          |                                                                  | ATTOR                                                                                 | NEY DOCKET NO.                                                         | CONFIRMATION NO.                                                                                              |

| 10/995,283                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11/24/2004                                                                                                                                                                                                        | L.                                                                                                   | Mizuki Segawa                                                                 |                                                                  |                                                                                       | 71971-012                                                              | 5361                                                                                                          |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SEMICONDUCTOR I                                                                                                                                                                                                   | DEVICE AND METHOD                                                                                    | OF MANUFACTURING                                                              | 3 THE SAME                                                       |                                                                                       |                                                                        |                                                                                                               |

| APPLN. TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SMALL ENTITY                                                                                                                                                                                                      | ISSUE FEE DUE                                                                                        | PUBLICATION FEE DUE                                                           | PREV. PAID ISSU                                                  | e fee                                                                                 | TOTAL FEE(S) DUE                                                       | DATE DUE                                                                                                      |

| nonprovisional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NO                                                                                                                                                                                                                | \$1400                                                                                               | \$300                                                                         | \$0                                                              |                                                                                       | \$1700                                                                 | 10/17/2006                                                                                                    |

| EXAMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | INER                                                                                                                                                                                                              | ART UNIT                                                                                             | CLASS-SUBCLASS                                                                | ]                                                                |                                                                                       |                                                                        |                                                                                                               |

| POTTER, R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                   | 2822                                                                                                 | 257-288000                                                                    |                                                                  |                                                                                       |                                                                        |                                                                                                               |

| <ol> <li>Change of corresponde<br/>CFR 1.363).</li> <li>Change of corresponde<br/>Address form PTO/SB</li> <li>"Fee Address" indir<br/>PTO/SB/47; Rev 03-07.</li> <li>Number is required.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ol> <li>For printing on the p</li> <li>the names of up to<br/>or agents OR, alternati</li> <li>the name of a sing<br/>registered attorney or<br/>2 registered patent atto<br/>listed, no name will be</li> </ol> | b 3 registered paten<br>vely,<br>le firm (having as a<br>agent) and the name<br>prneys or agents. If | t attorne<br>member<br>es of up                                               | ra 2                                                             |                                                                                       |                                                                        |                                                                                                               |

| 3. ASSIGNEE NAME AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ND RESIDENCE DATA                                                                                                                                                                                                 | A TO BE PRINTED ON T                                                                                 | L<br>THE PATENT (print or ty                                                  | pe)                                                              |                                                                                       |                                                                        |                                                                                                               |

| <ul> <li>3. ASSIGNEE NAME AND RESIDENCE DATA TO BE PRINTED ON THE PATENT (print or type)         PLEASE NOTE: Unless an assignee is identified below, no assignee data will appear on the patent. If an assignee is identified below, the document has been filed for recordation as set forth in 37 CFR 3.11. Completion of this form is NOT a substitute for filing an assignment.         (A) NAME OF ASSIGNEE         (B) RESIDENCE: (CITY and STATE OR COUNTRY)     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                                                                                      |                                                                               |                                                                  |                                                                                       |                                                                        |                                                                                                               |

| Please check the appropria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ate assignee category or                                                                                                                                                                                          | categories (will not be pr                                                                           | inted on the patent) :                                                        | Individual Co                                                    | orporation                                                                            | n or other private grou                                                | up entity Government                                                                                          |

| 4a. The following fee(s) are submitted:       4b. Payment of Fee(s): (Please first reapply any previously paid issue fee shown above)            [Issue Fee           [A check is enclosed.             Publication Fee (No small entity discount permitted)           [A dvance Order - # of Copies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |                                                                                                      |                                                                               |                                                                  |                                                                                       | ·                                                                      |                                                                                                               |

| 5. Change in Entity State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                                                                                 | ,                                                                                                    |                                                                               |                                                                  |                                                                                       |                                                                        |                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SMALL ENTITY state<br>Publication Fee (if requested states)                                                                                                                                                       |                                                                                                      | b. Applicant is no lon<br>from anyone other than to<br>Office.                | <u> </u>                                                         |                                                                                       |                                                                        |                                                                                                               |

| NOTE: The Issue Fee and Publication Fee (if required) will not be accepted from anyone other than the applicant; a registered attorney or agent; or the assignee or other party in interest as shown by the records of the United States Patent and Trademark Office.  Authorized Signature Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                   |                                                                                                      |                                                                               |                                                                  |                                                                                       |                                                                        |                                                                                                               |