US006100184A

**Patent Number:**

6,100,184

## United States Patent [19]

Zhao et al. [45] Date of Patent: Aug. 8, 2000

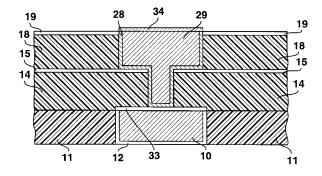

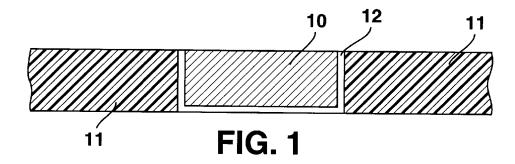

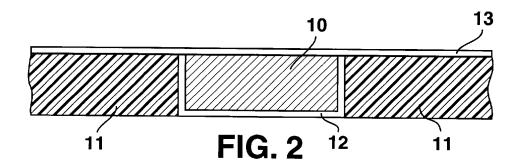

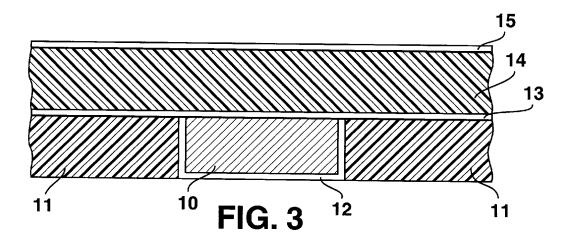

# [54] METHOD OF MAKING A DUAL DAMASCENE INTERCONNECT STRUCTURE USING LOW DIELECTRIC CONSTANT MATERIAL FOR AN INTER-LEVEL DIELECTRIC LAYER

[75] Inventors: Bin Zhao, Irvine, Calif.; Prahalad K. Vasudev, Austin, Tex.; Ronald S. Horwath, Santa Clara; Thomas E. Seidel, Sunnyvale, both of Calif.; Peter M. Zeitzoff, Austin, Tex.

[73] Assignees: Sematech, Inc., Austin, Tex.; Lucent Technologies Inc., Murray Hill, N.J.

[21] Appl. No.: 08/914,995

[22] Filed: Aug. 20, 1997

85, 902, 629, 636, 648, 653, 656, 687

## [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,789,648 | 12/1988 | Chow et al 437/2   | 225 |

|-----------|---------|--------------------|-----|

| 5,635,423 | 6/1997  | Huang et al 437/1  | 195 |

| 5,695,810 | 12/1997 | Dubin et al 427    | /96 |

| 5,731,245 | 3/1998  | Joshi et al 438/7  | 705 |

| 5,739,579 | 12/1997 | Chiang et al 257/6 | 535 |

| 5,753,967 | 5/1998  | Lin                | 535 |

## OTHER PUBLICATIONS

"A Novel Sub-Half Micron Al-Cu Via Plug Interconnect Using Low Dielectric Constant Material as Inter-Level Dielectric", Zhao et al., IEEE Electron Device Letters, vol. 18, No. 2, Feb. 1997, pp. 57–59.

"Low Capacitance Multilevel Interconnection Using Low-e Organic Spin-on Glass for Quarter-Micron High-Speed ULSIs", Furusawa et al., 1995 Symposium on VLSI Technology Digest of Technical Papers, pp. 59–60.

"Low-k Organic Spin-on Materials in a Non-Etchback Interconnect Strategy", J. Waeterloos et al., DUMIC Conference, Feb. 20-21, 1996, pp. 52-59.

"Integration of BPDA-PDA Polyimide with Two levels of AL(Ci) Interconnects", Wetzel et al., 1995 Material Research Society Symposium Proceedings, vol. 381, pp. 217–229.

"A Novel 0.25 um Via Plug Process Using Low Temperature CVD AL/TiN", Dixit et al., Dec. 10–13, 1995, International Electron Devices Meeting, pp. 10.7.1–10.7.3.

"Single Step PVD Planarized Aluminum Interconnect with Low-e Organic ILD for High Performance and Low Cost ULSI", Zhao et al., 1996 Symposium on VLSI Technology Digest of Technical Papers, pp. 72–73.

"A Highly Reliable Low Temperature Al–Cu Linve/Via Metallization for Sub–Half Micrometer CMOS", Joshi et al., IEEE Electron Device Letters, vol. 16, No. 6, Jun. 1995, pp. 233–235.

"A Planarized Multilevel Interconnect Scheme with Embedded Low-Dielectric-Constant Polymers for Sub-Quarter-Micron Applications", Jeng et al., 1994 Symposium on VLSI Technology Digest of Technical Papers, pp. 73–74.

"On Advanced Interconnect Using Low Dielectricl Constant Materials as Inter–Level Dielectrics", Zhao et al., 1996, Material Research Society Symposium Proceedings vol. 427, pp. 415–427.

"Electromigration Reliability of Tungsten and Aluminum Vias and Improvements Under AC Current Stress", Tao et al., IEEE Transactions on Electron Devices, vol. 40, No. 8, Aug. 1993, pp. 1398–1405.

"Planar Copper–Polyimide Back End of the Line Interconnections for ULSI Devices," B. Luther et al., 1993 VMIC Convference, Jun. 8–9, 1993, pp. 15–21.

Pending Patent Application titled, "Use of Cobalt Tungsten Phosphide as a Barrier Material for Copper Metallization", Serial No. 08/754,600, filed Nov. 20, 1996.

Primary Examiner—John F. Niebling Assistant Examiner—David A. Zarneke

#### [57] ABSTRACT

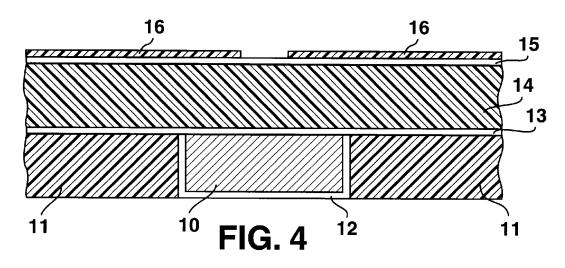

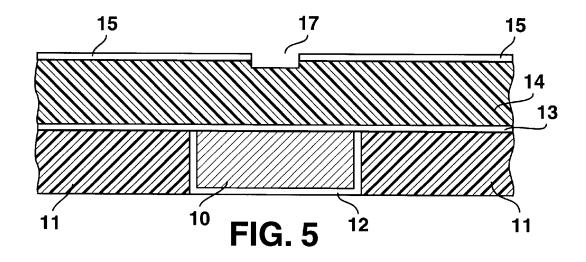

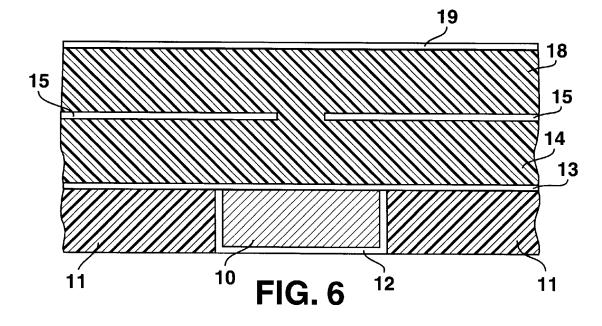

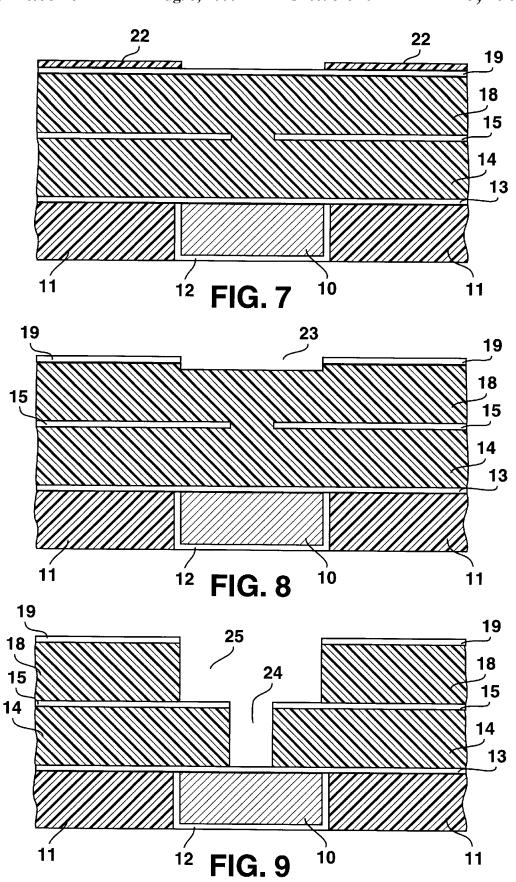

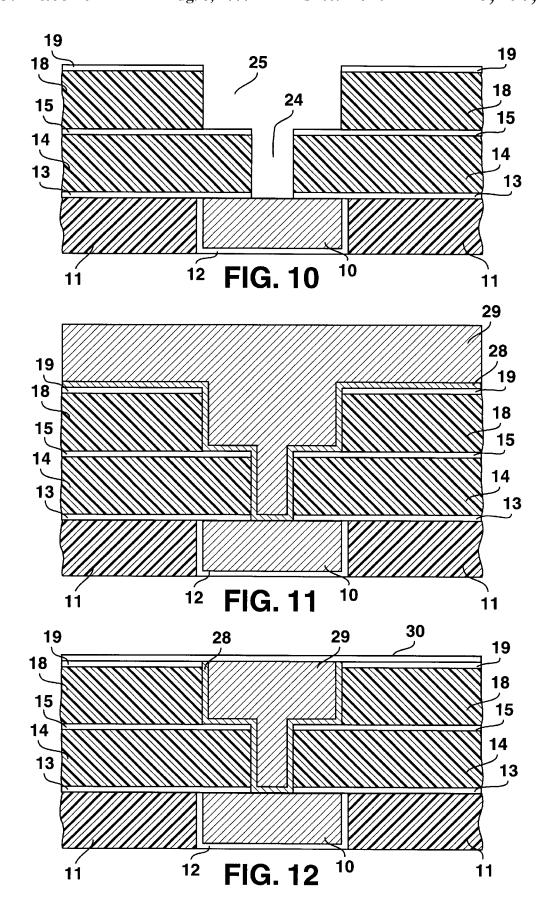

A technique for fabricating a dual damascene interconnect structure using a low dielectric constant material as a dielectric layer or layers. A low dielectric constant (low-) dielectric material is used to form an inter-level dielectric (ILD) layer between metallization layers and in which via and trench openings are formed in the low- ILD. The dual damascene technique allows for both the via and trench openings to be filled at the same time.

## 12 Claims, 6 Drawing Sheets

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.