**Patent Number:**

**Date of Patent:**

# United States Patent [19]

Clay

## [54] DISK DRIVE SYSTEM INTERFACE ARCHITECTURE EMPLOYING STATE MACHINES

- [75] Inventor: Donald W. Clay, Louisville, Colo.

- [73] Assignce: Conner Peripherals, Inc., San Jose, Calif.

- [21] Appl. No.: 110,883

- [22] Filed: Aug. 24, 1993

- [52] **U.S. Cl.** ...... **395/310**; 395/439; 395/894; 395/404

## [56] References Cited

## U.S. PATENT DOCUMENTS

5,276,662 1/1994 Shaver, Jr. et al. ...... 369/32

Primary Examiner—Jack B. Harvey Assistant Examiner—John Travis Attorney, Agent, or Firm—Fliesler, Dubb, Meyer & Lovejoy

5,465,338

Nov. 7, 1995

## [57] ABSTRACT

[11]

[45]

In a disk drive storage system, an interface apparatus for controlling the transfer of sectors of data between a host processor and a buffer within the storage system in response to READ and WRITE command issued by the host processor. The apparatus comprises a Byte Count State Machine for controlling the transfer of a sector of data between the host processor and the buffer, an Update Task File State Machine for counting the sectors transferred by the Byte Count State Machine and generating the sector address of the next sector to be transferred by the Byte Count State Machine, a Read State Machine for controlling the processing of all READ commands and a Write State Machine for controlling the processing of all WRITE commands.

## 7 Claims, 18 Drawing Sheets

## WRITE

FIG. 3C

# INITIALIZATION

# FIG. 4B

FIG. 5

WD

=0

-0

NAN 200 WC FIG. 8 NAN WB 201 F NAN 202 NAN WA 224 DFF 228 NAN 203 SECT CNT NOT = ONAN 204 WA Ĥ END DELAY NAN 205 SECT CNT NAN F 206 NAN 207 ► W0 WA STAT NAN 208 ► W1 NAN WB DFF W2 225 OK TO XFR 229 **W3** NAN **W4** 209 SECT CNT WB Ê ► W5 NAN 210 W6 LONG-W7 AND D **W8** 211 ECODE **W9** AND 212 WA ► WB AND 213 WC AND 214 ♦ WD R + WE OR 226 WC AND 215 → WF DFF 230 232 AND 216 BLK CNT · WC NOT = O AND 217 BYTE CNF AXXX I NAN 218 NOT = OLONG-NAN 219 NAN Ŕ 220 NAN NAN 227 221 WD NAM 222 DFF **BLK CNT** 231 NAN 223 WD SECT CNT

RESET CLOCK

FIG. 9

FIG. 11

**RST**A

DFF AND CLOCK-400 414 BLK CNT = 1-OR 402 NANC DFF 401 403 AND AND BYTE CNT -O-420 415 GATE AND 1ST WORD INV AND AND 405 404 • 406 416 HIOR-OR READ AND AND 408 READ DATA INV 421 MODE 407 AND WRITE INV 418 MODE 409 WRITE OR DATA AND AND HIOW 410 419 422 OR AND 411 AND C1-413 **RESET** 412 CCBBAA + RST A С DECR **C1** NAN NAN AND DFF BYTE -C 439 С 431 423 426 CNT NOF B **C5** ARD 437 DFF NANO AND B 424 427 432 Α DFF NAN C2 MANC A + CLK HIGH BYTE CLK+ 425 Ç 433 H 428 CLK HIGH BYTE EN ECC NAN CLK LOW BYTE 434 BYTE CNT = 0 AND AND 435 NOF WRITE MODE-→ AWR 429 438 AND 436 AND NAN → GATE HIGH BYTE 440 430 DFF 442 CLK-INV FIG. 12 441 NAN

18

FIG. 13

# FIG. 14

## DISK DRIVE SYSTEM INTERFACE ARCHITECTURE EMPLOYING STATE MACHINES

## BACKGROUND OF THE INVENTION

## 1. Field of the Invention

The present invention relates generally to digital data storage systems and more particularly to an AT interface architecture employing state machines for use in a digital <sup>10</sup> data storage system. More particular still, the invention relates to a flash solid state memory system that employs the AT interface architecture comprising state machines.

2. Description of the Related Art

15 Magnetic disk drives have been widely accepted in the computer industry and are used for storing large amounts of data. Over the years, magnetic disk drives have decreased in size while increasing in operational speed and in the amount of data that can be stored on the magnetic media. Magnetic 20 disk drives have associated with them a seek latency time which is associated with the time necessary to move the desired transducer to the desired track or cylinder on the magnetic media for the purpose of recovering or writing data to and from the magnetic media. In addition, there is a  $_{25}$ rotational latency associated with waiting for the desired data sector to pass underneath the transducer once the transducer is located on the desired track. Magnetic disk drives also have the associated problems of relying on mechanical hardware for locating the transducer at a specific 30 location with regards to the magnetic media and for maintaining the rotational speed of the magnetic media at some constant value. The mechanical hardware is affected by the normal wear and tear associated with mechanical devices. Further, magnetic disk drives have employed various track 35 following servo systems for maintaining the transducer on a desired track once the transducer reaches that desired track. Finally, the magnetic disk drive tracks are divided into a fixed number of sectors where each sector stores a fixed number of data bytes. As a rule, magnetic disk drive systems 40 will write a complete sector each time a sector is written. Where the data is less than a full sector the data is padded with zeros to fill up the sector. This is to say that if the sector length is 512 bytes, whenever a sector is written 512 bytes of data will be written into that sector. The requirements of  $_{45}$ writing a full sector every time a sector is written means that a substantial portion of the magnetic surface may be allocated to contain filler data rather than useful data. Finally, it can readily be realized that the data would also be recovered from the magnetic disk drive in sector lengths and, therefore, 50 a full sector must be read from the disk regardless of the actual amount of useful data that was recorded in that sector.

With the advent of solid state memories, attempts have been made to emulate the magnetic disk drives by use of solid state memories in place of the magnetic media. 55 Examples of such emulations are found in U.S. Pat. No. 4,642,759 entitled "Bubble Memory Disk Emulation System" and U.S. Pat. No. 5,131,089 entitled "Solid State Disk Drive Emulation".

The ideal system would use a solid state memory that is 60 nonvolatile such as the above-referenced bubble memory or the solid state memory with its own power supply to maintain the stored data even though power is turned off to the drive. However, each of these solid state memories each have their own advantages and disadvantages which must be 65 weighed in selecting which solid state memory should and could be used in a specific design.

To have a solid state drive emulate a magnetic disk drive, the solid state storage media must be transparent to the host. Ideally, the solid state drive would accept the same commands and data formats as the magnetic disk drive such that no change in programming or system configuration need be done within the host. A disadvantage associated with most solid state memories is the time necessary to write into the memory. The slow write speed is a major reason why the solid state drives emulating magnetic disk drives have not been more widely accepted and marketed within the industry.

At present, both in magnetic disk drives and in flash disk drives, a microcontroller is employed for controlling the operation of the storage system. One of the functions of the microcontroller is to control the transfer of data across the host interface between the host processor and the storage media within the drive system. This requires that the microprocessor dedicate resources to transfer data between the host computer and the storage system across the interface in response to READ and WRITE commands. This requirement limits the microprocessor's availability to perform other functions and, therefore, results in a limitation on the overall system performance of the storage system. In magnetic disk drive storage systems, some attempts have been made to unburden the microprocessor by transferring some of the functions of the microprocessor to state machines or to have a two microprocessors involved in performing the functions thereby reducing the workload on each microprocessor and allowing two functions to be in process at the same time. In particular, the flash solid state drive system requires the microprocessor to be involved in housekeeping operations with regard to the flash memory, as well as controlling the reading and writing of data from the memory buffer to the flash memory itself. This increased responsibility on the microprocessor further reduces the system performance due to the time necessary to perform the increased functions allocated to the microprocessor.

## SUMMARY OF THE INVENTION

Accordingly, it is an object of the invention to provide an AT interface architecture comprised of state machines such that the microprocessor is not involved in the transfer of data between the host and the buffer within the storage system.

Another object of the invention is to provide a Read State Machine, a Write State Machine, a Byte Count State Machine and an Update Task File State Machine which perform and control the transfer of data between the system and the host across the host interface.

Another object of the invention is the coaction between the Read State Machine, the Byte Count State Machine and the Update Task File State Machine for controlling the transfer of data during a READ operation, that is the transfer of data from the buffer within the storage system to the host.

Still another object of the invention is the coaction between the Write State Machine, the Byte Count State Machine and the Update Task File State Machine during a WRITE operation, that is the transfer of data from the host to the buffer within the storage system.

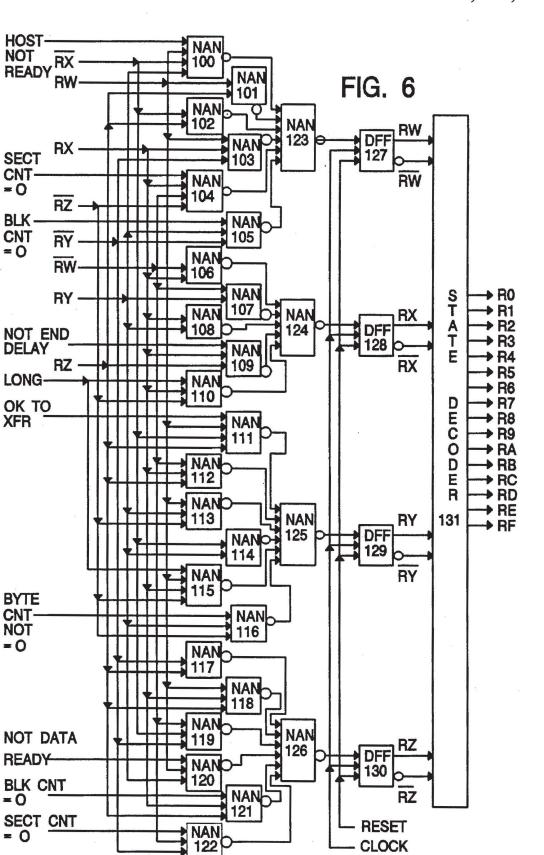

Briefly, there are four state machines in the AT interface architecture that are used to control the overall operation of data transfer to and from the host. A Write State Machine controls the overall operation of write commands, ie write sectors, write sector long, write multiple, write buffer, or write DMA. A Read State Machine controls the operation of the read commands, ie read sectors, read sector long, read multiple, read buffer, or read DMA. An Update Task File State Machine tracks the number of sectors processed and then generates; a signal to increment the sector address. A Byte Count State Machine controls the conversion of words to bytes and the transfer of data between the host and the 5 storage system.

The operation of the four state machines are intertwined. The Read and Write State Machines control the overall operation of the data transfer and are mutually exclusive. At the point of the transfer for either a READ or WRITE 10 operation where the task file needs to be updated, the Read or Write State Machine will initiate a cycle of the Update Task File State Machine. When either the Read or Write State Machines are started, the Byte Count State Machine is activated. The Byte Count State Machine generates pulses to 15 decrement the byte counter every time that a byte of data is transferred to or from the data register to control the transfer of data during a READ or WRITE operation. The Read and Write State Machines hold in their cycle awaiting for the byte count to go to zero as controlled by the Byte Count 20 State Machine. The Read State Machine issues a gate first word signal to tell the byte count machine to stage the first two bytes into the data register so that the first two bytes will be ready when the host starts reading data.

The state machines interact with the AT registers. The task file count register is used to keep the number of sectors transferred. The head and sector configuration registers are used to tell when the task file and sector registers should be wrapped. The byte count register, which is fed from the ECC 30 size register and the transfer size register, is used to count the number of bytes in the sector or the number of ECC bytes to be transferred. The block count register is loaded with a one for all but the read multiple command and for a read multiple command with the number of sectors to be trans-35 ferred in each block. The byte count register generates signals when the byte count register contains either a zero or a one.

An advantage of the AT interface employing state machines is that the microprocessor within the storage 40 system is relieved of the task of controlling the transfer of data to and from the host processor from the memory buffer within the storage system, thereby increasing system performance.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

The invention will be described with respect to the particular embodiments thereof and references will be made to the drawings, in which; 50

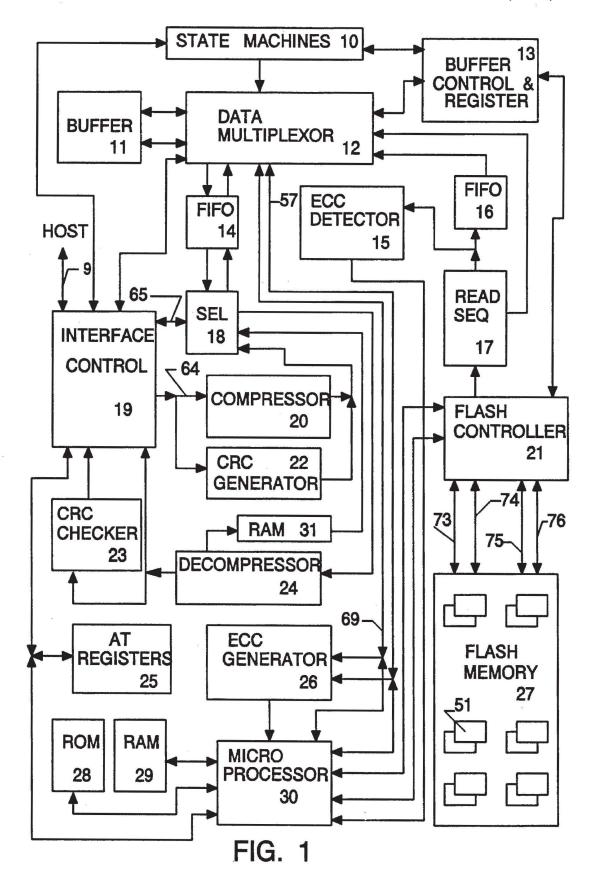

FIG. 1 is a logic diagram of the flash solid state drive;

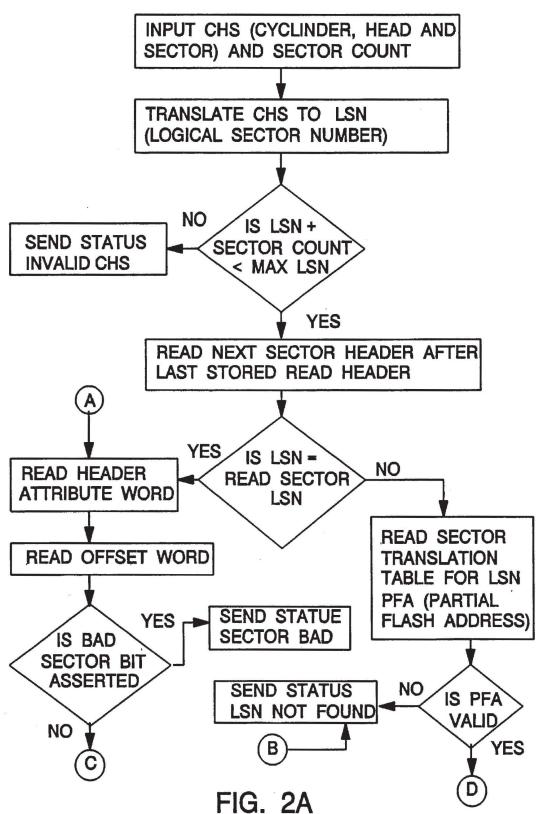

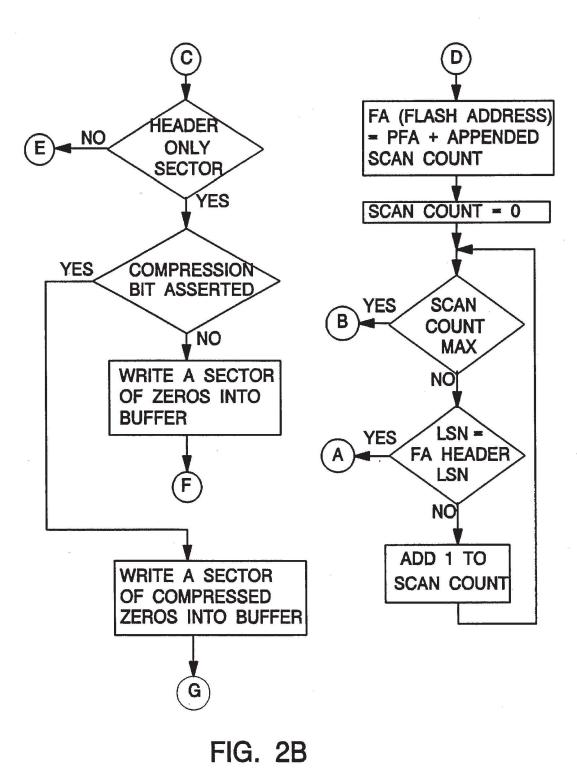

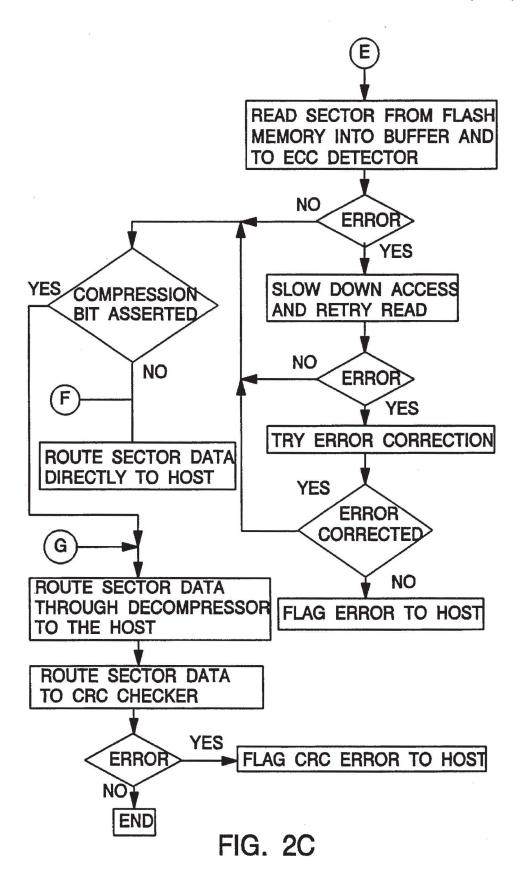

FIGS. 2A through 2C is a flow chart setting forth the operation of the flash solid state drive for a read operation;

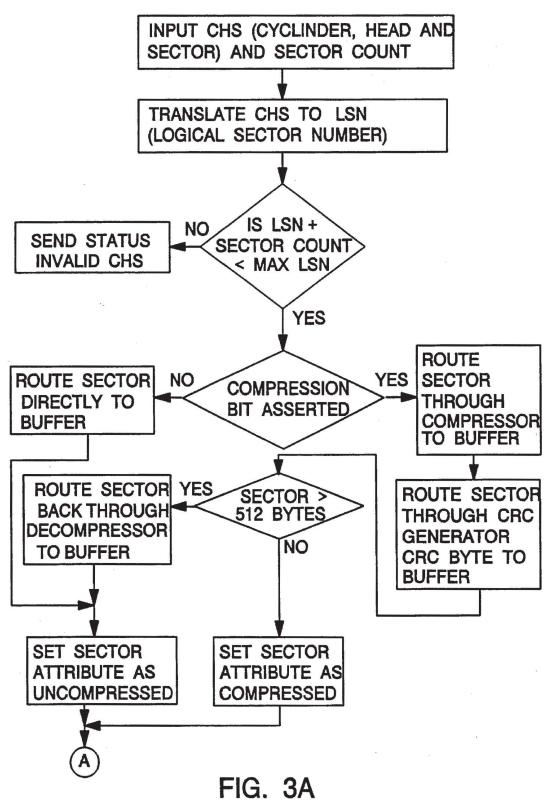

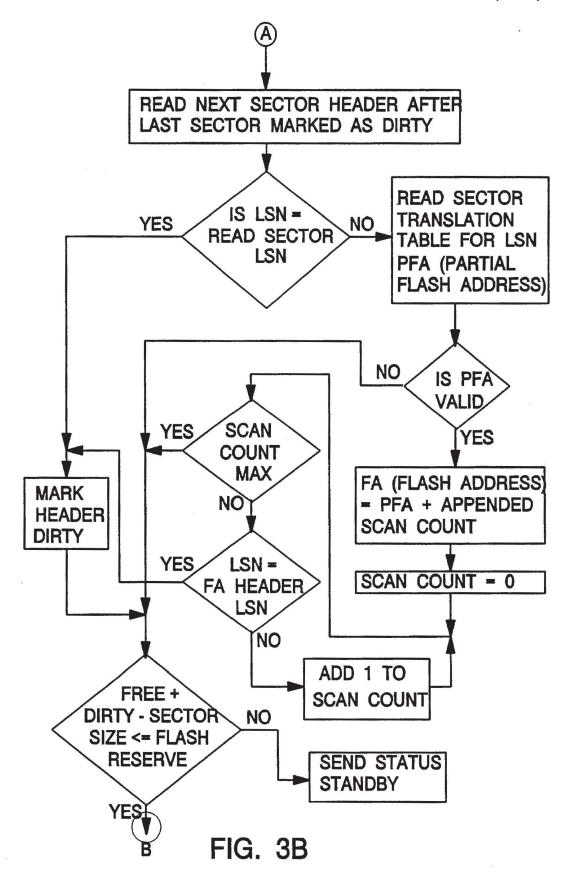

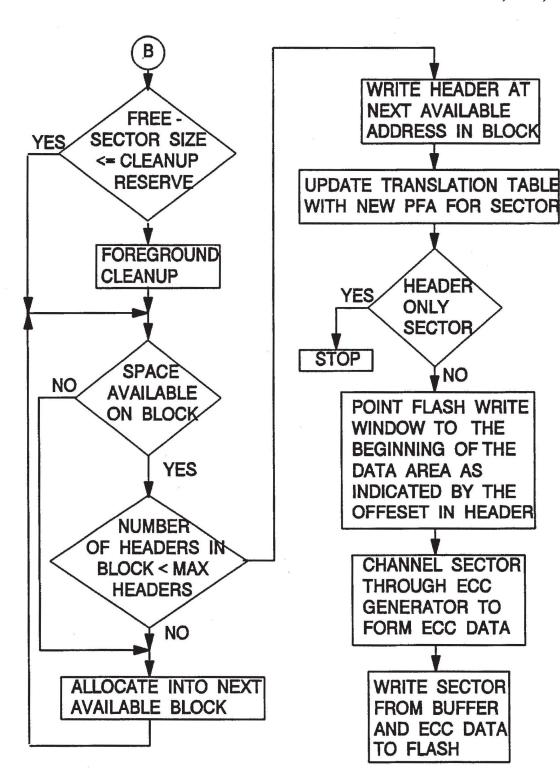

FIGS. 3A through 3C is a flow chart setting forth the operation of the flash solid state drive for a write operation; 55

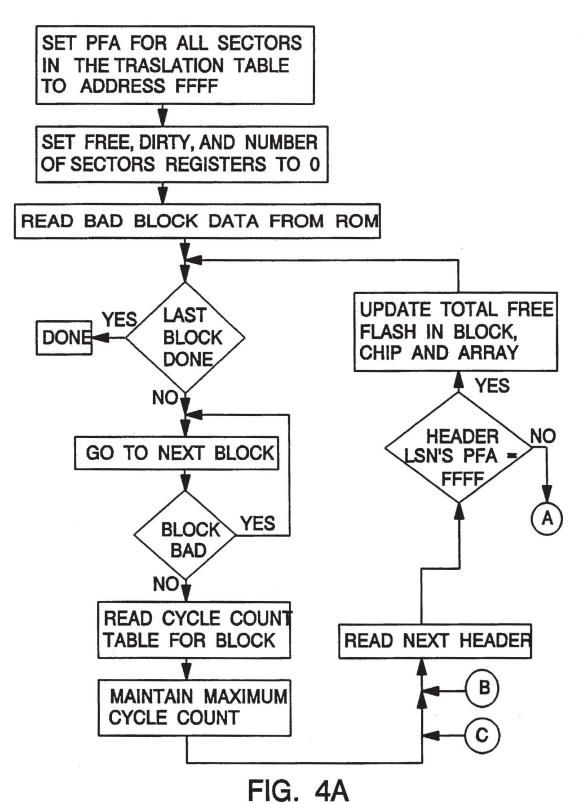

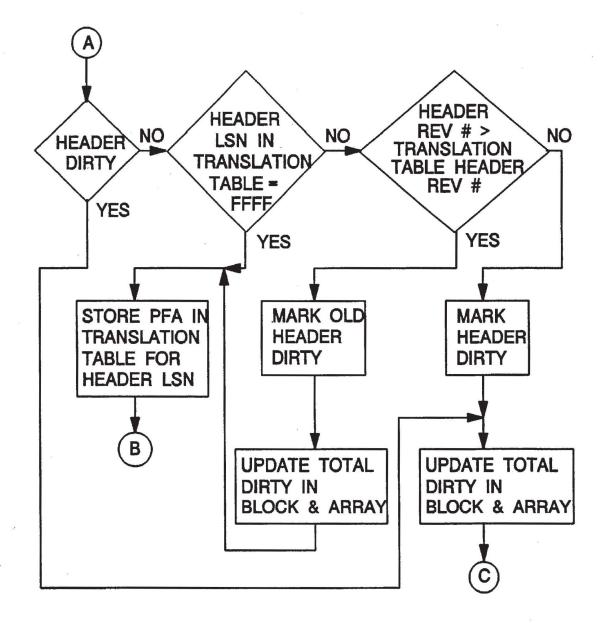

FIGS. 4A and 4B is a flow chart setting forth the operation of the flash solid state drive to initialize the sector translation table during the power up sequence;

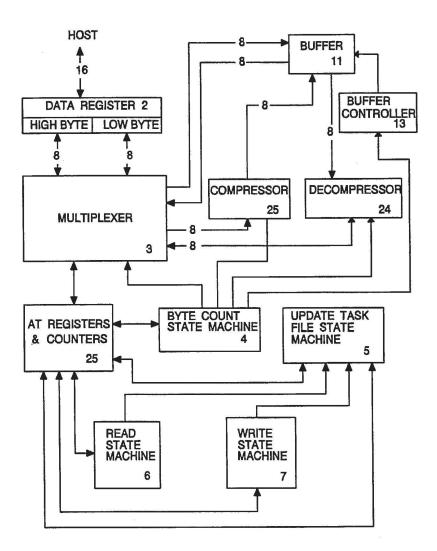

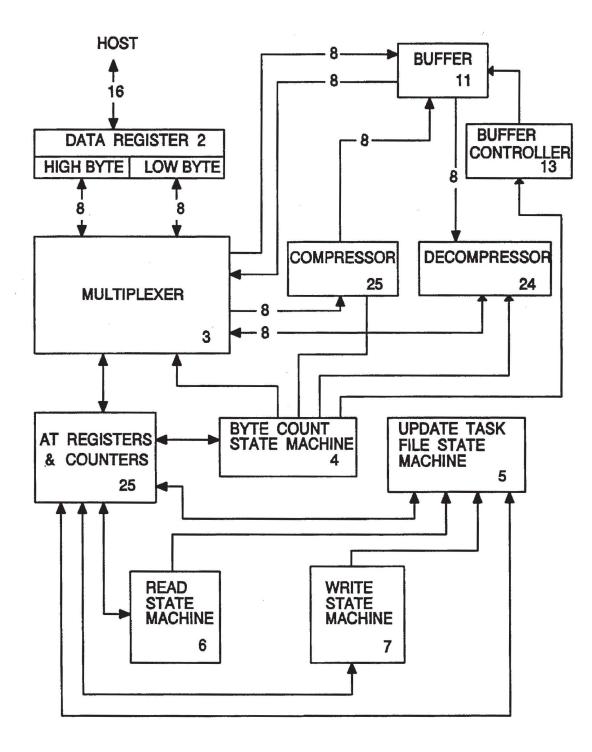

FIG. 5 is an overall logic diagram of the major components of the ATA interface including the four state machines. <sup>60</sup>

FIG. 6 is a logic diagram of the Read State Machine;

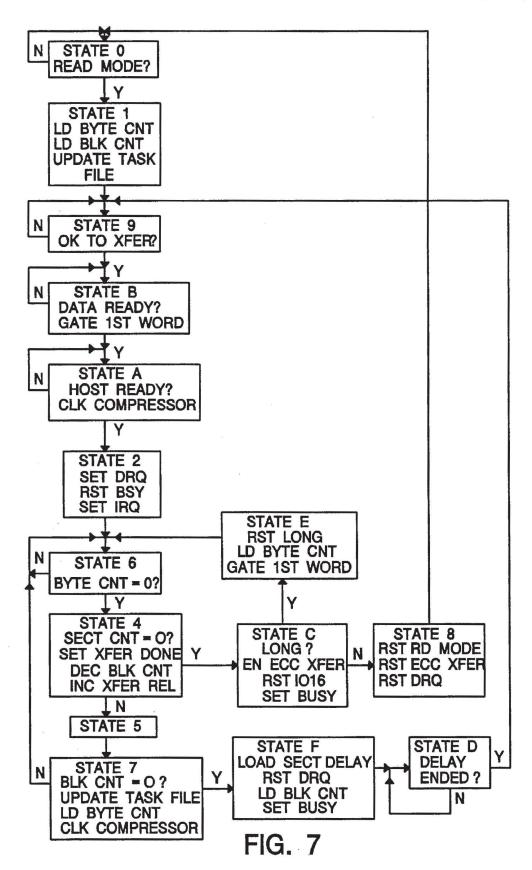

FIG. 7 is a flow chart of the operation of the Read State Machine:

FIG. 8 is a logic diagram of the Write State Machine;

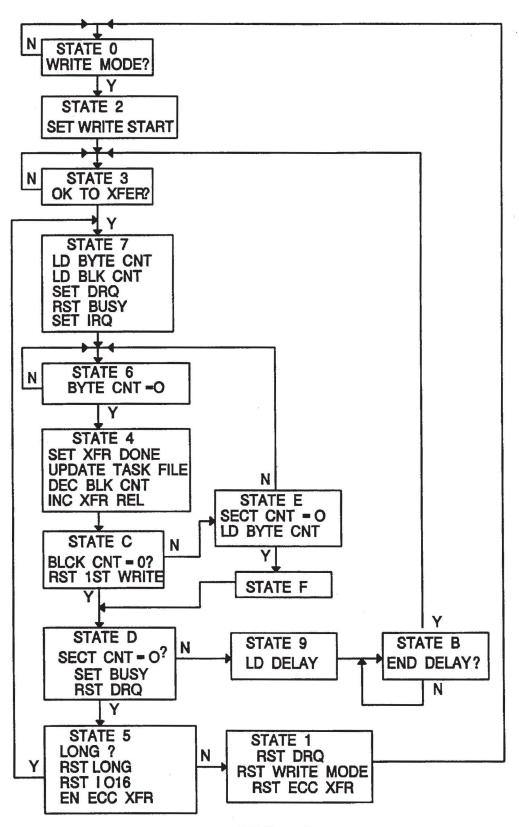

FIG. 9 is a flow chart of the operation of the Write State Machine;

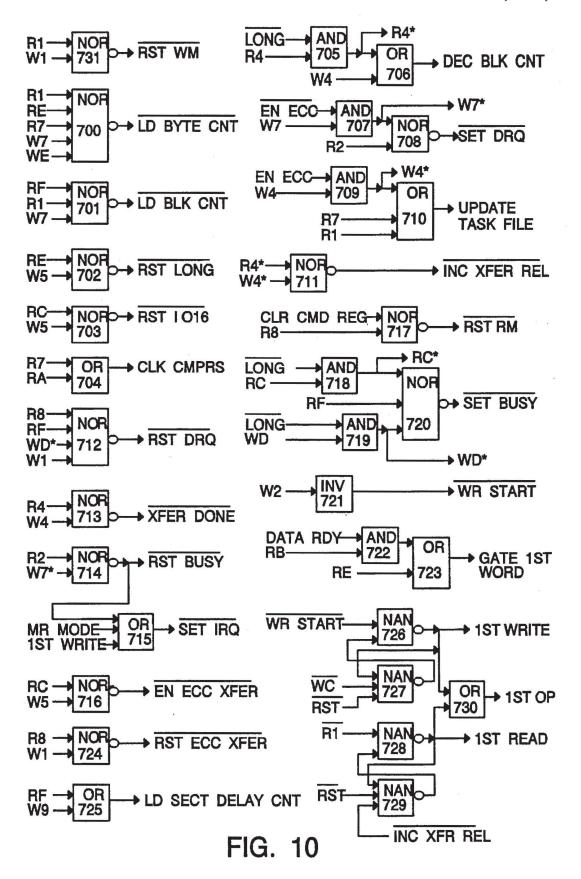

FIG. 10 is the control logic controlled by both the Read and Write State Machines for providing control signals to the storage system during a read and write operation and to the host processor during a read and write operation;

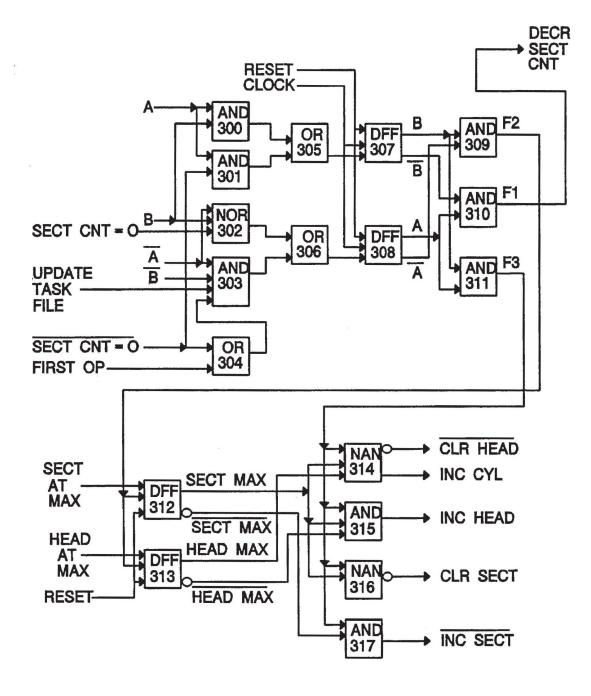

FIG. 11 is a logic diagram of the Update Task File State Machine:

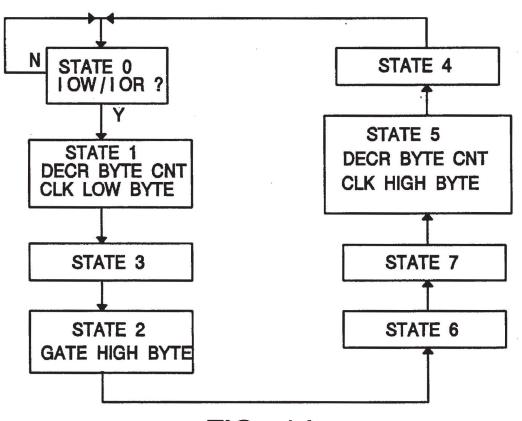

FIG. 12 is a logic diagram of the Byte Count State Machine:

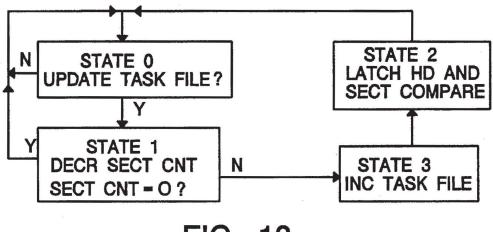

FIG. 13 is a flow chart of the operation of the Update Task File State Machine; and

FIG. 14 is a flow chart of the operation of the Byte Count State Machine.

## DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

## SYSTEM ARCHITECTURE

FIG. 1 is a logic diagram showing the components of the flash solid state drive. The flash solid state drive is 100% hardware and software compatible with ATA/IDE Interface standards and will support all mandatory AT-Attachment standard commands.

Flash memory 27 is comprised of thirty Intel 28F008 flash chips 51 where the chip data size is 8 Mb and 8 bits of data are simultaneously written into or read from the flash chip. Two flash chips are paired together and addressed at the same time such that 16 bits may be written or read simultaneously into or from the flash memory. To accomplish this flash controller 21 is dual ported so as to provide both address and data to each flash chip of a chip pair by means of lines 73 through 76. The flash solid state drive is controlled by microprocessor 30 in conjunction with an operating program stored in ROM 28. Microprocessor 30 is also connected to RAM 29 to allow the dynamic storing of data necessary for controlling the operation of the drive. Microprocessor 30 is connected to AT registers 25, to interface control circuitry 19, to flash control 21, to data multiplexer 12, to ECC generator 26, to buffer control and registers 13 and to ECC detector 15.

For a write operation, data for a sector is received from the host on bus 9 to interface control 19. If the sector data is to be compressed, the sector data is transferred via line 64 to 45 compressor 20 for data compression and through CRC generator 22 for generating CRC data. Data compressor 20 is a LEMPAL/ZIV type data compressor. The compressed sector data, after being compressed, is stored in buffer 11. After the compressed sector data has been stored in buffer 11 the CRC data byte is stored in buffer 11 and made part of the data associated with the sector being stored.

If the sector data was not to be compressed, then the sector data would leave interface control 19 on line 65 and pass directly through selector 18, FIFO 14 and data multiplexer 12 into buffer 11. State machines 10 contains a Write State Machine which controls the sequence of operations during a write operation. Once the data for the sector, either compressed or uncompressed, has been stored in buffer 11, the Write State Machine will then transfer the sector data from data multiplexer 12 to microprocessor 30. Microprocessor 30 acts as a dual port microprocessor where the ports are connected to data multiplexer 12 by means of buses 57 and 69. When sector data is transferred from buffer 11 to microprocessor 30 the sector data is also passed through ECC generator 26 to generate the ECC data. The ECC data is also provided to microprocessor 30. Microprocessor 30 transfers the sector data and ECC data as data words, where

each data word consists of two bytes of data to flash controller 21. Microprocessor 30 performs the task of taking two sequential bytes of sector data from buffer 11 or ECC data and forming data words for flash controller 21. Flash controller 21 then writes the data word into the flash memory 5 27.

During a read operation, the read command is received from the host on bus 9 by interface control 19. State machine 10 includes a Read State Machine which controls the sequence of operation during the read procedure. The data is 10read from flash memory 27 by flash controller 21 in data word format. Read sequencer 17 receives the data word and provides sequentially each of the two bytes of data making up the received data word to speed matching buffer FIFO 16. Read sequencer 17 also routes the data bytes to ECC 15 detector 15 for the detection of an error in the read data. The output of FIFO 16 is routed through multiplexer 12 to buffer 11. When the data for a sector has been stored in buffer 11 and no data error was detected by ECC detector 15, the sector data is then directed from buffer 11 through data 20 multiplexer 12 and speed matching buffer FIFO 14 to selector 18. If the sector data was compressed, then the sector data is routed from selector 18 through decompressor 24. The decompressed sector data from decompressor 24 is routed to CRC checker 23 and to interface control 19 for <sup>25</sup> transmission to the host. If CRC checker 23 detects a CRC error, a flag is raised to the host indicating that an error exists in the sector data that was transmitted for that sector. If the read sector data was not compressed, sclector 18 will route the sector data via line 65 to interface control 19 which will <sup>30</sup> then route the data to the host via bus 9.

State machines **10** also contains a between sector state machine for updating the task file registers and a Byte Count State Machine for maintaining of the number of bytes of data transfer during a read or write operation. 35

AT registers 25 and buffer control registers 13 are used to control the sequence of operation in conjunction with the microprocessor performing the operation program as stored in ROM 28 and the operation of the various state machines. Buffer control and registers 13 include a tie breaking state machine to resolve conflicts in the data multiplexer 12 for access to buffer 11 and a buffer signal state machine for controlling the reading and writing of data into and out of buffer 11.

The function of and description of the AT registers 25 and buffer registers 13 are as follows:

## AT REGISTERS

## 1. TASK FILE ERROR REGISTER

This register is the error indicating register to the Host. It has bit significance except at power on or during the diagnostic command. It is a read only register to the Host.

bit 7 - Bad Block

bit 6 - ECC Data Check

bit 4 - ID Not Found

bit 2 - Aborted Command

bit 1 - Track 0 Not Found

bit 0 - Address Mark Not Found

2. TASK FILE PRECOMP REGISTER

This register is a write only register to the Host. It was previously used to indicate at what cylinder to begin precompensation. It is used for other commands at this point in 65 time.

3. TASK FILE COUNT REGISTER

The register is used by the Host to indicate how many sectors are to be transferred on a read or write command. 4. TASK FILE SECTOR REGISTER

This register contains the logical sector requested by the host.

5. TASK FILE SDH REGISTER

bit 4 - Drive address

bit 3 - Head bit 8

bit 2 - Head bit 4

- bit 1 Head bit 2

- bit 0 Head bit 1

6. TASK FILE CYLINDER LOW REGISTER

This register and the following register contain the cylinder requested by the Host.

7. TASK FILE CYLINDER HIGH REGISTER

8. COMMAND REGISTER

This register is used by the Host to communicate the desired command. When either the Host or the drive write this register, the drive will become busy. When the drive is busy, only the drive may write the task file. When the drive is not busy, only the Host may write the Task File unless the drive writes **0D** bit **3** to enable the microprocessor access to the Task File registers.

9. SECTOR CONFIGURATION REGISTER

This is a 8 bit register used to determine the sector wrap point for the Host values.

10 HEAD CONFIGURATION REGISTERS

This is a 4 bit register used to determine the head wrap point for the Host values.

- bit 3 Head bit 8

- bit 2 Head bit 4

- bit 1 Head bit 2

- bit 0 Head bit 1

- 11. DIGITAL ADDRESS REGISTER

This register is the same as that read at 3F7 by the Host with the exception that bit 7 is a one instead of tristate as it is to the interface.

- bit 7 Always 1

- bit 6 Always 1

- bit 5 Head bit 3~

- bit 4 Head bit 2~

- bit 3 Head bit 1-

- bit 2 Head bit 0-

- bit 1 Drive 1~

- bit 0 Drive 0~

- 12. AT CONTROL REGISTER

This register contains status bits for use by the microcode. It is read only.

bit 7 - Sector>maximum logical sector

This bit contains the result of a comparison of the Task File Sector Number register and the Sector configuration register.

bit 6 - Head>maximum logical head

This bit contains the result of a comparison of the Task File SDH register head value and the Head configuration register.

bit 5 - Count equal to 0

This bit is 1 when the Task File Count Register is equal to 0.

bit 4 - ECC Error

This bit is 1 when an ECC error is detected. The ECC should be reset by toggling AT Res 1 in the Microprocessor's reset register before continuing.

50

55

20

25

30

50

55

60

bit 3 - Byte count equal to 0

This bit is one when the transfer count register that counts the number of bytes to be transferred on the interface is=0.

bit 2 - IOR & IOW equal to 0

This bit is for use in PCMCIA interfaces. It is 1 when both IOR & IOW are active low at the same time.

bit 1 - Task file update state 1

This bit and bit **0** contain the status of the task file update state machine. It is triggered by the read or write state <sup>10</sup> machines and normally should not be able to be seen changing. It should always be in state 00.

bit 0 - Task file update state 0

13. TASK FILE STATUS REGISTER

This register which is a read/write register used to access <sup>15</sup> the Task File register which provides a summary status of the drive. All bits are read/write.

bit 7 - Busy

bit 6 - Ready

bit 5 - Write Fault

bit 4 - Seck Complete

bit 3 - Data Request

bit 2 - Corrected data

bit 1 - Index

bit 0 - Error bit

14. INTERFACE CONTROL REGISTER

bit 7 - Host PDIAG Out

This bit, when set to 1, drives the Host PDIAG signal active low. It is bit settable.

bit 6 - LED/Drive Slave Present

This bit, when set to 0, drives the DASP signal low to the interface.

bit 5 - Processor Host Interrupt Enable

This bit may be set to 1 to force the Host interrupt to be 35 enabled. It should be reset to allow the Host to enable or disable the drive's interrupt.

bit 4 - OK to continue

This bit is used by the processor to allow a multiple sector read or write to continue. Normally it should be set to <sup>40</sup> I at initialization. If sector automation is to be inhibited, this bit should be set to zero. Then, between sectors, the bit pulse, CONTINUE R/W 0E, bit 3, is pulsed to continue the R/W.

bit  $\mathbf{3}$  - Enable microprocessor access to the Task File  $^{45}$  Registers.

This bit is used by the processor to enable it to access the Task File even when the drive is not busy. Normally, this bit is not ever used.

bit 2 - INDEX.

This bit is routed to the status register to simulate the index of a drive. For the flash drive it should not be needed.

bit 1 - C~/D.

The address bit of the drive. Is set to 0 for drive C or 0 and to 1 for drive 1 or D. This bit is used to route status and is compared to the bit in the SDH register to determine the addressed drive.

bit 0 - Slave Present.

This bit is used to indicate that a second drive is present. It is set during a reset sequence when dual drive is detected. It is used to route status because if the second drive is not present, the master drive, drive **0**, is responsible to return 00 for status. Setting this bit 65 allows the hardware to return this status.

15. BIT PULSES REGISTER

This register is setup to allow bit operations to be done. When it is read, it always returns FFh. To pulse any of these bits, a zero is written.

bit 7 - Set Host IRQ.

This bit sets the Host interrupt which is gated by the Host interrupt enable.

bit 6 - Reset Long.

This reset is used to reset the Long bit, set by the Host when it does either a read or write long.

bit 5 - Reset Read/Write Mode.

This bit resets both read and write modes and the Data Request bit.

bit 4 - Set Read Mode.

This bit sets read mode. It is the only bit required to kick off a read operation if all other initialization has been accomplished.

bit 3 - Continue R/W.

This bit is used when the sector automation is disabled, register **0D** bit **4** set to 0. to allow the next sector to begin.

bit 2 - Increment Block Release

This is the drive side pulse used to increment the Sectors Available Register 40 on a read and to decrement it on a write.

bit 1 - Increment Transfer Release.

- This is the Host side pulse used to decrement the Sectors Available Register 40 on a read and to increment it on a write.

- bit 0 Set Write Mode.

Used to set Write Mode. This bit is used by the microprocessor to start any non-autowrite write operation. 16. INTERFACE BITS REGISTER

This is a collection of bits that are useful for interface operation.

bit 7 - Host IRQ.

This is the Host IRQ bit just before it goes to the output drivers.

bit 6 - Host Interrupt Enable.

This is the Host Interrupt Enable bit just before it goes to the output drivers.

bit 5 - Host PDIAG In.

This bit comes from the PDIAG line just on the input side of the Host input receivers.

bit 4 - Long

This bit is the long bit set by the Host when it does either a read or write long operation.

bit 3 - HIO16

This is the HIO16 line just before it goes to the Host interface.

bit 2 - Write Mode

The Write mode latch.

bit 1 - Read Mode

The Read Mode latch.

bit 0 - Drive Slave Present In.

The drive slave present line at the input receiver lines. 17. ECC 1 GENERATION 4

This register and the following three registers are the registers where the ECC Generator 1 result is stored. To produce the correct ECC value, the registers should be initialized to F0, 0F, 00, FF respectively before the data is read by the microprocessor from Port 1 of the Buffer. It is possible to interrupt the ECC generation by saving away the current contents of the registers and then restoring them to continue.

25

30

35

45

18. ECC 1 GENERATION 3 19. ECC 1 GENERATION 2

20. ECC 1 GENERATION 1

21, ECC 2 GENERATION 4

This register and the following three registers are the 5 registers where the ECC Generator 2 result is stored. To produce the correct ECC value, the registers should be initialized to F0, 0F, 00, FF respectively before the data is read by the microprocessor from Port 1 of the Buffer. It is possible to interrupt the ECC generation by saving away the 10 current contents of the registers and then restoring them to continue.

22. ECC 2 GENERATION 3

23. ECC 2 GENERATION 2

24. ECC 2 GENERATION 1

25. ECC DETECTION 4

The ECC Detection automatically loads the polynomial into this register and the following 3 registers and then calculates the ECC on the read data. The hardware then automatically triggers the compare on the ECC bytes read at 20 the end of the sector.

26. ECC DETECTION 3

27. ECC DETECTION 2

28. ECC DETECTION 1

29. TRANSFER LENGTH LOW REGISTER

This register and the following one, control the length of each sector transfer. It is normally set only at power on time. This register is used to measure the length of the sector transfer.

**30. TRANSFER LENGTH HIGH REGISTER**

31. 22 - BIT PULSES 2

This register is setup to allow bit operations to be done. When it is read, it always returns FFh. To pulse any of these bits, a zero is written.

bit 7 - Last Transfer.

This bit is used to force the AT automation to end the transfer at the end of the current sector or block.

bit 6 - Start Compressor.

This bit provides the capability to start the compressor in the non-autowrite case. One of its principle other uses 40 will be to start the compressor to rewrite a sector that has expanded back to the buffer as a non-compressed sector.

32. AT DATA 1 REGISTER

bit 7 - Disable compression

This bit disables the compression circuitry when set. When compression is disabled, a sectors are transferred as 512 byte sectors.

bit 6 - PIO Mode

When this bit is set, Host data transfers are done in PIO mode. This bit enables the IO16 circuitry when set. bit 5 - EISA DMA Mode

This bit enables EISA DMA Mode. It controls how the Host Interface to drive handshaking is done on read and 55 write DMA commands. When this bit is set DMA transfers are accomplished with Host DMA Request and Host DMA Acknowledge remaining active for the entire transfer although the Host will drop Host DMA Acknowledge when it does a refresh cycle. 60

bit 4 - ISA DMA Mode

This bit enables ISA DMA Mode. It controls how the Host Interface to drive handshaking is done on read and write DMA commands. When this bit is set DMA transfers are accomplished with Host DMA Request 65 and Host DMA Acknowledge toggling on every word transfer.

10

bit 3 - Multiple Mode

This bit is set when the Host issues a Set Multiple Command, C6h. It enables multiple operations in the ASIC hardware.

bit 2 - Host DMA Enable

This bit is only used by the microprocessor when connected to a Compaq computer that requires this signal to initiate a DMA read/write transfer.

bit 1 - Disable Autowrites

When set this bit, autowrites are disabled. Disabling autowrites requires that the microprocessor set Write Mode, by clearing register 0E, bit 4.

bit 0 - Disable CRC

When set this bit disables the CRC check. It also disables writing the CRC bit.

33. CRC REGISTER

This register contains the CRC byte. It is valid at the end of a sector until the start of the next sector.

34. BLOCK SIZE REGISTER

This register contains the number of sectors in a block on a read/write multiple. It is set by the microprocessor when the Host issues a C6h, Set Multiple Command. It is used by the AT ASIC circuitry to control the number of sectors to be transferred under a single DRQ.

35. ECC LENGTH REGISTER

This register controls the length of the transfer of the ECC bytes during a long read or write command. It is usually only set during reset, but may also be modified by the Host, Set ECC Length. This register is used by the AT circuitry of the ASIC.

#### **36. BYTE COUNT LOW REGISTER**

This register and the following register are the actual transfer length registers. They are loaded by the AT circuitry of the ASIC with either the contents of Transfer Length Register or the ECC Length Register dependent upon if the data or the ECC bytes are being transferred.

**37. BYTE COUNT HIGH REGISTER**

38. BLOCK COUNT REGISTER

This register is used in read or write operations and is loaded with either I if the operation is to be a normal read or write command, the block size register for a read or write multiple command where the remaining sectors to be transferred is greater than the block size, or the Task File Count for a read or write multiple operation where the number of sectors remaining to be transferred is less than the block size.

## 39. READ WRITE STATES REGISTER

This register contains the current state of both the read and write state machines that are used to control any read or write operation to or from the host. The upper nibble contains the write states and the lower nibble contains the read states.

bit 7 - Wa bit 6 - Wb bit 5 - Wc bit 4 - Wd

bit 3 - Rw

bit 2 - Rx

bit 1 - Ry

bit 0 - Rz

40. SECTORS AVAILABLE REGISTER

This register maintains a count of the number of sectors available to the Host on a read operation and the number of sectors available to the drive on a write operation. It may be loaded by the microprocessor. It is reset on an autowrite

t5

25

35

unless they are disabled.

41. SEGMENT SIZE REGISTER

This register contains the current size of the buffer segment. It is set by the microprocessor. It is used by the AT circuitry in the ASIC to determine if there is any additional 5 room in the segment to place data.

11

42. BETWEEN SECTOR DELAY REGISTER

This register is used to control the amount of delay, in 400 ns increments, between sectors on multiple block read and write operations.

## BUFFER REGISTERS

## 1. START POINTER LOW BYTE 1

This and the next register makes up the start pointer to the ram buffer for the first port of the microprocessor. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12-15 are bounded by the buffer size register so that the start pointer will only contain valid 20 addresses for the buffer size selected. This register is loaded into the microprocessor #1 address registers when the address pointer equals the microprocessor wrap pointer.

2. START POINTER HIGH BYTE 1

3. WRAP POINTER LOW BYTE 1

This and the next register are the wrap pointer to the ram buffer for the first port of the microprocessor. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12-15 are bounded by the buffer size register so that the wrap pointer will only contain valid 30 addresses for the buffer size selected. This register is loaded with the address that the programmer wants to cause a wrap condition on.

4. WRAP POINTER HIGH BYTE 1

5. ADDRESS POINTER LOW BYTE 1

This and the next register makes up the address pointer to the ram buffer for the first port of the microprocessor. This pointer is incremented to the next address upon each access to the ram. It is reset to 00000h on the assertion of sector 40 reset buffer 1. This register's upper address bits 12-15 are bounded by the buffer size register so that the address pointer will only contain valid addresses for the buffer size selected. The microprocessor #1 start and wrap pointers can be used to select a wrap point inside the ram buffer. When 45 the address pointer equals the wrap pointer the Start pointer is loaded for the next ram access.

6. ADDRESS POINTER HIGH BYTE 1

7. BUFFER CONTROL 1

This register contains the controls and status of port 1 of 50the microprocessor.

bit 7 - U1PROG $\sim$ (R)

Progress bit. Bit7=0 then the data in the data register is not valid yet. Bit7=1 Data is valid in the data register. 55

bit 2 - ECC ENABLE

- This bit when set will cause the data being read from this port to be clocked into the ecc generator. If the bit is clear data will not be clocked into the ecc generator. bit 1 - U1STRT (W/R)

- Port activation bit. Bit 1=0. Any read or writes to the data register will cause no action to be taken. Bit 1=1. If bit 0=0 and the data register is written data will be transferred to the ram. If bit 0=1 then an immediate fetch of the first byte will be performed and there after a new 65 byte will be fetched upon reading the data register.

bit 0 - U1DIRW~/R (W/R)

The direction of the port. Bit **0**=0 a write is performed to the ram. Bit 0=1 a read is performed.

8. DATA REGISTER

This is the data register for first microprocessor port. If microprocessor port #1 is active then a read of this register will pass data read from the ram and start off another fetch operation to the ram. A write to this register will place the written data into the ram.

9. START POINTER LOW BYTE 2

This and the next register makes up the start pointer to the ram buffer for the first port of the microprocessor. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12-15 are bounded by the buffer size register so that the start pointer will only contain valid addresses for the buffer size selected. This register is loaded into the microprocessor #1 address registers when the address pointer equals the microprocessor wrap pointer.

10. START POINTER HIGH BYTE 2

11. WRAP POINTER LOW BYTE 2

This and the next register makes up the wrap pointer to the ram buffer for the first port of the microprocessor. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12-15 are bounded by the buffer size register so that the wrap pointer will only contain valid addresses for the buffer size selected. This register is loaded with the address that the programmer wants to cause a wrap condition on.

12. WRAP POINTER HIGH BYTE 2

13. ADDRESS POINTER LOW BYTE 2

This and the next register makes up the address pointer to the ram buffer for the first port of the microprocessor. This pointer is incremented to the next address upon each access to the ram. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12-15 are bounded by the buffer size register so that the address pointer will only contain valid addresses for the buffer size selected. The microprocessor #1 start and wrap pointers can be used to select a wrap point inside the ram buffer. When the address pointer equals the wrap pointer the Start pointer is loaded for the next ram access.

14. ADDRESS POINTER HIGH BYTE 2

15. BUFFER CONTROL 2

This register contains the controls and status of port 2 of the microprocessor.

bit 7 - U1PROG~ (R)

Progress bit. Bit7=0 then the data in data register is not valid yet. Bit 7=1 Data is valid in data register.

bit 2 - ECC ENABLE

This bit when set will cause the data being read from this port to be clocked into the ecc generator. If the bit is clear data will not be clocked into the ecc generator.

bit 1 - U1STRT (W/R)

Port activation bit. Bit 1=0. Any read or writes to the data register will cause no action to be taken. Bit 1=1. If bit 0=0 and the data register is written data will be transferred to the ram. If bit 0=1 then an immediate fetch of the first byte will be performed and there after a new byte will be fetched upon reading the data register. bit 0 - U1DIRW~/R (W/R)

The direction of the port. Bit 0=0 a write is performed to

the ram. Bit 0=1 a read is performed. 16. DATA REGISTER 2

This is the data register for second microprocessor port. If microprocessor port #2 is active then a read of this register will pass data read from the ram and start off another fetch operation to the ram. A write to this register will place the written data into the ram.

20

40

## 17. INTERFACE START POINTER LOW WORD

This and the next register makes up the start pointer to the ram buffer for the interface port. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12–15 are bounded by the buffer size register so 5 that the start pointer will only contain valid addresses for the buffer size selected. This register will be loaded into the interface address pointer upon a successful compare of the interface address pointer with the interface wrap pointer.

19. INTERFACE START POINTER HIGH WORD

20. INTERFACE WRAP POINTER LOW WORD

This and the next register makes up the wrap pointer to the ram buffer for the interface. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12–15 are bounded by the buffer size register so 15 that the wrap pointer will only contain valid addresses for the buffer size selected. This register is loaded with the address that the programmer wants to cause a wrap condition on.

21. INTERFACE WRAP POINTER HIGH WORD

22. INTERFACE ADDRESS POINTER LOW WORD

This and the next register makes up the address pointer to the ram buffer for the interface. This pointer is incremented to the next address upon each access to the ram. It is reset to 00000 on the assertion of sector reset buffer 1 or upon  $_{25}$ receiving an autowrite pulse. This register's upper address bits 12-15 are bounded by the buffer size register so that the address pointer will only contain valid addresses for the buffer size selected. The interface start and wrap pointers can be used to select a wrap point inside the ram buffer. 30 When the address pointer equals the wrap pointer the Start pointer is loaded for the next ram access. This loading of the address pointer to 00000 by receiving an autowrite can be disabled by setting bit2 of the interface buffer control register. 35

23. INTERFACE ADDRESS POINTER HIGH WORD 24. INTERFACE BUFFER CONTROL

This register contains the controls and status of the interface buffer port.

Bit 7 - IFPROG~ (R)

- Interface access to ram. Bit 7=0 when an access to the buffer ram is in progress. Bit 7=1 when interface port is idle.

- Bit 6 FIFO FULL (R)

- Bit **6**=0 When there is room in the sector count FIFO for 45 releases. Bit **6**=1 When the sector count FIFO is full and can not accept any more entries.

Bit 5 - FIFO EMPTY (R)

- Bit 5=1 when the sector count FIFO is empty. Bit 5=0 when there is data in the sector count FIFO 50

- Bit 4 RESET FIFO

- Bit 4=1 then the sector count FIFO is held in reset. Bit4=0 the sector count FIFO is free to be loaded.

Bit 2 - AUTOWRITE~ (W/R)

- Autowrite load of start pointer. Bit2=0 will cause the start pointer to be loaded into the address pointer if an autowrite is received Bit2=1 will inhibit the load of the start pointer into the address pointer on autowrites. Bit 1- IFACT (R)

- Interface port active. Bit 1=0 the interface port is not active. Bit 1=1 means the interface port is active. Bit 0- IFDIRW-/R (R)

- Interface direction. Bit 0=0 the data is flowing from the interface to the buffer. Bit 0=1 the data is flowing from 65 the buffer to the interface. This bit is only valid if Bit 1=1.

## 14

25. SECTOR COUNT LOW

This and the next register forms the sector count register port. The nine bits contain the number of bytes in the sector that is being released. This register is a port to a 16 word×10 bit FIFO. Sixteen sector counts can be stored up at a time. Bit 6 of register 24 returns the status of whether this FIFO is full. Both bytes must be written to load the 10-bit word in the FIFO. Bit 2 of the sector count high register is used to tell whether the sector that corresponds to this count is compressed or uncompressed. You set the bit to 1 for compressed data. Bits 11–15 are ignored but should be written as zero. The FIFO is reset and count purged if sector reset buffer 1 is asserted or if the interface deasserts its read\_mode.

26. SECTOR COUNTER HIGH

27. READ SEQ START POINTER LOW WORD

This and the next register makes up the start pointer to the ram buffer for the read sequencer port. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12–15 are bounded by the buffer size register so that the start pointer will only contain valid addresses for the buffer size selected. This register is loaded into the read sequencer address pointer upon a successful compare of the read sequencer address pointer to the read sequencer wrap pointer.

28. READ SEQ START POINTER HIGH WORD 29. READ SEQ WRAP POINTER LOW WORD

This and the next register makes up the wrap pointer to the ram buffer for the read sequencer. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits 12–15 are bounded by the buffer size register so that the wrap pointer will only contain valid addresses for the buffer size selected. This register is loaded with the address that the programmer wants to cause a wrap condition on.

30. READ SEQ WRAP POINTER HIGH WORD 31. READ SEQ ADDRESS POINTER LOW WORD

This and the next register makes up the address pointer to the ram buffer for the read sequencer port. This pointer is incremented to the next address upon each access to the ram. It is reset to 00000 on the assertion of sector reset buffer 1. This register's upper address bits **12–15** are bounded by the buffer size register so that the address pointer will only contain valid addresses for the buffer size selected. The read sequencer start and wrap pointers can be used to select a wrap point inside the ram buffer. When the address pointer equals the wrap pointer the Start pointer is loaded for the next ram access.

32. READ SEQ ADDRESS POINTER HIGH WORD 33. READ SEQ CONTROL

Bit 7 - RSPROG~ (R)

Read sequencer ram access. Bit 7=0 the read sequencer is accessing the ram. Bit 7=1 the read sequencer is idle. Bit 1 - RSACT~ (R)

Read sequencer active. Bit1=0 means there is data in the read sequencer FIFO. Bit 1=1 means there is no data in the read sequencer FIFO.

Bit 0 - RSDIRW - /R(R)

Read sequencer active. Bit **0** will always equal 0. Since the Read sequencer only writes to the buffer ram.

34. BUFFER CONTROL REGISTER

Bit 7 - ADDRESS HIGH-/BCS1 (W/R)

Address or buffer chip select. Bit7=0 the address high will be sent to the buffer ram. Bit 7=1 then BCS1 will be sent to the buffer ram in place of the high address.

35. BUFFER SIZE REGISTER

This register selects the size ram buffer the chip will

10

01 - 8K BUFFER

access.

03 - 16K BUFFER

07 - 32K BUFFER

0F - 64K BUFFER

**36. BUFFER COUNT REGISTER**

This register contains the number of clock periods minus 1 that will be used to access the buffer ram. Only bits 0-3 are used.

15

## SYSTEM OPERATION

The flash solid state drive operates under an operating system stored in ROM 28. The flash solid state drive 15 performs various prodedures under the joint control of the operating system and the various state machines.

FIGS. 2A. 2B and 2C set forth the operation of the flash solid state drive for a read operation. The host sends to the flash solid state drive the read command, the sector count 20 (the number of sectors to be read) and the cylinder, head and sector numbers (CHS address). Upon receiving the CHS address, the flash solid state drive will translate that CHS address into a logical sector number (LSN). Each sector that would have existed on the magnetic disk drive will have an <sup>25</sup> associated LSN in the flash solid state drive. Therefore for the emulation of any magnetic disk drive, the flash solid state drive will have a maximum number of LSNs.

A test is performed which adds the received sector count 30 to the generated LSN and compares that summation to the maximum LSN for the flash solid state drive. If the resulting summation is greater than the maximum LSN or if the generated LSN was equal to zero, then the CHS address sent by the host was in error. Under this condition the flash solid 35 state drive will send status of invalid CHS to the host.

Each LSN has a header stored in the flash memory which identifies and describes the sector to the drive. When the drive is first manufactured, a sector header for each LSN is written in the flash array. A header for each LSN will always 40 exists in the flash array and it is possible for more than one header for a given LSN to exist in the flash array however only one such header will be mark clean and the remaining duplicate headers will be marked dirty or invalid. During operation, the drive will store the location of the header of 45 the last LSN read.

If the CHS sent by the host was valid, the drive will read the next header in the flash array after the sector header who's location in the flash memory was stored during the last read operation. The stored sector header location allows 50 the drive to calculate the flash array address for the next header. Effectively, if the LSN stored in the next header is the LSN for the LSN to be read then the drive has avoided the time necessary to seek a flash memory address for the LSN.

Therefore a test is done to compare the LSN generated for this read operation against the LSN read from the next sector header after the last stored sector header during the last read operation. If there is no match, the drive will go to a sector translation table and read a partial flash address PFA for the 60 LSN. The sector translation tables has stored for each LSN a PFA. The low three order bits of the complete flash address FA are not included within the PFA thereby reducing the width of the sector translation table by one byte. In the preferred embodiment the largest PFA stored in the sector 65 translation table is address FFFE. The PFA for the LSN is checked to determine if the PFA has a value of FFFF which

would indicate an error condition. If an error condition is sensed, status is sent to the host indicating that the CHS address was not found.

If the PFA is valid, the drive will add the value of a scan count multiplied by the header size to the PFA to form the FA. A scan count register is maintained within the drive for generating the complete offset for the FA. At this time, the scan count register will be made to be equal to zero. The scan count is then determined by the drive and if the scan count has a value of 0 to 7, the drive will read the header located at the FA and determine if the LSN being sought is equal to the LSN stored in the sector header. If the LSN being sought is different than the LSN stored in the header, 1 is added to the scan count and the process is repeated. This loop will be repeated until either the scan count reaches a count of 8 which will cause the drive to send status of CHS not found to the host or a match has been obtained between the LSN being sought and the LSN stored in the header being read at the flash address.

When either the condition that the LSN being sought was equal to the LSN stored in the next sector header after the last header stored from the previous read operation or the LSN in the header of the sector addressed in the flash memory, the drive will read the header. The header includes an attribute word and an offset word. The attribute word contains a bit that is set if the host has indicated that the sector was bad. If the bad sector bit is asserted, the drive will send status to the host indicating that the sector is marked bad. The offset word indicates the location of the data stored for that sector. If the attribute word indicates zero bytes of data, the drive will determine from the attribute word if the attribute word's compression bit is asserted. The compression bit indicates whether or not the sector data was compressed during the writing operation for storing that sector. If the compression bit was asserted, the drive will write a sector of compressed zero bytes into the buffer. If the compression bit was not asserted, the drive will write a sector, 512 bytes, of zeroes into the buffer. Since no data was stored within the flash memory, the drive generates the proper bytes of data to be stored into the buffer.

Where the attribute word indicates that data is stored after the header, the drive will read as data words from the flash memory the sector data, the CRC data, if any, and the ECC date. The offset word indicates the address at which the data is stored. As previously described, the flash memory is so arranged as to have the flash chips paired together such that 16 bits or two bytes of data may be read from the flash memory at a time. The offset provides the address at which the data starts in both of the flash chips. Data is stored on the flash chips starting at the address indicated by the offset and subsequent data words are read by incrementing the flash address for the first data word until all the data words are read for the sector. The data words are converted into two sequential bytes of data by the read sequencer 17 and each byte of sector data is read through multiplexer 12 into buffer 11. The bytes are routed through the ECC detector 15 and if an error is detected, the drive will slow down the access time to allow more settling time for the flash memory and retry reading the sector. If the retry was not successful, error correction techniques are then attempted to correct the error. If the error was not corrected, a flag is set indicating the error for the host.

If there was no error or if an error is corrected, then the drive will again determine whether the compression bit in the header was asserted. If the compression bit was not asserted, the buffer will contain 512 bytes of data and 4 bytes of ECC data. The drive will then route the uncompressed

sector data through the data multiplexer 12, FIFO 14, selector 18 and interface control 19 to the host. If the compression data bit was asserted, the buffer will contain either the compressed data for the sector or a compressed sector of zeros, a CRC byte and 8 bytes of ECC data. The 5 drive will route the compressed data from buffer 11 through data multiplexer 12, FIFO 14 and selector 18 to decompressor 24. Decompressor 24 decompresses the data and provides 512 bytes of data to interface control 19 to be transferred to the host. The output of the decompressor 24 is 10 also sent through the CRC checker 23 which will determine if the decompressed data contains an error. If an error is detected by the CRC checker, a flag CRC error is posted to the host to indicate that the sector data just received by the host contains an error. The use of the CRC checker allows the drive to identify an error most likely occurring during 15 either the compression or decompression of the sector data.

FIGS. 3A-3C describe the flash solid state drive operation for a write operation. The host issues a write instruction, the CHS address and a sector count of the number of sectors to be written. Again, the drive will translate the CHS address into a LSN. The LSN is then tested to see if the LSN is a valid LSN and, if not, sends an ID not found status to the host. The drive contains a register which has a bit assigned to it for indicating whether the data is to be compressed during a write instruction or has been compressed for a read<sup>25</sup> instruction. The host processor can set this bit for a write operation and the drive sets the bit during a read operation. If the compression bit is not asserted, the 512 bytes are routed through interface control 19, selector 18, FIFO 14 and data multiplexer 12 into buffer 11. No CRC data is <sup>30</sup> generated for this sector since it was not passed through compressor 20.

Whenever a sector is written into the flash memory, a new header is written for that sector. Therefore the compression 35 bit in the attribute word of the sector header is set to indicate the sector data is uncompressed. If the compression bit is asserted, the incoming sector data is routed through interface control 19 to compressor 20 and CRC generator 22. Compressor 20 is a LEMPEL/ZIV data compressor. The com- 40 pressor operates on 512 byte sectors and achieves an average compression ratio of approximately 1.6 to 1. The uncompressed data is passed through CRC generator 22 to form one byte of CRC data which is appended to the compressed data bytes from compressor 20. After compression is com- 45 pleted by compressor 20, a test is made as to the number bytes generated by the compression operation. In some circumstances it is possible for the number of compressed data bytes to be greater than the 512 bytes of original data. If the number of compressed bytes is equal to or less than 50 512 bytes, the drive will route the compressed data and the appended CRC byte through selector 18, FIFO 14, data multiplexer 12 into buffer 11. Buffer 11 is segmented and has allocated areas for storing data received for storage in the flash memory or for storing data to be sent to the host and 55 for storing background data.

If the compression results in greater than 512 bytes of compressed data, the drive will re-route the compressed data from buffer 11 through data multiplexer 12, FIFO 14 and selector 18 to decompressor 24 such that the data is decompressed back to its original 512 bytes and stored in RAM 31. The sector data is then routed as uncompressed data from RAM 31 through selector 18, FIFO 14, data multiplexer 12 into buffer 11.

If the compression results in an unsuccessful compression 65, the compression bit in the attribute word is set to indicate uncompressed. If the compression resulted in a successful

compression, the compression bit in the attribute word is set to indicate compression.

Since a new sector header is written for each writing of a sector and a sector header always exists within the flash memory for each logical sector number, the active or old sector header in the flash memory must be marked as invalid or dirty. In a similar fashion to the read operation, the last header associated with the sector marked dirty from the last write operation has been saved by the drive. The drive uses that header address as a pointer to the address for the next sector header in the flash array following the sector that was marked dirty during the last write operation. The drive reads the sector header and determines if the LSN in that header equals the LSN associated with the CHS address issued by the host. If the LSNs are the same, the drive will mark that header as dirty or invalid. A header is marked dirty or invalid by making the LSN stored in the header equal to 0000 which is an illegal LSN. If the LSN being sought is not equal to the LSN stored in the header, the drive reads the sector translation table to obtain a PFA for the LSN, in a similar fashion as was done for the read operation. Again, the PFA is tested as to whether it is valid or not and, if it is valid, the scan count is appended to the PFA to form the complete FA. Again, the scan count is set to zero and the drive then goes through the same loop of three steps, that is testing if the scan count is equal to 8, comparing the LSN being sought against the LSN in the header at the flash address and, finally, to add 1 to the scan count. If a match of the LSNs is found, the header at that FA is marked dirty.

If the PFA was invalid or the scan count reached a count of 8 indicating that the FA was invalid, the drive will ignore this situation and proceed with the write operation. This condition can be ignored because if the same LSN was issued during a read instruction, the read instruction would find the same invalid addresses and would return an ID not found status to the host. Further, since the write operation generates a new header which will update the sector translation table, there is no adverse affect by not finding the previous header for the LSN.

At this time either the old header has been marked invalid or the old header has not been found, the drive will next make a calculation of the amount of space available on the flash array for storing data. The drive maintains a register indicating the amount of free sectors and the amount of dirty sectors. The drive adds the number of free sectors to the number of dirty sectors and subtracts the number of sectors to be written during this write operation. The results is compared against a flash reserve set by the drive which is the number of sectors that have been reserved by the drive which are not available for writing data into. If the result is greater than the flash reserve, then standby status is sent to the host, indicating that the write operation cannot be performed.

If the result is equal to or less than the flash reserve, the drive performs the next test by subtracting the sector size from the number of free sectors and comparing the results with the cleanup reserve. The clean-up reserve is an amount of sectors that are predetermined by the drive as necessary to perform clean-up operations. If the result is greater than the clean-up reserve, the drive goes into a foreground clean-up operation. Each of the flash chips contains one megabyte of data and the block area that can be erased is 64 kilobytes of data. Therefore each block of data may contain a plurality of sectors stored within the block. The drive then reviews each block on each chip pair within the flash memory to determine if any block contains only dirty sectors. If such a block is found, that block is erased making that block available as free space.

In some situations the drive will find that a large proportion of a block is dirty and a small portion of the block has stored sector data. The drive will then go into a mode where it will read those sectors into the buffer and then restore 5 those sectors into the clean-up reserve area, thereby allowing the block to then be erased and provide more free space in the array. The reading and writing during a clean-up operation follows the same procedure as the reading and writing of read/write command from the host. 10

The drive will next check the block to which it last read a header during the write operation to determine whether that block has space available for writing the present sector. If space is not available, the drive will move to the next block on the chip and determine if space is available on that <sup>15</sup> block. Once a block is found with space available for writing the sector, a test is performed to determine if addition of this header would surpass the maximum number of headers allowed for a block. If the maximum number of headers would be surpassed, the drive will move on to the next block <sup>20</sup> until a block is found that has both space available and room for another header.

Once an available block has been located, the header for the new sector is written at the next available address in the block. At this time the drive will write the flash address less<sup>25</sup> the three low order bits into the sector translation table as the PFA for the LSN.

The drive will then check the attribute word for the new header to determine whether there is any data to be actually 30 stored for the sector. If no data is to be written, the write operation is completed. If there is data to be written, the drive will point the write circuitry on the proper flash chip pair to the address to begin writing the sector data. As previously discussed in the read operation, data is written 35 with the first data word being written at the offset flash addresses and all subsequent data words written at incremented addresses until all the data words have been written into the flash memory. Again data is written in a form of data words where data words contains two bytes of data. Effec-40 tively, all even bytes of data are stored in one flash chip and all odd bytes of data for the sector are stored in the other flash chip. During an erase operation of a block, a block in both of the flash chips will be erased.

The drive is now ready for the actual writing of data into the flash memory. The sector data stored in buffer 11 is first routed through multiplexer 12 to microprocessor 30 and to ECC generator 26. ECC generator generates 4 bytes of ECC data which is appended to the end of the sector data to be stored. Microprocessor 30 receives the byte by byte data from buffer 11 and provides data words to flash controller 21 such that flash controller 21 may write 16 bits in parallel into the flash memory. Microprocessor 30 will provide data words until all the data words for the sector data, the CRC data, if any, and the ECC data have been read into the flash 55 memory.

During a write operation the sectors associated with a write command are attempted to be written sequentially into the flash array. However, this is not a requirement as the flash solid state drive maintains the location of each sector's 60 location within the drive. Further, during a foreground operation, sectors may be moved from their original positions to other positions within the memory thereby destroying the sequentiality of location from which the sectors were originally written in the flash memory. However, the loca-65 tion of each sector is updated in the sector translation table whenever a sector is written, either in response to a write

20

command from the host or during a foreground clean-up operation.

When power is brought up to the flash solid state drive, the sector translation table must be recreated from the header information stored in the flash memory. ROM 28 is composed of flash chips and, therefore, is capable of being written into. A table of bad blocks is stored in ROM 28. Seldom does a block within the flash array go bad and, therefore, the time necessary to write this data into ROM 28 is not prohibitive. A block is deemed bad if two or more unrecoverable errors have been detected during a read operation from two or more unique locations in that block.

FIGS. 4A and 4B show the procedure enacted by the flash solid state drive to reconstruct the sector translation table during the power-up sequence. First, the PFA for each LSN is set to the illegal address of FFFF. Next, the registers containing the number of free sectors,dirty sectors and total number of sectors are reset to zero. Finally, the bad block data is read from ROM 28 and stored in RAM 29.

A test is done to establish if the last block in the flash array has been processed. If the last block has been processed, the initiation procedure is done. If the last block has not been processed, the drive will go to the next block in the flash array. In the beginning, the drive will go to the first block in the first chip pair and sequentially go through the blocks on a given chip pair and then through all chip pairs until all blocks on all chip pairs have been processed. When arriving at a block, the block table is checked to determine if the block is bad. If the block is bad, the block is not processed and the drive will go to the next block. Arriving at a good block the drive will read from the block the cycle count for that block.

Each block has stored within a designated area in the block a cycle count indicating the number of times the block has been erased. The cycle count is read and noted by the drive for that block of memory. The cycle count for the block being processed is compared with the maximum cycle count presently stored in the maximum cycle counter register. If the cycle count for this block is greater than the maximum cycle count in the register, the cycle count for this block is stored and becomes the maximum cycle count. The maximum and individual cycle counts are used by the drive in determining the wear profile of the flash memory. Since flash chips have a lifetime defined by the number of times the blocks on the chip are erased, it is desirable to attempt to maintain the cycle count across the flash memory as evenly as possible such that the flash chips in the flash memory age at the same rate. The drive can use the knowledge of the maximum cycle count and the cycle count for a given block in determining whether or not that block should be erased during a clean-up process as described for the write operation. By not erasing the block, the block will remain in its present erase age until other portions of the flash memory obtain approximately the same age.

Once arriving at a block the process will read the next header in the block. The header first read will be the first header in each block as that block is processed. The header LSN is read and that LSN's location is read from the sector translation table to determine if that LSN's PFA is equal to the invalid address of FFFF. A header is maintained by the drive at the end of the space allocated for header data to be written into the flash memory. This last header for has a LSN equal to FFFF. Therefore, after the header is read, the header LSN is checked for the value of FFFF and, if the condition is met, the drive knows that all headers have been processed. If the header LSN is not equal to FFFF then the drive will

ROM.

go on and process the header in that block.

Next, the header for the sector is checked to see if the sector is dirty, that is, does the sector contain valid data. The sector is noted to be dirty by having a LSN equal to 0000. If the sector is dirty, the dirty block register and dirty array <sup>5</sup> register are updated and the drive will read the next header. If the header is not dirty, the drive will read the logical sector number in the header and then reference that LSN in the sector translation table to determine if the PFA associated with that LSN is FFFF. If the PFA is not FFFF, the drive <sup>10</sup> knows that it had processed the same LSN prior to processing this header.

The header attribute word has a field which indicates the revision number which is generated by the drive whenever a LSN is written such that the highest revision number  $^{\rm 15}$ represent the LSN having the most recent and therefore valid data for that LSN. The drive will read the header for the PFA in the sector translation table for the LSN. The drive then compares the revision number in the retrieved or old header 20 for that LSN with the revision number for the presently being processed LSN. If the presently processed header's revision number is greater than the old header's revision number, the old header's is marked dirty by making a old header's LSN equal to 0000. The drive will then update the 25 dirty block register and dirty array register. Next, the drive will modify the sector translation table to reflect the PFA of the header presently being processed for the LSN stored the header presently being processed. The drive will then go on to process the next header.

If the header revision number for the presently processed sector is less than the revision number in the old header, then the presently processed header's LSN is marked dirty by making the LSN equal to 0000. In practice this occasion should not arise because low revision sectors should have been marked dirty when the latest revision was written. This process is done to make sure that the PFA associated with a LSN contains the most recent data that was stored in the flash memory for that LSN. Once again the total dirty block register and array register are updated and the drive then proceeds to the next header for processing.

When the last header has been processed in that block, the drive will update the total amount of free flash in the block, chip and array registers. When the last block has been processed, the sector translation table has been rebuilt and  $_{45}$  the total amount of free flash for each block, chip and the memory is stored in a free flash block registers, free flash chip registers and a free flash memory register. At the end of the initialization the drive will therefore have reconstructed the sector translation table and will know the free flash  $_{50}$  available for processing on each chip, for each block on each chip and for the total memory.

The foregoing description of the system architecture and the system operation would allow a drive designer, skilled in the art, to construct the flash solid state drive and to write an 55 operating system for operating that constructed flash solid state drive in the manner as heretofore set forth above. It is understood that the designer of the operating system may wish to vary the steps in the procedure as set forth in the discussion of the operation of the system. Further, the 60 designer may wish to design the system architecture to take advantages of the specification which the designer is setting for his own flash solid state drive. Such variations that could be to include would be where the operating system stored in ROM performs the procedures that are carried out by the state machines or where additional state machines carry out other portions of the operating system that where stored in

From the foregoing discussion a flash solid state drive has been described which emulates a magnetic disk drive. Specifically, the drive described emulates a 40 megabyte magnetic disk drive. The flash memory array will store 30 megabytes of compressed data which is equivalent to approximately 45 megabytes of uncompressed data. The flash drive described employs various length sectors for enhancing data storage, the simultaneous reading and writing of two bytes of information into and out of the flash memory to increase the speed of the flash solid state drive and the dynamic storage of sectors in the flash memory.

The flash solid state drive is transparent to the host and can be used directly in place of a magnetic disk drive having the same storage capacity, or less. Further, the flash array may be altered in size to contain more or less flash chips, thereby increasing or decreasing the capacity of long term memory within the flash solid state drive. The described flash solid state drive is plug compatible with the magnetic disk drive which it emulates and does not require any reprogramming of the host system employing the flash solid state drive.

## AT INTERFACE ARCHITECTURE STATE MACHINES

FIG. 5 is an overview of the major components of the AT architecture involved in the transfer of data to and from the host. In the WRITE command the host places a data word, two bytes, into data register 2, then the data word is transfer as two bytes of data via multiplexer 3 either directly to the buffer 11 if their is to be no compression or to compressor 25 and then to buffer 11 if their is to be compression. In the READ command, two bytes of data will be transferred from buffer 11 via multiplexer 3 to data register 2 then to the host as a data word if the sector being read was not compressor 24 and then two bytes will be sequentially transferred from decompressor 24 via multiplexer 3 to data register 2 and then a data word will be transferred to the host if the sector was compressed.

AT registers 25 can be accessed by the host, the microprocessor and the state machines and contains the information for controlling the transfer of data during a READ or WRITE operation. Byte Count State Machine 4 controls the transfer of a sector of data between data register 2 and buffer 11, compressor 25 and decompressor 24. Update Task File State Machine 5 determines when all sectors have been transferred and will cause the sector address to be incremented if another sector is to be transferred. Read State Machine 6 controls all READ commands. Write State Machine 7 controls all WRITE commands.

## UPDATE TASK FILE STATE MACHINE

The purpose of the Update Task File State Machine is to increment the cylinder head and sector values of the sector address, and to decrement the sector counter upon a request from either the Read State Machine or the Write State Machine.

#### STRUCTURE

FIG. 11 is a logic diagram of Update Task File State Machine 5. FFs 307 and 308 form a two bit register storing the present state of the state machine where FF 308 is the low bit. ANDs 309, 310 and 311 decode the count in FFs 307 and 308. AND's 309 output F2 will be high during state 2 of the state machine, AND's 310 output F1 will be high during state 1 of the state machine and AND's 311 output F3 will be high during state 3 of the state machine. ANDS 300, 301, 303, NOR 302 and OR 304 sequence the states of the 5 state machine as a function of the present state stored in FFs 307 and 308 and input control signals from the AT registers 25. ORs 305 and 306 output represent the next state of the state machine that will be read into FFs 307 and 308 by the next clock pulse. FFs 312 and 313, ANDs 315 and 317 and 10 NANs 314 and 316 control the incrementing of the sector address in response to outputs F1 and F3.

## OPERATION

FIG. 13 is a flow chart of the operation of the Update Task <sup>15</sup> File State Machine.

#### State 0

The state machine remains reset, at state 0, until it receives an update task file signal from either the Read or Write State Machine. If the sector counter is equal to zero and this is not the first operation of a read or write operation, the state machine will not respond to the update task file signal and will remain in state 0. If the sector count is not equal to zero or this is a first operation then the update task file signal will cause the state machine to switch to the next state.

#### State 1