### (12) United States Patent Ding et al.

#### (10) **Patent No.:** US 6,887,353 B1 May 3, 2005

(45) Date of Patent:

#### (54) TAILORED BARRIER LAYER WHICH PROVIDES IMPROVED COPPER INTERCONNECT ELECTROMIGRATION RESISTANCE

- (75) Inventors: Peijun Ding, San Jose, CA (US); Tony Chiang, Mountain View, CA (US);

- Barry L. Chin, Saratoga, CA (US)

- Assignee: Applied Materials, Inc., Santa Clara, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 863 days.

- (21) Appl. No.: 08/995,108

- (22) Filed: Dec. 19, 1997

- (51) **Int. Cl.**<sup>7</sup> ..... **C23C 14/00**; C23C 14/32; H01L 21/44

- **U.S. Cl.** ...... **204/192.15**; 204/192.17; 204/192.22; 204/192.25; 438/656

- **Field of Search** ...... 204/192.15, 192.17, 204/192.22, 192.25; 438/652, 656, 660

#### (56)References Cited

#### U.S. PATENT DOCUMENTS

| 4,319,264 A |   | 3/1982  | Gangulee et al 357/71 |

|-------------|---|---------|-----------------------|

| 4,985,750 A | * | 1/1991  | Hoshino 257/751       |

| 5,186,718 A |   | 2/1993  | Tepman et al 29/25.01 |

| 5,236,868 A |   | 8/1993  | Nulman 437/190        |

| 5,240,880 A | * | 8/1993  | Hindman et al 438/656 |

| 5,281,485 A |   | 1/1994  | Colgan et al 428/457  |

| 5,320,728 A |   | 6/1994  | Tepman 204/192        |

| 5,391,517 A | * | 2/1995  | Gelatos et al 438/643 |

| 5,521,120 A | * | 5/1996  | Nulman et al 438/653  |

| 5,571,752 A | * | 11/1996 | Chen et al 438/642    |

| 5,676,587 A |   | 10/1997 | Landers et al 451/57  |

| 5,707,498 A | * | 1/1998  | Ngan 204/192.12       |

| 5,795,796 A | * | 8/1998  | Kim 438/660           |

|             |   |         |                       |

#### FOREIGN PATENT DOCUMENTS

| EP | 0 570 205 A1 | 11/1993 | <br>H01L/21/321 |

|----|--------------|---------|-----------------|

| EP | 0 751 566 A2 | 1/1997  | <br>H01L/23/532 |

#### OTHER PUBLICATIONS

Karen Holloway et al., "Tantalum as a Diffusion as a Diffusion Barrier Between Copper and Silicon: Failure Mechanism and Effect of Nitrogen Additions", J. Appl. Phys. 71 (11), Jun. 1, 1992, pp. 5433-5444.

Katsutaka Sasaki et al., "Stoichiometry of Ta-N Film and Its Application for Diffusion Barrier in the Al<sub>3</sub> Ta/Ta-N/Si Contact System", Japanese Journal of Applied Physics, vol.

29, No. 6, Jun. 1990, pp. 1043–1047.

E. M. Zielinski et al., "The Effects of Processing on the Microstructure of Copper Thin Films on Tantalum Barrier Layers", Mat. Res. Soc. Symp. Proc. vol. 391, (1995,) pp

PCT International Search Report dated Mar. 25, 1999. Gang Bai et al., "Copper Interconnection Depostion Techniques and Integration", 1996 Symposium on VLSI Technology, Digests of Technical Papers (0-7803-3342-X/96, S. M. Rossnagel and J. Hopwood, "Metal ion deposition from ionized magnetron sputtering discharge", J. Vac. Sci. Technol. B, vol. 12, No. 1, pp. 449–453 (Jan./Feb. 1994).

S. M. Rossnagel et al., "Thin, high atomic weight refractory film deposition for diffusion barrier, adhesion layer, and seed layer applications", J. Vac. Sci. Technol. B, vol. 14, No. 3, pp. 1819-1827 (May/Jun. 1996).

C. Steinbruchel, "Patterning of Copper for Multilevel Metallization: Reactive Ion Etching and Chemical-Mechanical Polishing", Applied Surface Science, 91, pp. 139–146

U.S. Appl. No. 08/824,911, filed Mar. 27, 1997, of Ngan et

U.S. Appl. No. 08/863,451, filed May. 27, 1997, of Chiang

U.S. Appl. No. 08/924,487, filed Aug. 23, 1997, of Ngan et

\* cited by examiner

Primary Examiner—Patrick Ryan Assistant Examiner-Julian Mercado (74) Attorney, Agent, or Firm-Shirley L. Church

#### **ABSTRACT**

Disclosed herein is a barrier layer structure useful in forming copper interconnects and electrical contacts of semiconductor devices. The barrier layer structure comprises a first layer of TaN, which is applied directly over the substrate, followed by a second layer of Ta. The TaN<sub>x</sub>/Ta barrier layer structure provides both a barrier to the diffusion of a copper layer deposited thereover, and enables the formation of a copper layer having a high <111> crystallographic content so that the electromigration resistance of the copper is increased. The TaN<sub>x</sub> layer, where x ranges from about 0.1 to about 1.5, is sufficiently amorphous to prevent the diffusion of copper into the underlying substrate, which is typically silicon or a dielectric such as silicon dioxide. The thickness of the TaN<sub>x</sub> and Ta layers used for an interconnect depend on the feature size and aspect ratio; typically, the TaN<sub>x</sub> layer thickness ranges from about 50 Å to about 1,000 Å, while the Ta layer thickness ranges from about 20 Å to about 500 Å. For a contact via, the permissible layer thickness on the via walls must be even more carefully controlled based on feature size and aspect ratio; typically, the TaN<sub>x</sub> layer thickness ranges from about 10 Å to about 300 Å, while the Ta layer thickness ranges from about 5 Å to about 300 Å. The copper layer is deposited at the thickness desired to suit the needs of the device. The copper layer may be deposited using any of the preferred techniques known in the art. Preferably, the entire copper layer, or at least a "seed" layer of copper, is deposited using physical vapor deposition techniques such as sputtering or evaporation, as opposed to CVD or electroplating. Since the crystal orientation of the copper is sensitive to deposition temperature, and since the copper may tend to dewet/delaminate from the barrier layer if the temperature is too high, it is important that the copper be deposited and/or annealed at a temperature of less than about 500° C., and preferably at a temperature of less than about 300° C.

7 Claims, 2 Drawing Sheets

1

#### TAILORED BARRIER LAYER WHICH PROVIDES IMPROVED COPPER INTERCONNECT ELECTROMIGRATION RESISTANCE

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention pertains to a particular  ${\rm TaN_x/Ta}$   $_{10}$  barrier/wetting layer structure which increases the degree of  $\{111\}$  crystal orientation in an overlying copper layer, thereby providing improved electromigration resistance of the copper.

#### 2. Brief Description of the Background Art

As microelectronics continue to miniaturize, interconnection performance, reliability, and power consumption has become increasingly important, and interest has grown in replacing aluminum alloys with lower-resistivity and higher-reliability metals. Copper offers a significant improvement over aluminum as a contact and interconnect material. For example, the resistivity of copper is about  $1.67 \,\mu\Omega$ cm, which is only about half of the resistivity of aluminum.

There are two principal competing technologies under evaluation by material and process developers working to <sup>25</sup> enable the use of copper. The first technology is known as damascene technology. In this technology, a typical process for producing a multilevel structure having feature sizes (i.e., width of the aperture) in the range of 0.5 micron ( $\mu$ m) or less would include: blanket deposition of a dielectric material; patterning of the dielectric material to form openings; deposition of a diffusion barrier layer and, optionally, a wetting layer to line the openings; deposition of a copper layer onto the substrate in sufficient thickness to fill the openings; and removal of excessive conductive material from the substrate surface using chemical-mechanical polishing (CMP) techniques. The damascene process is described in detail by C. Steinbruchel in "Patterning of copper for multilevel metallization: reactive ion etching and chemical-mechanical polishing", Applied Surface Science 91 (1995)139-146.

The competing technology is one which involves the patterned etch of a copper layer. In this technology, a typical process would include deposition of a copper layer on a desired substrate (typically a dielectric material having a barrier layer on its surface); application of a patterned hard mask or photoresist over the copper layer; pattern etching of the copper layer using wet or dry etch techniques; and deposition of a dielectric material over the surface of the patterned copper layer, to provide isolation of conductive lines and contacts which comprise various integrated circuits

Typically, the copper layer can be applied using sputtering techniques well known in the art. The sputtering of copper 55 provides a much higher deposition rate than evaporation or CVD (chemical vapor deposition) and provides a purer copper film than CVD.

In integrated circuit interconnect structures where copper is the material used to form conductive lines and contacts, it for recognized that copper diffuses rapidly into adjacent layers of SiO<sub>2</sub> and silicon and needs to be encapsulated. Gang Bai et al. in "Copper Interconnection Deposition Techniques and Integration", 1996 Symposium on VLSI Technology, Digests of Technical Papers (0-7803-3342-X/ 65) orientation. The Ti/TiN/TiN<sub>x</sub> barrier layer was deposited using IMP (ion metal plasma) techniques, and the barrier layer thicknesses were as follows. The thickness of the first layer of Ti ranges from greater than about 100 Å to about 500 Å (the feature geometry controls the upper thickness limit). The thickness of the TiN second layer ranges from greater than about 100 Å to less than about 800 Å

2

annealed in UHV (ultra high vacuum) after copper deposition provided the best barrier layer. Sputtered copper appeared to be preferable over CVD copper and over electroplated copper, although all the data for electroplated copper was not available at the time of presentation of the paper.

U.S. Pat. No. 4,319,264 of Gangulee et al., issued Mar. 9, 1982 and titled "Nickel-gold-nickel Conductors For Solid State Devices" discusses the problem of electromigration in solid state devices. In particular, the patent discusses the application of direct current over particular current density ranges which induces motion of the atoms comprising the thin film conductor, the effect known as electromigration. Electromigration is said to induce crack or void formation in the conductor which, over a period of time, can result in conductor failure. The rate of electromigration is said to be dependent on the current density imposed on the conductor, the conductor temperature, and the properties of the conductor material. In high current density applications, potential conductor failure due to electromigration is said to severely limit the reliability of the circuit. In discussing the various factors affecting performance of the conductive materials, grain structure is mentioned as being important. (In order to obtain adequate lithographic line width resolution, it is recommended that the film be small grained, with a grain size not exceeding about one-third of the required line width.) Uniformity of grain size and preferred crystallographic orientation of the grains are also said to be factors which promote longer (electromigration limited) conductor lifetimes. Fine grained films are also described as being smoother, which is a desirable quality in semiconductor applications, to lessen difficulties associated with covering the conductor with an overlayer.

U.S. Pat. No. 5,571,752 to Chen et al., issued Nov. 5, 1996, discloses a method for patterning a submicron semi-conductor layer of an integrated circuit. In one embodiment describing an aluminum contact, titanium or titanium nitride having a thickness of between approximately 300 and 2,000 Å is formed by sputter deposition to reach the bottom of a contact opening. Finally, a second conductive layer, typically aluminum, is applied over the surface of the conformal conductive layer. The aluminum is sputtered on, preferably at a temperature ranging between approximately 100° C. and 400° C. This method is said to make possible the filling of contact openings having smaller device geometry design requirements by avoiding the formation of fairly large grain sizes in the aluminum film.

As described in U.S. patent application Ser. No. 08/824, 911, of Ngan et al., filed Mar. 27, 1997 and commonly assigned with the present invention, efforts have been made to increase the <111> crystallographic content of aluminum as a means of improving electromigration of aluminum. In particular, the <111> content of an aluminum layer was controlled by controlling the thickness of various barrier layers underlying the aluminum layer. The underlying barrier layer structure was Ti/TiN/TiN<sub>x</sub>, which enabled aluminum filling of high aspect vias while providing an aluminum fill exhibiting the high degree of aluminum <111> crystal orientation. The Ti/TiN/TiN<sub>x</sub> barrier layer was deposited using IMP (ion metal plasma) techniques, and the barrier layer thicknesses were as follows. The thickness of the first layer of Ti ranges from greater than about 100 Å to about 500 Å (the feature geometry controls the upper thickness limit). The thickness of the TiN second layer ranges from 3

titanium to about 100 atomic percent titanium) ranges from about 15 Å to about 500 Å. A  $\text{Ti/TiN/TiN}_x$  barrier layer having this structure, used to line a contact via, is described as enabling complete filling of via with sputtered warm aluminum, where the feature size of the via or aperture is 5 about 0.25 micron or less and the aspect ratio ranges from about 5:1 to as high as about 6:1.

Subsequently, in U.S. Pat. No. 5,882,399, of Ngan et al., issued Mar. 16, 1999, the inventors disclose that to maintain a consistently high aluminum <111> crystal orientation 10 content of an interconnect during the processing of a series of semiconductor substrates in a given process chamber, it is necessary to form the first deposited layer of the barrier layer to a minimal thickness of at least about 150 Å, to compensate for irregularities in the crystal orientation which may be 15 present during the initial deposition of this layer when the process chamber is initially started up (and continuing for the first 7-8 wafers processed). Ngan et al. teach that in the case of a copper conductive layer, it may also be necessary that the first layer of a barrier layer structure underlying the 20 copper layer have a minimal thickness of at least about 150 A, to enable a consistent crystal orientation within the copper layer during the processing of a series of wafers in a semiconductor chamber.

#### SUMMARY OF THE INVENTION

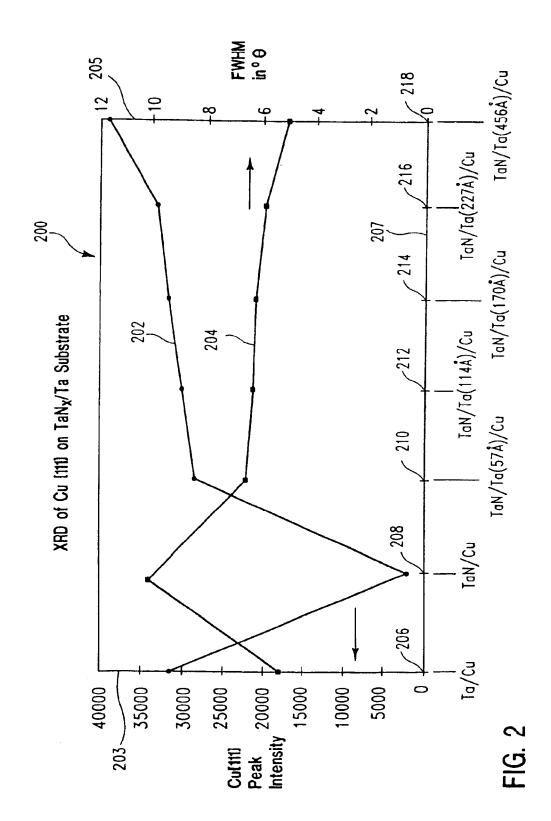

We have discovered that tantalum nitride  $(TaN_x)$  is a better barrier layer for copper than tantalum (Ta). However, copper deposited directly over  $TaN_x$  does not exhibit a sufficiently high degree of <111> crystal orientation to provide the desired copper electromigration characteristics. We have developed a barrier layer structure comprising a layer of Ta overlying a layer of  $TaN_x$  which provides both a barrier to the diffusion of a copper layer deposited thereover, and enables the formation of a copper layer having a high <111> crystallographic content, so that copper electromigration resistance is increased.

The  $\mathrm{TaN}_x$  layer, where x ranges from about 0.1 to about 1.5, is sufficiently amorphous to prevent the diffusion of copper into underlying silicon or silicon oxide surfaces. The desired thickness for the  $\mathrm{TaN}_x$  layer is dependent on the device structure. For a typical interconnect, the  $\mathrm{TaN}_x$  layer thickness ranges from about 50 Å to about 1,000 Å. For a contact, the  $\mathrm{TaN}_x$  layer, the thickness on the wall of a contact via ranges from about 10 Å to about 300 Å, depending on the feature size. The  $\mathrm{TaN}_x$  layer is preferably deposited using standard reactive ion sputtering techniques at a substrate temperature ranging from about 20° C. to about 500° C. However, ion deposition sputtering techniques may be used to deposit this layer.

The Ta layer deposited over the  $\text{TaN}_x$  layer has a desired thickness ranging from about 5 Å to about 500 Å, wherein the thickness is preferably greater than about 20 Å, depending on the feature size. The Ta layer is preferably deposited using standard ion sputtering techniques at a substrate temperature ranging from about 20° C. to about 500° C. However, ion deposition sputtering techniques may be used to deposit this layer.

The copper layer is deposited at the thickness desired to 60 suit the needs of the device. The copper layer may be deposited using any of the preferred techniques known in the art. Preferably, the entire copper layer or at least a "seed" layer of copper is deposited using physical vapor deposition techniques such as sputtering or evaporation, as opposed to 65

4

temperature of the copper either during deposition or during subsequent annealing processes not be higher than about  $500^{\circ}$  C. Preferably, the maximum temperature is about  $300^{\circ}$  C.

We have also developed a method of producing a copper interconnect structure comprising a copper layer deposited over a barrier layer structure of the kind described above, comprising a Ta layer overlying a  $\text{TaN}_x$  layer, where the Cu <111> crystallographic content is at least 70% of the Cu <111> crystallographic content which can be obtained by depositing the copper layer over a pure Ta barrier layer which is about 500 Å thick. The method comprises the steps of:

- a) depositing a first layer of  $TaN_x$  having a thickness ranging from greater than about 50 Å to about 1,000 Å;

- b) depositing a second layer of Ta having a thickness ranging from about 5 Å to about 500 Å over the surface of the first layer of TaN<sub>x</sub>; and

- c) depositing a third layer of copper over the surface of the second layer of Ta, wherein at least a portion of the third layer of copper is deposited using a physical vapor deposition technique, and wherein the substrate temperature at which the third layer of copper is deposited is less than about 500° C.

Further, we have developed a method of producing a copper-comprising contact via structure comprising a copper layer deposited over a barrier layer structure of the kind described above, comprising a Ta layer overlying a  $\text{TaN}_x$  layer; wherein the Cu <111> crystallographic content is at least 70% of the Cu <111> crystallographic content which can be obtained by depositing said copper layer over a pure Ta barrier layer which is about 300 Å thick. The method comprises the steps of:

- a) depositing a first layer of  $TaN_x$  having a thickness ranging from greater than about 10 Å to about 300 Å;

- b) depositing a second layer of Ta having a thickness ranging from about 5 Å to about 300 Å over the surface of said first layer of TaN<sub>x</sub>; and

- c) depositing a third layer of copper over the surface of the second layer of Ta, wherein at least a portion of the third layer of copper is deposited using a physical vapor deposition technique, and wherein the substrate temperature at which the third layer of copper is deposited is less than about 500° C.

In the method of producing a copper-comprising contact structure described above, a least a portion of the first layer of  $TaN_x$ , or the second layer of Ta, or the third layer of Ta, or at least a portion of more than one of these three layers may be deposited using ion-deposition sputtering, where at least a portion of the sputtered emission is in the form of ions at the time the emission reaches the substrate surface, and where, typically 10% or more of the sputtered emission is in the form of ions at the time the emission reaches the substrate surface.

#### BRIEF DESCRIPTION OF THE DRAWINGS

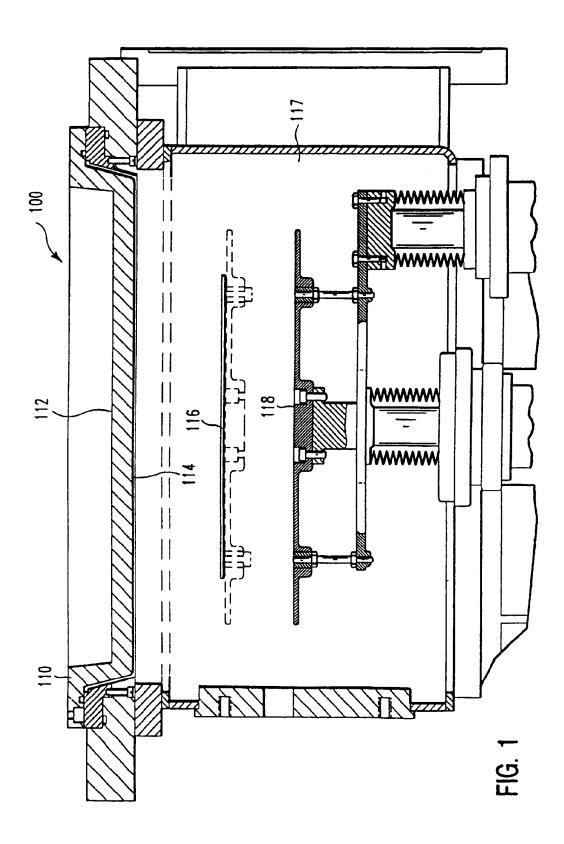

FIG. 1 shows a schematic of a cross sectional view of a sputtering chamber of the kind which can be used to deposit the barrier layer of the present invention.

FIG. 2 shows a graph representative of the copper <111> crystal orientation on a  $TaN_x/Ta$  barrier layer as a function of the thickness of the Ta layer, with the  $TaN_x$  layer held constant at about 500 Å.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.