This is an *Archive IEEE Standard*. It has been withdrawn or superseded by a later version of the standard.

ARCHIVE STANDARDS MAY HAVE VALUE AS HISTORICAL DOCUMENTS, BUT THEY ARE NOT VALID OR APPROVED IEEE STANDARDS. THE IEEE SHALL NOT BE LIABLE FOR ANY DAMAGES RESULTING FROM THE SUBSCRIBER'S OR USERS' PRACTICE OF THIS UNAPPROVED, ARCHIVE IEEE STANDARD.

For more information about this or other current, revised or withdrawn standards, please consult the IEEE Standards Status report on-line at <a href="http://standards.ieee.org/db/status/">http://standards.ieee.org/db/status/</a>.

# IEEE Standards for Local and Metropolitan Area Networks:

Supplement to Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications

Media Access Control (MAC) Parameters, Physical Layer, Medium Attachment Units, and Repeater for 100 Mb/s Operation, Type 100BASE-T (Clauses 21–30)

Sponsor

LAN MAN Standards Committee of the IEEE Computer Society

Approved 14 June 1995

IEEE Standards Board

Approved 4 April 1996

**American National Standards Institute**

2nd Printing, Corrected Edition

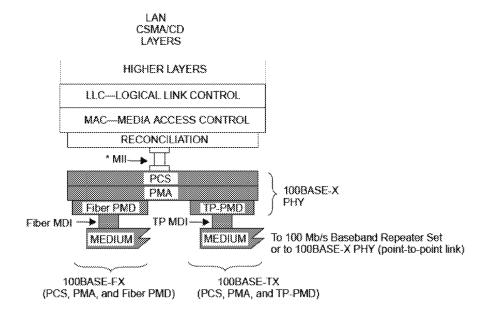

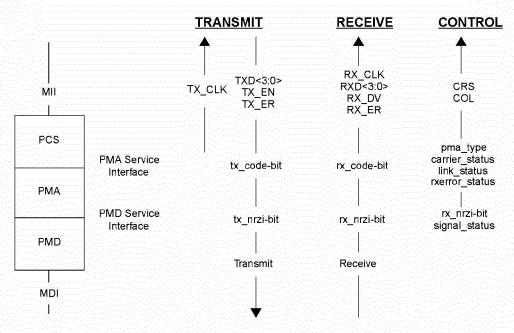

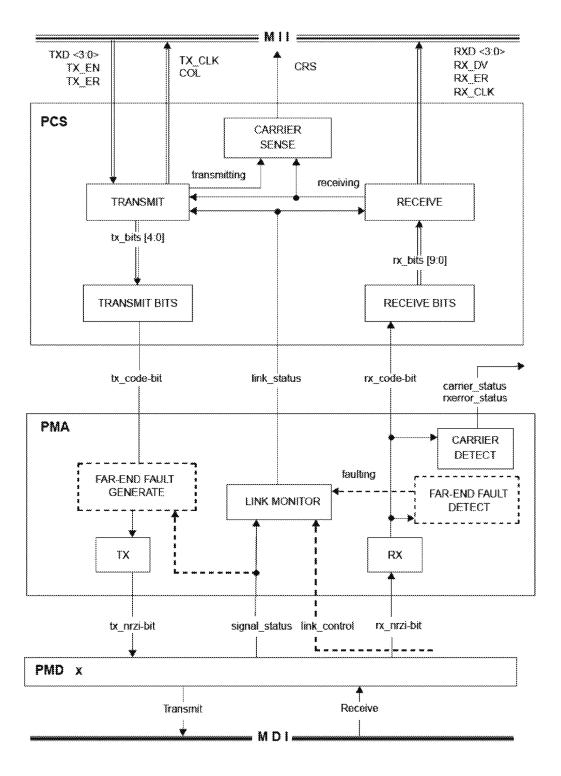

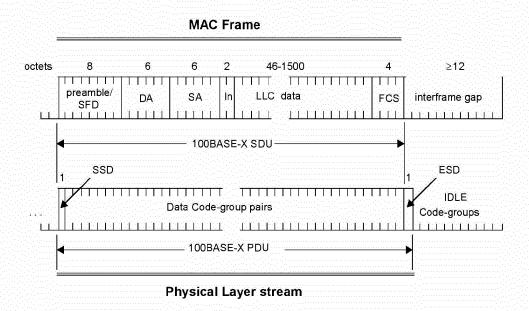

Abstract: The ISO/IEC CSMA/CD Media Access Control (MAC) is given an additional set of parameters for 100 Mb/s operation. A repeater and added Physical Layers, known collectively as 100BASE-T, as well as significant additional supporting material for a Media Independent Interface (MII), management, and automatic configuration, are specified. This includes 100BASE-T4, which uses four pairs of Category 3, 4, or 5 generic twisted, balanced cable; 100BASE-TX, which uses two pairs of Category 5 balanced cable or 150 | shielded balanced cable; and 100BASE-FX, which uses two multi-mode fibers. Fibre Distributed Data Interface (FDDI) media interface specifications are referenced to provide the 100BASE-TX and 100BASE-FX physical signaling channels, defined under the subcategory 100BASE-X.

**Keywords:** 100BASE-FX, 100BASE-T, 100BASE-T4, 100BASE-TX, 100BASE-X, Auto-Negotiation, Fast Ethernet, management, Media Independent Interface (MII), repeater

The Institute of Electrical and Electronics Engineers, Inc. 345 East 47th Street, New York, NY 10017-2394, USA

Copyright © 1995 by the Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 1995. Printed in the United States of America

ISBN 1-55937-542-6

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

**IEEE Standards** documents are developed within the Technical Committees of the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason IEEE and the members of its technical committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; (508) 750-8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

# **Corrected Edition, June 1996**

The following corrections have been made to this edition:

**Page 23:** The designation of reference [A5] has been corrected to ANSI/EIA/TIA 526-14-1990. [Note that further updates to annex A can be found in ISO/IEC 8802-3: 1996.]

Page 32: In the last line of text on the page, the word "fourth" has been corrected to "sixth."

**Page 174:** In figure 24-11, the "BAD SSD" box text has been corrected. "RXD $<3.0> \Leftarrow 1110$ " now reads "RXD $<3:0> \Leftarrow 1110$ ".

**Page 234:** The page, containing subclauses 27.7.4.11 and 27.7.4.12, was inadvertently omitted from the first printing. It is now included.

**Page 286:** Under list item a), notes 2 and 3 were misnumbered and have been corrected. Also, references in notes 2 and 3 to table 29-2 have been corrected to table 29-3.

**Page 301:** In table 30-1d, "aAutoNegAdvertisedTechnologyAbilit" has been corrected to "aAutoNegAdvertisedTechnologyAbility".

Page 312: In subclause 30.4.1.1.2, the reference to 20.2.2.3 for "other" has been corrected to 30.2.5.

Page 323: In subclause 30.5.1.1.2, the reference to 20.2.2.3 for "other" has been corrected to 30.2.5.

Note that additional corrections are under consideration, and that some reference documents have been updated. These will be included in future maintenance documents.

# Introduction

(This introduction is not part of IEEE Std 802.3u-1995.)

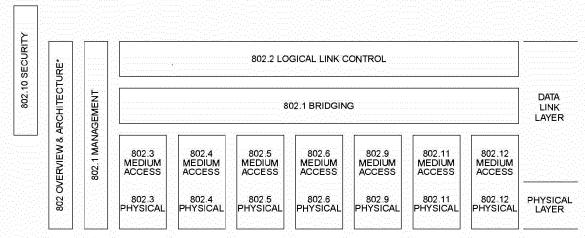

This standard is part of a family of standards for local and metropolitan area networks. The relationship between the standard and other members of the family is shown below. (The numbers in the figure refer to IEEE standard numbers.)

<sup>\*</sup> Formerly IEEE Std 802.1A.

This family of standards deals with the Physical and Data Link layers as defined by the International Organization for Standardization (ISO) Open Systems Interconnection Basic Reference Model (ISO 7498 : 1984). The access standards define several types of medium access technologies and associated physical media, each appropriate for particular applications or system objectives. Other types are under investigation.

The standards defining the technologies noted above are as follows:

| • IEEE Std 802 <sup>1</sup> :                | Overview and Architecture. This standard provides an overview to the family of IEEE 802 Standards. This document forms part of the 802.1 scope of work.                                                              |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • ANSI/IEEE Std 802.1B<br>[ISO/IEC 15802-2]: | LAN/MAN Management. Defines an Open Systems<br>Interconnection (OSI) management-compatible architecture,<br>and services and protocol elements for use in a LAN/MAN<br>environment for performing remote management. |

| • ANSI/IEEE Std 802.1D<br>[ISO/IEC 10038]:   | MAC Bridging. Specifies an architecture and protocol for the interconnection of IEEE 802 LANs below the MAC service boundary.                                                                                        |

| • ANSI/IEEE Std 802.1E<br>[ISO/IEC 15802-4]: | System Load Protocol. Specifies a set of services and protocol for those aspects of management concerned with the loading of systems on IEEE 802 LANs.                                                               |

<sup>&</sup>lt;sup>1</sup>The 802 Architecture and Overview standard, originally known as IEEE Std 802.1A, has been renumbered as IEEE Std 802. This has been done to accommodate recognition of the base standard in a family of standards. References to IEEE Std 802.1A should be considered as references to IEEE Std 802.

• ANSI/IEEE Std 802.2 [ISO/IEC 8802-2]: Logical Link Control

• ANSI/IEEE Std 802.3 [ISO/IEC 8802-3]: CSMA/CD Access Method and Physical Layer Specifications

• ANSI/IEEE Std 802.4 [ISO/IEC 8802-4]: Token Bus Access Method and Physical Layer Specifications

• ANSI/IEEE Std 802.5 [ISO/IEC 8802-5]: Token Ring Access Method and Physical Layer Specifications

• ANSI/IEEE Std 802.6 [ISO/IEC 8802-6]: Distributed Queue Dual Bus Access Method and Physical

Layer Specifications

• IEEE Std 802.9: Integrated Services (IS) LAN Interface at the Medium Access

Control (MAC) and Physical (PHY) Lavers

• IEEE Std 802.10: Interoperable LAN/MAN Security, Currently approved:

Secure Data Exchange (SDE)

• IEEE 802.12: Demand Priority Access Method/Physical Layer Specifications

In addition to the family of standards, the following is a recommended practice for a common Physical Layer technology:

• IEEE Std 802.7: IEEE Recommended Practice for Broadband Local Area

Networks

The following additional working groups have authorized standards projects under development:

• IEEE 802.11: Wireless LAN Medium Access Control (MAC) Sublayer and

Physical Layer Specifications

• IEEE 802.14: Standard Protocol for Cable-TV Based Broadband

Communication Network

The reader of this standard is urged to become familiar with the complete family of standards.

# Conformance test methodology

An additional standards series, identified by the number 1802, has been established to identify the conformance test methodology documents for the 802 family of standards. Thus the conformance test documents for 802.3 are numbered 1802.3, the conformance test documents for 802.5 will be 1802.5, and so on. Similarly, ISO will use 18802 to number conformance test standards for 8802 standards.

#### IEEE Std 802.3u-1995

At the time this standard (IEEE Std 802.3u-1995) was published, the IEEE 802.3 standard consisted of the following published documents:

- ISO/IEC 8802-3: 1993 [ANSI/IEEE Std 802.3, 1993 Edition]

- IEEE Std 802.3j-1993, Fiber Optic Active and Passive Star-Based Segments, Type 10BASE-F (Clauses 15–18)

- IEEE Std 802.3k-1992, Layer Management for 10 Mb/s Baseband Repeaters (Clause 19)

- IEEE Std 802.31-1992, Type 10BASE-T Protocol Implementation Conformance Statement (PICS)

Proforma (Subclause 14.10)

- IEEE Std 802.3p-1993 and IEEE Std 802.3q-1993, Guidelines for the Development of Managed Objects (GDMO) (ISO/IEC 10165-4) Format for Layer-Managed Objects (Clause 5) and Layer Management for 10 Mb/s Baseband Medium Attachment Units (MAUs) (Clause 20)

- IEEE Std 1802.3d-1993, Type 10BASE-T Medium Attachment Unit (MAU) (Conformance Test Methodology (Clause 6)

At the time this standard was published, there was revision and supplementary material that had been approved and scheduled for publication. Also, a new edition of ISO/IEC 8802-3 was in preparation to consolidate a significant amount of the above material. Information on the current state of this and other IEEE 802 standards may be obtained from

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

IEEE 802 committee working documents are available from

IEEE Document Distribution Service AlphaGraphics #35 Attn: P. Thrush 10201 N. 35th Avenue Phoenix, AZ 85051 USA

# Patent information

The IEEE Standards Board calls attention to the fact that it is claimed that portions of IEEE Std 802.3u-1995 are the subject of patents owned by a number of companies. The IEEE takes no position with respect to patent validity. Each of these companies has assured IEEE that it is willing to grant a license on these patents on reasonable and nondiscriminatory terms to anyone wishing to obtain such a license. The undertakings of these companies in this respect are on file with the IEEE Standards Department, and the license details may be obtained by contacting the Standards Department.

# **Participants**

When the IEEE 802.3 Working Group approved IEEE Std 802.3u-1995, it had the following membership:

# Geoffrey O. Thompson, Chair

Peter Tarrant, Type 100BASE-T Task Force Chair, Phase 1 Howard Frazier, Type 100BASE-T Task Force Chair, Phase 2 Paul Sherer, Editor-in-Chief, Phase 1 Howard Johnson, Editor-in-Chief, Phase 2 Colin Mick, Comment Editor

Walter Hurwitz†

Martin Adams Don Aelmore Paul Ahrens Vish Akella Abe Ali Nitish Amin Mike Armstrong Denis Beaudoin Larry Birenbaum\* Mark Bohrer Paul Booth\* Samuel Bourche David Bourque Sidney Bouzaglo Richard Bowers Richard Brand Charles E. Brill Bill Bunch† Peter Campbell Kiwon Chang Samuel Chang Howard Charney Hon Wah Chin Jacques Christ Ronald J. Cooper Ron Crane Ian Crayford\* Robert Curtis Bernard Daines Sean Dingman Thuyen Dinh Dan Dove James Doyle Peter Ecclesine Dean Edwards George Eisler Nick Esser Jim Everitt David Fischer Alan Flatman Christian G. Folting Atsuhisa Fukuoka Wolfgang Heidasch

Ernie Jensen Clarence Joh Anthony Jordan Dieter Junkers Omer Kal Ron Kao Yongbum Kim Srinivas Kola Josef Kozilek George Kubovcik Hans Lackner Erik Lander David Law\* Chun-Tsung Lee Jack Lee Vincent Lefebvre Richard Lewis Sam Liang Chan-De Lin Chang-Chi Liu Terry Lockyer Ken Lu Andy J. Luque Brian MacLeod Kenneth MacLeod Joseph Mazor Mike McConnell John McCool Tim McShane Mart L. Molle Shimon Muller Samba Murthy Larry Nicholson Paul Nikolich Ahmad Nouri J. Michael O'Connor Lloyd Oliver Pat Overs Sandeep Patel John Payne Tony Peatfield

Thomas J. Quigley Mohammad Rajabzadeh Shlomo Rakib Brian Ramelson Peter Rautenberg Dennis Rehm Victor Renteria Sean Riley Gary Robinson Khosrow Sadeghi David Schwartz Stephen Sedio Rich Seifert Koichiro Seto Chen-Chung Shih Som Sikdar Charan J. Singh\* Paramjeet (P. J.) Singh Dinah Sloan Tom Slykhouse Michael Smith Dror Sofer Gregory Somer Walter Sotelo Peter Staub Ron Sulvma Daniel Sze Martin Takessian Wen-Tsung Tang Tim Teckman Douglas Thomson Nader Vijeh Moshe Voloshin Ikuo Wakayama Chang Jung Wang Yun-Che Wang Ken Ward **Bob Watson** David Wong Paul Woodruff\*

Nariman Yousefi

Jamie Zartman

William Quackenbush

<sup>\*</sup> served as sub-task force chair or clause editor

<sup>†</sup> served as clause editor but was not a working group member at the time of ballot

# The following persons were on the balloting committee:

Don Aelmore Bernhard Albert Alan Albrecht Abe Ali Hasan S. Alkhatib Corey Anderson Kit Athul William E. Ayen Kendall F. Barney Larry Birenbaum Simon Black Kwame Boakve Kathleen L. Briggs Peter K. Campbell James T. Carlo Alan J. Chwick Alistair Coles Ian Crayford Robert S. Crowder Joe Curcio Ibibia K. Dabipi Robert Donnan Daniel Dove Edward A. Dunlop John E. Emrich Alvin W. Eng Philip H. Enslow, Jr. Changxin Fan John W. Fendrich David Fifield Michael Fischer Christian G. Folting Howard M. Frazier Harvey A. Freeman Robert J. Gagliano D. G. Gan Harry Gold Patrick Gonia Andrew Gruskay

Jacob J. Hsu Howard Johnson Gary C. Kessler Mladen Kezunovic Yongbum Kim Mikio Kiyono Kenneth C. Kung David Law Lanse M. Leach Sam Liang Randolph S. Little Donald C. Loughry Robert D. Love William C. Lynch Peter Martini William C. McDonald Tim J. McShane Bennett Meyer Colin K. Mick Ann Miller Bruce D. Miller Richard H. Miller David S. Millman Warren Monroe John E. Montague Kinji Mori David J. Morris James R. Moulton Wayne D. Moyers Shimon Muller Paul Nikolich Ellis S. Nolley Robert O'Hara Donal O'Mahony Young Oh Joerg Ottensmeyer Roger Pandanda Lalit Mohan Patnaik Lucy W. Person

Thomas L. Phinney Kirk Preiss Alberto Profumo Vikram Punj Andris Putnins Brian Ramelson Fernando Ramos Eugene J. Reilly Everett O. Rigsbee Gary S. Robinson Philip T. Robinson James W. Romlein Floyd E. Ross S. I. Samovlenko Frederick E. Sauer Frederick Scholl David Schwartz Mick Seaman John Selep Koichiro Seto Donald A. Sheppard Leo Sintonen William R. Smith Harry P. Solomon Robert K. Southard Efstathios D. Sykas Steven R. Taylor Patricia Thaler Geoffrey O. Thompson Kaichi Tsuno Mark-Rene Uchida Barry M. Vornbrock Yun-Che Wang Alan J. Weissberger Frank J. Weisser Raymond P. Wenig Earl J. Whitaker Jerry A. Wyatt Oren Yuen

When the IEEE Standards Board approved this standard on June 14, 1995, it had the following membership:

# E. G. "Al" Kiener, Chair

# Donald C. Loughry, Vice Chair

# Andrew G. Salem, Secretary

Gilles A. Baril Clyde R. Camp Joseph A. Cannatelli Stephen L. Diamond Harold E. Epstein Donald C. Fleckenstein

Jay Forster\*

Donald N. Heirman

Richard J. Holleman Jim Isaak Ben C. Johnson Sonny Kasturi Lorraine C. Kevra Ivor N. Knight Joseph L. Koepfinger\* D. N. "Jim" Logothetis L. Bruce McClung Marco W. Migliaro Mary Lou Padgett John W. Pope Arthur K. Reilly Gary S. Robinson Ingo Rusch Chee Kiow Tan Leonard L. Tripp

Also included are the following nonvoting IEEE Standards Board liaisons:

Satish K. Aggarwal Richard B. Engelman Robert E. Hebner Chester C. Taylor

Kristin M. Dittmann IEEE Standards Project Editor

<sup>\*</sup>Member Emeritus

# Contents

| CL  | AUSE    |            |                                                                         | PAGE |

|-----|---------|------------|-------------------------------------------------------------------------|------|

| Rev | visions | to ISO/IE  | C 8802-3: 1993 [ANSI/IEEE Std 802.3, 1993 Edition]                      | 1    |

| 21  | Introd  | luction to | 100 Mb/s baseband networks, type 100BASE-T                              | 27   |

|     | 21.1    | Overvie    | ew                                                                      | 27   |

|     |         | 21.1.1     | Reconciliation Sublayer (RS) and Media Independent Interface (MII)      |      |

|     |         | 21.1.2     | Physical Layer signaling systems                                        |      |

|     |         | 21.1.3     | Repeater                                                                |      |

|     |         | 21.1.4     | Auto-Negotiation                                                        | 28   |

|     |         | 21.1.5     | Management                                                              | 28   |

|     | 21.2    | Abbrev     | iations                                                                 | 29   |

|     | 21.3    | Referen    | ices                                                                    | 30   |

|     | 21.4    |            | ons                                                                     |      |

|     | 21.5    | State di   | agrams                                                                  | 30   |

|     |         | 21.5.1     | Actions inside state blocks                                             | 30   |

|     |         | 21.5.2     | State diagram variables                                                 |      |

|     |         | 21.5.3     | State transitions                                                       | 31   |

|     |         | 21.5.4     | Operators                                                               | 31   |

|     | 21.6    | Protoco    | l Implementation Conformance Statement (PICS) proforma                  |      |

|     |         | 21.6.1     | Introduction                                                            | 32   |

|     |         | 21.6.2     | Abbreviations and special symbols                                       | 32   |

|     |         | 21.6.3     | Instructions for completing the PICS proforma                           | 32   |

|     |         | 21.6.4     | Additional information                                                  | 33   |

|     |         | 21.6.5     | Exceptional information                                                 | 33   |

|     |         | 21.6.6     | Conditional items                                                       |      |

|     | 21.7    |            | n of 100BASE-T to other standards                                       |      |

|     | 21.8    | MAC d      | elay constraints (exposed MII)                                          | 35   |

| 22  | Recor   | nciliation | Sublayer (RS) and Media Independent Interface (MII)                     | 37   |

|     | 22.1    |            | ew                                                                      |      |

|     | 22.1    | 22.1.1     | Summary of major concepts                                               |      |

|     |         | 22.1.2     | Application                                                             |      |

|     |         | 22.1.3     |                                                                         |      |

|     |         | 22.1.4     | Rates of operation                                                      | 39   |

|     | 22.2    |            | nal specifications                                                      | 39   |

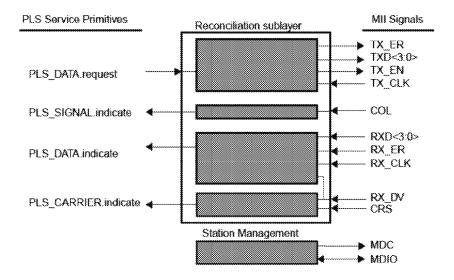

|     |         | 22.2.1     | Mapping of MII signals to PLS service primitives and Station Management | 39   |

|     |         | 22.2.2     | MII signal functional specifications                                    |      |

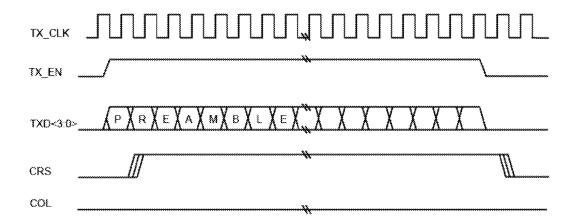

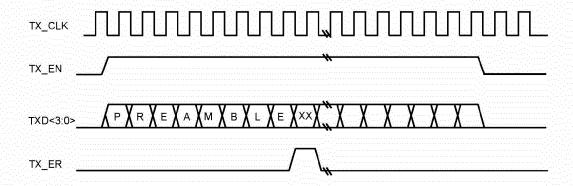

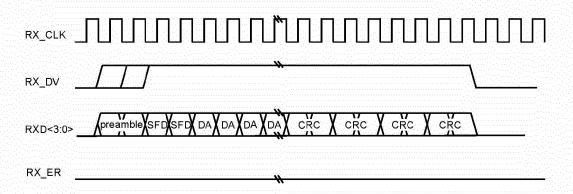

|     |         | 22.2.3     | Frame structure                                                         |      |

|     |         | 22.2.4     | Management functions                                                    |      |

|     | 22.3    | Signal t   | iming characteristics                                                   |      |

|     |         | 22,3.1     | Signals that are synchronous to TX CLK                                  |      |

|     |         | 22.3.2     | Signals that are synchronous to RX_CLK                                  | 61   |

|     |         | 22.3.3     | Signals that have no required clock relationship                        |      |

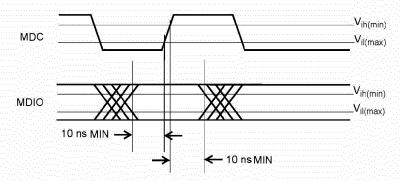

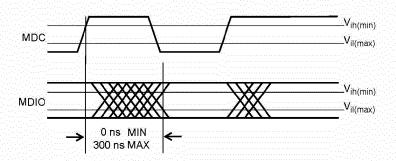

|     |         | 22,3,4     | MDIO timing relationship to MDC                                         |      |

|     | 22.4    |            | al characteristics                                                      |      |

|     |         | 22.4.1     | Signal levels                                                           |      |

|     |         | 22.4.2     | Signal paths                                                            |      |

|     |         | 22.4.3     | Driver characteristics                                                  |      |

|     |         | 22.4.4     | Receiver characteristics                                                |      |

|     |         | 22,4,5     | Cable characteristics                                                   |      |

|     |         | 22.46      | Hat investion and somewal                                               | 67   |

This is an<sub>x</sub>Archive IEEE Standard. It has been superseded by a later version of this standard.

| CL/ | AUSE         |           |                                                                                  | AUL  |

|-----|--------------|-----------|----------------------------------------------------------------------------------|------|

|     | 22.5         | Dower c   | Supply                                                                           | 6'   |

|     | 22.3         | 22.5.1    | Supply voltage                                                                   |      |

|     |              | 22.5.2    | Load current                                                                     | 67   |

|     |              | 22.5.3    | Short-circuit protection                                                         | 6    |

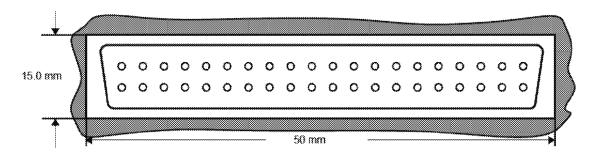

|     | 22.6         |           | nical characteristics                                                            | 65   |

|     | 22.0         | 22.6.1    | Definition of mechanical interface                                               | - 65 |

|     |              | 22.6.2    | Shielding effectiveness and transfer impedance                                   | 65   |

|     |              | 22.6.3    | Shielding effectiveness and transfer impedance  Connector pin numbering          | 60   |

|     |              | 22.6.4    | Clearance dimensions                                                             | 69   |

|     |              | 22.6.5    | Contact assignments                                                              |      |

|     | 22.7         |           | Il Implementation Conformance Statement (PICS) proforma for clause 22,           |      |

|     | 22.          | Reconc    | iliation Sublayer (RS) and Media Independent Interface (MII)                     | 7    |

|     |              | 22.7.1    | Introduction                                                                     | 71   |

|     |              | 22.7.2    | Identification                                                                   |      |

|     |              | 22.7.3    | PICS proforma tables for reconciliation sublayer and media independent interface |      |

|     |              | 22.1.3    | 1 165 proforma tables for reconcination subjayer and media independent interface | . 12 |

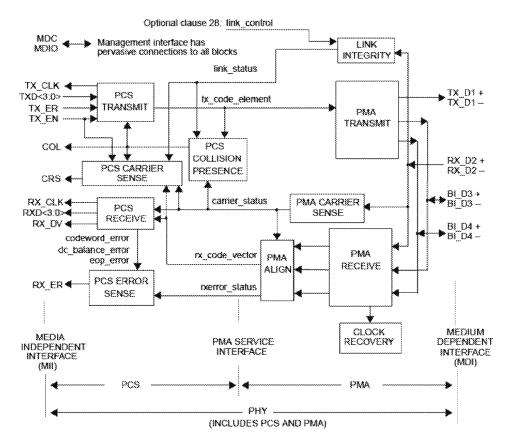

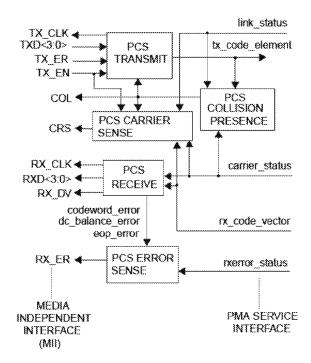

| 23  | Physic       | cal Codin | g Sublayer (PCS), Physical Medium Attachment (PMA) sublayer and                  |      |

| 25. | haseh        | and medi  | um, type 100BASE-T4                                                              | 8    |

|     | 23.1         |           | ew                                                                               |      |

|     | 23.1         | 23.1.1    | Scope                                                                            | Q    |

|     |              | 23.1.2    | Objectives                                                                       |      |

|     |              | 23.1.3    | Relation of 100BASE-T4 to other standards                                        |      |

|     |              | 23.1.4    | Summary                                                                          | Q    |

|     |              | 23.1.5    | Summary Application of 100BASE-T4                                                | Q.   |

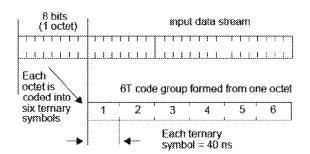

|     | 23.2         |           | nctional specifications                                                          | 84   |

|     | 23.2         | 23.2.1    | PCS functions                                                                    |      |

|     |              | 23.2.1    | PCS interfaces                                                                   |      |

|     |              | 23.2.3    | Frame structure                                                                  | 90   |

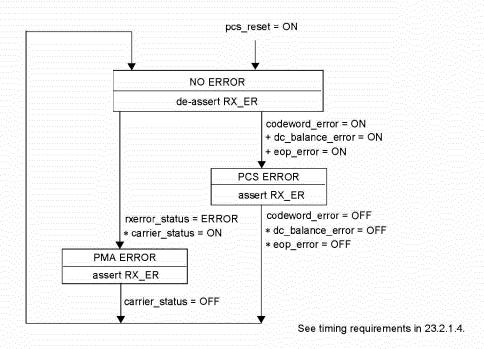

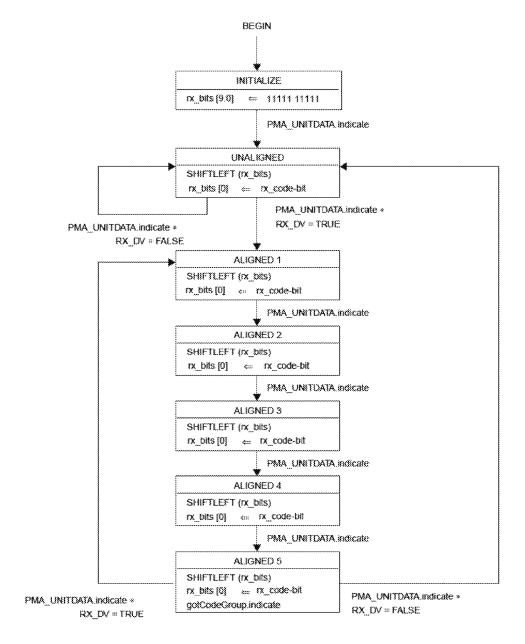

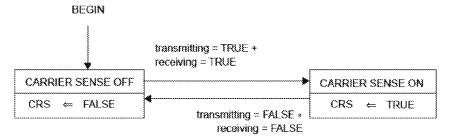

|     |              | 23.2.4    | PCS state diagrams                                                               |      |

|     |              | 23.2.5    | PCS electrical specifications                                                    |      |

|     | 23.3         |           | ervice interface                                                                 | 90   |

|     | 25.5         | 23.3.1    | PMA TYPE indicate                                                                |      |

|     |              | 23.3.2    | PMA_UNITDATA.request                                                             |      |

|     |              | 23.3.3    |                                                                                  |      |

|     |              | 23.3.4    | PMA_UNITDATA.indicate PMA_CARRIER.indicate                                       | 101  |

|     |              | 23.3.5    | PMA_LINK_indicate                                                                | 102  |

|     |              | 23.3.6    | PMA_LINK request                                                                 |      |

|     |              | 23.3.7    | PMA_RXERROR indicate                                                             | 102  |

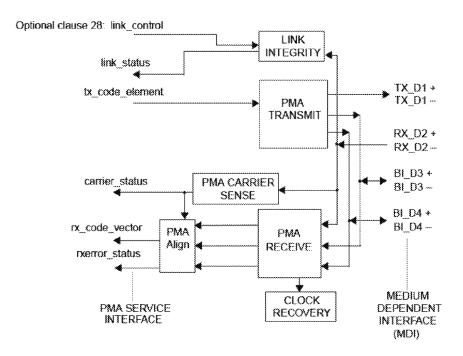

|     | 23.4         |           | inctional specifications                                                         |      |

|     | ∠3.⊤         | 23.4.1    | PMA functions                                                                    |      |

|     |              | 23.4.2    | PMA interface messages                                                           |      |

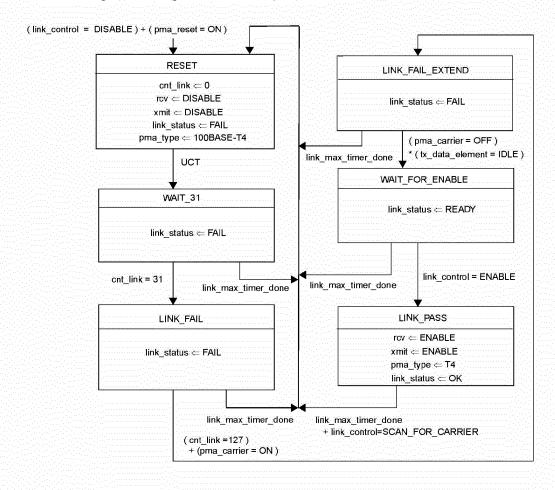

|     |              | 23.4.3    | PMA state diagrams                                                               |      |

|     | 23.5         |           | lectrical specifications                                                         | 117  |

|     | 20.0         | 23.5.1    | PMA-to-MD1 interface characteristics                                             |      |

|     |              | 23.5.1    | Power consumption                                                                |      |

|     | 23.6         |           | gment characteristics                                                            |      |

|     | <i>ل</i> ى ك | 23.6.1    | Cabling                                                                          |      |

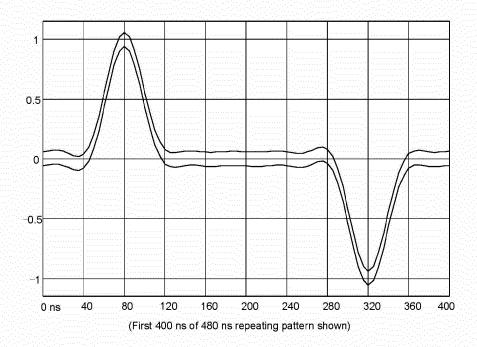

|     |              | 23.6.1    | Link transmission parameters                                                     | 124  |

|     |              | 23.6.3    | Noise                                                                            |      |

|     |              | 23.0.3    | Test Halles and the                                                              | 120  |

This is an Archive IEEE Standard. It has been superseded by a later version of this standard.

| CLI | AUSE   |           |                                                                          | PAGE                        |

|-----|--------|-----------|--------------------------------------------------------------------------|-----------------------------|

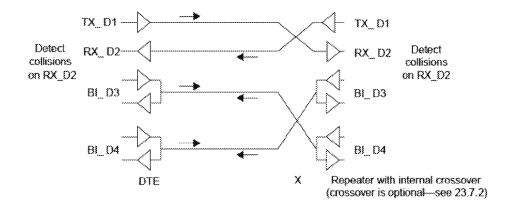

|     | 23.7   | MDI sp    | ecification                                                              | 129                         |

|     | 23.    |           | MDI connectors                                                           |                             |

|     |        | 23.7.2    | Crossover function                                                       | 130                         |

|     | 23.8   | System    | considerations                                                           | 130                         |

|     | 23.9   | Environ   | mental specifications                                                    | 130                         |

|     |        | 23.9.1    | General safety                                                           |                             |

|     |        | 23.9.2    |                                                                          |                             |

|     |        | 23.9.3    | Network safety Environment                                               | 132                         |

|     | 23.10  | PHY lal   | beling                                                                   |                             |

|     |        |           | summary                                                                  |                             |

|     |        | 23.11.1   | Timing references                                                        | 133                         |

|     |        |           | Definitions of controlled parameters                                     |                             |

|     |        | 23.11.3   | Table of required timing values                                          | 136                         |

|     | 23.12  | Protoco   | 1 Implementation Conformance Statement (PICS) proforma for clause 23,    |                             |

|     |        | Physica   | l Coding Sublayer (PCS), Physical Medium Attachment (PMA) sublayer       |                             |

|     |        | and base  | eband medium, type 100BASE-T4                                            | 143                         |

|     |        | 23.12.1   | Introduction                                                             | 143                         |

|     |        | 23.12.2   | Identification                                                           | 143                         |

|     |        | 23.12.3   | Major capabilities/options                                               | 144                         |

|     |        | 23.12.4   | PICS proforma tables for the Physical Coding Sublayer (PCS), Physical Me | dium                        |

|     |        |           | Attachment (PMA) sublayer and baseband medium, type 100BASE-T4           | 144                         |

| 24  | Dlamin | سالحال ام | a Cublar or (DCC) and Division Medium Attachment (DMA) cublar or         |                             |

| 24. |        |           | g Sublayer (PCS) and Physical Medium Attachment (PMA) sublayer,          | 1 277                       |

|     | 24.1   |           | -X<br>w                                                                  |                             |

|     | 24.1   | 24.1.1    |                                                                          |                             |

|     |        | 24.1.1    | Scope Objectives                                                         |                             |

|     |        | 24.1.2    | Relationship of 100BASE-X to other standards                             | 157<br>157                  |

|     |        | 24.1.3    | Summary of 100BASE-X sublayers                                           | 1 <i>51</i><br>1 <b>5</b> 7 |

|     |        | 24.1.5    | Inter-sublayer interfaces                                                | 150                         |

|     |        | 24.1.6    | Functional block diagram                                                 |                             |

|     |        | 24.1.7    | State diagram conventions                                                |                             |

|     | 24.2   |           | 1 Coding Sublayer (PCS)                                                  |                             |

|     | 24.2   | 24.2.1    |                                                                          |                             |

|     |        | 24.2.1    | Service Interface (MII) Functional requirements                          | 160                         |

|     |        | 24.2.3    | State variables                                                          | 160                         |

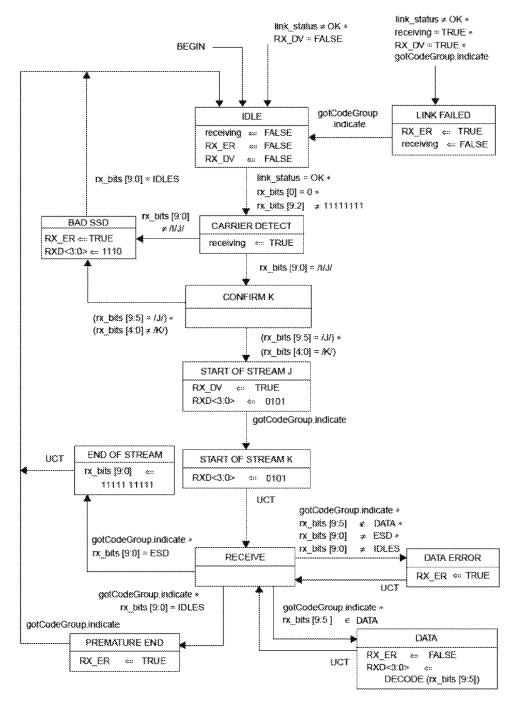

|     |        | 24.2.3    | State diagrams                                                           |                             |

|     | 24.3   |           | l Medium Attachment (PMA) sublayer                                       |                             |

|     | 27.3   | 24.3.1    | Service interface                                                        |                             |

|     |        | 24.3.2    | Functional requirements                                                  |                             |

|     |        | 24.3.3    | State variables                                                          |                             |

|     |        | 24.3.4    | Process specifications and state diagrams                                |                             |

|     | 24.4   |           | 1 Medium Dependent (PMD) sublayer service interface                      |                             |

|     | 27,7   | 24.4.1    | PMD service interface                                                    |                             |

|     |        | 24.4.2    | Medium Dependent Interface (MDI)                                         |                             |

|     | 24.5   |           | ibility considerations                                                   |                             |

|     | 24.6   |           |                                                                          |                             |

|     | 21.0   | 24.6.1    | PHY delay constraints (exposed MII)                                      | 188                         |

|     |        | 24.6.2    | DTE delay constraints (unexposed MII)                                    |                             |

|     |        | 24.6.3    | Carrier de-assertion/assertion constraint                                |                             |

|     | 24.7   |           | carrier de-assertion/assertion constraint                                | 100                         |

This is an Archive IEEE Standard. It has been superseded by a later version of this standard.

CLAUSE PAGE

|     | 24.8   | .8 Protocol Implementation Conformance Statement (PICS) proforma for clause 24,<br>Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) sublayer, |                                                                        |     |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----|

|     |        | type 100                                                                                                                                                         | DBASE-X                                                                |     |

|     |        | 24.8.1                                                                                                                                                           | Introduction                                                           | 190 |

|     |        | 24.8.2                                                                                                                                                           | Identification                                                         | 190 |

|     |        | 24.8.3                                                                                                                                                           | PICS proforma tables for the Physical Coding Sublayer (PCS) and        |     |

|     |        |                                                                                                                                                                  | Physical Medium Attachment (PMA) sublayer, type 100BASE-X              | 191 |

| 25. | Physic | cal Mediu                                                                                                                                                        | m Dependent (PMD) sublayer and baseband medium, type 100BASE-TX        | 193 |

|     | 25.1   | Overvie                                                                                                                                                          | W                                                                      | 193 |

|     | 25.2   | Function                                                                                                                                                         | nal specifications                                                     | 193 |

|     | 25.3   | General                                                                                                                                                          | exceptions                                                             | 193 |

|     | 25.4   |                                                                                                                                                                  | requirements and exceptions                                            |     |

|     |        | 25.4.1                                                                                                                                                           | Change to 7.2.3.1.1, "Line state patterns"                             |     |

|     |        | 25.4.2                                                                                                                                                           | Change to 7.2.3.3, "Loss of synchronization"                           |     |

|     |        | 25.4.3                                                                                                                                                           | Change to table 8-1, "Contact assignments for unshielded twisted pair" |     |

|     |        | 25.4.4                                                                                                                                                           | Deletion of 8.3, "Station labelling"                                   |     |

|     |        | 25,4,5                                                                                                                                                           | Change to 9.1.9, "Jitter"                                              |     |

|     |        | 25.4.6                                                                                                                                                           | Replacement of 11.2, "Crossover function"                              |     |

|     |        | 25.4.7                                                                                                                                                           | Change to A.2, "DDJ test pattern for baseline wander measurements"     | 195 |

|     |        | 25.4.8                                                                                                                                                           | Change to annex G, "Stream cipher scrambling function"                 | 195 |

|     |        | 25.4.9                                                                                                                                                           | Change to annex I, "Common mode cable termination"                     |     |

|     | 25.5   |                                                                                                                                                                  | Implementation Conformance Statement (PICS) proforma for clause 25,    | 175 |

|     | 23.3   | Physical                                                                                                                                                         | Medium Dependent (PMD) sublayer and baseband medium,                   |     |

|     |        |                                                                                                                                                                  | DBASE-TX                                                               |     |

|     |        | 25.5.1                                                                                                                                                           | Introduction                                                           |     |

|     |        | 25.5.2                                                                                                                                                           | Identification                                                         |     |

|     |        | 25.5.3                                                                                                                                                           | Major capabilities/options                                             | 197 |

|     |        | 25.5.4                                                                                                                                                           | PICS proforma tables for the Physical Medium Dependent (PMD) sublayer  |     |

|     |        |                                                                                                                                                                  | and baseband medium, type 100BASE-TX                                   | 197 |

| 26. | Physic |                                                                                                                                                                  | m Dependent (PMD) sublayer and baseband medium, type 100BASE-FX        |     |

|     | 26.1   | Overvie                                                                                                                                                          | <b>W</b>                                                               | 199 |

|     | 26.2   | Function                                                                                                                                                         | nal specifications                                                     | 199 |

|     | 26.3   | General                                                                                                                                                          | exceptions                                                             | 199 |

|     | 26.4   | Specific                                                                                                                                                         | requirements and exceptions                                            | 200 |

|     |        | 26.4.1                                                                                                                                                           |                                                                        |     |

|     |        | 26.4.2                                                                                                                                                           | Crossover function                                                     | 200 |

|     | 26.5   | Protocol                                                                                                                                                         | Implementation Conformance Statement (PICS) proforma for clause 26,    |     |

|     |        | Physical Medium Dependent (PMD) sublayer and baseband medium,                                                                                                    |                                                                        |     |

|     |        |                                                                                                                                                                  | )BASE-FX                                                               | 201 |

|     |        | 26.5.1                                                                                                                                                           | Introduction                                                           |     |

|     |        | 26.5.2                                                                                                                                                           | Identification                                                         | 201 |

|     |        | 26.5.3                                                                                                                                                           | Protocol summary                                                       | 201 |

|     |        | 26.5.4                                                                                                                                                           | Major capabilitics/options                                             |     |

|     |        | 26.5.5                                                                                                                                                           | PICS proforma tables for Physical Medium Dependent (PMD) sublayer      |     |

|     |        | 20.0.0                                                                                                                                                           | and baseband medium, type 100BASE-FX                                   | 202 |

|     |        |                                                                                                                                                                  |                                                                        |     |

| CLP | MOSE  |             |                                                                                   | PAGE                |  |

|-----|-------|-------------|-----------------------------------------------------------------------------------|---------------------|--|

| 27  | Rene  | iter for 10 | 00 Mb/s baseband networks                                                         | 203                 |  |

| -   | 27.1  |             |                                                                                   |                     |  |

|     |       | 27.1.1      | Scope                                                                             |                     |  |

|     |       | 27.1.2      | Application perspective                                                           | 204                 |  |

|     |       | 27.1.3      | Relationship to PHY                                                               |                     |  |

|     | 27.2  |             | iterface messages                                                                 |                     |  |

|     | 27.3  |             |                                                                                   |                     |  |

|     | 27.5  | 27 3 1      | er functional specifications                                                      | 206                 |  |

|     |       | 27.3.2      | Detailed repeater functions and state diagrams                                    |                     |  |

|     | 27.4  |             | er electrical specifications                                                      |                     |  |

|     | -     | 27.4.1      | Electrical isolation                                                              | 224                 |  |

|     | 27.5  |             | nmental specifications                                                            |                     |  |

|     | 27.5  | 27.5.1      | General safety                                                                    |                     |  |

|     |       | 27.5.2      | Network safety                                                                    |                     |  |

|     |       | 27.5.3      | Electrical isolation                                                              |                     |  |

|     |       | 27.5.4      | Reliability                                                                       |                     |  |

|     |       | 27.5.5      | Environment                                                                       |                     |  |

|     | 27.6  |             | er labeling                                                                       |                     |  |

|     | 27.7  |             | I Implementation Conformance Statement (PICS) proforma for clause 27,             | . 220               |  |

|     | 27.7  |             | er for 100 Mb/s baseband networks                                                 | 227                 |  |

|     |       | 27.7.1      | Introduction                                                                      |                     |  |

|     |       | 27.7.2      | Identification                                                                    |                     |  |

|     |       | 27.7.3      | Major capabilities/options                                                        | 229                 |  |

|     |       | 27.7.4      | PICS proforma tables for the Repeater for 100 Mb/s baseband networks              | 229                 |  |

| 28  | Phyci | cal Laver   | link signaling for 10 Mb/s and 100 Mb/s Auto-Negotiation on twisted pair          | 235                 |  |

| ∠o. | 28.1  | -           | This signating for 10 Mb/s and 100 Mb/s Auto-Negotiation on twisted pair          |                     |  |

|     | 20,1  | 28.1.1      | Scope                                                                             |                     |  |

|     |       | 28.1.2      | Application perspective/objectives                                                |                     |  |

|     |       | 28.1.3      | Relationship to ISO/IEC 8802-3                                                    |                     |  |

|     |       | 28.1.4      | Compatibility considerations                                                      |                     |  |

|     | 28.2  |             | nal specifications                                                                |                     |  |

|     | 20.2  | 28.2.1      | Transmit function requirements                                                    |                     |  |

|     |       | 28.2.1      |                                                                                   |                     |  |

|     |       | 28.2.3      | Receive function requirements  Arbitration function requirements                  | . 242               |  |

|     |       | 28.2.4      | Management function requirements                                                  | 244                 |  |

|     |       | 28 2 5      | Absence of management function                                                    | 240<br>253          |  |

|     |       | 28.2.6      |                                                                                   | 200                 |  |

|     | 28.3  |             | Technology-Dependent Interface                                                    |                     |  |

|     | 28.3  |             | agrams and variable definitions                                                   | . Z33               |  |

|     |       | 28.3.1      |                                                                                   |                     |  |

|     |       | 28.3.2      | State diagram timers                                                              |                     |  |

|     |       | 28.3.3      | State diagram counters                                                            |                     |  |

|     | 20.4  | 28.3.4      | State diagrams                                                                    |                     |  |

|     | 28.4  |             | al specifications                                                                 | . 260               |  |

|     | 28.5  |             | Implementation Conformance Statement (PICS) proforma for clause 28,               | 265                 |  |

|     |       |             | ll Layer link signaling for 10 Mb/s and 100 Mb/s Auto-Negotiation on twisted pair |                     |  |

|     |       | 28.5.1      | Introduction                                                                      | 267                 |  |

|     |       | 28.5.2      | Identification                                                                    |                     |  |

|     |       | 28.5.3      | Major capabilities/options                                                        | 268                 |  |

|     |       | 28.5.4      | PICS proforma tables for Physical Layer link signaling for                        |                     |  |

|     | 20.   | ¥.          | 10 Mb/s and 100 Mb/s Auto-Negotiation on twisted pair                             | 268<br>2 <b>9</b> 0 |  |

|     | 286   | A TITO N    | AGAIGITAN AVNOUCIAN                                                               | 771                 |  |

This is an<sub>x</sub>Archive IEEE Standard. It has been superseded by a later version of this standard.

| CLAUSE     |                                                                           | PAGE |  |  |  |

|------------|---------------------------------------------------------------------------|------|--|--|--|

| 20 Syctor  | n considerations for multi-segment 100BASE-T networks                     | 281  |  |  |  |

| 29.1       | Overview                                                                  |      |  |  |  |

| 27.1       | 29.1.1 Single collision domain multi-segment networks                     |      |  |  |  |

|            | 29.1.2 Repeater usage                                                     | 283  |  |  |  |

| 29.2       | Transmission System Model 1                                               |      |  |  |  |

| 29.3       | Transmission System Model 2                                               |      |  |  |  |

|            | 29.3.1 Round-trip collision delay                                         |      |  |  |  |

| 30. Laver  | Layer Management for 10 Mb/s and 100 Mb/s                                 |      |  |  |  |

| 30.1       | Overview                                                                  |      |  |  |  |

|            | 30.1.1 Scope                                                              | 290  |  |  |  |

|            | 30.1.2 Relationship to objects in IEEE Std 802.1F-1993                    | 290  |  |  |  |

|            | 30.1.3 Systems management overview                                        |      |  |  |  |

|            | 30.1.4 Management model                                                   |      |  |  |  |

| 30.2       | Managed objects                                                           | 292  |  |  |  |

|            | 30.2.1 Introduction                                                       | 292  |  |  |  |

|            | 30.2.2 Overview of managed objects                                        | 292  |  |  |  |

|            | 30.2.3 Containment                                                        | 295  |  |  |  |

|            | 30.2.4 Naming                                                             | 296  |  |  |  |

|            | 30.2.5 Capabilities                                                       | 296  |  |  |  |

| 30.3       | Layer management for 10 Mb/s and 100 Mb/s DTEs                            | 302  |  |  |  |

|            | 30.3.1 MAC entity managed object class                                    | 302  |  |  |  |

|            | 30.3.2 PHY entity managed object class                                    | 309  |  |  |  |

| 30.4       | Layer management for 10 Mb/s and 100 Mb/s baseband repeaters              |      |  |  |  |

|            | 30.4.1 Repeater managed object class                                      | 312  |  |  |  |

|            | 30.4.2 Group managed object class                                         | 316  |  |  |  |

|            | 30.4.3 Repeater port managed object class                                 | 317  |  |  |  |

| 30.5       | Layer management for 10 Mb/s and 100 Mb/s MAUs                            |      |  |  |  |

|            | 30.5.1 MAU managed object class                                           |      |  |  |  |

| 30.6       | Management for link Auto-Negotiation                                      |      |  |  |  |

|            | 30.6.1 Auto-Negotiation managed object class                              | 326  |  |  |  |

| ANNEXES    |                                                                           |      |  |  |  |

| 22A (infor | mative) MII output delay, setup, and hold time budget                     | 331  |  |  |  |

| 22B (infor | mative) MII driver ac characteristics                                     | 334  |  |  |  |

| 22C (infor | mative) Measurement techniques for MII signal timing characteristics      | 336  |  |  |  |

| 23A (norn  | native) 6T code words                                                     | 338  |  |  |  |

| 23B (infor | mative) Noise budget                                                      | 340  |  |  |  |

|            | mative) Use of cabling systems with a nominal differential characteristic |      |  |  |  |

|            | impedance of 120                                                          | 341  |  |  |  |

| 27A (norm  | native) Repeater delay consistency requirements                           | 342  |  |  |  |

| 20 A (norn | rative) Selector Field definitions                                        | 3/13 |  |  |  |

This is an Archive IEEE Standard. It has been superseded by a later version of this standard.

| ANN | EXES          |                                                     | PAGE |

|-----|---------------|-----------------------------------------------------|------|

| 28B | (normative)   | IEEE 802.3 Selector Base Page definition            | 344  |

| 28C | (normative)   | Next Page Message Code Field definitions            | 346  |

| 29A | (informative) | DTE and repeater delay components                   | 348  |

|     |               | Recommended topology documentation                  |      |

| 30A | (normative)   | GDMO specification for 802.3 managed object classes | 350  |

| 30B | (normative)   | GDMO and ASN 1 definitions for management           | 389  |

# IEEE Standards for Local and Metropolitan Area Networks:

# Supplement to Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications

# Revisions to ISO/IEC 8802-3 : 1993 [ANSI/IEEE Std 802.3, 1993 Edition]

#### EDITORIAL NOTES

- 1—The following changes to ISO/IEC 8802-3: 1993 [ANSI/IEEE Std 802.3, 1993 Edition] (and supplements 802.3j-1993, 802.3k-1992, 802.3k-1992, and 802.3p&q-1993) affect clauses 1, 2, 4, 5, 14, 19, 20, Annex A, and Annex D. These changes must also be applied to the 1995 edition of ISO/IEC 8802-3, which will incorporate all the supplements.

- 2—The text as shown includes editorial changes that accommodate recent changes to the IEEE style.

- 3—Editing instructions are shown in **bold italic** type. Where modifications are made to paragraphs of existing text, deletions are shown in strikethrough type and additions are <u>underscored</u>. Editorial notes will not be carried over into future editions.

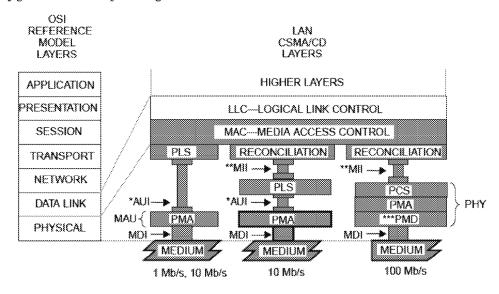

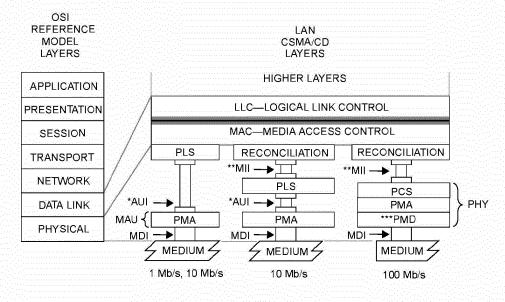

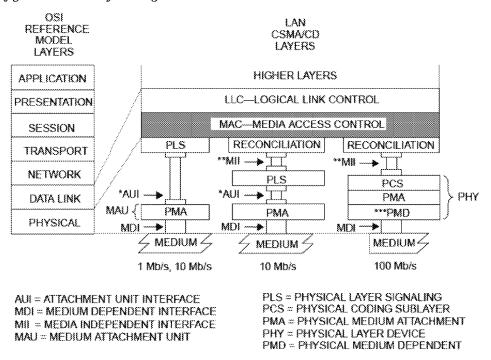

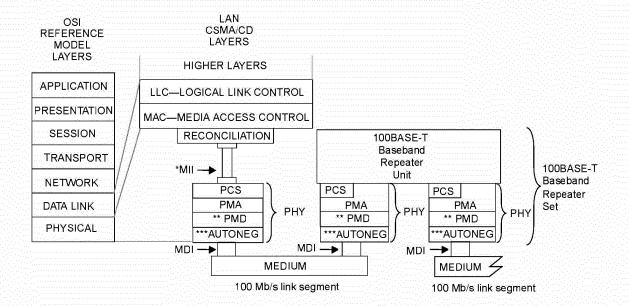

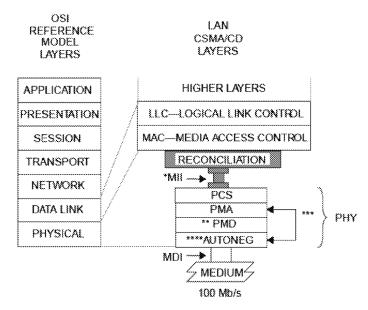

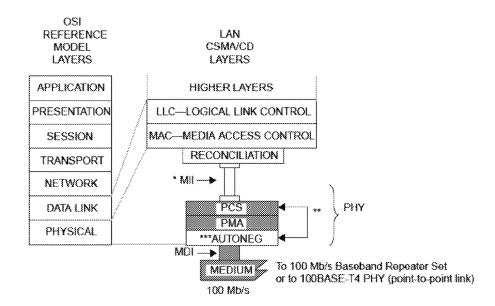

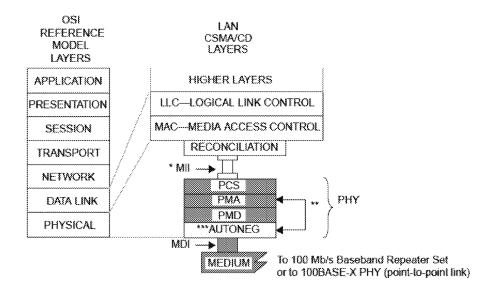

# Replace figure 1-1 with the following:

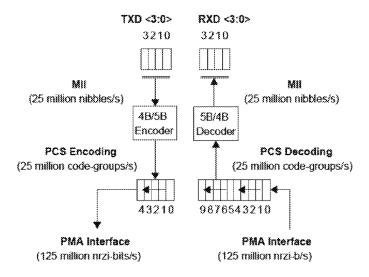

AUI = ATTACHMENT UNIT INTERFACE MDI = MEDIUM DEPENDENT INTERFACE MII = MEDIA INDEPENDENT INTERFACE MAU = MEDIUM ATTACHMENT UNIT

PLS = PHYSICAL LAYER SIGNALING PCS = PHYSICAL CODING SUBLAYER PMA = PHYSICAL MEDIUM ATTACHMENT PHY = PHYSICAL LAYER DEVICE PMD = PHYSICAL MEDIUM DEPENDENT

- NOTE—The three types of layers below the MAC sublayer are mutually independent.

- \* AUI is optional for 10 Mb/s systems and is not specified for 1 Mb/s and 100 Mb/s systems.

- \*\* MII is optional for 10 Mb/s DTEs and for 100 Mb/s systems and is not specified for 1 Mb/s systems.

- \*\*\* PMD is specified for 100BASE-X only; 100BASE-T4 does not use this layer. For an exposed AUI residing below an MII, see 22.5.

Figure 1-1—LAN standard relationship to the ISO Opens Systems Interconnection (OSI) reference model

# Change 1.1.1 to read as follows:

The Carrier Sense Multiple Access with Collision Detection (CSMA/CD) media access method is the means by which two or more stations share a common transmission medium. To transmit, a station waits (defers) for a quiet period on the medium (that is, no other station is transmitting) and then sends the intended message in bit-serial form. If, after initiating a transmission, the message collides with that of another station, then each transmitting station intentionally sends a few additional bytes transmits for an additional predefined period to ensure propagation of the collision throughout the system. The station remains silent for a random amount of time (backoff) before attempting to transmit again. Each aspect of this access method process is specified in detail in subsequent sections of this standard.

This is a comprehensive standard for Local Area Networks employing CSMA/CD as the access method. This standard is intended to encompass several media types and techniques for signal rates of from 1 Mb/s to 20 Mb/s 100 Mb/s. This edition of the standard provides the necessary specifications for 10 Mb/s baseband and broadband systems, a 1 Mb/s baseband system, and a Repeater Unit. three families of systems: a 1 Mb/s baseband system, 10 Mb/s baseband and broadband systems, and a 100 Mb/s baseband system.

#### Change 1.1.2.2 to read as follows:

Two Three important compatibility interfaces are defined within what is architecturally the Physical Layer.

- a) Medium Dependent Interfaces (MDI). To communicate in a compatible manner, all stations shall adhere rigidly to the exact specification of physical media signals defined in Section clause 8 (and beyond) in this standard, and to the procedures that define correct behavior of a station. The medium-independent aspects of the LLC sublayer and the MAC sublayer should not be taken as detracting from this point; communication by way of the ISO/IEC 8802-3 [ANSI/IEEE Std 802.3] Local Area Network requires complete compatibility at the Physical Medium interface (that is, the coaxial physical cable interface).

- b) Attachment Unit Interface (AUI). It is anticipated that most DTEs will be located some distance from their connection to the coaxial physical cable. A small amount of circuitry will exist in the Medium Attachment Unit (MAU) directly adjacent to the coaxial physical cable, while the majority of the hardware and all of the software will be placed within the DTE. The AUI is defined as a second compatibility interface. While conformance with this interface is not strictly necessary to ensure communication, it is highly recommended, since it allows maximum flexibility in intermixing MAUs and DTEs. The AUI may be optional or not specified for some implementations of this standard that are expected to be connected directly to the medium and so do not use a separate MAU or its interconnecting AUI cable. The PLS and PMA are then part of a single unit, and no explicit AUI implementation is required.

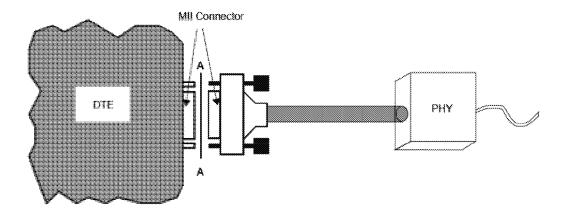

- c) Media Independent Interface (MII). It is anticipated that some DTEs will be connected to a remote PHY, and/or to different medium dependent PHYs. The MII is defined as a third compatibility interface. While conformance with implementation of this interface is not strictly necessary to ensure communication, it is highly recommended, since it allows maximum flexibility in intermixing PHYs and DTEs. The MII is optional.

#### 1.3 References

#### Replace 1.3 with the following:

The following standards contain provisions which, through references in this text, constitute provisions of this International Standard. At the time of publication, the editions indicated were valid. All standards are subject to revision, and parties to agreements based on this International Standard are encouraged to investigate the possibility of applying the most recent editions of the standards listed below. Members of IEC and ISO maintain registers of currently valid International Standards.

EDITORIAL NOTE—In the following references, changes are not indicated by strikethroughs and underscores.

ANSI X3.237-1995, Rev 2.1 (1 January 1995), FDDI Low-Cost Fibre Physical Layer—Medium Dependent (LCF-PMD) (ISO/IEC CD 9314-9).

ANSI X3.263: 1995, Revision 2.2 (1 March 1995), FDDI Twisted Pair—Physical Medium Dependent (TP-PMD) (ISO/IEC CD 9314-10).

CISPR 22: 1993, Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment.<sup>1</sup>

IEC 60, High-voltage test techniques.<sup>2</sup>

IEC 68, Basic environmental testing procedures.

IEC 96-1: 1986, Radio-frequency cables, Part 1: General requirements and measurement methods, and Amendment 2: 1993.

IEC 169-8: 1978 and -16: 1982, Radio-frequency connectors, Part 8: Radio-frequency coaxial connectors with inner diameter of outer conductor 6.5 mm (0.256 in) with bayonet lock—Characteristic impedence 50 ohms (Type BNC) and Part 16: Radio-frequency coaxial connectors with inner diameter of outer conductor 7 mm (0.276 in) with screw coupling—Characteristic impedence 50 ohms (75 ohms) (Type N).

IEC 380: 1985, Safety of electrically energized office machines.<sup>3</sup>

IEC 435: 1983, Safety of data processing equipment.<sup>4</sup>

IEC 603-7: 1990, Connectors for frequencies below 3 MHz for use with printed boards, Part 7: Detail specification for connectors, 8-way, including fixed and free connectors with common mating features.

IEC 793-1: 1992, Optical fibres, Part 1: Generic specification.

IEC 793-2: 1989. Optical fibres, Part 2: Product specifications.<sup>5</sup>

IEC 794-1: 1993. Optical fibre cables, Part 1: Generic specification.

IEC 794-2: 1989. Optical fibre cables, Part 2: Product specifications.

IEC 807-2: 1992, Rectangular connectors for frequencies below 3 MHz, Part 2: Detail specification for a range of connectors with assessed quality, with trapezoidal shaped metal shells and round contacts—Fixed solder contact types.

IEC 825-1: 1993, Safety of laser products, Part 1: Equipment classification, requirements and user's guide.

<sup>&</sup>lt;sup>1</sup>CISPR documents are available from the International Electrotechnical Commission, 3 rue de Varembé, Case Postale 131, CH 1211, Genève 20, Switzerland/Suisse. CISPR documents are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

<sup>&</sup>lt;sup>2</sup>IEC publications are available from International Electrotechnical Commission. IEC publications are also available in the United States from the American National Standards Institute.

<sup>&</sup>lt;sup>3</sup>IEC 380: 1985 was withdrawn in 1991. It has been replaced by IEC 950: 1991.

<sup>&</sup>lt;sup>4</sup>IEC 435: 1983 was withdrawn in 1991. It has been replaced by IEC 950: 1991.

<sup>&</sup>lt;sup>5</sup>Subclause 9.9 is to be read with the understanding that the following changes to IEC 793-2: 1989 have been requested: a) Correction of the numerical aperture tolerance in table III to  $\pm 0.015$ ; and b) Addition of another bandwidth category of 150 MHz referred to 1 km, for the type A1b fibre in table III.

IEC 874-1: 1993, Connectors for optical fibres and cables, Part 1: Generic specification.

IEC 874-2: 1993, Connectors for optical fibres and cables, Part 2: Sectional specification for fibre optic connector—Type F-SMA.

IEC 950: 1991, Safety of information technology equipment, including electrical business equipment.<sup>6</sup>

IEC 1076-3-101: 1995 [48B Secretariat 276], Detail specification for a range of shielded connectors with trapezoidal shaped shells and nonremovable rectangular contacts on a  $1.27 \times 2.54$  millimeter centerline.<sup>7</sup>

IEEE Std 802-1990, IEEE Standards for Local and Metropolitan Area Networks: Overview and Architecture (ANSI).<sup>8</sup>

IEEE Std 802.1F-1993, IEEE Standards for Local and Metropolitan Area Networks: Common Definitions and Procedures for IEEE 802 Management Information (ANSI).

ISO 2382-9: 1984, Data processing—Vocabulary—Part 9: Data communications. 9

ISO 7498: 1984, Information processing systems—Open Systems Interconnection—Basic Reference Model.

ISO/IEC 8824: 1990, Information technology—Open Systems Interconnection—Specification of Abstract Syntax Notation One (ASN.1).

ISO/IEC 8825: 1990, Information technology—Open Systems Interconnection—Specification of Basic Encoding Rules for Abstract Syntax Notation One (ASN.1).

ISO 9314-1: 1989, Information processing systems—Fibre Distributed Data Interface (FDDI)—Part 1: Token Ring Physical Layer Protocol (PHY).

ISO 9314-2: 1989, Information processing systems—Fibre Distributed Data Interface (FDDI)—Part 2: Token Ring Media Access Control (MAC).

ISO 9314-3: 1990, Information processing systems—Fibre Distributed Data Interface (FDDI)—Part 3: Physical Layer Medium Dependent (PMD).

ISO/IEC 10040: 1992, Information technology—Open Systems Interconnection—Systems management overview.

ISO/IEC 10164-1: 1993, Information technology—Open Systems Interconnection—Systems management—Object Management Function.

ISO/IEC 10165-1: 1993, Information technology—Open Systems Interconnection—Management information services—Structure of management information—Management Information Model.

ISO/IEC 10165-2: 1992, Information technology—Open Systems Interconnection—Management information services—Structure of management information—Definition of management information.

<sup>&</sup>lt;sup>6</sup>IEC 950: 1991 replaces IEC 380: 1985 and 435: 1983.

<sup>&</sup>lt;sup>7</sup>Presently this is a committee draft.

<sup>&</sup>lt;sup>8</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, Service Center, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA.

<sup>&</sup>lt;sup>9</sup>ISO and ISO/IEC publications are available from the International Organization for Standardization, Case Postale 56, 1 rue de Varembé, CH-1211, Genéve 20, Switzerland/Suisse. They are also available in the United States from the American National Standards Institute.

CSMA/CD

ISO/IEC 10165-4: 1992, Information technology—Open Systems Interconnection—Management information services—Structure of management information—Part 4: Guidelines for the definition of managed objects.

ISO/IEC 7498-4: 1989, Information processing systems—Open Systems Interconnection—Basic Reference Model—Part 4: Management framework.

ISO/IEC 8877: 1992, Information technology—Telecommunications and information exchange between systems—Interface connector and contact assignments for ISDN Basic Access Interface located at reference points S and T.

ISO/IEC 9646-1: 1994, Information technology—Open Systems Interconnection—Conformance testing methodology and framework—Part 1: General concepts.

ISO/IEC 9646-2: 1994, Information technology—Open Systems Interconnection—Conformance testing methodology and framework—Part 2: Abstract Test Suite specification.

ISO/IEC 10165-4: 1992, Information technology—Open Systems Interconnection—Structure of management information—Part 4: Guidelines for the definition of managed objects.

ISO/IEC 11801: 1995, Information technology—Generic cabling for customer premises.

NOTE—Local and national standards such as those supported by ANSI, EIA, IEEE, MIL, NPFA, and UL are not a formal part of the ISO/IEC 8802-3 standard except where no international standard equivalent exists. Reference to such local or national standards may be useful resource material and are located in annex A.

#### 1.4 Definitions

EDITORIAL NOTE—The definitions subclauses within several clauses of ISO/IEC 8802-3 are consolidated in this revised clause. In the following definitions, changes are not indicated by strikethroughs and underscores. See the end of this subclause for further editing instructions.

# Replace 1.4 with the following text:

- **1.4.1 100BASE-FX:** IEEE 802.3 Physical Layer specification for a 100 Mb/s CSMA/CD LAN over two optical fibers. (See IEEE 802.3 clauses 24 and 26.)

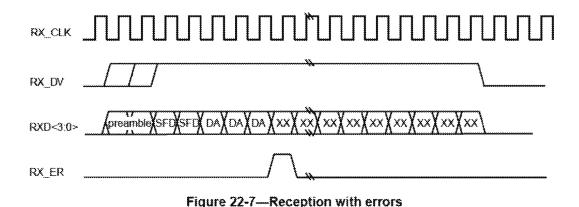

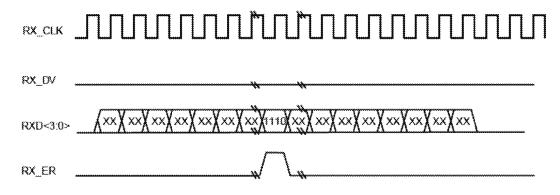

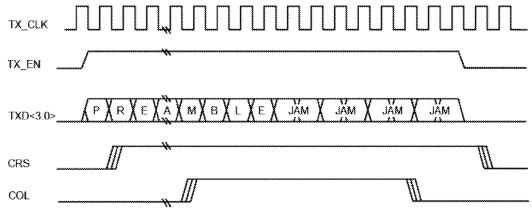

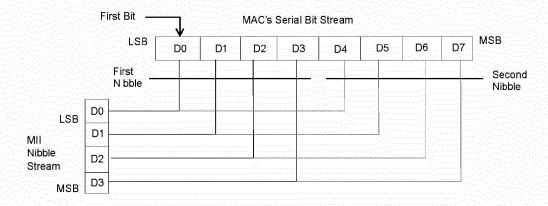

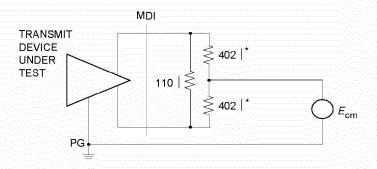

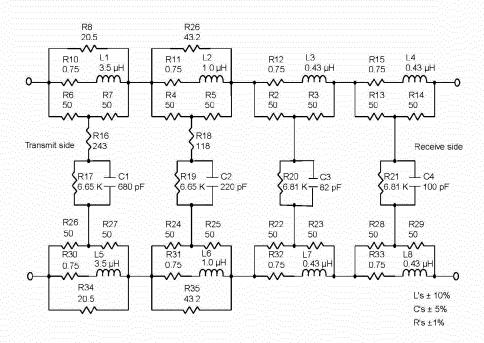

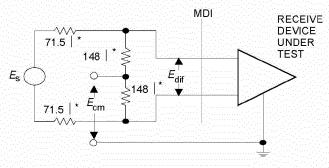

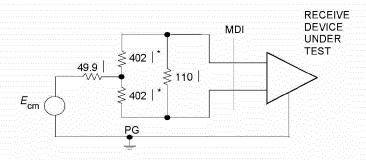

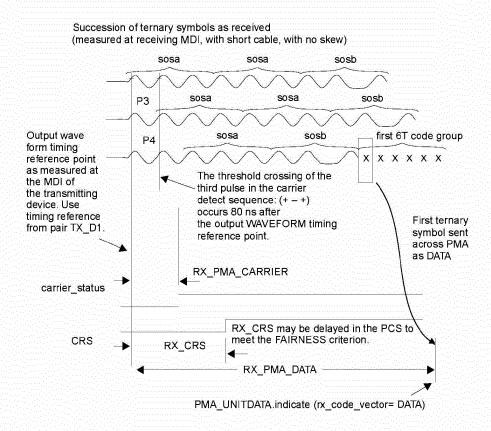

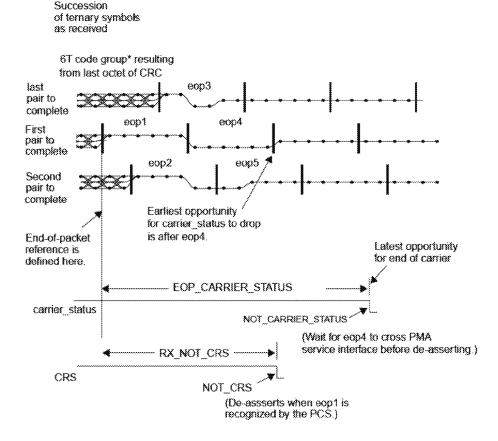

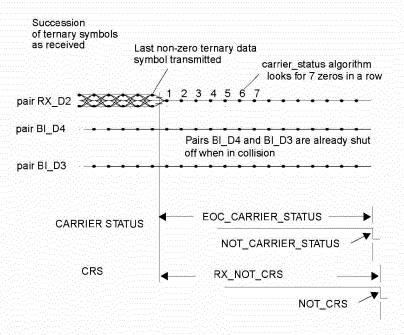

- **1.4.2 100BASE-T:** IEEE 802.3 Physical Layer specification for a 100 Mb/s CSMA/CD LAN. (See IEEE 802.3 clauses 22 and 28.)