| 1   | David C. Marcus (SBN 158704)                                 |

|-----|--------------------------------------------------------------|

| ~   | david.marcus@wilmerhale.com                                  |

| 2   | James M. Dowd (SBN 259578)                                   |

| 3   | james.dowd@wilmerhale.com                                    |

|     | Matthew J. Hawkinson (SBN 248216)                            |

| 4   | matthew.hawkinson@wilmerhale.com Aaron Thompson (SBN 272391) |

| 5   | aaron.thompson@wilmerhale.com                                |

| 3   | WILMER CUTLER PICKERING                                      |

| 6   | HALE AND DORR LLP                                            |

| 7   | 350 South Grand Avenue, Suite 2100                           |

| 1   | Los Angeles, CA 90071                                        |

| 8   | Telephone: (213) 443-5300                                    |

| 9   | Facsimile: (213) 443-5400                                    |

| 9   | William F. Lee (pro hac vice)                                |

| 10  | william.lee@wilmerhale.com                                   |

|     | WILMER CUTLER PICKERING                                      |

| 11  | HALE AND DORR LLP                                            |

| 12  | 60 State Street                                              |

| 132 | Boston, MA 02109                                             |

| 13  | Telephone: (617) 526-6000                                    |

| 14  | Facsimile: (617) 526-5000                                    |

|     | Attorneys for Defendants and Counterclaim-Plaintiffs         |

| 15  | Hughes Communications Inc.                                   |

| 16  | Hughes Network Systems LLC                                   |

|     | DISH Network Corporation,                                    |

| 17  | DISH Network LLC, and                                        |

| 18  | dishNET Satellite Broadband LLC                              |

|     | Additional Counsel Listed on Signature Page                  |

| 19  | Additional Counsel Listed on Signature Page                  |

| 20  |                                                              |

| 20  |                                                              |

| 21  |                                                              |

| 22  |                                                              |

| 23  |                                                              |

| 24  | Apple 1115                                                   |

Expert Report of Dr. Brendan Frey Case No. 2:13-cv-07245-MRP-JEM

# UNITED STATES DISTRICT COURT 2 CENTRAL DISTRICT OF CALIFORNIA 3 THE CALIFORNIA INSTITUTE OF 4 TECHNOLOGY, 5 Plaintiff and Counter-Defendant, 6 VS. 7 HUGHES COMMUNICATIONS INC., HUGHES NETWORK SYSTEMS LLC, DISH NETWORK CORPORATION, 9 DISH NETWORK LLC, and DISHNET SATELLITE BROADBAND LLC, 10 11 Defendants and Counter-Plaintiffs. 12 13 14 15 16 17 18 19 20 21 22 23

24

Case No. 2:13-cv-07245-MRP-JEM

EXPERT REPORT OF DR. BRENDAN FREY REGARDING INVALIDITY OF PATENTS-IN-SUIT

### EXPERT REPORT OF DR. BRENDAN FREY REGARDING INVALIDITY OF PATENTS-IN-SUIT

2

3

1

#### SUMMARY OF REPORT I.

4 5

6

7

8

9

10

11

12

13

14

15

16

17

18 19

20

21

22

23

24

I have been retained as an expert in this case by counsel for Defendants and Counter-Plaintiffs Hughes Communications Inc., Hughes Network Systems LLC, DISH Network Corporation, DISH Network LLC, and dishNET Satellite Broadband LLC (collectively, "Defendants"). I expect to testify at trial about the matters set forth in this report, if asked about these matters by the Court or by the parties' attorneys.

- I understand that the Plaintiff and Counter-Defendant in this proceeding, the California Institute of Technology ("Plaintiff" or "Caltech") has asserted against Defendants the following four patents:

- U.S. Patent No. 7,116,710 (the "'710 patent");

- U.S. Patent No. 7,421,032 (the "'032 patent");

- U.S. Patent No. 7,916,781 (the "'781 patent"); and

- U.S. Patent No. 8,284,833 (the "833 patent").

- I further understand that Plaintiff has asserted the following claims: 3.

- claims 1, 4, 6, 15, 20, and 22 of the '710 patent;

- claims 1, 18, 19, and 22 of the '032 patent;

- claims 16 and 19 of the '781 patent; and

- claims 1, 2, 4, and 8 of the '833 patent.

- I have been asked for my expert opinion on whether the claims listed in the preceding paragraph (the "asserted claims") are valid. In my opinion, all of the asserted claims are invalid for the reasons stated below.

- 5. I have also been asked for my opinion on whether various documents, including an email from an inventor dated March 7, 2000, demonstrate conception

of the claimed invention. In my opinion, these documents do not demonstrate conception for the reasons stated below.

6. I have also been asked for my opinion regarding whether three references (two by Luby et al. and one by Richardson et al.) were material to the claimed invention. In my opinion, as explained below, these three references, none of which were before the patent office during prosecution of the asserted patents, were material to the claimed invention.

#### BACKGROUND

### A. Qualifications and Experience

- 7. I received a B.Sc. with Honors in Electrical Engineering from the University of Calgary in 1990, a M.Sc. in Electrical and Computer Engineering from the University of Manitoba in 1993, and a Ph.D. in Electrical and Computer Engineering from the University of Toronto in 1997. Since July 2001, I have been at the University of Toronto, where I am a Professor of Electrical and Computer Engineering and Computer Science.

- 8. During my career I have conducted research in the areas of graphical models, error-correcting coding, machine learning, genome biology and computer vision. I have authored more than 200 publications and am named as an inventor on nine patents issued by the U.S. Patent and Trademark Office.

- 9. I have received a number of honors and awards for the research I have conducted. In 2008, I was named a Fellow of the Institute for Electrical and Electronic Engineers (IEEE), an honor given to a person with an "extraordinary record or accomplishments" in the field of electrical engineering. In 2009, I was named a Fellow of the American Association for the Advancement of Science (AAAS), an honor that recognizes "efforts on behalf of the advancement of science or its applications which are scientifically or socially distinguished."

- 10. In 2009, I was awarded a Steacie Fellowship for my work on the theory and implementation of artificial and natural mechanisms for inferring patterns from data. The Steacie Fellowship is awarded by the Natural Sciences and Engineering Research Council of Canada (NSERC) to "outstanding and highly promising scientists and engineers" who are faculty members of Canadian universities. In 2011, I received the NSERC's John C. Polanyi Award, in recognition of my research on inferring genetic codes embedded in DNA that direct activities within cells.

- 11. Throughout my career I have received funding from various governmental agencies to support my research, including the Natural Sciences and Engineering Research Council of Canada, the Canadian Institutes of Health Research, and the Canadian Institute for Advanced Research.

- 12. A copy of my curriculum vitæ is attached to this report as Exhibit A.

#### B. Understanding of the Law

13. I am not an attorney. For the purposes of this report, I have been informed about certain aspects of the law that are relevant to my analysis and opinions. My understanding of the law is as follows:

#### i) Invalidity in General

14. A patent is presumed valid, and a challenger to the validity of a patent must show invalidity of the patent by clear and convincing evidence. Clear and convincing evidence is evidence that makes a fact highly probable.

### ii) Anticipation

15. A patent claim is invalid if it is "anticipated" by prior art. For the claim to be invalid because it is anticipated, all of its requirements must have existed in a single device or method that predates the claimed invention, or must have been described in a single publication or patent that predates the claimed invention.

22

23

24

- 16. The description in a written reference does not have to be in the same words as the claim, but all of the requirements of the claim must be there, either stated or necessarily implied, so that someone of ordinary skill in the art, looking at that one reference would be able to make and use the claimed invention.

- 17. A patent claim is also anticipated if there is clear and convincing proof that, more than one year before the filing date of the patent, the claimed invention was: in public use or on sale in the United States; patented anywhere in the world; or described in a printed publication anywhere in the world. This is called a statutory bar.

#### iii) Obviousness

- 18. A patent claim is invalid if the claimed invention would have been obvious to a person of ordinary skill in the art at the time the application was filed. This means that even if all of the requirements of a claim cannot be found in a single prior art reference that would anticipate the claim or constitute a statutory bar to that claim, the claim is invalid if it would have been obvious to a person of ordinary skill who knew about the prior art.

- 19. The determination of whether a claim is obvious should be based upon several factors, including:

- the level of ordinary skill in the art that someone would have had at the time the claimed invention was made;

- · the scope and content of the prior art;

- what difference, if any, existed between the claimed invention and the prior art.

- 20. In considering the question of obviousness, it is also appropriate to consider any secondary considerations of obviousness or non-obviousness that may be shown. These include:

- commercial success of a product due to the merits of the claimed invention;

9

8

10 11

12

13 14

15

16

17

19

18

20 21

22

- a long felt need for the solution provided by the claimed invention;

- unsuccessful attempts by others to find the solution provided by the claimed invention;

- · copying of the claimed invention by others;

- · unexpected and superior results from the claimed invention;

- acceptance by others of the claimed invention as shown by praise from others in the field or from the licensing of the claimed invention; and

- independent invention of the claimed invention by others before or at about the same time as the named inventor thought of it.

- 21. A patent claim composed of several elements is not proved obvious merely by demonstrating that each of its elements was independently known in the prior art. In evaluating whether such a claim would have been obvious, it is relevant to consider if there would have been a reason that would have prompted a person of ordinary skill in the field to combine the elements or concepts from the prior art in the same way as in the claimed invention. For example, market forces or other design incentives may be what produced a change, rather than true inventiveness. It is also appropriate to consider:

- whether the change was merely the predictable result of using prior art elements according to their known functions, or whether it was the result of true inventiveness;

- whether there is some teaching or suggestion in the prior art to make the modification or combination of elements claimed in the patent;

- whether the innovation applies a known technique that had been used to improve a similar device or method in a similar way; or

- whether the claimed invention would have been obvious to try, meaning that

the claimed innovation was one of a relatively small number of possible

approaches to the problem with a reasonable expectation of success by those

of ordinary skill in the art.

- 22. In considering obviousness, it is important to be careful not to determine obviousness using the benefit of hindsight; many true inventions might seem obvious after the fact.

23. A single reference can alone render a patent claim obvious, if any differences between that reference and the claims would have been obvious to a person of ordinary skill in the art at the time of the alleged invention – that is, if the person of ordinary skill could readily adapt the reference to meet the claims of the patent, by applying known concepts to achieve expected results in the adaptation of the reference.

#### iv) The "Written Description" Requirement

- 24. A patent claim is invalid if the patent specification does not contain a written description of the invention to which the claim is directed. To satisfy the written description requirement, a patent specification must describe the claimed invention in sufficient detail that one of ordinary skill in the art can reasonably conclude that the inventor had possession of the claimed invention.

- 25. An applicant shows possession of the claimed invention by describing the claimed invention with all of its limitations using such descriptive means as words, structures, figures, diagrams, and formulas that fully set forth the claimed invention. A description that merely renders the invention obvious does not satisfy the written description requirement.

#### v) Inequitable Conduct and Materiality

- 26. I have been informed that during prosecution, inventors have a duty to disclose to the Patent Office all information known to the inventors that is material to the patentability of the claims being examined.

- 27. Information is deemed to be material to patentability when it is not cumulative to information already before the Patent Office, and when: (1) it establishes, by itself or in combination with other information, that a claim was unpatentable; or (2) it refutes, or is inconsistent with, a position the applicant takes

21

22

23

- Caltech's Second Supplemental Responses to Interrogatories 1-5 and Caltech's First Supplemental Responses to Interrogatories 6-11;

- Email from Brendan Frey to Dariush Divsalar dated Dec. 8, 1999 (CALTECH000024021);

- Khandekar, Aamod ("Capacity Achieving Codes on the Binary Erasure Channel") (CALTECH000007321-7349).

- Khandekar, Aamod, "Graph-based Codes and Iterative Decoding," thesis dated June 10, 2002.

- McEliece Email dated March 7, 2000 (CALTECH000008667)

- Luby, M. et al., "Practical Loss-Resilient Codes," STOC '97 (1997)

- Luby, M. et al., "Analysis of Low Density Codes and Improved Designs Using Irregular Graphs," STOC '98, p. 249-259 (1998)

- Richardson, T. et al. "Design of provably good low-density parity check codes," *IEEE Transactions on Information Theory* (1999) (preprint)

- 29. Level of Ordinary Skill in the Art

- 30. In my opinion, based on the materials and information I have reviewed, and on my extensive experience working with people in the technical areas relevant to the patents-in-suit (*i.e.* in the field of code design), a person of ordinary skill in the art is a person with a Ph.D. in electrical or computer engineering with emphasis in signal processing, communications, or coding, or a master's degree in the above area with at least three years of work experience this field at the time of the alleged invention. I understand that Caltech has agreed with this definition of the level of ordinary skill in this case. <sup>23</sup>

I was asked to use a similar qualification for a "person of ordinary skill in the art" for purposes of a declaration that I understand was filed in connection with petitions for *Inter Partes Review* of the asserted patents. See Declaration of Brendan Frey dated October 14, 2014, at ¶2.

<sup>&</sup>lt;sup>2</sup> Reporter's Transcript of Claim Construction and Motion Hearing of July 9, 2014, Ex. 1026, at

<sup>&</sup>lt;sup>3</sup> This is also consistent with testimony given by, e.g., Dr. Dariush Divsalar, an author of one of the prior art references discussed in this report (see Divsalar Dep. at 55-56).

31. I understand that the parties have agreed on the following claim constructions:

| Claim Term                                                                                                                                                                   | Agreed-Upon Construction                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "irregularly"<br>('710 and '032 patents)                                                                                                                                     | "a different number of times"                                                                                                                                                                    |

| "interleaving" / "interleaver" / "scramble" ('710 patent)                                                                                                                    | "changing the order of data elements" / "module that changes the order of data elements"                                                                                                         |

| "sums of bits in subsets of the information bits" / "summing of bits in a subset of the information bits" / "adding additional subsets of information bits" ('781 patent)    | "the result(s) of adding together two or<br>more information bits from a subset of<br>information bits" / "adding together two or<br>more information bits from a subset of<br>information bits" |

| "wherein two or more memory<br>locations of the first set of memory<br>locations are read by the permutation<br>module different times from one<br>another"<br>('833 patent) | "where two or more memory locations of<br>the first set of memory locations are read<br>by the permutation module a different<br>number of times from one another"                               |

| "permutation module"<br>('833 patent)                                                                                                                                        | "a module that changes the order of data elements"                                                                                                                                               |

32. I further understand that the Court in this case has issued a claim construction order construing certain disputed claim terms as follows:

| Claim Term                                    | Court's Construction     |

|-----------------------------------------------|--------------------------|

| "transmitting" / "transmission" ('032 patent) | "sending over a channel" |

| "codeword"<br>('781 patent)                                        | "a discrete encoded sequence of data elements"                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "repeat"<br>('710 and '032 patents)                                | plain meaning <sup>4</sup>                                                                                                                                                                                                                                                                                      |

| "combine" / "combining"<br>('833 patent)                           | "perform logical operations on"                                                                                                                                                                                                                                                                                 |

| Equation in claim 1 of the '032 patent ('032 patent)               | "the parity bit $x_j$ is the sum of (a) the parity bit $x_{j-1}$ and (b) the sum of a number, 'a,' of randomly chosen irregular repeats of the message bits"                                                                                                                                                    |

| Γanner Graph term in claims 11 and 18 of '032 patent ('032 patent) | "a graph representing an IRA code as a set of parity checks where every message bit is repeated, at least two different subsets of message bits are repeated a different number of times, and check nodes, randomly connected to the repeated message bits, enforce constraints that determine the parity bits" |

33. For the purposes of this report, I have used the constructions given in the two tables above. For all other claim terms, I have used the plain and ordinary meaning the term would have to one of ordinary skill in the art.

### II. OVERVIEW OF THE TECHNOLOGY

34. The four patents-in-suit, which share a common specification, relate to the field of error-correcting codes. Below I provide a brief introduction to channel coding and error-correcting codes, and highlight a few of the developments in the field that are relevant to the asserted patents. Also, attached as Appendix A is a mathematical description of some properties of error-correcting codes.

<sup>&</sup>lt;sup>4</sup> The Claim Construction Order dated August 6, 2014 expounded on the plain meaning of "repeat." For example, the order said the "plain meaning of 'repeat' requires the creation of new bits corresponding to or reflecting the value of the original bits. In other words, repeating a bit with the value 0 will produce another bit with the value 0. The Court will refer to this concept as duplication" (Claim Construction Order dated August 6, 2014, p. 10).

35. Most computing devices and other digital electronics use bits to represent information. A bit is a binary unit of information that may have one of two values: 1 or 0. Any type of information, including, *e.g.*, text, music, images and video information, can be represented digitally as a collection of bits.

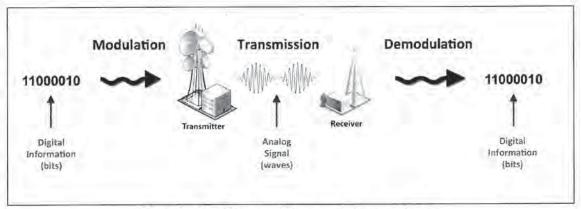

36. When transmitting binary information over an analog communication channel, the data bits representing the information to be communicated (also called "information bits" or "source bits") are converted into an analog signal that can be transmitted over the channel. This process is called *modulation*. The transmitted signal is then received by a receiving device and converted back into binary form. This process, in which a received analog waveform is converted into bits, is called *demodulation*. The steps of modulation and demodulation are shown in the figure below:

Modulation, Transmission, and Demodulation

37. Transmission over physical channels is never 100% reliable. The transmitted signal can be corrupted during transmission by "noise" caused by, e.g., obstacles obstructing the signal path, interference from other signals, or electrical/magnetic disturbances. Noise can cause bits to "flip" during transmission: for example, because of noise, a bit that was transmitted as a 1 can be corrupted during transmission and demodulated as 0, and vice versa.

- 38. Error-correcting codes were developed to combat such transmission errors.

Using the bits representing the information to be communicated (called "information bits", "data bits" or "source bits") an error-correcting code generates "parity bits" that allow the receiver to verify that the bits were transmitted correctly, and to correct transmission errors that may have occurred.

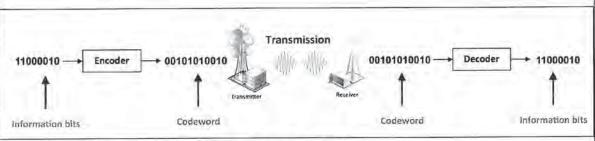

- 39. Bits are encoded by an *encoder*, which receives a sequence of information bits as input, generates parity bits based on the information bits according to a particular encoding algorithm, and outputs a sequence of encoded bits (or data elements) called a *codeword*. The codeword produced by the encoder is then modulated and transmitted as an analog signal.

- 40. At the receiver the signal is received, demodulated and passed to the *decoder*, which uses a decoding algorithm to recover the original codeword and the original information bits.

**Encoding and Decoding**

- 41. Error-correcting codes work by adding redundant information to the original message. Due to redundancy, the information represented by a given information bit is spread across multiple bits of the codeword. Thus, even if one of those bits is flipped during transmission, the original information bit can still be recovered from the others.

- 42. As a simple example, consider an encoding scheme, which I will call "repeat-three," that outputs three copies of each information bit. In this scheme, the information bits "1 0 1" would be encoded as "111 000 111." Upon receipt,

the decoder converts instances of "111" into "1" and instances of "000" into "0" to produce the decoded bits "1 0 1," which match the original information bits.

- 43. Suppose a bit is flipped during transmission, changing "000" to "010." The decoder will be able to detect that there was a transmission error, because "010" is not a valid "repeat-three" codeword. Using a "majority vote" rule, the decoder can infer that the original information bit was a 0, correcting the transmission error. Thus, due to the redundancy incorporated into the codeword, no information was lost due to the transmission error.

- 44. Error-correcting codes may be either *systematic* or *non-systematic*. In a systematic code, both the parity bits and the original information bits are included in the codeword. In a non-systematic code, the encoded data only includes the parity bits.

- 45. Systematic and non-systematic codes had been known in the art for decades prior to May 18, 2000, the claimed priority date of the patents-in-suit (*see*, *e.g.*, Wicker Dep. at 77:15-20; *see also*, *e.g.*, Divsalar Dep. at pp. 66-67).

### B. Coding Rate

46. Many error-correcting codes encode information bits in groups, or *blocks* of fixed length n. An encoder receives an k-bit block of information bits as input, and produces a corresponding n-bit codeword. The ratio k/n is called the *rate* of the code. Because the codeword generally includes redundant information, n is generally greater than k, and the rate k/n of an error-correcting code is generally less than one.

### C. Performance of Error-Correcting Codes

47. The effectiveness of an error-correcting code may be measured using a variety of metrics.

48. One tool used to assess the performance of a code is its *bit-error rate* (BER). The BER is defined as the number of corrupted information bits divided by the total number of information bits during a particular time interval. For example, if a decoder outputs 1000 bits in a given time period, and 10 of those bits are corrupted (*i.e.*, they differ from the information bits originally received by the encoder), then the BER of the code during that time period is (10 bit errors) / (1000 total bits) = 0.01 or 1%. <sup>5</sup>

49. The BER of a coded transmission depends on the amount of noise that is present in the communication channel, the strength of the transmitted signal (*i.e.*, the power that is used to transmit the modulated waveform), and the performance of the error-correcting code. An increase in noise tends to increase the error rate and an increase in signal strength tends to decrease the error rate. The ratio of the signal strength to the noise, called the "signal-to-noise ratio," is often used to characterize the channel over which the encoded signal is transmitted. The signal-to-noise ratio can be expressed mathematically as  $E_b/N_0$ , in which  $E_b$  is the amount of energy used to transmit each bit of the signal, and  $N_0$  is the density of the noise on the channel. The BER of an error-correcting code is often measured for multiple values of  $E_b/N_0$  to determine how the code performs under various channel conditions.

50. Error-correcting codes may also be assessed based on their computational complexity. The complexity of a code is a rough estimate of how many calculations are required for the encoder to generate the encoded parity bits and how many calculations are required for the decoder to reconstruct the information

<sup>&</sup>lt;sup>5</sup> Note that as used herein, BER refers to the *information* BER, which measures the percentage of bits that remain incorrect after decoding. This is not to be confused with the *transmission* BER, which measures the percentage of bits that are incorrect when they are received by the decoder.

<sup>&</sup>lt;sup>6</sup> More precisely,  $E_b/N_0$  is the *normalized* signal-to-noise ratio. It is a dimensionless quantity that does not depend on the particular units used to measure the strength of the signal and the quantity of noise on the channel.

bits from the parity bits. If a code is too complex, it may be impractical to build encoders/decoders that are fast enough to use it.

#### D. LDPC Codes, Convolutional Codes, Turbocodes, and Repeat-Accumulate codes

- 51. In 1963, Robert Gallager described a set of error correcting codes called Low Density Parity Check ("LDPC") codes. Gallager described how LDPC codes provide one method of generating parity bits from information bits using a matrix populated with mostly 0s and relatively few 1s, and he described how decoding could be performed using an iterative "message passing" decoding algorithm, as described below.<sup>7</sup>

- 52. Gallager's work was largely ignored over the following decades, as researchers continued to discover other algorithms for calculating parity bits. These algorithms included, for example, convolutional encoding (see below) with Viterbi decoding and cyclic code encoding with bounded distance decoding. In many cases these new codes could be decoded using low-complexity decoding algorithms.

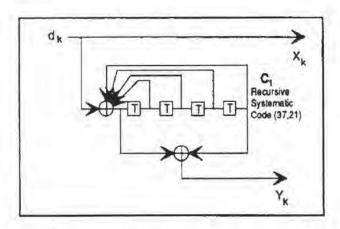

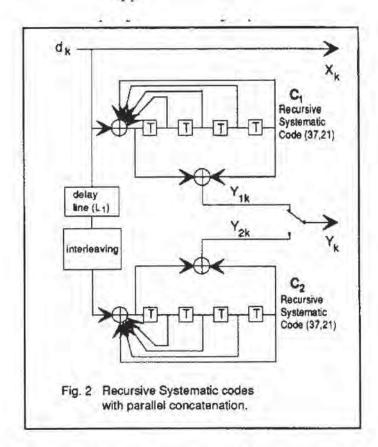

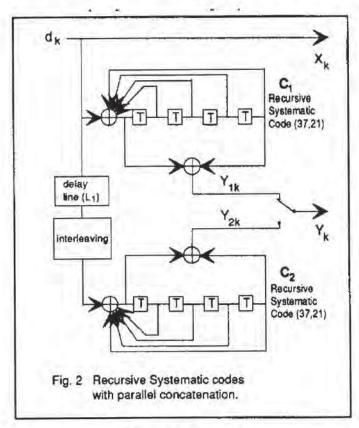

- 53. In 1993, researchers discovered "turbocodes," a class of error-correcting codes capable of transmitting information at a rate close to the Shannon Limit the maximum rate at which information can be transmitted over a channel. Turbocodes make use of "convolutional codes", which were described in the 1960's and were widely used in telephone modems in the 1980's and 1990's. A convolutional code is a type of error-correcting code that generates parity bits by processing the information bits in order. The convolutional code contains a "memory bank" in the form of a short sequence of bits, e.g., 4 bits. When an information bit  $d_k$  is processed, the memory bits  $s_1$ ,  $s_2$ ,  $s_3$ ,  $s_4$  are combined with the information bit to produce a new memory bit and the remaining memory bits are

<sup>&</sup>lt;sup>7</sup> Gallager, R., Low-Density Parity-Check Codes (Monograph, M.I.T. Press, 1963).

<sup>&</sup>lt;sup>8</sup> Claude Berrou et al., Near Shannon Limit Error-Correcting Coding and Decoding: Turbo Codes, 2 IEEE International Conference on Communications, ICC '93 Geneva. Technical

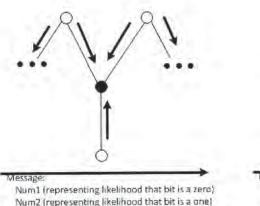

54. Convolutional codes are usually decoded using the "Viterbi algorithm" or the "BCJR algorithm". These algorithms can be viewed as iterative "message passing" decoding algorithms, if we represent the convolutional code using a "Tanner graph" or a "factor graph", as described below.

55. The main drawback of convolutional codes is that they only produce local redundancy in the output stream. They do not perform well when the channel introduces errors that are nearby. Turbocodes overcome this deficiency by encoding the input bits twice. The input bits are fed to a convolutional encoder in their normal order, and they are also reordered by an interleaver and the reordered bits are encoded by a second convolutional encoder. Using a turbocode, a small number of errors will not result in loss of information unless the errors happen to fall close together in both the original data stream and in the permuted data stream, which is unlikely.

56. A standard turbocoder encodes a sequence of information bits using two convolutional coders. The information bits are passed to the first convolutional coder in their original order. At the same time, a copy of the information bits

permuted by an interleaver is passed to the second convolutional coder. The figure below shows the structure of a typical turbocoder.<sup>9</sup>

57. In 1995, David J. C. MacKay rediscovered Gallager's work from 1963 relating to low-density parity-check (LDPC) codes and demonstrated that they have performance comparable to that of turbocodes. Turbocodes and LDPC codes have some common characteristics: both codes use pseudo-random permutations to spread out redundancy, and both use iterative "message passing" decoding algorithms.

MacKay, D. J. C, and Neal, R. M. "Near Shannon Limit Performance of Low Density Parity Check Codes." *Electronics Letters*, vol. 32, pp. 1645-1646 (1996).

<sup>&</sup>lt;sup>9</sup> Claude Berrou et al., Near Shannon Limit Error-Correcting Coding and Decoding: Turbo Codes, 2 IEEE International Conference on Communications, ICC '93 Geneva. Technical Program, Conference Record 1064 (1993); '032 patent, 1:29-56.

58. In 1995 and 1996, researchers began to explore "concatenated" convolutional codes. While turbocodes use two convolutional coders connected in parallel, concatenated convolutional codes use two convolutional coders connected in series: the information bits are encoded by a first encoder, the output of the first encoder is interleaved, and the interleaved sequence is encoded by a second convolutional code. In such codes, the first and second encoders are often called the "outer coder" and the "inner coder," respectively.

59. In 1998, researchers developed "repeat-accumulate," or "RA codes" by simplifying the principles underlying turbocodes. <sup>12</sup> In RA codes, the information bits are first passed to a repeater that repeats (*i.e.*, duplicates) the information bits and outputs a stream of repeated bits (the encoder described above in the context of the "repeat three" coding scheme is one example of a repeater). The repeated bits are then passed through an interleaver, which scrambles their order, and then to an accumulator, where they are "accumulated" to form the parity bits, which are transmitted across the channel.

60. The accumulation operation is a running sum process whereby each input bit is added to the previous input bits to produce a sequence of running sums, each of which represents the sum of all input bits yet received. More formally, if an accumulator receives a sequence of input bits  $i_1$ ,  $i_2$ ,  $i_3$ , ...  $i_n$ , it will produce output bits  $o_1$ ,  $o_2$ ,  $o_3$ , ...  $o_m$  such that:

22 | Henedetto, S. et al., Serial Concatenation of Block and Convolutional Codes, 32.10 | Electronics Letters 887-888 (1996).

Divsalar, D. et al., "Coding Theorems for Turbo-like Codes," *Proc. 36th Allerton Conf. on Comm., Control and Computing*, 201 (Sept. 1998).

<sup>13</sup> Here I use the ⊕ symbol to denote modulo-2 addition.

| $o_1=i_1$                                                  |   |

|------------------------------------------------------------|---|

| $o_2=i_1\oplus i_2$                                        |   |

| $o_3=i_1\oplus i_2\oplus i_3$                              |   |

| 1                                                          |   |

| $o_n = i_1 \oplus i_2 \oplus i_3 \oplus \cdots \oplus i_n$ | n |

61. The accumulation operation can also be described as a recursive operation in which each output bit is the sum of the previous output bit and the current input bit:

$$o_1 = i_1$$

$o_2 = o_1 \oplus i_2$

$o_3 = o_2 \oplus i_3$

$\vdots$

$o_n = o_{n-1} \oplus i_n$

- 62. As this recursive formulation shows, each accumulated bit can be calculated by performing a single modulo-2 addition operation. This relatively low computational complexity is one of the benefits of accumulate codes. In particular, it allows accumulate codes to be encoded quickly and cheaply.

- 63. Repetition and accumulation were well known in the art by May 18, 2000 and by March 7, 2000, the claimed priority date and the claimed conception date, respectively, of the patents-in-suit (*see*, *e.g.*, Wicker Dep. at 66:18-67:11, Jin Dep. at 67:8-23, 122:7-13).

#### E. Irregularity

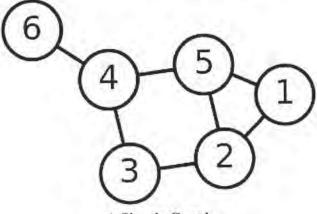

64. A regular code is a systematic code that corresponds to a Tanner graph in which each information node is connected to the same number of check nodes, or a nonsystematic code that corresponds to a Tanner graph in which each parity node

is connected to the same number of check nodes.<sup>14</sup> By contrast, an *irregular code* is a systematic code that corresponds to a Tanner graph in which some information nodes are connected to more check nodes than others, or a nonsystematic code that corresponds to a Tanner graph in which some parity nodes are connected to more check nodes than others. The concepts of *regular* and *irregular* need not be expressed with reference to Tanner graphs, but it is convenient to do so.

- 65. Irregular LDPC codes were first introduced in a 1997 paper by Luby et al. <sup>15</sup> The paper showed that irregular codes perform better than regular ones on certain types of noisy channels. At the time, this paper was widely read by coding theorists, and gave rise to several lines of research into irregular error-correcting codes. For example, in my own paper titled "Irregular Turbocodes," presented at the 1999 Allerton Conference on Communications, Control, and Computing, I applied the concept of irregularity to turbocodes by explaining how to construct irregular turbocodes in which some information bits connect to more check nodes than others. My experimental results demonstrated that these irregular turbocodes perform better than the regular turbocodes that were known in the art.

- 66. By May 18, 2000 and by March 7, 2000, the claimed priority date and the claimed conception date, respectively, of the patents-in-suit, it was known to those with ordinary skill in the art that the performance of any type of error-correcting code could be improved by adding irregularity (see, e.g., Wicker Dep. at 232:6-233:8). For example, on Dec. 8, 1999, I wrote to Dr. Divsalar, the lead author on the paper "Coding Theorems for 'Turbo-Like' Codes" discussed in this report, suggesting that the RA codes that he and Dr. Robert McEliece had been working on should be made irregular (see CALTECH000024021).

<sup>14</sup> For a more complete discussion of Tanner graphs, see generally Appendix A.

<sup>&</sup>lt;sup>15</sup> Luby, M. et al., "Practical Loss-Resilient Codes," STOC '97 (1997).

A. Summary of the Specification.

2

3

5

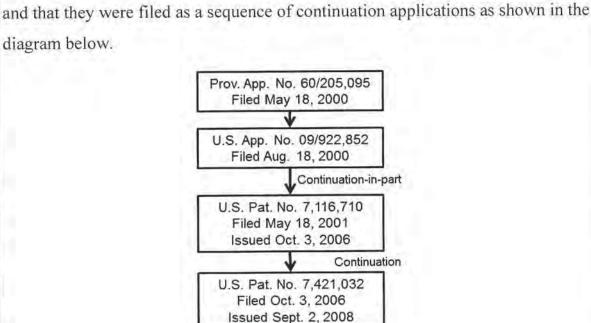

diagram below.

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Continuation

Continuation

67. I have been informed that the patents-in-suit share a common specification

U.S. Pat. No. 8,284,833 Filed Mar. 28, 2011 Issued Oct. 9, 2012

The specification, which is common to the four patents-in-suit, is generally directed to irregular RA codes (or "IRA" codes). Figure 2 of the specification, reproduced below, shows the structure of an IRA encoder:

U.S. Pat. No. 7,916,781

Filed Jun. 30, 2008 Issued Mar. 29, 2011

-22-

- 69. Explaining this figure, the patents describe encoding data using an outer coder 202 connected to an inner coder 206 via an interleaver 204 (labeled "P") ('710 patent at 2:33-40).

- 70. Outer coder 202 receives a block of information bits and duplicates each of the bits in the block a given number of times, producing a sequence of repeated bits at its output (id. at 2:50-52). The outer coder repeats bits irregularly i.e., it outputs more duplicates of some information bits than others (id. at 2:48-50).

- 71. The repeated bits are passed to an interleaver 204, where they are scrambled (*id.* at 3:18-22). The scrambled bits are then passed to the inner coder 206, where they are accumulated to form parity bits (*id.* at 2:65-67; 2:33-38). According to the specification:

Such an accumulator may be considered a block coder whose input block  $[x_1, ..., x_n]$  and output block  $[y_1, ..., y_n]$  are related by the formula

$$y_1 = x_1$$

$$y_2 = x_1 \oplus x_2$$

$$y_3 = x_1 \oplus x_2 \oplus x_3$$

$$y_n = x_1 \oplus x_2 \oplus x_3 \oplus \dots \oplus x_n$$

(id. at 3:2-10).

72. The patent specification teaches both systematic and non-systematic codes.

In a systematic code, the encoder outputs a copy of the information bits in addition

to the parity bits output by inner coder 206 (the systematic output is represented in Fig. 2. as an arrow running toward the right along the top of the figure).

73. I discuss each of the patents individually below. However, I note here that Caltech has characterized all four of the asserted patents as being directed to IRA codes. <sup>16</sup>

#### B. '710 Patent

#### i) <u>Claims</u>

74. The '710 patent includes 33 claims, of which claims 1, 11, 15, and 25 are independent. Independent claims 1 and 11 are directed to methods of encoding a signal that include "first encoding" and "second encoding" steps. Independent claim 15 is directed to a "coder" for encoding bits that includes a "first coder" and a "second coder." Claim 25 is directed to a "coding system" that also encodes bits using a first and second coder, and further includes a decoder for decoding the encoded bits. I understand that Caltech asserts claims 1, 4, 6, 15, 20, and 22 in this case.

### ii) Prosecution History

### a) First Office Action: September 3, 2004

75. The patent office issued a first office action rejecting some of the claims under 35 U.S.C. § 102 as anticipated by U.S. Patent No. 6,014,411 (to Wang) and under 35 U.S.C. § 103 as obvious over Wang in view of Wiberg et al., "Codes and Iterative Decoding on General Graphs," 1995 Intl. Symposium on Information Theory, Sep. 1995, p. 506.

<sup>&</sup>lt;sup>16</sup> See, e.g., Plaintiff's Technology Tutorial (Dkt. No. 85), p. 1 (which states that "[a]II of the patents in suit relate to a novel error correction technique known as IRA codes").

### Response: November 24, 2004

1

2

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

In response, the applicant argued that the rejected claims are not anticipated or obvious over the cited art because they all require that bits be repeated "irregularly" or "a different number of times" during the first encoding step, while Wang teaches repeating bits "the same number of times, i.e., regularly" (Response dated Nov. 24, 2004 at 11).

#### c) Second Office Action: March 4, 2005

The patent office issued a second office action allowing some claims and rejecting others. In particular, the examiner allowed claim 1 in response to the applicant's arguments. The examiner also rejected independent claims 15 and 24, under 35 U.S.C. § 102 as anticipated by U.S. Patent No. 6,396,423 (to Laumen et al.). The patent office also rejected several dependent claims under 35 U.S.C. § 103 as obvious over Laumen alone.

#### Response: May 5, 2005

78. In response, the applicant attempted to overcome the examiner's rejections by amending claims 15 and 24 to require that the second coder encode bits at a rate "within 50% of one" (previously, the claims had recited a rate "close to one") (Response dated May 5, 2005 at 7-8). In the same amendment, the applicant added new claims 32-35.

#### Third Office Action: July 21, 2005

The patent office issued a third office action maintaining its previous 79. rejections over Laumen, noting that Laumen teaches a transmission rate of 1/2, and 1/2 is "within 50% of one" (Office Action dated Jul. 21, 2005 at 4).

### Response: October 21, 2005

To overcome the examiner's rejection, the applicant canceled claims 32 and 34 and incorporated their subject matter into claims 15 and 24, respectively. As

-25-

amended, claims 15 and 24 require that the second coder encode bits at a rate "within 10% of one" (Response dated Oct. 21, 2005 at 9).

#### C. '032 Patent

#### i) <u>Claims</u>

81. The '032 patent includes 23 claims, of which claims 1, 11, and 18 are independent. Independent claim 1 is directed to a method that comprises generating a sequence of parity bits from a collection of message bits in accordance with particular mathematical formulae, and making the parity bits available for transmission. Independent claim 11 is directed to an encoder that generates a sequence of parity bits from a collection of message bits in accordance with a particular Tanner Graph. Independent claim 18 is directed to a device for decoding a data stream that has been encoded in accordance with the same Tanner Graph. I understand that Caltech asserts claims 1, 18, 19, and 22 in this case.

#### ii) Prosecution History

## a) First Office Action: September 6, 2007

82. The patent examiner initially allowed pending claims 1-17 and rejected independent claim 18 and dependent claims 19-24 under 35 U.S.C. § 103 as obvious over U.S. Patent No. 5,530,707 (to Lin) in view of U.S. Patent No. 6,859,906 (to Hammons et al.).

### b) Response: Feb 4, 2008

83. To overcome the examiner's rejection, the applicant canceled claim 20 and incorporated its subject matter into independent claim 18. The amendment further limited claim 18 to require that the message passing decoder of claim 18 be configured to decode a data stream that has been encoded in accordance with a particular Tanner graph.

#### D. '781 Patent

#### i) <u>Claims</u>

84. The '781 patent includes 22 claims, of which claims 1, 13, 19, 20, and 21 are independent. Independent claim 1 is directed to a two-step process for encoding a signal, where the first encoding step involves a linear transform operation and the second involves an accumulation operation. Independent claims 13 and 19 are directed to methods of encoding a signal that generate codewords by summing information bits and accumulating the resulting sums. Independent claims 20 and 21 are directed to methods that involve summing information bits and parity bits to generate a portion of an encoded signal. I understand that Caltech asserts claims 16 and 19 in this case.

#### ii) Prosecution History

#### a) First Office Action: October 28, 2010

85. The patent examiner issued a first office action allowing some claims but rejecting claims 13-17 and 20 as anticipated by U.S. Patent 5,181,207 (to Chapman, et. al.) and requiring applicants to clarify the term "irregular," as it appeared in claims 9 and 23.

### b) Response: January 27, 2011

- 86. To overcome the examiner's rejection, the applicant canceled claim 21 and incorporated its subject matter into independent claim 13. As amended, claim 13 requires that "the information bits appear in a variable number of subsets" (Response dated Jan. 27, 2011 at 4).

- 87. In accompanying remarks, applicants disagreed with the examiner's statement that the term "irregular" was unclear, stating that "[i]t is believed that the meaning of the term "irregular" in the claims is clear and is well known in the art of computer coding technology" (id. at 7) (emphasis added). However, to overcome

the examiner's rejection, the applicant amended claims 9 and 23 to remove the word "irregular," replacing it with the requirement that the information bits appear "in a variable number of subsets" (id. at 3, 6).

#### E. '833 Patent

#### i) Claims

88. The '833 patent includes 14 claims, of which claims 1 and 8 are independent. Independent claims 1 and 8 are directed to an apparatus and a method, respectively, for encoding information bits that are stored in a first set of memory locations by combining information bits with parity bits that are stored in a second set of memory locations, and accumulating the bits in the second set of memory locations. Both claims require that at least two of the first set of memory locations be read "different times from one another." I understand that Caltech asserts claims 1, 2, 4, and 8 in this case.

#### ii) Prosecution History

- 89. After the examiner had allowed all pending claims in the application, the applicant attempted to amend claims 1 and 8 as follows: "wherein a total number of indices two or more memory locations of the first set of memory locations are read by the permutation module different times from one another represents a variable number" (Amendment dated May 7, 2012).

- 90. The examiner did not enter these amendments after allowance because they changed the scope of the claims that had already been allowed. The applicant subsequently filed a request for continued examination, after which the examiner allowed the claims as amended.

<sup>&</sup>lt;sup>17</sup> As noted above, the parties have agreed that this claim term requires memory locations to be read a different <u>number</u> of times from one another.

#### IV. SUMMARY OF THE PRIOR ART

#### A. Divsalar

3

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

- 91. D. Divsalar, H. Jin, and R. J. McEliece, "Coding theorems for "turbo-like" codes," *Proc. 36th Allerton Conf. on Comm., Control and Computing*, Allerton, Illinois, pp. 201-210 ("Divsalar") was published in Sept. 1998, about 1.5 years before the filing of the provisional application to which the patents-in-suit claim priority, and I have been informed that Divsalar qualifies as prior art to all four of the patents-in-suit.

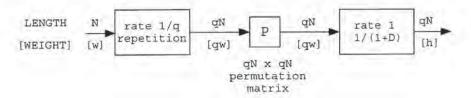

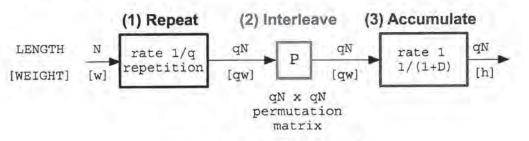

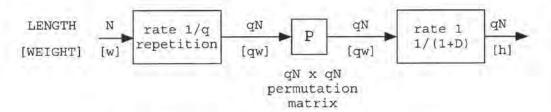

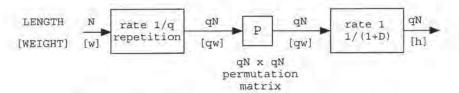

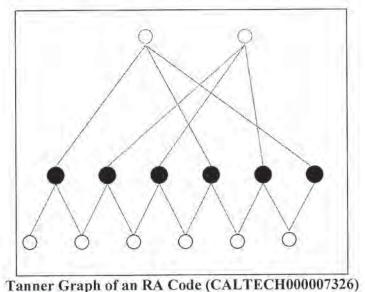

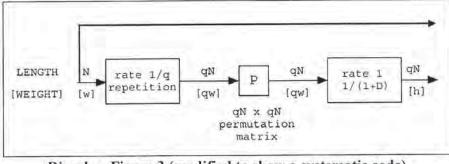

- 92. Divsalar teaches "repeat and accumulate" codes, which it describes as "a simple class of rate 1/q serially concatenated codes where the outer code is a q-fold repetition code and the inner code is a rate 1 convolutional code with transfer function 1/(1+D)" (Divsalar at 1). Fig. 3 of Divsalar, reproduced below, shows an encoder for a repeat-accumulate code with rate N/qN:

Figure 3. Encoder for a (qN, N) repeat and accumulate code. The numbers above the input-output lines indicate the length of the corresponding block, and those below the lines indicate the weight of the block.

- 93. A block of N information bits enters the coder at the left side of the figure and is provided to the repeater (labeled "rate 1/q repetition") (see id. at 5). The repeater duplicates each of the N information bits q times and outputs the resulting  $N \times q$  repeated bits, which are then "scrambled by an interleaver of size qN" (id., referring to the box labeled "P"). The scrambled bits are "then encoded by a rate 1 accumulator" (id., emphasis in original; see also Divsalar Tr. at pp. 59-63, 68-69).

- 94. Divsalar describes the accumulator as follows:

6

7

8

9

10

11

- (id. at 5). The plus signs ("+") in Divsalar's formula represent modulo-2, or exclusive-OR, addition (see id.; see also Divsalar Tr. 69:10-16).

- 95. Divsalar uses repeat-accumulate codes to prove a conjecture regarding the interleaver gain exponent (IGE), which is a numerical parameter that estimates the rate at which the word error rate decreases as the block length increases.

[W]e prefer to think of [the accumulator] as a block coder whose

input block  $[x_1, ..., x_n]$  and output block  $[y_1, ..., y_n]$  are related by

96. Divsalar further shows that RA codes have "very good" performance and that they can be efficiently decoded using a "message passing decoding algorithm" (id. at 9-10).

97. Divsalar teaches that turbocodes, serially concatenated convolutional codes

"turbo-like" codes and they include as special cases both the classical turbo codes

repeat-and-accumulate codes, and prove the IGE conjecture for them" (Divsalar at

information bits are punctured, or truncated, none of the parity bits are punctured,

and RA codes can all be viewed as "turbo-like" codes: "We call these systems

and the serial concatentation of interleaved convolutional codes" (Divsalar

1). More specifically, RA codes can be viewed as turbocodes, in which the

Abstract) and "In Section 5, we define a special class of turbo-like codes, the

12

13

14

15

16

17

18

20

19

21

22

23

24

and the convolutional code is an accumulator. "The accumulator can be viewed as a truncated rate-1 recursive convolutional encoder with transfer function 1/(1 + D)" (Divslar at 5). Divsalar also makes use of the fact that RA codes can be viewed as turbocodes to explain the decoder: "But an important feature of turbo-like codes is the availability of a simple iterative, message passing decoding algorithm that approximates ML decoding. We wrote a computer program to implement this -30-

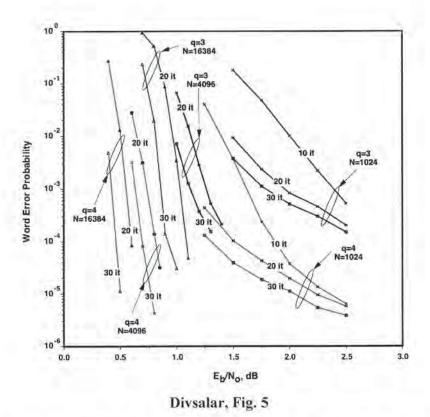

'turbo-like' decoding for RA codes with q = 3 (rate 1/3) and q = 4 (rate 1/4), and the results are shown in Figure 5" (Divsalar at 9).

98. As explained further below, Divsalar teaches all but one aspect of an IRA code: irregularity (the "I" in <u>Irregular Repeat-Accumulate</u>). That is, Divsalar teaches regular repeat-accumulate (RA) codes rather than irregular repeat-accumulate codes. A single modification to Divsalar – *i.e.*, changing the repeat to being irregular instead of regular – would result in the IRA codes that Caltech claims to have invented. I also explain below why it would have been obvious to one of ordinary skill before the Caltech patents were filed (and before Caltech's claimed conception date) to add irregularity to the repeat-accumulate codes of Divsalar, resulting in the irregular repeat-accumulate codes to which the patents-insuit are directed.

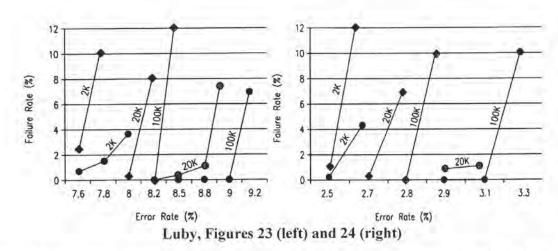

#### B. Luby

99. U.S. Patent No. 6,081,909 to Luby et al. ("Luby"), titled "Irregularly graphed encoding technique," was filed Nov. 6, 1997, about 2.5 years before the filing of the provisional application to which the patents-in-suit claim priority, and I have been informed that Luby qualifies as prior art to all four of the patents-in-suit.

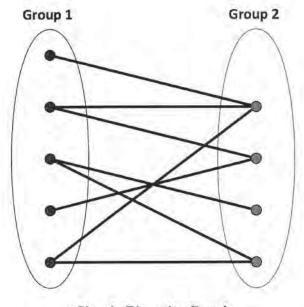

100. The Luby patent mirrors the teachings of Luby's seminal paper that I described above, in which the concept of irregular error-correcting codes was first introduced. Specifically, Luby teaches "a technique for creating loss resilient and error correcting codes having irregular graphing between the message data and the redundant data" (Luby at 1:5-10). "Irregular graphing" refers to codes with Tanner graphs in which some information nodes are connected to more check nodes than others (see, e.g., id. at 3:27-29, stating that "different numbers of first edges are associated with the data items").

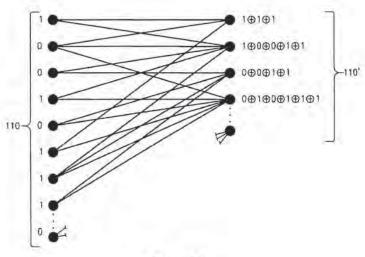

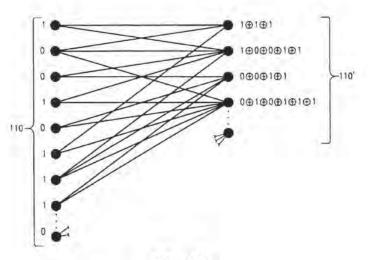

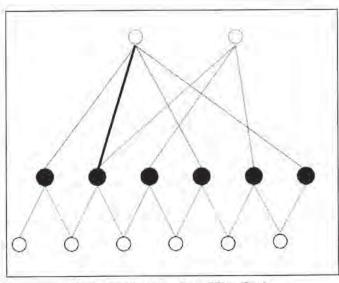

101. A Tanner graph corresponding to an irregular code is shown in Fig. 17 of Luby, reproduced below:

FIG. 17

102. In this figure, the circles on the left represent information bits to be encoded and the circles on the right represent parity checks computed for these information bits. Each parity check on the right is computed by summing together (modulo 2) all of the information bits connected to that parity check by an edge in the graph (see id. at 17:64-67).<sup>18</sup>

103. As the figure shows, some information nodes on the left contribute to three parity checks on the right, while others contribute to two (*i.e.*, all nodes on the left which are connected to two lines, such as the top node, contribute to two parity checks and all nodes on the left which are connected to three lines, such as the second node from the top, contribute to three parity checks). An encoding scheme with a Tanner graph in which some information nodes are connected to more check nodes than others is the defining characteristic of an irregular code.

<sup>&</sup>lt;sup>18</sup> I explain what an "edge" is in this context in Appendix A, below.

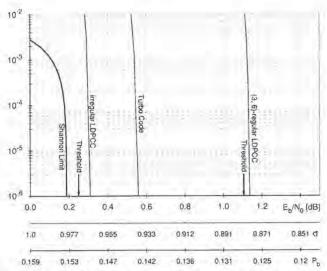

### C. MacKay

104. D. J. C. MacKay, S. T. Wilson, and M. C. Davey, "Comparison of constructions of irregular Gallager codes," *IEEE Trans. Commun.*, Vol. 47, No. 10, pp. 1449-1454 ("MacKay") was published in Oct. 1999, about six months before the filing of the provisional application to which the patents-in-suit claim priority, and I have been informed that MacKay qualifies as prior art to all four of the patents-in-suit.

105. MacKay is motivated by "[t]he excellent performance of irregular Gallager codes," and explores "ways of further enhancing these codes" (MacKay at 1459). In particular, MacKay investigates the constructions of both regular and irregular Gallager codes with encoding algorithms that have low computational complexity.

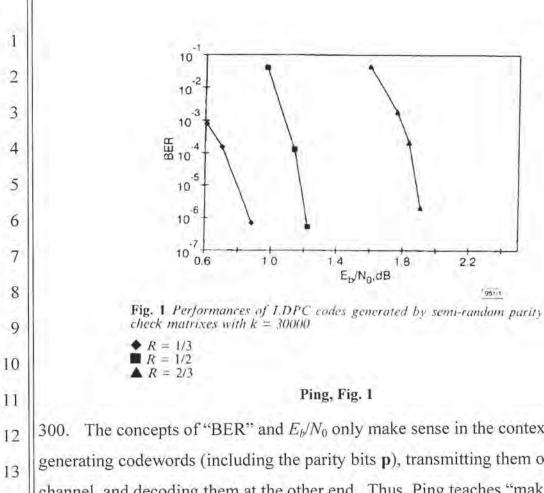

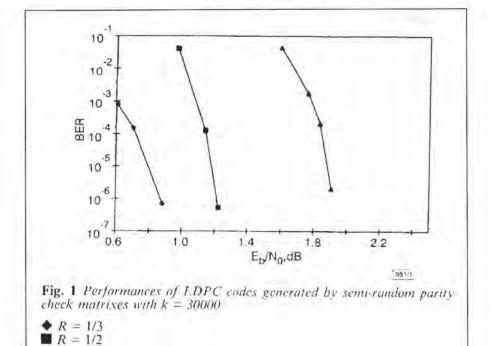

#### D. Ping

106. L. Ping, W. K. Leung, N. Phamdo, "Low Density Parity Check Codes with Semi-random Parity Check Matrix." *Electron. Letters*, Vol. 35, No. 1, pp. 38-39 ("Ping") was published in Jan. 1999, more than a year before the filing of the provisional application to which the patents-in-suit claim priority, and I have been informed that Ping qualifies as prior art to all four of the patents-in-suit.

107. Ping teaches constructing LDPC codes that can be encoded in two stages. In the first encoding stage, a generator matrix is applied to a sequence of information bits to produce sums of information bits. In the second stage, the sums of information bits are accumulated recursively to generate the parity bits (*see* Ping at 38).

108. Ping's code can be described as an LDPC code with two components: an outer coder that is an LDGM coder followed by an inner coder that is an

accumulator. Thus Ping teaches LDPC codes that are also accumulate codes. 19 1 understand that the codes Caltech has accused of infringement, i.e., the DVB-S2 codes, can also be encoded using LDPC + accumulate coders. One difference 3 between Ping and the accused codes is that Ping's LDPC code is regular whereas 4 in the accused DVB-S2 codes, the LDPC code is irregular. As explained below, it 5 was obvious before Caltech's alleged invention to make codes irregular, e.g., 6 because it was known that doing so would improve their performance. In 7 particular, it was obvious before Caltech's alleged invention to make Ping's LDPC code irregular. Therefore, if Caltech establishes that its claims cover the accused 8 DVB-S2 codes, then those claims would be invalid in view of Ping and the art that 9 rendered it obvious to make Ping's LDPC code irregular, e.g. Luby, MacKay and 10 Frey99. 11 E. Frey99 12 109. Frey, B. J. and MacKay, D. J. C., "Irregular Turbocodes," Proc. 37th 13 14 was published on or before March 20, 2000, which is before the filing of the

Allerton Conf. on Comm., Control and Computing, Monticello, Illinois ("Frey99") provisional application to which the patents-in-suit claim priority, and I have been informed that Frey99 qualifies as prior art to all four of the patents-in-suit.

110. Frey99 is a paper that I wrote in collaboration with David MacKay. In Frey99, David MacKay and I applied the concept of irregularity to turbocodes by explaining how to construct irregular turbocodes, i.e., turbocodes with Tanner graphs in which some information nodes are connected to more check nodes than others. Our experimental results demonstrated that these irregular turbocodes perform better than the regular turbocodes that were known in the art.

15

16

17

18

19

20

21

22

23

Below I refer to these codes as "LDPC + accumulate" codes.

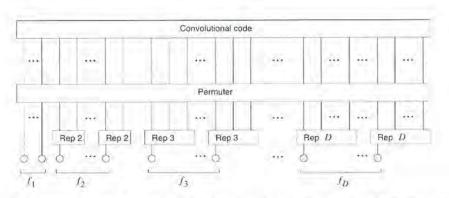

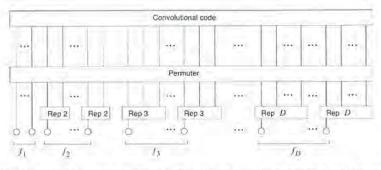

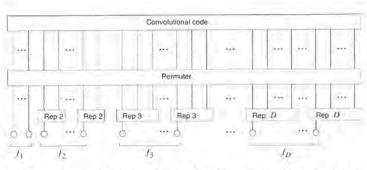

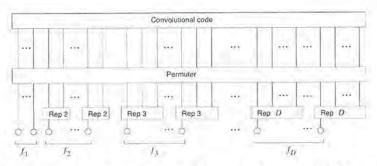

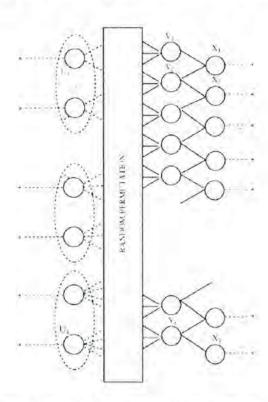

111. As I explain in Frey99, "an *irregular turbocode* has the form shown in Fig. 2, which is a type 'trellis-constrained code' as described in [7]. We specify a *degree* profile,  $f_d \in [0, 1]$ ,  $d \in \{1, 2, ..., D\}$ .  $f_d$  is the fraction of codeword bits that have degree d and d is the maximum degree. Each codeword bit with degree  $d^{20}$  is repeated d times before being fed into the permuter. Several classes of permuter lead to linear-time encodable codes. In particular, if the bits in the convolutional code are partitioned into 'systematic bits' and 'parity bits', then by connecting each parity bit to a degree 1 codeword bit, we can encode in linear time' (Frey99 at 2).

112. As this passage explains, the irregular turbocodes I described in Frey99 operate by irregularly repeating the information bits, interleaving the repeated bits using a "permute" (*i.e.*, an interleaver), and encoding the permuted bits using a convolutional code. Figure 2 of Frey99, reproduced below, illustrates such an irregular turbocode:

Figure 2: A general irregular turbocode. For d = 1, ..., D, fraction  $f_d$  of the codeword bits are repeated d times, permuted and connected to a convolutional code.

113. In this figure, bits in the subset  $f_1$  are not repeated, bits in the subset  $f_2$  are repeated twice, bits in the subset  $f_3$  are repeated three times, and bits in the subset  $f_D$  are repeated D times.

$<sup>^{20}</sup>$  A bit with "degree d" is a bit that contributes to d parity check bits. In Frey99, bits of degree d are repeated d times prior to permutation.

## F. Frey Slides

114. I prepared the Frey Slides (titled "Irregular Turbo-Like Codes") in collaboration with David MacKay and presented them at the Allerton Conference in September, 1999. The Frey Slides contain the material upon which the Frey99 paper, published in the Allerton 1999 conference proceedings, is based.

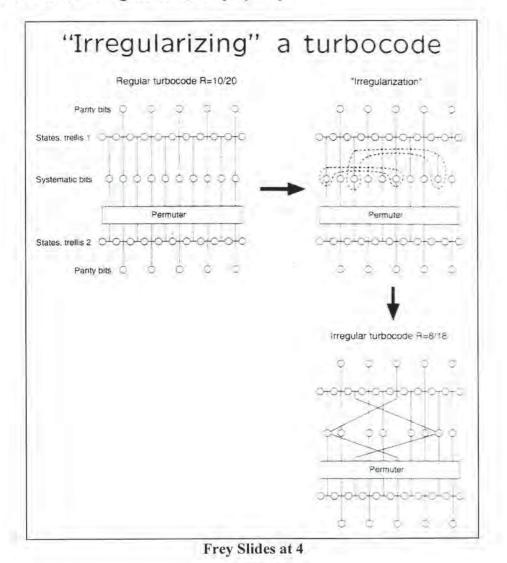

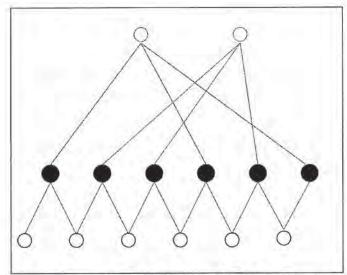

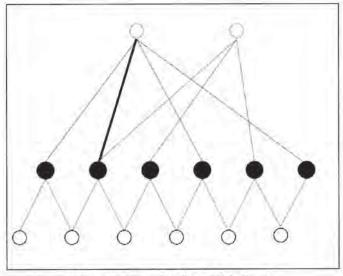

115. In particular, the Frey Slides describe how irregularity can improve code performance and introduce the concept of irregular turbocodes. Using the same procedure described in the Frey99 paper, the Frey Slides show how known, regular turbocodes can be "irregularized," step by step:

-36-

In the figure above, a regular turbocode (upper left) is "irregularized" by tying information nodes together (upper right), thereby raising their degree, resulting in an irregular turbocode (lower right).

116. Also, using a diagram identical to Figure 2 of Frey99 (described above) the Frey Slides show how irregular turbocodes can be implemented via irregular repetition:

|     | Trellis rep | resenting constituent cor | volutional codes, | average rate R |       |

|-----|-------------|---------------------------|-------------------|----------------|-------|

|     | -           |                           |                   | ***            | 1446  |

|     |             | Permuter                  |                   |                |       |

|     |             |                           | 1996              |                |       |

| 1 8 | Rep 2 Rep 2 | Rep 3 Rep                 | 3                 | Rep D          | Rep D |

Frey Slides at 5

- 117. The Frey Slides also describe selection of degree profiles (*see id.* at 6) and provide details regarding the rate of the resulting convolutional coder and the overall rate of the irregular turbocode (*id.* at 5-8, 13).

- 118. I understand that Caltech has alleged a date of invention of March 7, 2000. I further understand that Caltech may argue that the Frey99 paper was not published until after its alleged invention date. In the event that the Court finds that the patents-in-suit are entitled to a date of invention that predates the publication of Frey99, and the Frey99 paper is deemed not to be prior art to the patents-in-suit, then the Frey Slides may be substituted for the Frey99 paper in all of the positions explained below. For the purposes of the invalidity opinions set forth in this report, the teachings of Frey99 and the Frey Slides are interchangeable. To illustrate how the Frey Slides may be substituted for Frey99, wherever I cite to Frey99 in the

report below, I have also included citations to the corresponding teachings in the Frey Slides.

#### G. RA.c

3

5

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

- 119. Source code file "RA.c," dated September 28, 1998, was written by David MacKay at the University of California at San Francisco.

- 120. The RA.c source code implements a "[r]epeat-accumulate code simulator." The file includes a function called "RA\_encode" that performs a repeat-accumulate encoding operation.

- 121. The operation of RA.c is described in a comment at the beginning of the source code file:

```

RA.c

(c) DJCM 98 09 28

Repeat-accumulate code simulator

read in code definition

loop (

encode source string

add noise

Code definition: (stored in "alist")

Use of alist allows arbitrary numbers of repetitions

of each bit.

source block length

number of repetitions of each source bit

n 1 n 2 ... n K

N = sum n k

permutation of N encoded bits

alist defines

note, an additional permutation of the N accumulated

bits may be a good idea. (for non-memoryless channels)

transmitted bits are integral of encoded bits

Future plans:

clump source bits into clumps. Have multiple parallel accumulated streams.

Have little sub-matrices (like GF(q) ) defining response of accumulator to

clumps.

(RA.c at 1) (emphasis added).

```

122. As shown by the highlighted passages above, the comment at the top of RA.c explicitly refers to repeat-accumulate codes in which different information bits are repeated different numbers of times. Therefore, this comment, written

more than 1.5 years before the alleged conception date of the patents-in-suit, explicitly teaches irregular repeat-accumulate codes.

#### H. '999 Patent

123. U.S. Patent No. 4,623,999 to Patterson et al. (hereinafter, the "999 patent"), was filed on June 4, 1984, more than 15 years before the filing date of the provisional application to which the patents-in-suit claim priority, and I have been informed that the '999 patent qualifies as prior art to all four of the patents-in-suit.

124. The '999 patent teaches an encoder for encoding information bits using a linear error-correcting code. The encoder taught by the '999 patent uses a plurality of memories that store values used during the encoding process ('999 patent at Abstract, describing "[a]n efficient look-up table encoder for encoding *k* bit information words with linear error correcting block codes is provided comprising a plurality of read-only **memories** ...") (emphasis added). The teachings of the '999 patent illustrate that the use of memories to implement error-correcting coders was known in the art for decades prior to the claimed priority date of the patents-in-suit.

## I. Accused Hughes Products

- 125. As I explain below, the earliest priority date to which the claims of the '833 patent could be entitled is March 28, 2011, the date those claims were first filed.

- 126. I have been informed that a number of the accused products in this case were sold by Defendants prior to March 28, 2011. If the claims of the '833 patent are entitled to a priority date of March 28, 2011, these accused products would qualify as prior art to the claims of the '833 patent.

## V. SUMMARY OF ANTICIPATION AND OBVIOUSNESS OPINIONS

127. As I explain in detail below, the asserted claims are either anticipated by or obvious over the prior art references described above. Broadly speaking, the

claimed codes represent the combination of RA codes, which were generally known by those of ordinary skill in the art by March 7, 2000, with irregularity, which had been shown years before to improve the performance of codes like RA codes.

128. One of ordinary skill in the art would have been motivated to combine these two ideas. RA codes are described in detail in Divsalar, published more than a year before the alleged conception date of the patents-in-suit. The concept of irregularity had been introduced by Luby in 1997, and by March 7, 2000 had been thoroughly explored in a number of papers and publications, including Frey99, MacKay, and the Luby '909 patent, discussed below (in particular, Frey99 teaches irregular *repetition*, which is specifically required by some of the asserted claims). By March 7, 2000, both RA codes and irregularity would have been common knowledge to one of ordinary skill in the art.

129. Indeed, prior to March 7, I myself suggested incorporating irregularity into RA codes. In particular, as described below, I suggested in an email to Dariush Divsalar that he make his RA codes irregular (*See* Email from Brendan Frey to Dariush Divsalar dated Dec. 8, 1999 (CALTECH000024021)). Consistent with the email I sent to Dr. Divsalar, making RA codes irregular was merely an obvious application of my earlier work on irregular turbocodes, which I presented at the Allerton 1999 conference, 6 months before Caltech's alleged conception date of March 7, 2000, and which is described in Frey99 and the Frey Slides.

130. I explain these opinions in further detail below, with reference to each limitation of the various claims that have been asserted by Caltech.

## VI. THE ASSERTED CLAIMS OF THE '710 PATENT ARE INVALID

131. As I explain below, asserted claims 1, 4, 6, 15, 20, and 22 of the '710 patent are invalid. I also explain why claims 3, 5, and 21, from which claims 4, 6, and 22

depend, respectively, are invalid. A summary of the opinions set forth in this section is given in the table below:

| '710 Claim | Frey 99 (or<br>Frey slides) | Frey99 (or Frey<br>slides) + Divsalar | Divsalar + Luby | Divsalar + MacKay |

|------------|-----------------------------|---------------------------------------|-----------------|-------------------|

| 1          | Anticipated                 | Anticipated by Frey or Obvious        | Obvious         | Obvious           |

| 3          | Anticipated                 | Anticipated<br>by Frey or Obvious     | Obvious         | Obvious           |

| 4          |                             | Obvious                               | Obvious         | Obvious           |

| 5          |                             | Obvious                               | Obvious         | Obvious           |

| 6          |                             | Obvious                               | Obvious         | Obvious           |

| 15         |                             | Obvious                               | Obvious         | Obvious           |

| 20         |                             | Obvious                               | Obvious         | Obvious           |

| 21         |                             | Obvious                               | Obvious         | Obvious           |

| 22         |                             | Obvious                               | Obvious         | Obvious           |

#### A. Claim 1 of the '710 Patent is Invalid

# 132. Claim 1 of the '710 patent reads:

1. A method of encoding a signal, comprising:

obtaining a block of data in the signal to be encoded;

partitioning said data block into a plurality of sub-blocks, each sub-block including a plurality of data elements;

first encoding the data block to from<sup>21</sup> a first encoded data block, said first encoding including repeating the data elements in different sub-blocks a different number of times;

interleaving the repeated data elements in the first encoded data block; and

second encoding said first encoded data block using an encoder that has a rate close to one.

## i) Claim 1 of the '710 Patent is Anticipated by Frey99

133. I explain below, one limitation at a time, why claim 1 is anticipated by Frey99.

<sup>&</sup>lt;sup>21</sup> I note that the word "from" here should be "form." That is, this limitation is about forming "a first encoded data block." Notwithstanding that typographical error, I have reproduced the claim as it is printed in the patent.

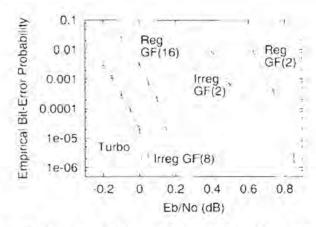

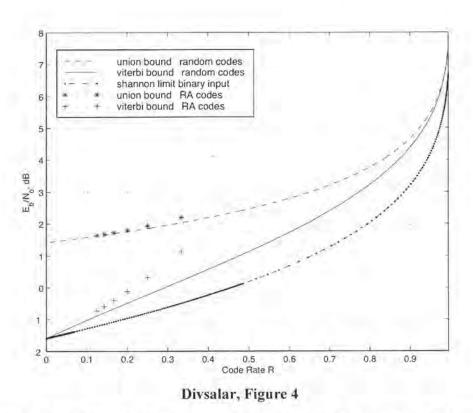

134. Even if the preamble limits the claim, it is taught by Frey99. As I explain above, Frey99 deals with the construction of irregular turbocodes. The purpose of the disclosed irregular turbocode is for the encoding and decoding of signals (*see also*, Frey Slides at 4). Frey99 explicitly discloses decoding signals that had been encoded using the disclosed irregular turbocode. *See*, *e.g.*, Frey99 at 4 ("*After receiving the channel output, the decoder computes* the channel output log-likelihood ratios ...") (emphasis added); 4 ("In our simulations, after each iteration, we check to see if the current decision gives a codeword. If it does, the iterations terminate and otherwise, *the decoder iterates further* ...") (emphasis added); 6 ("Fig. 4 shows the simulated BER-E<sub>b</sub>/N<sub>0</sub> curves for the original block length N-131,072 regular turbocode (dashed line) and its irregular cousin (solid line), using profile e = 10,  $f_e = 0.05$ "); *see also*, Frey Slides at 2 ("making decoding easier"); Frey Slides at 9, 11, 12 (showing BER- $E_b/N_0$  curves).

# b) "obtaining a block of data in the signal to be encoded"

135. Frey99 deals exclusively with block codes. For example, Frey99 includes experimental results comparing a regular code and an irregular code, both having "block length N = 131,082" (Frey99 at 6; see also Frey Slides at 13, teaching "long block lengths," and "short block lengths"). Frey99's use and discussion of that block length means that Frey99 takes bits in blocks of 131,082 and encodes them, just as is required by this claim limitation. Similarly, Frey99 also includes other discussion of obtaining data in blocks for encoding. For example, Frey99 describes experimental results relating to, e.g., the "block length" of irregular turbocodes. In selecting a coding profile, Frey99 teaches "making small changes to a <u>block length N = 10,000</u> version of the original rate R = 1/2 turbocode proposed by Berrou et al." (Frey99 at 5) (emphasis added). Also, Frey99 uses the "BER" or "block error rate" to compare the performance of various codes (see, e.g.,

Frey99 at Figure 4). Frey99's reference to "block error rate" means that Frey99 obtains data in blocks for encoding.

c) "partitioning said data block into a plurality of sub-blocks, each sub-block including a plurality of data elements"

136. Frey99 teaches this limitation. Frey99 describes irregular turbocodes as follows: "an *irregular turbocode* has the form shown in Fig. 2, which is a type 'trellis-constrained code' as described in [7]. We specify a *degree profile*,  $f_d \in [0, 1]$ ,  $d \in \{1, 2, ..., D\}$ .  $f_d$  is the fraction of codeword bits that have degree d and d is the maximum degree. Each codeword bit with degree d is repeated d times before being fed into the permuter. Several classes of permuter lead to linear-time encodable codes. In particular, if the bits in the convolutional code are partitioned into 'systematic bits' and 'parity bits', then by connecting each parity bit to a degree 1 codeword bit, we can encode in linear time." Frey99 at 2 (emphasis added).

137. As described above, Frey99 partitions the information bits into groups, where the bits in each group all have the same degree (*i.e.*, they are all repeated the same number of times). Frey99 also illustrates this operation graphically in Figure 2, reproduced below:

Figure 2: A general irregular turbocode. For d = 1, ..., D, fraction  $f_d$  of the codeword bits are repeated d times, permuted and connected to a convolutional code.

138. In Figure 2 of Frey99, the circles at the bottom represent information bits. The groups of information bits labeled  $f_2, f_3, ..., f_D$  represent sub-blocks into which the data block is partitioned (see also Frey Slides at 5).

139. Thus, the bits that are repeated twice (the bits labeled  $f_2$ ) constitute one subblock, the bits that are repeated three times (the bits labeled  $f_3$ ) constitute a second sub-block, and so on. As shown in Figure 2 of Frey99, each of these sub-blocks contains a plurality of bits (or "data elements"), as required by claim 1 of the '710 patent.

d) "first encoding the data block to from [sic] a first encoded data block, said first encoding including repeating the data elements in different sub-blocks a different number of times"

140. Frey99 teaches repeating the data elements in different sub-blocks a different number of times (which is commonly known as "irregular repetition" to those of ordinary skill in in the art).

141. For example, Figure 2 of Frey99, reproduced above, shows that the data elements in each sub-block are repeated a different number of times. In Figure 2 of Frey99, the circles at the bottom represent information bits in the data block. The groups of information bits labeled  $f_2$ ,  $f_3$ , ...,  $f_D$  represent sub-blocks into which the data block is partitioned. The blocks labeled "Rep 2," "Rep 3," and "Rep D" represent the step of repetition. For example, an information bit that is connected to a box labeled "Rep 2" is repeated twice, a bit connected to a box labeled "Rep 3" is repeated three times, etc.. In the figure above, the repeated bits are represented by the vertical lines connecting the "Rep n" boxes to the box labeled "Permuter" (see also Frey Slides at 5).

5

6

7

8

10

12

13

21

22

23

24