# UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

APPLE INC., Petitioner,

v.

CALIFORNIA INSTITUTE OF TECHNOLOGY, Patent Owner.

> Case IPR2017-00700 Patent 7,421,032 B2

Before KEN B. BARRETT, TREVOR M. JEFFERSON, and JOHN A. HUDALLA, *Administrative Patent Judges*.

BARRETT, Administrative Patent Judge.

DOCKET

DECISION Institution of *Inter Partes* Review 37 C.F.R. § 42.108

### I. INTRODUCTION

### A. Background and Summary

Apple Inc. ("Petitioner") filed a Petition requesting *inter partes* review of U.S. Patent No. 7,421,032 B2, issued September 2, 2008 ("the '032 patent," Ex. 1001). Paper 5 ("Pet."). The Petition challenges the patentability of claims 11–17 of the '032 patent on various grounds of obviousness under 35 U.S.C. § 103. California Institute of Technology ("Patent Owner") filed a Preliminary Response to the Petition. Paper 13 ("Prelim. Resp.").

An *inter partes* review may not be instituted "unless . . . the information presented in the petition . . . shows that there is a reasonable likelihood that the petitioner would prevail with respect to at least 1 of the claims challenged in the petition." 35 U.S.C. § 314(a). Having considered the arguments and evidence presented by Petitioner and Patent Owner, we determine that Petitioner has demonstrated a reasonable likelihood that it would prevail in establishing the unpatentability of challenged claims 11–16 of the '032 patent, and that Petitioner has not demonstrated a reasonable likelihood that it would prevail in establishing the unpatentability of claim 17 of the '032 patent.

## B. Related Proceedings

One or both parties identify, as matters involving or related to the '032 patent, *Cal. Inst. of Tech. v. Broadcom Ltd.*, No. 2:16-cv-03714 (C.D. Cal. filed May 26, 2016) and *Cal. Inst. of Tech. v. Hughes Commc'ns, Inc.*, 2:13-cv-07245 (C.D. Cal. filed Oct. 1, 2013), and Patent Trial and Appeal Board cases IPR2015-00059, IPR2015-00060, IPR2015-00061, IPR 2015-00067, IPR2015-00068, IPR2015-00081, IPR2017-00210, IPR2017-00211, IPR2017-00700 Patent 7,421,032 B2

# IPR2017-00219, IPR2017-00297, IPR2017-00423, IPR2017-00701, and IPR2017-00728. Pet. 3, Paper 7.

C. The '032 Patent

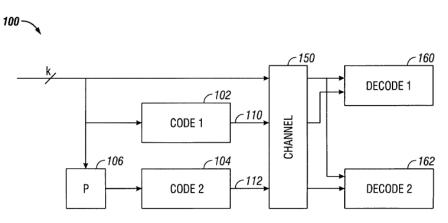

The '032 patent is titled "Serial Concatenation of Interleaved Convolutional Codes Forming Turbo-Like Codes." The '032 patent explains some of the prior art with reference to its Figure 1, reproduced below.

Figure 1 is a schematic diagram of a prior "turbo code" system. Ex. 1001,

2:16–17. The '032 patent specification describes Figure 1 as follows:

A block of k information bits is input directly to a first coder 102. A k bit interleaver 106 also receives the k bits and interleaves them prior to applying them to a second coder 104. The second coder produces an output that has more bits than its input, that is, it is a coder with rate that is less than 1. The coders 102, 104 are typically recursive convolutional coders.

Three different items are sent over the channel 150: the original k bits, first encoded bits 110, and second encoded bits 112. At the decoding end, two decoders are used: a first constituent decoder 160 and a second constituent decoder 162. Each receives both the original k bits, and one of the encoded portions 110, 112. Each decoder sends likelihood estimates of the decoded bits to the other decoders. The estimates are used to decode the uncoded information bits as corrupted by the noisy channel.

*Id.* at 1:41–56.

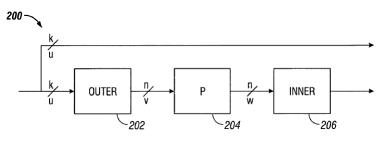

A coder 200, according to a first embodiment of the invention, is described with respect to Figure 2, reproduced below.

Figure 2 of the '032 patent is a schematic diagram of coder 200.

The coder 200 may include an outer coder 202, an interleaver 204, and inner coder 206.... The outer coder 202 receives the uncoded data. The data may be partitioned into blocks of fixed size, say k bits. The outer coder may be an (n,k) binary linear block coder, where n>k. The coder accepts as input a block u of k data bits and produces an output block v of n data bits. The mathematical relationship between u and v is  $v=T_0u$ , where  $T_0$  is an  $n\times k$  matrix, and the rate<sup>[1]</sup> of the coder is k/n.

The rate of the coder may be irregular, that is, the value of  $T_0$  is not constant, and may differ for sub-blocks of bits in the data block. In an embodiment, the outer coder 202 is a repeater that repeats the k bits in a block a number of times q to produce a block with n bits, where n=qk. Since the repeater has an irregular output, different bits in the block may be repeated a different number of times. For example, a fraction of the bits in the block may be repeated two times, a fraction of bits may be repeated four times. These fractions define a degree sequence, or degree profile, of the code.

The inner coder 206 may be a linear rate-1 coder, which means that the n-bit output block x can be written as  $x=T_Iw$ , where  $T_I$  is a nonsingular n×n matrix. The inner coder 210 can

<sup>&</sup>lt;sup>1</sup> We understand that the "rate" of an encoder refers to the ratio of the number of input bits to the number of resulting encoded output bits related to those input bits.

have a rate that is close to 1, e.g., within 50%, more preferably 10% and perhaps even more preferably within 1 % of 1.

*Id.* at 2:36–60. In an embodiment, the second ("inner") encoder 206 is an accumulator. *Id.* at 2:66–67. "The serial concatenation of the interleaved irregular repeat code and the accumulate code produces an irregular repeat and accumulate (IRA) code." *Id.* at 3:30–32.

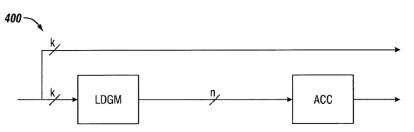

Figure 4 of the '032 patent is reproduced below.

Figure 4 shows an alternative embodiment in which the outer encoder is a low-density generator matrix (LDGM). *Id.* at 3:56–59. LDGM codes have a "sparse" generator matrix. *Id.* at 3:59–60. The IRA code produced is a serial concatenation of the LDGM code and the accumulator code. *Id.* at 3:60–62. No interleaver (as in the Figure 2 embodiment) is required in the Figure 4 arrangement because the LDGM provides scrambling otherwise provided by the interleaver in the Figure 2 embodiment. *Id.* at 3:62–64.

"The set of parity checks may be represented in a bipartite graph, called the Tanner graph, of the code." *Id.* at 3:33–35. Figure 3, shown below, depicts such a Tanner graph.

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.