### US005436621A

## United States Patent [19]

Macko et al.

[11] Patent Number:

5,436,621

[45] Date of Patent:

Jul. 25, 1995

### [54] MESSAGING PERIPHERAL WITH SECURE MESSAGE DATA FUNCTION

[75] Inventors: William J. Macko, West Palm Beach; Greg Cannon, Delray Beach, both of

Fla.

[73] Assignee: Motorola, Inc., Schaumburg, Ill.

[21] Appl. No.: 84,905

[22] Filed: Jul. 2, 1993

340/825.34

### [56] References Cited

### U.S. PATENT DOCUMENTS

| 4,806,906 | 2/1989  | Oda et al           | 340/825.44  |

|-----------|---------|---------------------|-------------|

| 4,839,628 | 6/1989  | Davis et al         | . 340/311.1 |

| 4,857,883 | 8/1989  | Mama                | . 340/311.1 |

| 5,012,234 | 4/1991  | Dulaney et al       | 340/825.31  |

| 5,043,721 | 8/1991  | May                 | 340/825.44  |

| 5,060,263 | 10/1991 | Bosen et al         | 340/825.31  |

| 5,073,767 | 12/1991 | Holmes et al        | 340/825.44  |

| 5,146,217 | 9/1992  | Holmes et al        | 340/825.34  |

| 5,151,694 | 9/1992  | Yamasaki            | 340/825.44  |

| 5,281,962 | 1/1994  | Vanden Heuvel et al | 340/825.27  |

| 5,302,947 | 4/1994  | Fuller et al        | 340/825.44  |

|           |         |                     |             |

### FOREIGN PATENT DOCUMENTS

90/13213 11/1990 WIPO .

#### OTHER PUBLICATIONS

PC Card Standard Release 2.0, Personal Computer Memory Card International Association, Sep. 1991.

Primary Examiner—Donald J. Yusko Assistant Examiner—Mark H. Rinehart Attorney, Agent, or Firm—Gregg E. Rasor

### 57] ABSTRACT

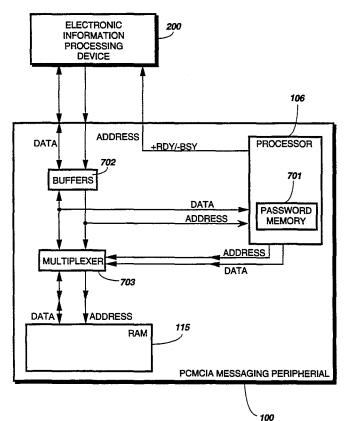

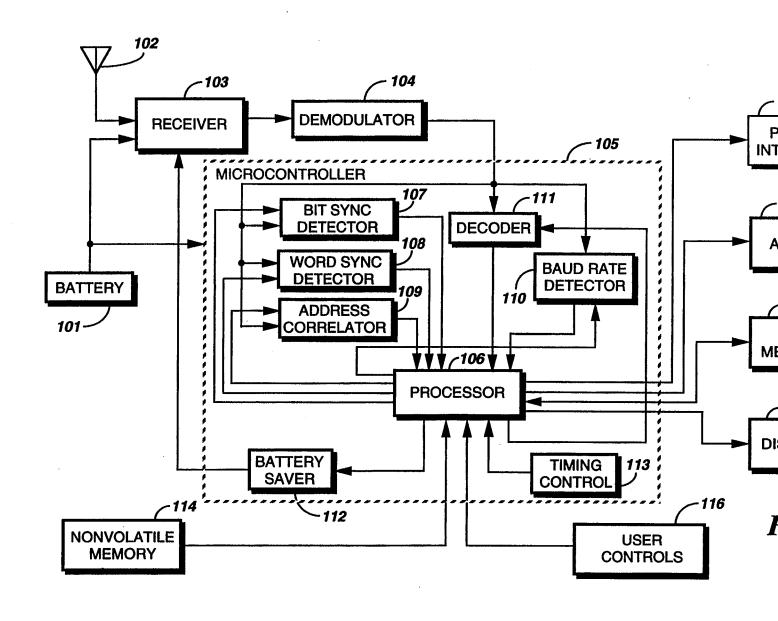

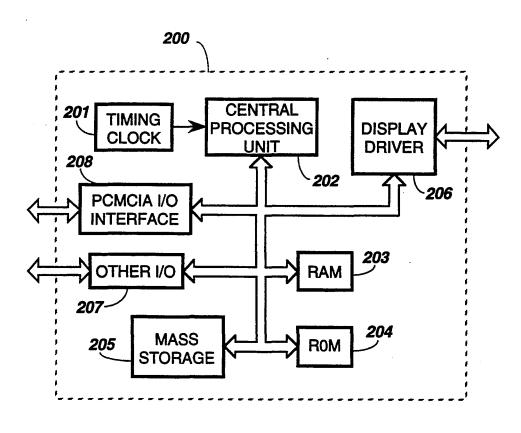

A messaging peripheral (100) includes a processor (106) for executing a microcode program that controls operation of the messaging peripheral (100), and a PCMCIA memory only interface (119) that allows communication of communication of at least one message and a user selectable password between an electronic information processing device (200) and the messaging peripheral (100). The PCMCIA memory only interface couples to a secure memory access interface that is controlled by the processor (106). The secure memory access interface (703) allows the electronic information processing device (200) to access the at least one message when a memory protection mode is selected and the processor (106) receives a user entered password and performs a correlation between the user entered password and the user selectable password.

### 18 Claims, 8 Drawing Sheets

**FIG. 2**

| Pin | Signal  | VO  | Function          | +/- |

|-----|---------|-----|-------------------|-----|

| 1   | GND     |     | Ground            |     |

| 2   | D3      | 1/0 | Data bit 3        |     |

| 3   | D4      | 1/0 | Data bit 4        |     |

| 4   | D5      | VO  | Data bit 5        |     |

| 5   | D6      | 1/0 | Data bit 6        |     |

| 6   | D7      | 1/0 | Data bit 7        |     |

| 7   | CE1     | i   | Card enable       | -   |

| 8   | A10     | 1   | Address bit 10    |     |

| 9   | OE      | l   | Output enable     | -   |

| 10  | A11     | I   | Address bit 11    |     |

| 11  | A9      | 1   | Address bit 9     |     |

| 12  | A8      | 1   | Address bit 8     |     |

| 13  | A13     | ı   | Address bit 13    |     |

| 14  | A14     | i   | Address bit 14    |     |

| 15  | WE/PGM  | ı   | Write enable      | -   |

| 16  | RDY/BSY | 0   | Ready/Busy        | +/- |

| 17  | Vcc     |     | Power Supply      |     |

| 18  | Vpp1    |     | Programming and   |     |

|     |         |     | Peripheral Supply |     |

| 19  | A16     | 1   | Address bit 16    |     |

| 20  | A15     | ı   | Address bit 15    |     |

| 21  | A12     | ı   | Address bit 12    |     |

| 22  | A7      | 1   | Address bit 7     |     |

| 23  | A6      | 1   | Address bit 6     |     |

| 24  | A5      | Ī   | Address bit 5     |     |

| 25  | A4      | 1   | Address bit 4     |     |

| 26  | A3      | ı   | Address bit 3     |     |

| 27  | A2      | Ī   | Address bit 2     |     |

| 28  | A1      | I   | Address bit 1     |     |

| 29  | A0      | 1   | Address bit 0     |     |

| 30  | D0      | 1/0 | Data bit 0        |     |

| 31  | D1      | 1/0 | Data bit 1        |     |

| 32  | D2      | VO  | Data bit 2        |     |

| 33  | WP      | 0   | Write protect     | -   |

| 34  | GND     |     | Ground            |     |

| Pin | Signal | I/O | Function                 | +/- |

|-----|--------|-----|--------------------------|-----|

| 35  | GND    |     | Ground                   |     |

| 36  | CD1    | 0   | Card Detect              | -   |

| 37  | D11    | VO  | Data bit 11              |     |

| 38  | D12    | VO  | Data bit 12              |     |

| 39  | D13    | VO  | Data bit 13              |     |

| 40  | D14    | 1/0 | Data bit 14              |     |

| 41  | D15    | 1/0 | Data bit 15              |     |

| 42  | CE2    | I   | Card enable              | -   |

| 43  | RFSH   | 1   | Refresh                  |     |

| 44  | RFU    |     | Reserved                 |     |

| 45  | RFU    |     | Reserved                 |     |

| 46  | A17    | 1   | Address bit 17           |     |

| 47  | A18    | I   | Address bit 18           |     |

| 48  | A19    | 1   | Address bit 19           |     |

| 49  | A20    | I   | Address bit 20           |     |

| 50  | A21    | l   | Address bit 21           |     |

| 51  | Vcc    |     | Power Supply             |     |

| 52  | Vpp2   |     | Programming and          |     |

|     |        |     | Peripheral Supply 2      |     |

| 53  | A22    | 1   | Address bit 22           |     |

| 54  | A23    | 1   | Address bit 23           | :   |

| 55  | A24    |     | Address bit 24           |     |

| 56  | A25    | l   | Address bit 25           |     |

| 57  | RFU    |     | Reserved                 |     |

| 58  | RESET  | 1   | Card Reset               | +   |

| 59  | WAIT   | 0   | Extend bus cycle         | -   |

| 60  | RFU    |     | Reserved                 | -   |

| 61  | REG    | 1   | Register select          | -   |

| 62  | BVD2   | 0   | Battery voltage detect 2 |     |

| 63  | BVD1   | 0   | Battery voltage detect 1 |     |

| 64  | D8     | 1/0 | Data bit 8               |     |

| 65  | D9     | 1/0 | Data bit 9               |     |

| 66  | D10    | 1/0 | Data bit 10              |     |

| 67  | CD2    | 0   | Card detect              | -   |

| 68  | GND    |     | Ground                   |     |

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.