[45] Date of Patent:

Nov. 25, 1986

## [54] AUTOMATED TELEPHONE VOICE SERVICE SYSTEM

|      | 3          |                                      |

|------|------------|--------------------------------------|

| [76] | Inventors: | Lawrence A. Lotito, 6625 Springpark  |

|      |            | Ave., Los Angeles, Calif. 90056;     |

|      |            | Teresa D. Huxford, 1822 Pandora      |

|      |            | Ave., #3, Los Angeles, Calif. 90025; |

|      |            | Ann L. Donaldson, 2321 W. 232nd      |

|      |            | St Torrence Calif 90501              |

| [21] | Appl. No.: 445,   | ,651                          |        |

|------|-------------------|-------------------------------|--------|

| [22] | Filed: Nov        | 7. 30, 1982                   |        |

| [51] | Int. Cl.4         | H04M 3/38; H04M               | 3/50   |

| [52] | U.S. Cl           | 379/88; 379                   | )/196; |

|      |                   | 37                            | 9/211  |

| [58] | Field of Search . | 179/18 B, 18 D, 18            | DA,    |

|      |                   | 6.17, 6.18, 6.09, 6.11: 360/3 |        |

# [56] References Cited

# U.S. PATENT DOCUMENTS

364/513.5, 513; 381/36, 51; 370/60, 61, 62

| Re. 30,903 | 4/1982  | Vicari et al 179/27 FH    |

|------------|---------|---------------------------|

| 1,922,879  | 8/1933  | Burgener 179/27 FH        |

| 2,685,614  | 8/1954  | Curtin 179/27 FH          |

| 2,863,950  | 12/1958 | Dunning et al 179/27 FH   |

| 2,892,038  | 6/1959  | Gatzert 179/27 FH         |

| 2,985,721  | 5/1961  | Gatzert 179/27 FH         |

| 2,998,489  | 8/1961  | Riesz 179/6.02            |

| 3,141,931  | 7/1964  | Zarouni 179/6.11          |

| 3,146,310  | 8/1964  | Jeffries et al 179/6.07   |

| 3,197,566  | 7/1965  | Sanders et al 179/18 BE   |

| 3,273,260  | 9/1966  | Walker 434/307            |

| 3,296,371  | 1/1967  | Fox 381/51                |

| 3,510,598  | 5/1970  | Ballin et al 179/18 BE    |

| 3,519,745  | 7/1970  | Colman 179/5 P            |

| 3,728,486  | 4/1973  | Kraus 179/2 R             |

| 3,733,440  | 5/1973  | Sipes 179/18 B            |

| 3,920,908  | 11/1975 | Kraus 179/2 CA            |

| 4,117,270  | 9/1978  | Lesea 179/18 BE           |

| 4,200,772  | 4/1980  | Vicari et al 179/27 FH    |

| 4,210,783  | 7/1980  | Vicari et al 179/18 FC    |

| 4,256,928  | 3/1981  | Lesea et al 179/18 BE     |

| 4,272,810  | 6/1981  | Gates et al 364/900       |

| 4,302,632  | 11/1981 | Vicari et al 179/27 FH    |

| 4,320,256  | 3/1982  | Freeman 179/6.04          |

| 4,371,752  | 2/1983  | Matthews et al 179/7.1 TP |

|            |         |                           |

# OTHER PUBLICATIONS

"Store & Forward Voice Switching", International

Resource Development, Inc., Report #145, pp. 45-56, Jan. 1980.

"A Design Model for a Real-Time Voice Storage System", Hattori et al., *IEEE Trans. on Communications*, vol. COM-30, No. 1, Jan. 1982, pp. 53-57.

Barish, Bernard T. and Slattery, Paul J., "BISCOM: Rx for Internal Communications", *Bell Laboratories Record*, vol. 42, No. 6, pp. 175-180 (Jun. 1974).

Watson, Jr., R. E. and S. B. Weinberg, "Telephone Answering Services," *Bell Laboratories Record*, vol. 43, No. 12, pp. 447–450 (Dec. 1965).

Liske, W., "Remote Controlled Switching of the Telephone Message Service of the Deutsche Bundespost," *TN-Nachrichten* vol. 70, pp. 13-16 (1970).

TN-Nachrichten vol. 70, pp. 13-16 (1970).

Probe Research, Inc., "ECS Telecommunications, Inc.," Proceedings of Voice Processing Seminar, Sep. 15, 1982.

Probe Research, Inc., "Voice Message Service," Proceedings of Voice Processing Seminar, Sep. 15, 1982.

Probe Research, Inc., "Logic Labs, Inc." Proceedings of Voice Processing Seminar, Sep. 15, 1982.

List Continued on next page.

### Primary Examiner-Thomas W. Brown

## [57] ABSTRACT

An automated telephone voice service system includes a data store having a plurality of addressable voice storage message baskets defined therein and a control system coupled between the store and a large plurality of telephone lines of a telephone network. An incoming cable may address a particular message basket by entering a code through the telephone keyboard or by a predetermined association with a particular call in line. Upon identification of the message basket the caller is greeted by a client's own voice and invited to leave a voice message which will be recorded in the message basket or given other client information. Upon entry of a personal identification code a caller is granted access to user account functions which include retrieval of voice messages, forwarding of messages to other message baskets or telephone lines, and administrative functions such as the changing of greetings or account operating criteria. Editing commands may be utilized during the recording of voice messages.

74 Claims, 27 Drawing Figures

#### OTHER PUBLICATIONS

Probe Research, Inc., "BBL Industries, Inc.," Proceedings of Voice Processing Seminar, Sep. 15, 1958. Probe Research, Inc., "Wang Laboratories," Proceedings of Voice Processing Seminar, Sep. 16, 1982.

Probe Research, Inc., "American Telephone and Tele-

graph, Inc.," Proceedings of Voice Processing Seminar, Sep. 16, 1982.

Probe Research, Inc., "Commterm, Inc.," Proceedings of Voice Processing Seminar, Sep. 16, 1982.

Probe Research, Inc., "American Express Company," Proceedings of Voice Processing Seminar, Sep. 16, 1982. Probe Research, Inc. "Equitable Life Assurance," Proceedings of Voice Processing Seminar, Sep. 16, 1982. Probe Research, Inc., "Massachusetts General Hospi-

tal," Proceedings of Voice Processing Seminar, Sep. 16,

Seaman, John, "Electronic Mail Coming at You," Com-

puter Decisions, pp. 129-160 (Oct. 1982).

"Voice Mail Update," Electronic Mail & Message Systems, vol. 4, No. 20 (Oct. 15, 1980).

Hanson, Bruce L., R. J. Nacon and D. P. Worrall, "Custom Calling Features Cater to Customers," Tele-

phony, pp. 28-32 (Sep. 1980). "Elect. Mail Pack Unveiled by DÉC." Electronic News, vol. 27, No. 1365 (Nov. 21, 1981).

ECS Telecommunications, Inc. Marketing Literature for their UMX System (Jan. 7, 1982).

Memo from C. W. Murphy to Jack Atkin Dated Jan. 30,

"ECS Unveils 1,000-User Digital Message Exchange," Communications.

Matthews, G. H., "The Pitfalls of Small Telecommunications Trunk Groups," ECS Telecommunications, Inc,

"New Product, Voice Message Systems," Business Communications Review pp. 37-40 (Jan.-Feb. 1981). Dukes, A., "IBM Unveils Voice Mailbox; Seen as Step Toward PBX," MIS Week, vol. 2, No. 39 (Sep. 30,

"Speechfile—IBM's Secret Message System Weapon," Electronic Mail & Message Systems, vol. 5, No. 12 (Jun. 15, 1981).

"Introducing Voice Store & Forward," Computer Decisions, (Oct. 1981).

Out Voice Product Brochures, Voice and Data Systems, Inc.

Dukes, A., "Atlanta Firm Enters Voice-Message Arena," Management Information Systems Week, p. 6 (Nov. 18, 1981).

"New Local Net, Voice Store and Forward from Wang," Computer Decisions (Aug. 1981).

Delphi Delta 1 Telephone Operator's Training Manual (Apr. 1, 1981).

Delphi Delta 1 Voicebank Data Entry Reference Manual (Jul. 20, 1981).

Delphi Delta 1 Voicebank Marketing Literature.

Delphi Delta 1 Specification.

Delphi Delta 1 Standard Processor Module (SPM-1) Specification (Mar. 13, 1978).

Delphi Pascal Programmers Manual (May 22, 1981).

TELEPHONE VOICE SERVICE SYSTEM 100

FIG.2

TELEPHONE ROOM SUBSYSTEM A, LINE GROUP 1 206

FIG:3

REAL TIME SUBSYSTEM 230

FIG.5

ISS PROCESSOR EXTENSION UNIT 726

FIG.8

FIG.9

BUS CONTROLLER EXTENSION 922

FIG.IO

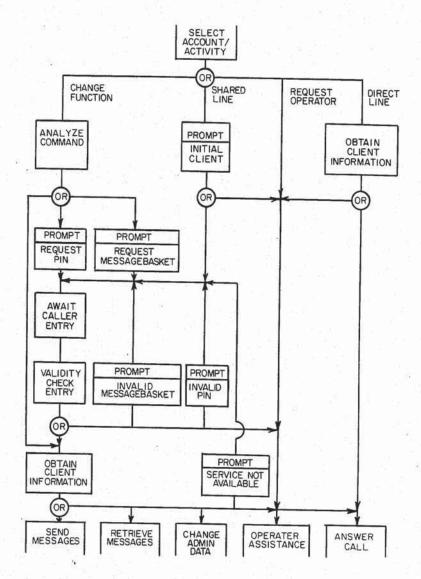

SELECT ACTIVITY FUNCTIONAL FLOW

FIG.15

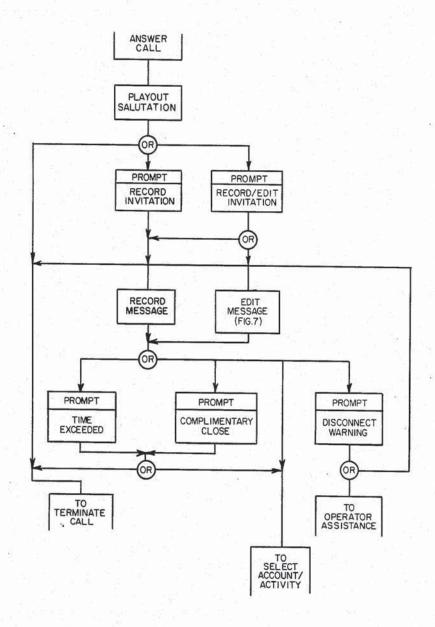

FIG.16 ANSWER CALL FUNCTIONAL FLOW

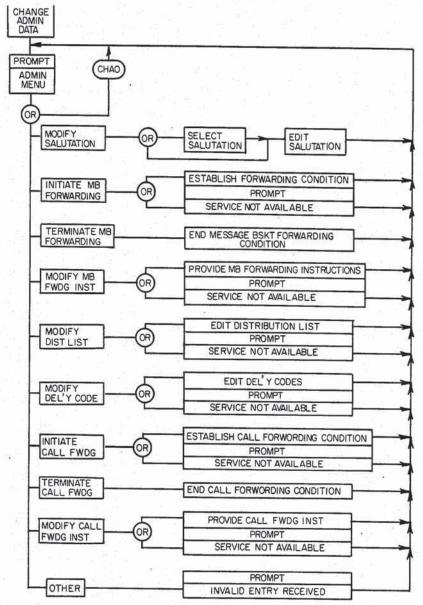

FIG. 25 ADMIN FUNCTIONAL FLOW

# AUTOMATED TELEPHONE VOICE SERVICE SYSTEM

#### BACKGROUND OF THE INVENTION

1. Field of the Invention

This invention relates to an automated telephone voice service system and more particularly to such a system which provides automatic recording and editing of voice messages as well as forwarding of recorded voice messages to other accounts and telephone numbers with or without operator assistance.

2. Discussion of the Prior Art

Voice responsive telephone service systems have traditionally meant either a telephone answering service or a forwarding service. Early telephone answering service systems connected individual secretarial lines to an operator plug board. Upon activation of one of 100 or more lines coming into an operator station an operator answered the call by making an appropriate plug connection between the active line and an operator headset. Upon identification of an active line the operator could access a corresponding client file to obtain a greeting for reading to the caller. The operator could then proceed to answer questions from information 25 from the client file information or take a handwritten message for storage in a client pidgeon hole until the client called in to retrieve his messages.

Telephone answering systems have subsequently been improved by providing the service operator with a semi-automated terminal to which calls are automatically directed. The line to be answered is automatically identified and corresponding client data is presented to a visual display for use by the operator in answering the call. Any received messages may be keyed into the system for storage in association with the client's account until the client calls to retrieve his messages.

While such a system affords considerable improvement over the early plugboard answering systems, it remains limited to a basic telephone answering mode in 40 which limited client information may be presented to a client and messages may be manually recorded for later retrieval by the client.

The forwarding services provide a somewhat different but still limited telephone service function. These 45 services include store and forward services and call forwarding services. The store and forward services enable a client to record a message and designate a number of persons or telephone numbers for delivery of the message. Delivery instructions can specify dates and 50 times for message delivery. The operator then proceeds to call the indicated persons or numbers in accordance with the delivery instructions and upon completing a call, play the prerecorded message. Such a system permits recording of a message at one time for delivery at 55 another time, but still requires operator assistance.

Call forwarding on the other hand can be completely automated, but merely forwards an incoming call to a previously designated telephone line. Such a system cannot process the call if either the originally called line 60 or the forwarded line are busy and cannot process a message at different times which are respectively convenient to the calling and called parties.

## SUMMARY OF THE INVENTION

An automated telephone voice service system in accordance with the invention includes a data store coupled to store and retrieve voice messages at each of a plurality of individually addressable message baskets therein and a control system providing a selective coupling between the store and each of a plurality of telephone lines of a telephone network. The control system is responsive to different data signals received over a particular one of the telephone lines to associate the particular telephone line with a particular message basket, to store in the particular message basket a voice message received over the particular telephone line, to forward a voice message stored in the particular message basket to at least one other of the individually addressable message baskets, and to forward a voice message stored in the particular message basket to at least one telephone line.

The service system is implemented with a high reliability fail soft data processing system in which duplication of processing system components enables a function of a failed component to be transferred to another component to assure that no single failure disables the entire system. The major processor subsystems include a real-time subsystem providing interactive coupling to the analog telephone lines, an interactive services subsystem providing a coupling to input-output devices such as terminals, tape drives, and printers, a file services subsystem hosting a plurality of disk drives, an information processing subsystem providing a sophisticated general multiprocessor capability and an executive services subsystem providing communication and coordination between the other subsystems.

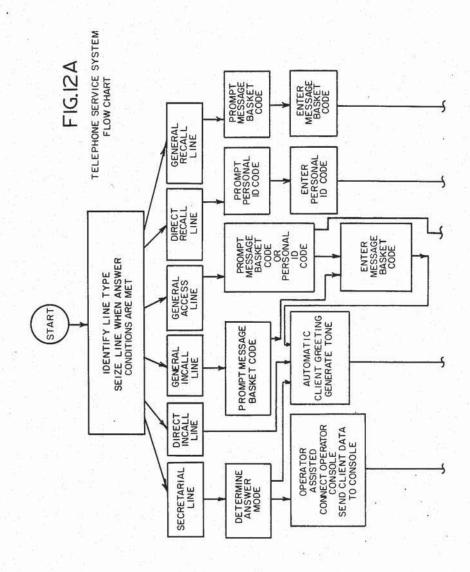

The real time subsystem provides the signal generating, signal detection and interface circuitry necessary for connection to several different physical and functional types of standard network telephone lines. The physically different types of lines include, two-wire lines, four-wire lines, pay telephone lines, operator lines and concentrator lines. The functionally different lines include secretarial lines which are usually coupled through a concentrator and function as jumped extensions of client telephone lines, and direct inward dial lines having virtual connections between an incoming line at a telephone switching office and a called telephone at a customer location (i.e. the telephone voice service system). Plural trunking connections to the service system concentrator and to the direct inward dial lines enable multiple calls to the same number to be processed simultaneously by the service system. Instead of a second or third caller to a given phone number receiving an irritating busy signal, the caller receives a prompt and efficient automatic response.

At the service system particular lines may be internally assigned predetermined designated functions. For example, some of the lines may be designated direct incall lines with each being assigned a predetermined association with a particular message basket. Such a line is controlled only in a telephone answering mode with a caller being greeted by a client selected voice message which may be in the client's own voice and changed at will and then invited to leave a voice message in the associated message basket upon the generation of a tone signal. Callers familiar with the system may edit the voice message using Touch Tone commands, but no editing prompts are provided. There is thus no confusion of callers who are unfamiliar with the system and who wish to simply record an unedited voice message upon the occurrence of the tone.

General incall lines are operated in a telephone answering mode in a manner similar to the direct incall

lines except that the general incall lines do not have a unique, predetermined association with a particular message basket. A caller is prompted to enter through the telephone keyboard dual tone multiple frequency (DTMF) data signals defining commands which select a 5 particular message basket code or address. A voice communication coupling between the calling telephone line and the selected particular message basket is then created by the telephone service system.

Other telephone lines may be assigned as direct or 10 a 5 second time out. general recall lines which afford a client access to account ownership functions afforded by the system. As with the incall lines each direct recall line is associated with a single predetermined message basket while a general recall lines requires entry of a message basket 15 code identifying a desired message basket. Security is maintained by enabling account ownership activities only after a personal identification code has been entered which corresponds to an associated message basket. Added security may be implemented for a direct 20 recall line by requiring entry of a second field of a personal identification code before account ownership activities are enabled. The second field is separated from the first field by a number sign key center and may be changed at any time by the account owner. Account 25 entry thus requires a caller to have knowledge of the direct recall telephone phone number, the first field of the personal identification code associated therewith, and if used, the second field of the personal identification code.

Account ownership activities include retrieval of messages, forwarding of messages, and administrative functions such as the recording of a new greeting, the changing of answering criteria for a secretarial line or the changing of the second field of the personal identifi- 35 cation code. Each message basket is divided into two parts, an inbasket which stores messages from outside callers and an outbasket which stores messages for forwarding to other inbaskets or telephone lines. Data storage space is conceived by storing only a single copy 40 of an outgoing voice message in the client's outbasket, even if the message is to be sent to many different parties.

If the message is to be sent to other message baskets a code is placed in the inbasket of each inbasket portion 45 thereof identifying the particular voice message in the particular outbasket of the sending client. If the message is to be communicated over one or more telephone lines, the outbasket message is simply accessed as the calls are initiated. This arrangement also enables a client 50 to retain ownership of a message so that a message can be changed or deleted until it has actually been deliv-

As a message is delivered to another service client the recipient can direct that the message be stored in the 55 recipient's inbasket for future reference and can automatically direct a voice message reply back to the sender with or without the original message attached.

A general access line affords a caller access to all voice service system functions. Any message basket 60 may be selected for leaving a message therein by entering the message basket number code therefor and entry of a personal identification number code enables access to account ownership activities. To minimize errors and enable the service system to readily distinguish between 65 different types of data sets, different data sets are required to have mutually exclusive code ranges. For example, one digit defines a delivery code selecting a

predetermined set of voice message delivery instructions, two digits define a predetermined distribution list, three to nine digits define a message basket number and ten or more digits define a telephone number including the area code even for a local number. A personal identification number code must be preceded by an asterisk (\*) and may have any reasonable number of digits within predetermined limits for the system, for example 3-15. All data sets are terminated by an # (enter) key or

In the event a system user requires assistance, more detailed voice message prompts are initiated by keying \*0 and communication with a voice message operator can be commanded by keying \*20. In the event that a client calls the system from a dial telephone, the service system detects a telephone company signal identifying a dial telephone line as the source of the call and automatically connects a service system operator to the line. The telephone service system in accordance with the invention thus provides a sophisticated user controlled system for the receipt and delivery of voice messages with an operator being required only for exceptional circumstances.

#### BRIEF DESCRIPTION OF THE DRAWINGS

A better understanding of the invention may be had from a consideration of the following Detailed Description taken in conjunction with the accompanying drawings in which:

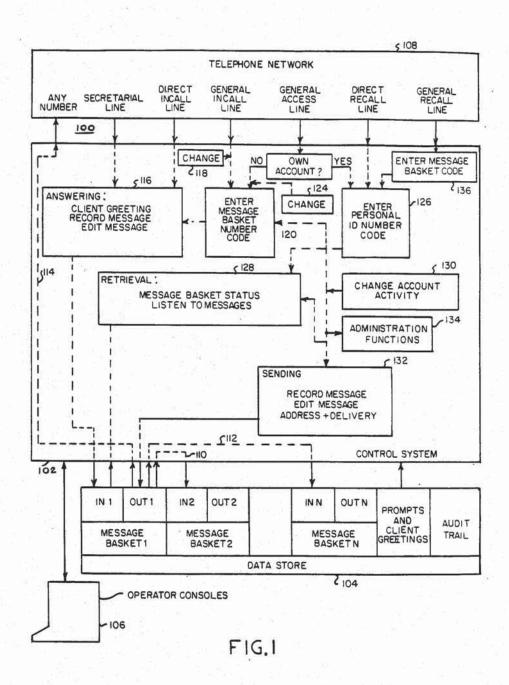

FIG. 1 is a functional block diagram representation of an automated telephone voice service system in accordance with the invention;

FIG. 2 is a block diagram representation of the system architecture for voice service system shown in FIG. 1;

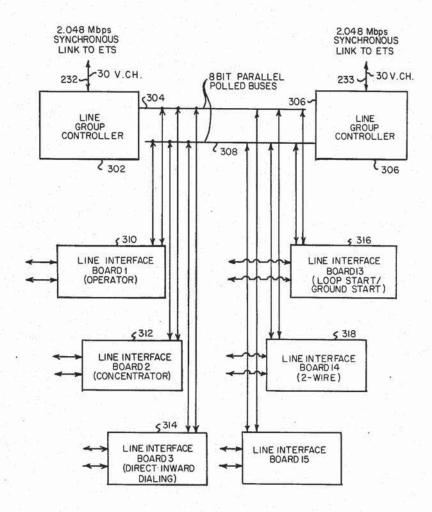

FIG. 3 is a block diagram representation of a telephone room subsystem line group used in the telephone voice service system shown in FIG. 2:

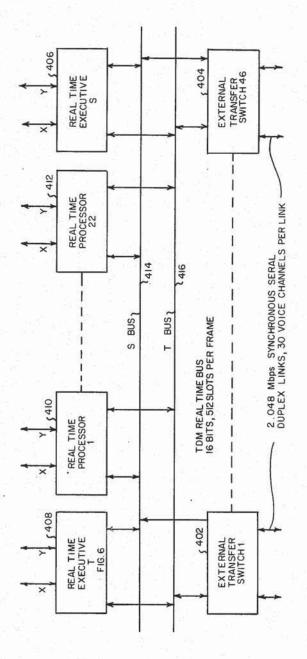

FIG. 4 is a block diagram representation of a real time subsystem used in the telephone voice service system shown in FIG. 2:

FIG. 5 is a block diagram representation of a standard processor module used in the voice service system shown in FIG. 1:

FIG. 6 is a block diagram representation of a real time executive used in the real time subsystem shown in FIG.

FIG. 7 is a block diagram representation of an interactive services subsystem used in the telephone voice service system shown in FIG. 2:

FIG. 8 is a block diagram representation of an interactive services subsystem processor extension unit shown in FIG. 7;

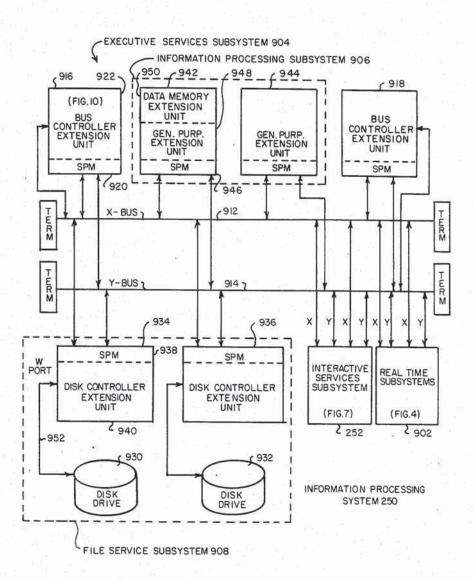

FIG. 9 is a block diagram representation of an information processing system shown in FIG. 2;

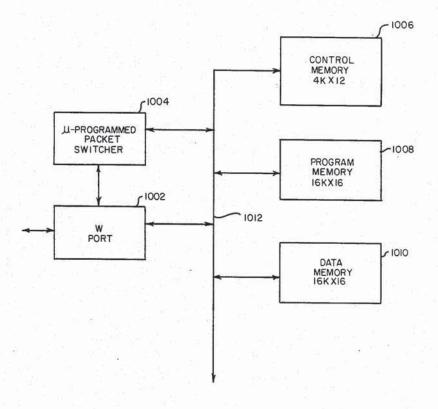

FIG. 10 is a block diagram representation of a bus controller extension unit shown in FIG. 9;

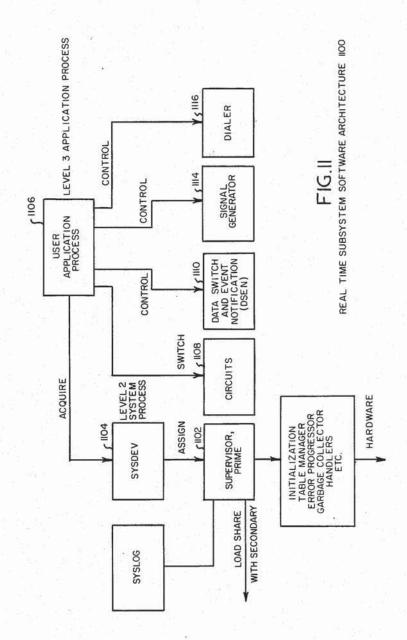

FIG. 11 is a block diagram representation of the software architecture for the real time subsystem shown in FIG. 4:

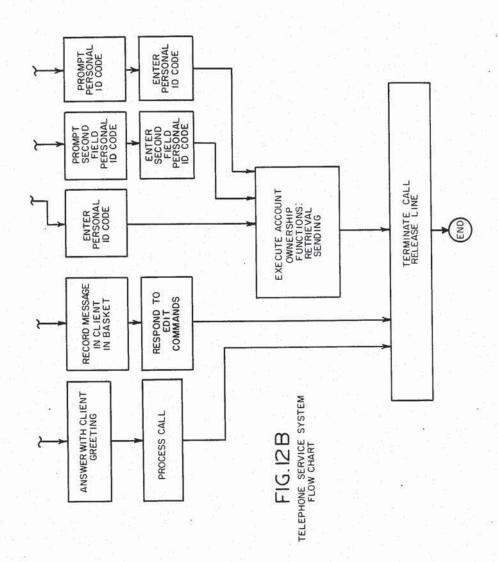

FIG. 12A in conjunction with FIG. 12B is a flow diagram describing the response of the automatic telephone voice service system to a user call;

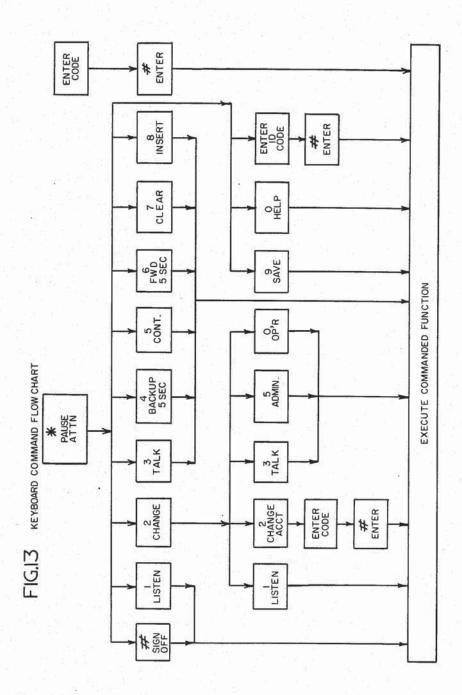

FIG. 13 is a flow diagram of telephone keyboard command operations.

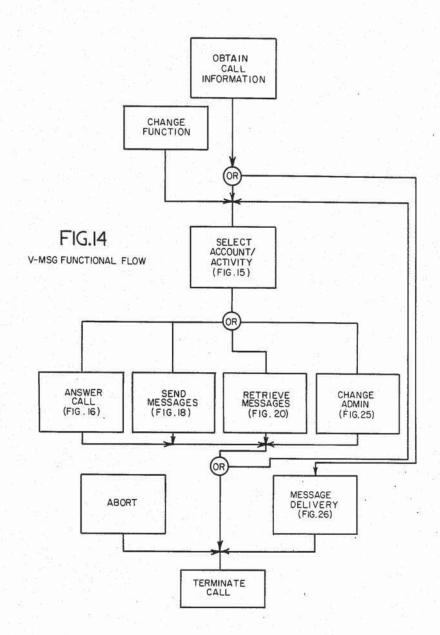

FIG. 14 is a voice messaging functional flow diagram for the service system shown in FIG. 1;

FIG. 15 is a select activity functional flow diagram that is useful in understanding the diagram shown in FIG. 14:

FIG. 16 is an answer call functional flow diagram that is useful in understanding the diagram shown in 5 FIG. 14.

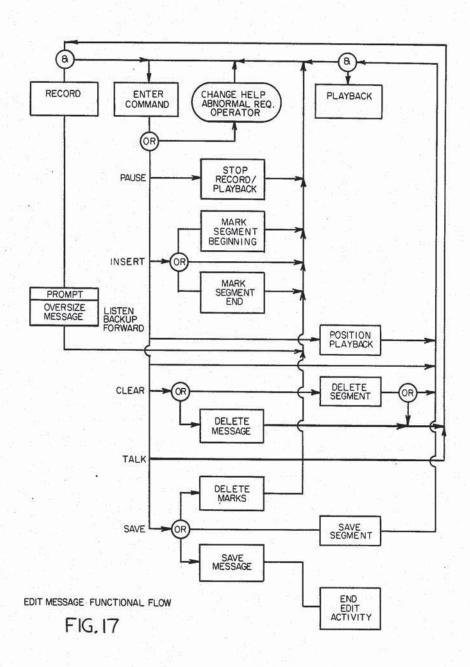

FIG. 17 is an edit message functional flow diagram that is useful in understanding the diagram shown in FIG. 16:

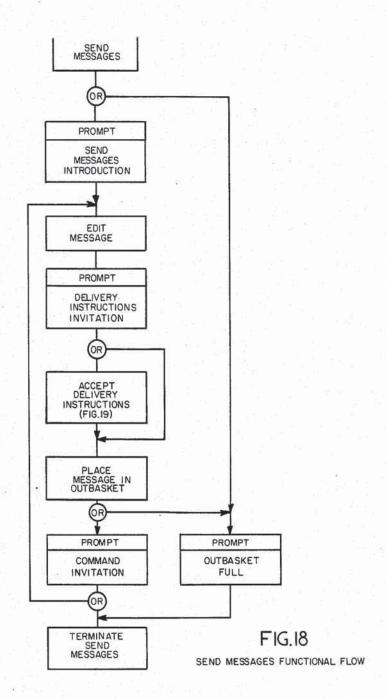

FIG. 18 is a send messages functional flow diagram 10 that is useful in understanding the diagram shown in FIG. 14.

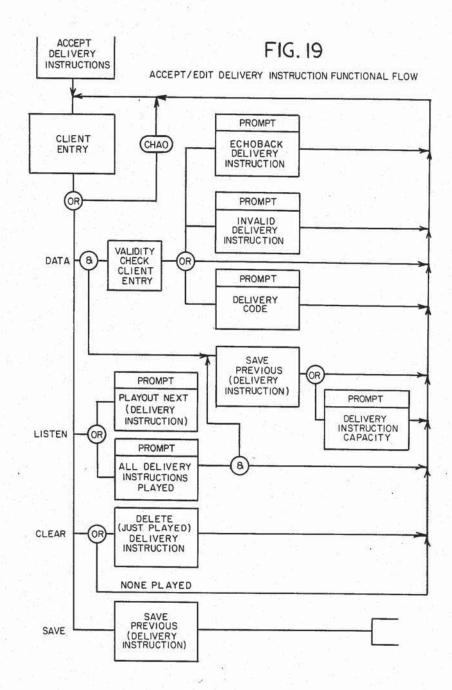

FIG. 19 is an accept/edit delivery instructions functional flow diagram that is useful in understanding the diagram shown in FIG. 18;

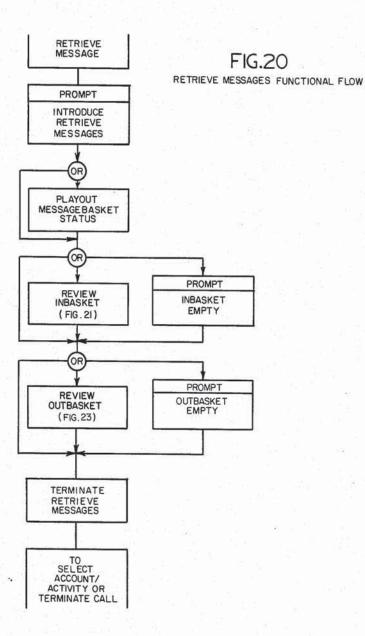

FIG. 20 is a retrieve messages functional flow diagram that is useful in understanding the diagram shown in FIG. 14:

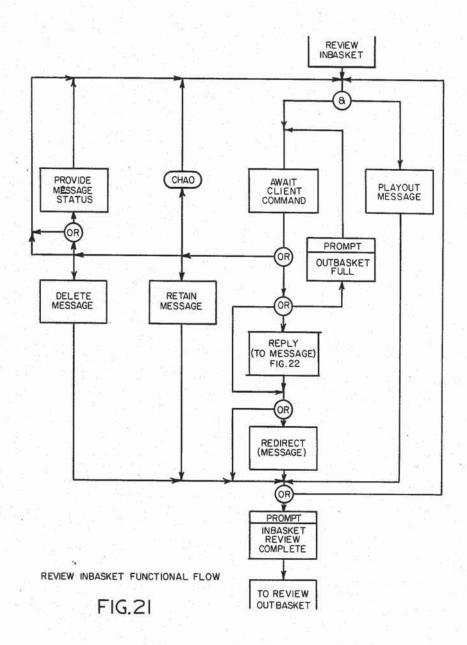

FIG. 21 is a review inbasket functional flow diagram that is useful in understanding the diagram shown in 20 account owner to record a single message in his outbas-FIG. 20:

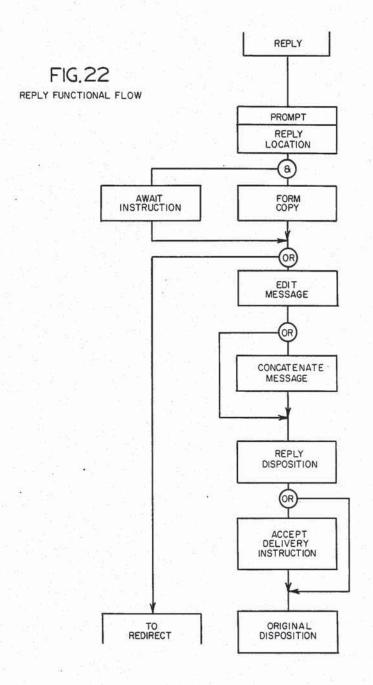

FIG. 22 is a reply functional flow diagram that is useful in understanding the diagram shown in FIG. 21;

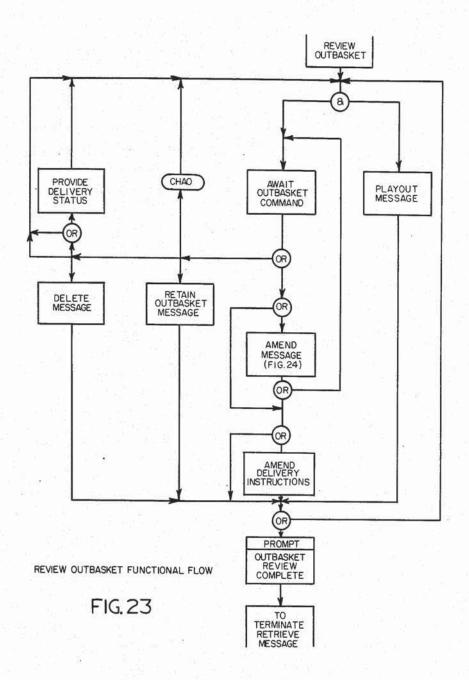

FIG. 23 is a review outbasket functional flow diagram that is useful in understanding the diagram shown 25 in FIG. 20;

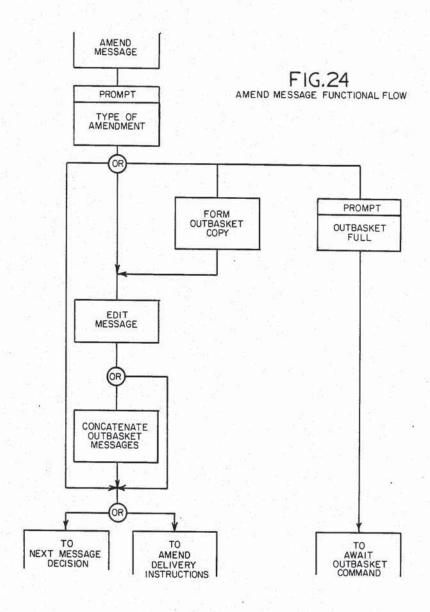

FIG. 24 is an amend message functional flow diagram that is useful in understanding the diagram shown in FIG. 23;

FIG. 25 is an administration functional flow diagram 30 that is useful in understanding the diagram shown in FIG. 14; and

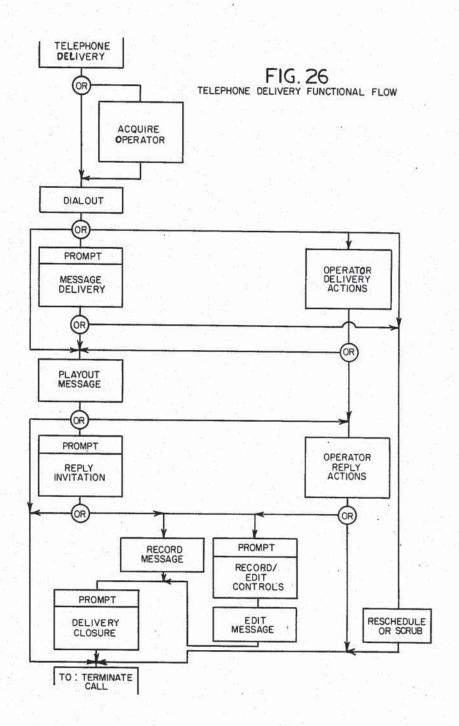

FIG. 26 is a telephone delivery functional flow diagram that is useful in understanding the diagram shown in FIG. 14.

#### DETAILED DESCRIPTION GENERAL BACKGROUND

Referring now to FIG. 1, an automated telephone voice service system 100 according to the invention 40 includes a control system 102 coupling a data store 104 and one or more operator consoles 106 to a standard telephone network 108 which may represent all of the interconnectable telephones throughout the United States and the world. The data store 104 is shown as a 45 single functional block divided into a plurality of addressable units. However, as is conventional the data store 104 may be physically implemented as one or more magnetic or electronic storage devices and may be distributed throughout a data processing system. 50 Data store 104 provides storage for a plurality of addressable message baskets designated message basket 1 through message basket N, a plurality of individually addressable voice message prompts and client greetings,

Each message basket provides storage for a plurality of voice messages and is segregated into an inbasket section and an outbasket section. Each inbasket section stores voice messages and message forwarding notices 60 directed by system users to client owners of the associated message basket. The inbasket of each message basket functions in a manner analogous to a recording mechanism for a telephone answering machine.

The outbasket portion of each message basket re- 65 ceives voice messages generated by the message basket account order for forwarding to selected other message baskets or to telephohe network 108 users at indicated

telephone numbers. The forwarding of a message from an outbasket to an inbasket as represented by arrows 110, 112 is accomplished automatically without human intervention while the forwarding of a message from an outbasket to a telephone network 108 user at a selected telephone number as indicated by arrow 114 may be accomplished either automatically or semiautomatically with operator assistance as required for compliance with the instructions of the client account and applicable state law. For example, in a fully automatic mode, the control system 102 can operate to call the indicated telephone number and upon its being answered, communicate an appropriate recorded voice message prompt, communicate the voice message being sent, and 15 then terminate the call. As an example, the voice message prompt might inform the person answering the telephone at the indicated number that the person is about to receive a prerecorded message from John Doe, the account owner. This mode of operation enables the ket and have the message broadcast to one or thousands of designated recipients without any further effort by the account owner. The account owner, when setting up, or modifying his account, establishes predetermined distribution lists and sets of delivery instructions, each having a different selection code number. The delivery instructions can cover such features as days of the week and time intervals during which delivery may be made, number of retries, and whether the forwarding of the message is to be accomplished automatically or semiautomatically with operator assistance.

In the semiautomatic mode, the control system 102 waits for delivery conditions to be met, and then obtains ownership of an active operator console including a terminal having a keyboard and a video display unit and an operator headset. The control system 102 informs the operator through the console 106 that a semiautomated message forwarding operation is to be undertaken and displays a prompting message for the operator to read. Upon command, the control system 102 generates the Touch Tone signals corresponding to the recipient's telephone number and connects the operator console 106 to the line when it is answered. The operator informs the answering party of the call, asks to talk to a particular person at the called telephone number if appropriate, and secures the permission of the called party to forward the voice message. The operator then commands the control system 102 to communicate the voice message stored in the outbasket to the called telephone line as indicated by arrow 114.

For voice messages forwarded to another inbasket rather than to a telephone number, the voice message is not actually recorded in duplicate in each of the designated inbaskets. Instead, a notification is merely stored and an audit trail for each client accessing the system 55 in the inbasket which indicates that a forwarded message is stored by the system for delivery to the owner of the forwarding message basket. The notification indicates the particular outbasket and the particular message within the outbasket which is being forwarded. This enables the person sending the message to retain ownership of the message in his own outbasket and selectively change or delete the message until it has actually been delivered. Depending upon the delivery instructions of the sender and the preselected instructions of the recipient, a forwarded message might simply wait for delivery until the recipient retrieves the messages stored in his inbasket at some point in time. Alternatively, the recipient might be informed of the

receipt of a message in his inbasket by a paging signal communicated over a paging system (not shown), by the illumination of an indicator light at the recipient's telephone, or by a telephone call to the recipient's telephone number informing the recipient by a prerecorded 5 message that a message has been received in the recipient's inbasket.

The prompts and client greeting section of data store 104 stores a plurality of individually addressable voice message prompts explaining how to operate the voice 10 service system 100 and a client greeting for each inbasket. A voice message prompt is prerecorded for each anticipated state at which a caller might access the voice service system 100. These prompts provide an explanation as to how the user should proceed from the 15 particular point of use and are accessed by the control system 102 and communicated to the user as appropriate. At any point, a knowledgeable user may override the prompt by inserting a command without taking the time to listen to a complete prompt message. The client 20 greetings are provided as an answer mode for message storage accesses to each of the system inbaskets. Each client may record and change his own personal greeting at will. This enables the greeting to include current 25 information such as telephone numbers at which the client can be reached for a given period of time, indications that the client is on vacation for a given period of time, indications as to when the client will return to his recorded a preestablished client greeting, a general system greeting is provided in its place. The system greeting invites the caller to leave a message but does not identify the specific owner of the inbasket which has been accessed by the call.

The audit trail portion of data store 104 stores a record for each caller accessing the system 100 of the command signals which have been given to the system 100 by the caller. This record enables the control system 102 to select particular voice message prompts in 40 Operation then becomes functionally equivalent to the accordance with the current state of the calling line. In addition, in the event that a calling party requests operator assistance, the audit trail record is displayed on the video display unit of a selected operator console 102 so that the operator selected to give assistance can see 45 immediately the state of the calling line, and what attempts have been made by the calling party to control the system 100. This enables the operator to more readily determine what mistakes have been made by the system in the state desired by the calling party.

The major functions which are performed by control system 102 are indicated by a plurality of functional blocks shown within the outline of control system 102. The particular functions executed by control system 55 102 depend upon by which one of the functionally different types of telephone lines the control system 102 is accessed and upon which keyboard commands are entered by a person accessing the voice messaging system

A secretarial line is effectively an extension of a client's normal use telephone line. The client's line may be utilized for receiving and placing telephone calls in a normal manner. The control system 102 responds to an incoming call on a secretarial line by waiting for a pre- 65 determined number of rings which may be preselected by the client in accordance with the day of the week, and time of day, and then answering the telephone.

Upon answering the telephone as indicated by answering function 116 the client greeting is accessed in data store 104 and communicated to the caller. The caller is invited to leave a recorded message which is then recorded and stored in the client's inbasket if a message is generated. Because the caller could quite possibly be a person who is not a client of the voice message service system 100 and is totally unfamiliar with its operation, no prompts are provided to the caller with respect to the editing of any message which is left in the client's inbasket. Such prompts might prove to be bewildering and confusing to any nonclient caller. However, a sophisticated caller who is familiar with the voice service system 100 is free to use normal system editing commands which enable the caller to edit the voice message. Upon completion of the message or upon the occurrence of a client selected timeout duration, the call is terminated and the message remains in the client's inbasket until retrieved by the client.

Another type of line upon which a call might come into the voice answering system 100 is a direct incall line. A direct incall line is responded to by control system 102 with answering function 116 in a manner similar to a response to a call on a secretarial line. The principal difference between the secretarial line and direct incall line is that a direct incall line is dedicated to the particular inbasket of the client and is not available for general use by the client. Typically there is no reason for waiting for a specified number of rings before office and so forth. In the event that a client fails to have answering a direct incall line and such a line is answered as soon as it becomes active.

A general incall line is similar in nature to a direct incall line except that the general incall line is not associated with any particular message basket or inbasket 35 thereof. Upon accessing the system 100 through a general incall line, a caller is prompted to enter a message basket number which number associates the incall line with a particular inbasket and causes control system 102 to transfer control of the call to answering function 116. secretarial line and direct incall line except that at any time the caller may command a change function 118 which enables the caller to enter a new message basket number code and thereby associate the general incall line with a different message basket and enable the caller to leave a message with the newly selected inbasket in accordance with answering function 116.

A general access line is intended primarily for clients of the voice service system 100 and affords the broadest calling party and what needs to be done to place the 50 range of system functions. Upon calling in on a general access line, a caller is prompted to either enter a message basket number if he desires to leave a message in another's inbasket or to enter his own personal ID number if he desires to have access to the ownership privileges of his own account as indicated by own account function 120. If the caller elects the enter message basket number code function 120, operation of the system is functionally equivalent to the response to a general incall line. Execution of a change function 124 enables the caller to select a new system inbasket in a manner functionally equivalent to change function 118.

If the caller on a general access line selects the enter personal ID number code function 126 instead of the message basket number code function number 120, the caller is granted immediate access to a message retrieval function 128 for the inbasket portion of his own message basket. The message retrieval function 128 informs the caller whether or not there are any messages within his

inbasket and, if there are, begins communicating the voice messages over the connected telephone line on a last in first out basis. Before each message is retrieved, the caller is informed of the age of the message on a lapsed time basis. For example, the system might inform 5 the caller that the message was recorded fifteen minutes ago and then begin relaying the message. This lapsed time indication avoids any uncertainties which might arise from different time zones and the caller may obtain the exact time for receipt of a message with operator 10 assistance. As a caller retrieves his messages, he may utilize the editing commands to rapidly scan through the messages before listening to the messages more carefully a second time or may on an individual basis command that each message be saved or cleared. After 15 each message is relayed the caller may also direct, at the caller's option, a reply to the sender, a forwarding of the message to one or more other parties. The caller may also simply go on to the next message, with the present message being saved or cleared at the option of the 20 caller. After reviewing the incoming messages, the caller is informed of the status of any outgoing messages in the caller's outbasket which are awaiting delivery. At any time during this process the caller may execute a change function 124 to leave a message at another's 25 inbasket or an account activity change function 130 which enables the caller to select one of the ownership functions. The control system 102 retains the originally entered personal ID number code and does not require reentry of this code. Upon executing an account activ- 30 ity change function 130 the client may selectively return to the retrieval function 128 or may command a sending function 132. In response to selection of the sending function 132 the control system 102 prompts the caller to record a voice message in the caller's outbasket by 35 initiating a talk command. During the recording of such a message all of the edit functions are available to the caller. Upon completion of the message the caller enters a save command and is then prompted to enter an address code. The address code is a two digit code which 40 identifies a preestablished list of up to 99 addressees for the voice message. Each of the 99 entries on the address list or distribution list may in turn be another list of up to 99 addresses, thus permitting a distribution list of almost 10,000 addresses in total. Upon selection of a 45 distribution list, the caller is prompted to enter a one digit code selecting a preestablished set of delivery instructions for the message. For example, the instructions may specify that delivery be made only during certain designated days or times such as normal business 50 hours in the calling party's time zone or a different time zone. Upon completion of the sending function the calling party may again execute a change command 124 or 130 to execute other voice messaging functions. For example, the caller may wish to access one or more of 55 the administration functions which are available to an account owner. These functions include changing the greeting for the inbasket message, changing the conditions under which a secretarial line is answered and so forth.

The control system 102 also provides connection to a direct recall line which is the counterpart of a direct incall line in that it is associated with a particular message basket but enables the account ownership function instead of the answering functions. Upon answering a 65 direct recall line, control system 102 executes the enter personal ID number code function 126 and functional execution, then proceeds in the same manner as if a

caller on a general access line had elected the enter personal ID code function 126. A general recall line is the counterpart to the general incall line and requires execution of an enter message basket code function 136 before advancing system control to the enter personal ID number code function 126 as with a direct recall line.

The direct recall line is of advantage in that it provides a higher security for access to the system because the caller must know both the telephone number of the direct recall line and the personal ID number code associated therewith. Each personal ID number code must be preceded by an asterisk symbol to identify it as such. Even further security may be provided by requiring a two field personal ID number code with the two fields being separated by a number sign (enter) key. The second field, if elected, may be changed at will by the client owner as one of the administration functions 134.

The system architecture of the telephone voice service system 100 is shown in block diagram form in FIG. 2 to which reference is now made. The telephone network 108 provides a number of physically different types of telephone lines to which connections must be made by the service system 100. By way of example, these different types are shown as including secretarial lines, direct inward dial lines, DX tie lines, and 2-wire lines. Connections are also provided for six wire operator stations. In the present example the different lines are shown to be connected rather arbitrarily to illustrate the maximum size of the system.

Up to 640 secretarial lines are connected to a concentrator 202 which selectively connects the voice information carried by these 640 secretary lines through 20 trunk lines 204 to a telephone room subsystem line group 1 processing circuit 206. Only analog voice information is carried by the trunk lines 204. Control commands and data such as trunk and line identification information, ringing signal indications, connection commands, and execution confirmation signals are communicated through a data set 208 within concentrator 202 over a serial data line 210 extending between data set 208 and a data set 212.

A telephone room subsystem A, line group 2 processing circuit 214 is illustrated as connecting to a direct inward dial line while a telephone room subsystem D, line group 168 processing circuit 216 is shown as being coupled to one direct inward dial line, two DX tie lines, and two 2-wire lines. Each represented telephone line is assumed to be a bidirectional full duplex line.

The concentrator 202 and each of the telephone room subsystem line groups 206, 214, 216 are physically located at one or more telephone company central offices or client PABX centers. The system can accommodate up to four telephone room subsystems with up to 42 line groups being associated with each telephone room subsystem. Each line group can in turn accommodate up to 8 operator telephone lines and up to 22 telephone trunks or lines of another type. It is thus possible for each 60 telephone room subsystem to connect to up to 1260 voice grade circuit terminations with the maximum of 4 telephone room subsystems providing in total connection to 5040 voice grade circuit terminations. Multiple lines may be assigned to a given data source to provide a capability of higher bandwidth than the single voice grade line. In the present example, the telephone room subsystem A line group 1 206 is coupled through the 20 trunks 204 to concentrator 202 and also through a maxi-

mum of 8 operator lines 220, 222 to operator headsets 224, 226 at a plurality of operator consoles 106.

The telephone room subsystems operate as interfaces between the digital portion of the telephone voice service system 100 and the analog telephone lines and 5 trunks. They provide analog-to-digital conversion of the voice signals, detect and generate DTMF data and command signals, detect and generate dial pulses, and communicate the telephone line information to an associated real time subsystem over one of two redundant 10 2.048 megabit per second time division multiplex serial data channels. The 30 lines to which a line group processing circuit may connect are each assigned to a different voice channel while the control information for all of the lines as well as the line group is carried by a single channel. A 32nd channel is utilized to synchronize the serial data links.

In the present example telephone room subsystem 206 is coupled to real time system 1 230 by a pair of redundant serial data links 232, 233. Similarly, line group 2 214 is coupled to real time subsystem 1 230 by a pair of redundant serial data links 234, 235 and line group 168 216 is coupled to real time subsystem 4 238 by a pair of redundant serial data links 239, 240.

Up to 4 real time subsystems receive the voice and control data from the 4 telephone room subsystems, provide selected switching connections between channels, and communicate with an information processing system 250 for storage and retrieval of voice messages and system control. The real time subsystems also perform any signal processing such as silence compression upon the voice signals.

An interactive service subsystem 252 provides a communication connection between the information processing system 215 and input/output devices for the voice service system 100. Interactive service subsystem 252 is illustrated as being coupled through two serial channel controllers 254, 255 and two sets of 16 serial data channels each 256, 257 to an RS 232 serial distribution panel 260. Distribution panel 260 provides serial data connection to up to 32 different devices. It is representatively shown as connecting to a line printer 262, a card reader 264, to the keyboard display terminals 266, 268 and 270 within operator consoles 106 and to the 45 data set 212. It will be recalled that the data set 212 carries the control and data information between concentrator 202 and the information processing system

As shown in FIG. 3, the telephone room subsystem A 50 line group 1 206 includes a line group controller 302 connected between the 2.048 MBPS 30 channel synchronous data link 232 and an 8 bit parallel poled bus 304 and a second line group controller 306 connected between the 2.048 MBPS 30 channel synchronous data 55 link 233 and an 8 bit parallel poled bus 308. Only one of the line group controllers 302, 306 provides active communication with the real time subsystem 1 230 at any one time. In the event that the active line group controller fails, the other immediately assumes the duties 60 thereof to continue uninterrupted communication between the connected telephone lines and the information processing system 250. The active line group controller poles the line interface boards connected to the associated bus for voice channel data and upon receiv- 65 ing data, inserts the data into a preassigned one of the 30 time division multiplex voice channel data slots on the synchronous data link 232 or 233.

12

Each line group provides bus 304, 308 connection to up to 15 line interface boards, each of which may couple to two different analog telephone lines. Each of the line interface boards is generally similar in construction except that certain variations are required in order to which a line interface board may connect. A variety of different line interface board types have been illustrated in FIG. 3 to demonstrate the different types of boards which might be included in a voice for service system. For example, line interface board 1 310 is an operator type of line interface board and is somewhat simpler than other types of boards in that it need carry no signaling functions since these are accommodated through the keyboard display terminals such as terminal 266.

The line interface board 310 interfaces two separate operator positions to the real time subsystem 230. Line interface board 310 provides battery feed circuits for powering two operator headset microphones at each position and amplifier circuitry for driving two sets of headset earpieces at each position. Functional circuits located on line interface board 310 include redundant power supply inputs, two separate current limited -48 volt battery feeds per circuit, a circuit providing a side tone fixed at -26 db for each headset circuit, a circuit providing audio mixing of headset microphone inputs, a circuit providing 4-wire operation separate receive and transmit voice paths, and an onboard MU-LAW codec. The MU-LAW codec provides conversion between the 13 bit digital sample of an analog voice signal and an 8 bit byte representation thereof to enable a single byte of sampled data to have a greater effective range and resolution than would be possible with 255 equal magnitude increments. MU-LAW codecs are well known to those skilled in the art and are not further described herein. Each of the 6-wire interface connections of the line interface board 310 provides headset A transmit tip, headset A transmit ring, headset B transmit tip, headset B transmit ring, headset A and B receive tip and headset A and B receive ring. Two low impedance microphone inputs per circuit (600 ohms or less) will drive two 300 ohm low impedance headsets per circuit.

A concentrator line interface board 2 312 provides connection to two concentrator trunk circuits 204. Concentrator line interface board 312 terminates to "dry' (no line voltage) 2-wire links from concentrator 202. Because system control signals are communicated through the serial data link 210, the line interface board 312 carries no supervisory or control signals except DTMF signals which are communicated through the telephone line. Line interface board 312 includes DTMF signal generating and detecting circuits which respond to or generate the required DTMF signals. These signals are separated from the voice channel information and are communicated to the appropriate line controller during a separate control time slot on the buses 304, 308 and are communicated by the active line group controller to the associated real time system during a separate control information time slot which occupies a 31st channel position on the synchronous data links. The line interface board 312 includes the redundant power supplies and MU-LAW codecs which are found on the operator line interface board 310.

A direct inward dial line interface board 3 314 terminates two 2-wire DII trunks, handles all DTMF signals associated therewith, detects supervisory and control signals and incoming dialed digits. The two incoming lines may be either CO WINK-START or immediate

14

start lines. The direct inward dial line interface board 314 hosts DTMF detection and generation, dial pulse detection, tone and voice envelope detection, and audio switches for call progress tone insertion. Line interface board 314 further includes 48 volt battery feed circuits, redundant power supply input, secondary voltage hazard protection, MU-LAW codecs, 2-wire to 4-wire conversion, and 600 ohm or 900 ohm line impedance selected by a strapping option. Also included on each DID line interface board 314 is a fixed compromise 10 network, a loop current indicator light emitting diode, a wink and immediate start strap option, a reverse battery indicator light emitting diode, a reverse battery front panel switch and test jacks for 2-wire testing. CO tip and CO ring wires are interfaced for 2-wire circuits. A 15 loop start/ground start line interface board 316 terminates two pay station telephone number conventional lines. It can accept incoming calls as well as seize a line to dial outgoing calls and handle all DTMF, supervisory and control signals. A 2-wire line interface board 20 318 interfaces two CO loop-start or ground-start trunk lines. The 2-wire interfaces provide CO tip and CO ring. The onboard functions include DTMF detection, tone and voice envelope detection, 2-wire to 4-wire conversion, loop disconnect dialer, a loop-start or 25 is to be dedicated. ground-start operation which is DIPSWITCH SE-LECTABLE, a 600 ohm or 900 ohm strap selectable line interface, a fixed compromise network, a loop current indicator light emitting diode, test jacks for 2-wire testing, redundant power supply inputs, secondary volt- 30 age hazard protection, and onboard MU-LAW codecs.

The real time subsystem 230 is representative of each of the real time subsystems and is shown in FIG. 4 as including a minimum of two and a maximum of 46 external transfer switches 402, 404. Each of the external 35 transfer switches is coupled to both an S bus which is controlled by a real time executive S 406 and a T bus which is controlled by a real time executive T 408. At least two and not more than 22 real time processors 410, 412 are also coupled to the S and T buses. The real time 40 processors 410, 412 are identical to the real time executives 406, 408 except that the bus control functions are not implemented on the real time processors 410, 412. The S and T buses are each time division multiplex real time buses which are 16 data bits wide and operate in 45 repetitive frames with 512 slots per frame. Only one of the buses is operative at any given time with the other being available as a hot standby in the event of a failure on the first bus.

The external transfer switches 402, 404 provide an 50 interface between the 2.048 MBPS serial data links and the S and T buses 414, 416. Each external transfer switch 402, 404 may connect to two high speed data links, each of which carries 30 bidirectional voice channels and one bidirectional control data channel on a 55 time division multiplex basis. In response to system commands the external transfer switches can connect any incoming or outgoing voice channel to any one or more time slots on the S bus 414 or T bus 416.

An any channel to any channel connection scheme 60 thus becomes possible. For example, certain incoming voice channels can be connected to a bus time slot allocated for voice message recording or selected outgoing channels can be connected to a bus time slot allocated to voice message retrieval. An operator line simply appears as one of the voice channels so that an operator can be selectively included in a set of voice connections. A multiparty conference call can be established by sim-

ply creating a bus channel for each incoming line and then connecting each outgoing line to all of the corresponding bus time slots for the incoming lines of the other parties. It will be appreciated that a "connection" does not imply a continuous physical connection but only the transfer of voice sample data bytes between select serial data link time slots and select S or T bus time slots.

The real time processors 410, 412 are each comprised of a standard processor module with a real time extension board connected thereto to provide additional processing and data storage capacity. In the voice messaging environment the real time processors provide data compaction by converting PCM encoded bytes of data to run length in coding format and by detecting periods of silence and encoding such periods in a run length encoding format. Data corresponding to periods of silence in excess of one second may be discarded if desired.

As with the real time processors 410, 412, each processor connected to the X and Y executive buses is comprised of a standard processor module and an extension module which extends the processor module and adapts it to a particular function to which the processor is to be dedicated.

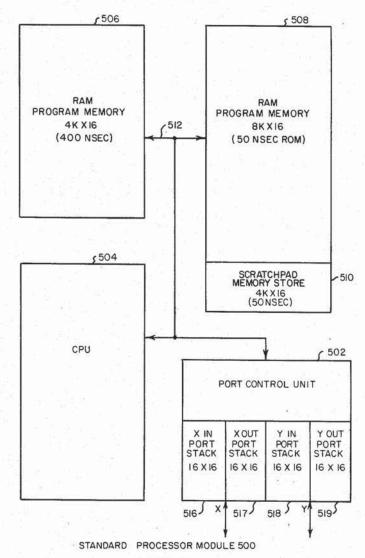

A standard processor module 500 is illustrated in FIG. 5, by way of example as including a port control unit 502, a CPU 504, a 4k×16 RAM program memory 506, an 8K×16 resident executive ROM program memory 508, and a 4K×16 scratch pad memory store 510 all interconnected by a 16 bit internal data bus 512. The port control unit 502 provides connection to the X bus through a 16 word X inport stack 516 and an X outport stack 517. Connection to the Y bus is through a 16 word Y inport stack 518 and a 16 word Y outport stack 519. The inport stacks 516, 518 each buffer a 16 word data packet as a packet is transferred from the bus to the port control unit while the two outport stacks 517, 519 buffer a 16 word data packet as the packet is being transferred from the port control unit to one of the executive buses.

The CPU 504 provides a basic data processing capability and may have its instruction set extended for special data processing functions by an extension module which connects to the standard processor module 500 and dedicates the standard processor module 500 to a particular processor type.

The 4K scratch pad memory store 510 provides storage for a large number of system variables and permits different sections or pages thereof to be dedicated to particular processes or programs. This eliminates the need for much of the time consuming process of storing process variables for one process or program whenever it is interrupted by another process or program. A basic REX program memory 508 is implemented in ROM to provide on the standard processor module 500 basic executive service functions such as a bootstrap startup program functions, diagnostic analysis, and communication over the executive buses. The 4K×16 RAM program memory 506 permits the standard processor module 500 to receive and store additional program data from other sources such as disk files on an overlay basis.

The standard processor module 500 is a complete computer constructed on a single board. When augmented by one of the several extension unit types, it operates as a processor on the X and Y executive buses. The standard processor module 500 serves as a self-contained functional node in an array of such units inter-

16

linked via the two independent, very high speed bidirectional X and Y data buses. The X and Y buffered data ports operate asynchronously relative to the standard processor module 500 itself. With some exceptions, a full instruction cycle of CPU 504 is 133 nanoseconds, 5 including all accesses to program memory, working registers, port input/output buffers stacks and scratch pad memory.

All standard processor modules connected to the main X and Y buses are logically isolated therefrom by 10 the logic of the port control unit 502. Interprocessor transfers are effected in packets of 16 16-bit words, moved between respective output and input stacks at the instantaneous rate of one word per instruction cycle. Including all overhead, each X or Y main bus in the 15 standard processor module array can maintain an average data rate of about 40 million bits per second. The physical identity of a standard processor module is determined by a 7-bit code permanently wired into each connector (permitting a maximum of 128 boards of all 20 types on the main bus). For communications between processors, a logical bus identification (BID) is used within packets and subsequently translated to the ap-

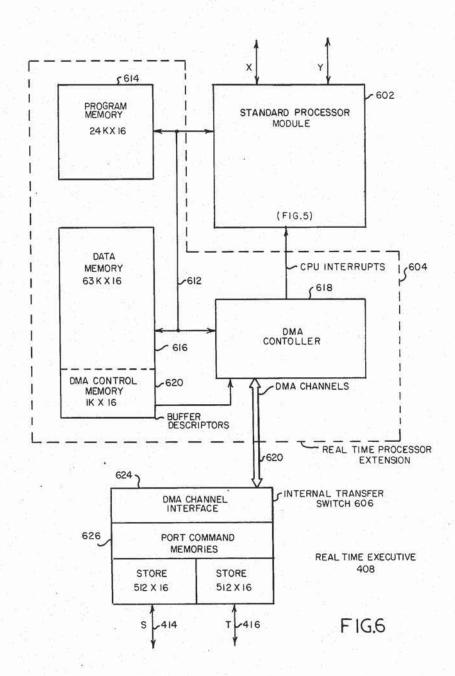

The real time executive 408 for the T bus 416 shown in FIG. 4 is illustrated in greater detail in FIG. 6. The real time executives 408 and 406 are essentially the same except that by a strap selection option one is designated 30 to control the T bus 416 and the other the S bus 414. Furthermore, except for the addition of a small amount of bus control circuitry such as synchronizing crystal clock signal generators, the real time executives 406, 408 are the same as the real time processors 410, 412.

Referring now to FIG. 6, the real time executive 408 includes a standard processor module 602, a real time processor extension unit 604, and an internal transfer switch 606. The real time processor extension 604 connects to the standard processor module 602 by the 16-bit 40 internal data bus 612 of standard processor module 602 and includes 24K words of additional program memory 614, 64K words of additional data memory 616, and a direct memory access (DMA) controller 618. The data memory 616 includes a 1K word section 620 which is 45 dedicated as a DMA control memory for the DMA controller 618. This section 620 stores buffer descriptors for use of DMA controller 618 in executing data trans-

The DMA controller 618 operates on a stand-alone 50 basis to transfer data between selected channels of the S and T buses and selected system storage locations such as records within magnetic disk files. The DMA controller 618 is coupled to the internal data bus 612 and by DMA channels 620 to the internal transfer switch 606. 55 DMA controller 618 is also coupled to communicate CPU interrupts to the standard processor module 602 in order to selectively interrupt the CPU of the standard processor module 602 as necessary to obtain communication over the X and Y executive buses.

The internal transfer switch 606 includes a DMA channel interface 624, port command memories 626 and 512 word×16 bit S and T bus buffer stores 628, 630. The internal transfer switch 606 is similar to the external transfer switches 402, 404 (FIG. 4) and operates to 65 transfer data between selected frame slots on the X time division multiplexed S and T buses 414, 416 and selected DMA channels 620.

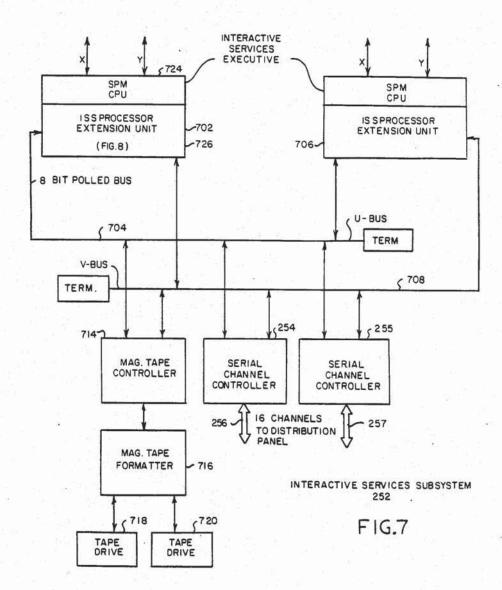

Referring now to FIG. 7, the interactive services subsystem 252 includes an interactive services executive 702 coupled to control an 8 bit parallel poled bus designated U bus 704 and an interactive services executive 706 coupled to control an 8 bit parallel poled bus designated V bus 708. The two interactive services executives 702, 706 and their respective buses 704, 708 provide redundant coupling of data information between the X and Y executive buses and the various input/output devices of the interactive services subsystem 252. By way of example, these devices are shown to include the serial channel controllers 254, 255 which interface the U and V buses to the 16 channels 256 and the 16 channels 257 respectively. As shown in FIG. 2, these channels connect in turn to the RS 232 distribution channel 260.

The U and V buses are also shown as providing a redundant coupling to a magnetic tape controller 714 which in turn couples through a magnetic tape formatter 716 to two magnetic tape drives 718, 720. The I/O devices connected to the interactive services subsystem 252 have been illustrated by way of example and particular I/O devices can be added to the subsystem or depropriate physical BID immediately prior to packet 25 ments of a particular configuration of a telephone voice service system 100 in accordance with the invention.

The interactive services executive 702 includes a standard processor module 724 and an interactive services subsystem bus extension unit 726.

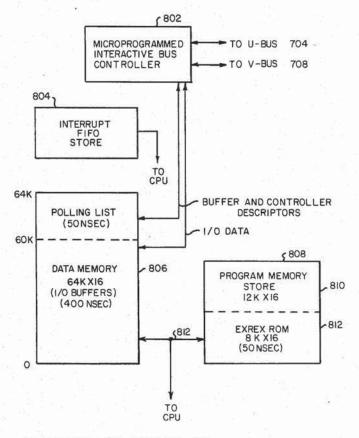

Referring now to FIG. 8, the interactive services subsystem processor extension unit 726 includes a microprogrammed interactive bus controller 802 which couples to the U bus 704 and V bus 708 and is selectively operable to control the U bus 704. The interactive bus controller 802 couples to an interrupt FIFO store 804 which in turn couples interrupt requests to the CPU of standard processor module 724 to control the transfer of data between a 64K×16 data memory 806 and the executive X, Y buses. The data memory 806 is partitioned to include a 4K poling list which is coupled for communication of buffer and controller descriptors with the interactive bus controller 802 and a 60K data memory section which is coupled for communication of I/O data with the interactive bus controller 802. Data memory 806 is further coupled along wth a 20K×16 program memory 808 to the internal data bus 812 of the standard processor module 724 to which the extension unit 726 connects. The program memory 808 includes a 12K×16 program memory store 810 composed of random access memory for receiving overlay programs and an 8K×16 extended resident executive ROM 812 storing process programs which are specifically related to the interactive services subsystem.

Referring now to FIG. 9, the information processing system 250 includes in addition to the interactive services subsystem 252, the real time subsystems 1-4 902. an executive services subsystem 904, an information processing subsystem 906, and a file services subsystem 908. The executive services subsystem 904 includes the two 16-bit parallel executive services main X and Y buses 912, 914 respectively, an executive services processor 916 coupled to control communications over the X bus 912 and an executive services processor 918 coupled to control communication over the Y bus 914. The executive services processor 916, which is substantially identical to processor 918 except for connection to control X bus 912 instead of Y bus 914, includes a standard processor module 920 and a bus controller extension 922. The dual X and Y bus arrangement provides redundancy in the event of a failure associated with one

programs, the SYSDISK programs, the system file maintenance programs. Any unused RAM program memory is available for general purpose programs that can run in any delta processor with sufficient program

of the two buses 912, 914. However, the two buses are operated independently of each other and carry separate, not redundant data. However, in the event of a 5 failure of one of the buses 912, 914, the other connects to all of the subsystems of the information processing system 250 and can carry the data associated therewith.

The executive services subsystem 904 manages the interprocessor communications and that part of the 10 system software that is responsible for systemwide re-

source and activity management.

Referring now to FIG. 10, the bus controller extension 922 includes a W port 1002 which connects to the particular X or Y bus which is being controlled. W port 15 1002 is controlled by a microprogrammed packet switcher 1004 which poles the data output ports connected to the controlled executive bus and upon finding a port with a 16-bit packet stored therein awaiting delivery, receives the logical address stored in the first 7 bits 20 thereof and uses the logical address to access a 4K×12 control memory 1006 which stores a table converting the logical address to a physical address corresponding thereo. The microprogram packet switcher 1004 then tests the indicated physical address input port for avail- 25 ability to receive the packet of data. If available, the packet is transferred. If not available, the packet to be transferred is queued in a queue of processors attempting to transmit to the busy recipient. If the processor will not accept any packets, the job services and man- 30 agement program (JSAM) determines whether a failure has occurred and if so invalidates the symbolic and logical identities of the processors stored in control memory 1006. This has the effect of logically removing that processor from the system.

The bus controller extension 922 also extends the storage capacity of the executive services processor 916 by the addition of a 16K×16 program memory 1008 and a 16K×16 data memory 1010. A 16 bit internal data bus 1012 interconnects the components of the bus controller extension 922 and to each other and with the

standard processor module 920.

Referring now to FIG. 9, the file services subsystem 908 provides the primary high capacity permanent storage media in the form of one or more disk drives 930, 45 932. The file services subsystem 902 includes at least two disk data processors 934, 936 which interface the disk drives 930, 932 to the X and Y executive buses 912, 914. The disk data processors 934, 936 receive data access requests for transfers of data over the executive 50 buses and satisfy those requests by transfers of data packets between the disk drives 930, 932 and requesting processes over the executive service buses 912, 914. Each of the disk data processors 934, 936 includes a standard processor module 938 and a disk controller 55 extension unit 940.

Although not separately shown, the disk controller extension unit 940 provides a 4K×16 PROM for program memory for physical initialization of the disk data processor 934, wakeup processing, and the disk controller microprogram. An additional 12K×16 words of RAM program memory are made available to augment the RAM program memory on the standard processor module 938. The RAM program memory of the disk data processor 934 is used for transient programs (infrequently used disk logical I/O routines), file management programs, and special purpose disk data processing programs such as the message basket maintenance

memory, scratch pad, and data memory resources. The disk controller extension unit 940 further includes 64K×16 words of data memory, all of which is acceptable by programs executing in the disk data processor 934. The disk controller extension unit 940 and the data memory therein provides a direct memory access DMA interface for the disk drive control logic. The disk data processor 934 provides standard data memory management routines and deals with blocks of data memories of up to 4K words in length. Disk data blocks longer than 4K words are supported by the datachaining features of the DMA interface and of the REX I/O service routines of the disk data processor 934. A buffer controlled block within the data memory lists the areas allocated to buffer the disk data blocks. Disk data buffers are maintained as a transparent "cache" memory for the data accessible on the disk drives attached to the disk data processor 934. Disk data process buffer management routines return unused buffer space to the data memory master only when the data in the buffer is no longer valid or when available data memory is not sufficient for current demand. Unused buffers are main-

tained in a queue, the first entry of which is the least

recently used buffer for cache management purposes. A physical record is a minimum unit of data accessed by the disk data processor 936. A physical record contains either two or three fields for identification and information storage, namely a count field, a key field (optional), and a data field. A gap between fields allows the disk data processor 934 to operate on the key or data fields after verifying the identity of the physical record. The data available for processing by the disk data processor 934 programs other than the disk controller microprogram is called a block, and is contained either in the data field alone or in the combined key and data fields. A block may be in one physical record or may be written across track boundaries in two or more physical records. A third unit of data is the logical record, which may be either part or all of a block or may be a series of blocks chained together by pointers. Programs outside the disk data processor 934 can act as only logical records, but all such accesses are translated into references to blocks within a specified area of the recording medium. On any initialized storage medium, the label record contains access information for a pack directory. The contents of the pack directory are records that describe the unused area of the pack (available tracks) and the separately allocated areas, which are referred to as data sets. The record in the pack directory that describes a data set is called the "data set label". It defines the characteristics of the data set and gives the location of two separate areas. The main area is the data area and contains the data blocks. An optional control area contains access and resource information that is automatically maintained by the disk data processor 934 programs and is only indirectly available during logical process of the data set. Each area is described in terms of the physical and logical organization of information in it and its location on the storage medium. Locations are defined in terms of extents, each of which is a continuous set of tracks. Access requests are always by block or track number relative to the start of the data set. Disk data processor programs translate the relative requests to the proper track and the proper extent.

4,023,081

The information processing system 906 includes at least two general purpose processors 942, 944 which provide a general multiprocessor data processing capability. For example, system accounting and administrative processing tasks would be assigned to the general 5 purpose processors 942, 944. The general purpose processor 942 is exemplary of these processors and includes a standard processor module 946 with a general purpose extension 948 coupled thereto. The general purpose processors 942, 944 provide program and data memory 10 for executing system utilities that may be executed in any processor with sufficient memory resources. In addition, each general purpose processor defines one or two virtual machine types for execution of high level source language programs under a virtual machine in- 15 terpreter (VMI). A kernel of standard processor module programs supplements the virtual machine interpreter to provide proper interfaces between the virtual machines and the actual information processing system 250

19

The general purpose extension unit 948 provides 20 additional program memory and a standard as well as an extended data memory interface. The general purpose extension unit 948 executes the standard data memory access instructions for the first 64K words of attached data memory. Data memory access registers and error 25 detection and correction logic are provided as for other extension boards. Data memory itself is on separate data memory extension units 950. Access to the whole of the attached data memory is provided by extended data memory extension instructions. These allow 22 bit word 30 addressing via the standard processor module address registers. The general purpose pocessor 942 provides standard data memory resource management routines for the first 64K words and special routines for the rest of the data memory. Each general purpose processor 35 may include up to 8 megabytes of data memory.

### SYSTEM ARCHITECTURE

A. System Summary

The system 100 is a general purpose, multi-media 40 computer system that uses fail-safe architecture to provide very high levels of availability and uninterrupted processing. Continuous operation for extended periods is assured, with no down time normally required for failures, maintenance or system modifications. The sys- 45 tem 100 is a tightly-coupled, distributed network of multiple high speed processors, interconnected by a high speed packet switching network, and a fully distributed fault tolerant operating system that together provide a flexible processing system. The system 100 50 can be used in environments which mix real-time, computational communications, interactive and transaction processing with large numbers of peripheral devices and storage units. The system 100 provides for a flexible growth path which is independent of the initial system 55 configuration.

B. System Architecture

A Delta system consists of five functionally unique subsystems; executive services, information processing, file services, interactive services and real-time. Each 60 subsystem contains at least two identical processors, with the capability to expand individual subsystems as required up to a maximum of 32 processors per system 100. This unique architecture provides maximum flexibility in supporting multiple concurrent applications.

There are three different perspectives in viewing the architecture of the Delta System. The physical system has a hierarchical structure composed of subsystems,

plus their devices, each incorporating specialized processors, functional characteristics and organizations. The functional organization includes a hierarchical network of system processes that provide an openended environment for large numbers of concurrent and simultaneous application processes.

20

The user system designer's structure provides a network consisting of a multi-processor host system that executes the machine code of the hardware processors and a number of idealized virtual machines that execute a higher level source-language oriented instruction set.

The following sections describe these aspects of the system.

C. The Physical System

The system 100 consists of from eight to 32 processors, together with a range of controllers, peripherals and storage modules. Each processor is a fully independent, high-speed 16-bit machine having a non-microcoded architecture and high-speed program memory. A maximum of 7.5 million instructions per second can be executed with an instruction cycle time of 133 nanoseconds. The instruction set contains over 340 instructions.

Each of the five subsystems within the system 100 consists of customized processors suited especially for the functions of that subsystem. Each processor type consists of a common processor to which are added the following extensions: extra memory, microprocessor based device controllers, interfaces to other system bus structures, and extensions to the basic processor architecture. Although the type of processors varies by function, basic elements of the architecture are common to all processors.

The management services needed to run a processor are common to all processors and are hard-wired into the processor. Each processor also has a firmware-resident executive system (REX) which organizes and manages the resources of the processor on behalf of both the system and the active processes within the system. The resident executive provides a wide range of functions ranging from wake-up diagnostics, interrupt handling, timer management, to input/output services. In addition, each processor type has a customized extension to the executive, which manages the individual nature of the various processor types.

To be able to communicate with other processors in the system 100, each processor has a pair of input/output ports that interface it to the packet-switched main interprocessor bus structure. Both buses 912, 914 of the pair are active, providing dynamic load sharing, thereby increasing system 100 utilization and throughput. Each provides a peak transfer rate of 120 Mbps and a sustainable rate of 40 Mbps.

To eliminate contention problems that can exist in multiprocessor systems based on global memory resources, each processor contains its own memory. Processors within the Information Processing Subsystem 906 can have from 500K-Bytes up to 8 M-Bytes of memory. All other processors may contain 500K-Bytes of memory. Independent processor upgrades can take place unrestricted by arbitrary system considerations. The total amount of memory available in a Delta System can be extremely large.

A similar philosophy exists within the processor architecture. Rather than have a small set of machine registers shared between the various activities and events contending for the use of the processor, with wasteful saving and restoring operations between every change, each processor is provided with over 4000

scratchpad registers to be allocated among multiple resident tasks.

Each of the five subsystems has sufficient resources to ensure survival of any single-point failure within itself, as well as many multiple-point failures. The system 100 as a whole is able to survive such occurrences.