# 22.2.4.1.2 Loopback

The PHY shall be placed in a loopback mode of operation when bit 0.14 is set to a logic one. When bit 0.14 is set, the PHY receive circuitry shall be isolated from the network medium, and the assertion of TX\_EN at the MII shall not result in the transmission of data on the network medium. When bit 0.14 is set, the PHY shall accept data from the MII transmit data path and return it to the MII receive data path in response to the assertion of TX\_EN. When bit 0.14 is set, the delay from the assertion of TX\_EN to the assertion of RX\_DV shall be less than 512 BT. When bit 0.14 is set, the COL signal shall remain de-asserted at all times, unless bit 0.7 is set, in which case the COL signal shall behave as described in 22.2.4.1.9. Clearing bit 0.14 to zero allows normal operation.

The default value of bit 0.14 is zero.

NOTE—The signal path through the PHY that is exercised in the loopback mode of operation is implementation specific, but it is recommended that the signal path encompass as much of the PHY circuitry as is practical. The intention of providing this loopback mode of operation is to permit a diagnostic or self-test function to perform the transmission and reception of a PDU, thus testing the transmit and receive data paths. Other loopback signal paths through a PHY may be enabled via the extended register set, in an implementation-specific fashion.

# 22.2.4.1.3 Speed selection

Link speed can be selected via either the Auto-Negotiation process, or manual speed selection. Manual speed selection is allowed when Auto-Negotiation is disabled by clearing bit 0.12 to zero. When Auto-Negotiation is disabled, setting bit 0.13 to a logic one configures the PHY for 100 Mb/s operation, and clearing bit 0.13 to a logic zero configures the PHY for 10 Mb/s operation. When Auto-Negotiation is enabled, bit 0.13 can be read or written, but the state of bit 0.13 has no effect on the link configuration, and it is not necessary for bit 0.13 to reflect the operating speed of the link when it is read. If a PHY reports via bits 1.15:11 that it is able to operate at only one speed, the value of bit 0.13 shall correspond to the speed at which the PHY can operate, and any attempt to change the setting of the bit shall be ignored.

The default value of bit 0.13 is one, unless the PHY reports via bits 1.15:11 that it is able to operate only at 10 Mb/s, in which case the default value of bit 0.13 is zero.

## 22.2.4.1.4 Auto-Negotiation enable

The Auto-Negotiation process shall be enabled by setting bit 0.12 to a logic one. If bit 0.12 is set to a logic one, then bits 0.13 and 0.8 shall have no effect on the link configuration, and the Auto-Negotiation process will determine the link configuration. If bit 0.12 is cleared to a logic zero, then bits 0.13 and 0.8 will determine the link configuration, regardless of the prior state of the link configuration and the Auto-Negotiation process.

If a PHY reports via bit 1.3 that it lacks the ability to perform Auto-Negotiation, the PHY shall return a value of zero in bit 0.12. If a PHY reports via bit 1.3 that it lacks the ability to perform Auto-Negotiation, bit 0.12 should always be written as zero, and any attempt to write a one to bit 0.12 shall be ignored.

The default value of bit 0.12 is one, unless the PHY reports via bit 1.3 that it lacks the ability to perform Auto-Negotiation, in which case the default value of bit 0.12 is zero.

## 22.2.4.1.5 Power down

The PHY may be placed in a low-power consumption state by setting bit 0.11 to a logic one. Clearing bit 0.11 to zero allows normal operation. The specific behavior of a PHY in the power-down state is implementation specific. While in the power-down state, the PHY shall respond to management transactions. During the transition to the power-down state and while in the power-down state, the PHY shall not generate spurious signals on the MII.

This is an Archive 1555 Standardser It has been superseded by a later version of this standard.

A PHY is not required to meet the RX\_CLK and TX\_CLK signal functional requirements when either bit 0.11 or bit 0.10 is set to a logic one. A PHY shall meet the RX\_CLK and TX\_CLK signal functional requirements defined in 22.2.2 within 0.5 s after both bit 0.11 and 0.10 are cleared to zero.

The default value of bit 0.11 is zero.

## 22.2.4.1.6 Isolate

The PHY may be forced to electrically isolate its data paths from the MII by setting bit 0.10 to a logic one. Clearing bit 0.10 allows normal operation. When the PHY is isolated from the MII it shall not respond to the TXD<3:0>, TX\_EN, and TX\_ER inputs, and it shall present a high impedance on its TX\_CLK, RX\_CLK, RX\_DV, RX\_ER, RXD<3:0>, COL, and CRS outputs. When the PHY is isolated from the MII it shall respond to management transactions.

A PHY that is connected to the MII via the mechanical interface defined in 22.6 shall have a default value of one for bit 0.10 so as to avoid the possibility of having multiple MII output drivers actively driving the same signal path simultaneously.

NOTE—This clause neither requires nor assumes any specific behavior at the MDI resulting from setting bit 0.10 to a logic one.

## 22.2.4.1.7 Restart Auto-Negotiation

If a PHY reports via bit 1.3 that it lacks the ability to perform Auto-Negotiation, or if Auto-Negotiation is disabled, the PHY shall return a value of zero in bit 0.9. If a PHY reports via bit 1.3 that it lacks the ability to perform Auto-Negotiation, or if Auto-Negotiation is disabled, bit 0.9 should always be written as zero, and any attempt to write a one to bit 0.9 shall be ignored.

Otherwise, the Auto-Negotiation process shall be restarted by setting bit 0.9 to a logic one. This bit is selfclearing, and a PHY shall return a value of one in bit 0.9 until the Auto-Negotiation process has been initiated. The Auto-Negotiation process shall not be affected by writing a zero to bit 0.9.

The default value of bit 0.9 is zero.

#### 22.2.4.1.8 Duplex mode

The duplex mode can be selected via either the Auto-Negotiation process, or manual duplex selection. Manual duplex selection is allowed when Auto-Negotiation is disabled by clearing bit 0.12 to zero. When Auto-Negotiation is disabled, setting bit 0.8 to a logic one configures the PHY for full-duplex operation, and clearing bit 0.8 to a logic zero configures the PHY for half-duplex operation. When Auto-Negotiation is enabled, bit 0.8 can be read or written, but the state of bit 0.8 has no effect on the link configuration. If a PHY reports via bits 1.15:11 that it is able to operate in only one duplex mode, the value of bit 0.8 shall correspond to the mode in which the PHY can operate, and any attempt to change the setting of bit 0.8 shall be ignored.

When a PHY is placed in the loopback mode of operation via bit 0.14, the behavior of the PHY shall not be affected by the state of bit 0.8.

The default value of bit 0.8 is zero, unless a PHY reports via bits 1.15:11 that it is able to operate only in full-duplex mode, in which case the default value of bit 0.8 is one.

## 22.2.4.1.9 Collision test

The COL signal at the MII may be tested by setting bit 0.7 to a logic one. When bit 0.7 is set to one, the PHY shall assert the COL signal within 512 BT in response to the assertion of TX\_EN. While bit 0.7 is set to one,

the PHY shall de-assert the COL signal within 4 BT in response to the de-assertion of TX\_EN. Clearing bit 0.7 to zero allows normal operation.

The default value of bit 0.7 is zero.

NOTE—It is recommended that the Collision Test function be used only in conjunction with the loopback mode of operation defined in 22.2.4.1.2.

## 22.2.4.1.10 Reserved bits

Bits 0.6:0 are reserved for future standardization. They shall be written as zero and shall be ignored when read; however, a PHY shall return the value zero in these bits.

## 22.2.4.2 Status register (register 1)

The assignment of bits in the Status register is shown in table 22-8 below. All of the bits in the Status register are read only, a write to the Status register shall have no effect.

| Bit(s) | Name                               | Description                                                                                                                                                   | R/W*      |

|--------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.15   | 100BASE-T4                         | 1 = PHY able to perform 100BASE-T4<br>0 = PHY not able to perform 100BASE-T4                                                                                  | RO        |

| 1.14   | 100BASE-X Full Duplex <sup>†</sup> | 1 = PHY able to perform full-duplex 100BASE-X<br>0 = PHY not able to perform full-duplex 100BASE-X                                                            | RO        |

| 1.13   | 100BASE-X Half Duplex              | 1 = PHY able to perform half-duplex 100BASE-X<br>0 = PHY not able to perform half-duplex 100BASE-X                                                            | RO        |

| 1.12   | 10 Mb/s Full Duplex <sup>b</sup>   | 1 = PHY able to operate at 10 Mb/s in full-duplex mode<br>0 = PHY not able to operate at 10 Mb/s in full-duplex mode                                          | RO        |

| 1.11   | 10 Mb/s Half Duplex                | 1 = PHY able to operate at 10 Mb/s in half-duplex mode<br>0 = PHY not able to operate at 10 Mb/s in half-duplex mode                                          | RO        |

| 1.10:7 | Reserved                           | ignore when read                                                                                                                                              | RO        |

| 1.6    | MF Preamble Suppression            | <ul><li>1 = PHY will accept management frames with preamble suppressed.</li><li>0 = PHY will not accept management frames with preamble suppressed.</li></ul> | RO        |

| 1.5    | Auto-Negotiation<br>Complete       | 1 = Auto-Negotiation process completed<br>0 = Auto-Negotiation process not completed                                                                          | RO        |

| 1.4    | Remote Fault                       | 1 = remote fault condition detected<br>0 = no remote fault condition detected                                                                                 | RO/<br>LH |

| 1.3    | Auto-Negotiation Ability           | 1 = PHY is able to perform Auto-Negotiation<br>0 = PHY is not able to perform Auto-Negotiation                                                                | RO        |

| 1.2    | Link Status                        | 1 = link is up<br>0 = link is down                                                                                                                            | RO/<br>LL |

| 1.1    | Jabber Detect                      | 1 = jabber condition detected<br>0 = no jabber condition detected                                                                                             | RO/<br>LH |

| 1.0    | Extended Capability                | 1 = extended register capabilities<br>0 = basic register set capabilities only                                                                                | RO        |

## Table 8—Status register bit definitions

\*RO = Read Only, LL = Latching Low, LH = Latching High

<sup>†</sup>Specifications for full-duplex mode operation are planned for future work.

This is an Archive 1555 Standardser te has been superseded by a later version of this standard.

## 22.2.4.2.1 100BASE-T4 ability

When read as a logic one, bit 1.15 indicates that the PHY has the ability to perform link transmission and reception using the 100BASE-T4 signaling specification. When read as a logic zero, bit 1.15 indicates that the PHY lacks the ability to perform link transmission and reception using the 100BASE-T4 signaling specification.

## 22.2.4.2.2 100BASE-X full-duplex ability

When read as a logic one, bit 1.14 indicates that the PHY has the ability to perform full-duplex link transmission and reception using the 100BASE-X signaling specification. When read as a logic zero, bit 1.14 indicates that the PHY lacks the ability to perform full-duplex link transmission and reception using the 100BASE-X signaling specification.

NOTE—Specifications for full-duplex mode operation are planned for future work.

# 22.2.4.2.3 100BASE-X half-duplex ability

When read as a logic one, bit 1.13 indicates that the PHY has the ability to perform half-duplex link transmission and reception using the 100BASE-X signaling specification. When read as a logic zero, bit 1.13 indicates that the PHY lacks the ability to perform half-duplex link transmission and reception using the 100BASE-X signaling specification.

# 22.2.4.2.4 10 Mb/s full-duplex ability

When read as a logic one, bit 1.12 indicates that the PHY has the ability to perform full duplex link transmission and reception while operating at 10 Mb/s. When read as a logic zero, bit 1.12 indicates that the PHY lacks the ability to perform full duplex link transmission and reception while operating at 10 Mb/s.

NOTE—Specifications for full-duplex mode operation are planned for future work.

## 22.2.4.2.5 10 Mb/s half-duplex ability

When read as a logic one, bit 1.11 indicates that the PHY has the ability to perform half-duplex link transmission and reception while operating at 10 Mb/s. When read as a logic zero, bit 1.11 indicates that the PHY lacks the ability to perform half-duplex link transmission and reception while operating at 10 Mb/s.

## 22.2.4.2.6 Reserved bits

Bits 1.10:7 are reserved for future standardization and shall be ignored when read; however, a PHY shall return the value zero in these bits. Bits 1.10:8 are specifically reserved for future PHY capabilities that will be reflected in the Auto-Negotiation base link code word Technology Ability field, as defined in 28.2.1.2.

## 22.2.4.2.7 MF preamble suppression ability

When read as a logic one, bit 1.6 indicates that the PHY is able to accept management frames regardless of whether they are or are not preceded by the preamble pattern described in 22.2.4.4.2. When read as a logic zero, bit 1.6 indicates that the PHY is not able to accept management frames unless they are preceded by the preamble pattern described in 22.2.4.4.2.

## 22.2.4.2.8 Auto-Negotiation complete

When read as a logic one, bit 1.5 indicates that the Auto-Negotiation process has been completed, and that the contents of registers 4, 5, 6, and 7 are valid. When read as a logic zero, bit 1.5 indicates that the Auto-

Negotiation process has not been completed, and that the contents of registers 4, 5, 6, and 7 are meaningless. A PHY shall return a value of zero in bit 1.5 if Auto-Negotiation is disabled by clearing bit 0.12. A PHY shall also return a value of zero in bit 1.5 if it lacks the ability to perform Auto-Negotiation.

## 22.2.4.2.9 Remote fault

When read as a logic one, bit 1.4 indicates that a remote fault condition has been detected. The type of fault as well as the criteria and method of fault detection is PHY specific. The Remote Fault bit shall be implemented with a latching function, such that the occurrence of a remote fault will cause the Remote Fault bit to become set and remain set until it is cleared. The Remote Fault bit shall be cleared each time register 1 is read via the management interface, and shall also be cleared by a PHY reset.

If a PHY has no provision for remote fault detection, it shall maintain bit 1.4 in a cleared state. Further information regarding the remote fault indication can be found in 28.2.1.2, and in 24.3.2.1.

## 22.2.4.2.10 Auto-Negotiation ability

When read as a logic one, bit 1.3 indicates that the PHY has the ability to perform Auto-Negotiation. When read as a logic zero, bit 1.3 indicates that the PHY lacks the ability to perform Auto-Negotiation.

#### 22.2.4.2.11 Link Status

When read as a logic one, bit 1.2 indicates that the PHY has determined that a valid link has been established. When read as a logic zero, bit 1.2 indicates that the link is not valid. The criteria for determining link validity is PHY specific. The Link Status bit shall be implemented with a latching function, such that the occurrence of a link failure condition will cause the Link Status bit to become cleared and remain cleared until it is read via the management interface. This status indication is intended to support the management attribute defined in 30.5.1.1.4, aMediaAvailable.

## 22.2.4.2.12 Jabber detect

When read as a logic one, bit 1.1 indicates that a jabber condition has been detected. This status indication is intended to support the management attribute defined in 30.5.1.1.6, aJabber, and the MAU notification defined in 30.5.1.3.1, nJabber. The criteria for the detection of a jabber condition is PHY specific. The Jabber Detect bit shall be implemented with a latching function, such that the occurrence of a jabber condition will cause the Jabber Detect bit to become set and remain set until it is cleared. The Jabber Detect bit shall be cleared each time register 1 is read via the management interface, and shall also be cleared by a PHY reset.

PHYs specified for 100 Mb/s operation (100BASE-X and 100BASE-T4) do not incorporate a Jabber Detect function, as this function is defined to be performed in the repeater unit in 100 Mb/s systems. Therefore, 100BASE-X and 100BASE-T4 PHYs shall always return a value of zero in bit 1.1.

## 22.2.4.2.13 Extended capability

When read as a logic one, bit 1.0 indicates that the PHY provides an extended set of capabilities which may be accessed through the extended register set. When read as a logic zero, bit 1.0 indicates that the PHY provides only the basic register set.

## 22.2.4.3 Extended capability registers

In addition to the basic register set defined in 22.2.4.1 and 22.2.4.2, PHYs may provide an extended set of capabilities that may be accessed and controlled via the MII management interface. Six registers have been defined within the extended address space for the purpose of providing a PHY-specific identifier to layer management, and to provide control and monitoring for the Auto-Negotiation process.

This is an Archive 1555 Standardser It has been superseded by a later version of this standard.

If an attempt is made to perform a read transaction to a register in the extended register set, and the PHY being read does not implement the addressed register, the PHY shall not drive the MDIO line in response to the read transaction. If an attempt is made to perform a write transaction to a register in the extended register set, and the PHY being written does not implement the addressed register, the write transaction shall be ignored by the PHY.

## 22.2.4.3.1 PHY Identifier (registers 2 and 3)

Registers 2 and 3 provide a 32-bit value, which shall constitute a unique identifier for a particular type of PHY. A PHY may return a value of zero in each of the 32 bits of the PHY Identifier.

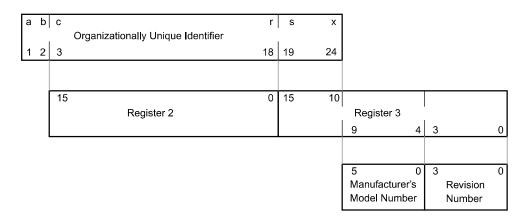

Bit 2.15 shall be the MSB of the PHY Identifier, and bit 3.0 shall be the LSB of the PHY Identifier.

The PHY Identifier shall be composed of the third through 24th bits of the Organizationally Unique Identifier (OUI) assigned to the PHY manufacturer by the IEEE,<sup>28</sup> plus a six-bit manufacturer's model number, plus a four-bit manufacturer's revision number. The PHY Identifier is intended to provide sufficient information to support the oResourceTypeID object as required in 30.1.2.

The third bit of the OUI is assigned to bit 2.15, the fourth bit of the OUI is assigned to bit 2.14, and so on. Bit 2.0 contains the eighteenth bit of the OUI. Bit 3.15 contains the nineteenth bit of the OUI, and bit 3.10 contains the twenty-fourth bit of the OUI. Bit 3.9 contains the MSB of the manufacturer's model number. Bit 3.4 contains the LSB of the manufacturer's model number. Bit 3.3 contains the MSB of the manufacturer's revision number, and bit 3.0 contains the LSB of the manufacturer's revision number.

Figure 22-12 depicts the mapping of this information to the bits of Registers 2 and 3. Additional detail describing the format of OUIs can be found in IEEE Std 802-1990.

Figure 22-12—Format of PHY Identifier

## 22.2.4.3.2 Auto-Negotiation advertisement (register 4)

Register 4 provides 16 bits that are used by the Auto-Negotiation process. See 28.2.4.1.

<sup>&</sup>lt;sup>28</sup>Interested applicants should contact the IEEE Standards Department, Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA.

## 22.2.4.3.3 Auto-Negotiation link partner ability (register 5)

Register 5 provides 16 bits that are used by the Auto-Negotiation process. See 28.2.4.1.

#### 22.2.4.3.4 Auto-Negotiation expansion (register 6)

Register 6 provides 16 bits that are used by the Auto-Negotiation process. See 28.2.4.1.

#### 22.2.4.3.5 Auto-Negotiation next page (register 7)

Register 7 provides 16 bits that are used by the Auto-Negotiation process. See 28.2.4.1.

#### 22.2.4.3.6 PHY specific registers

A particular PHY may provide additional registers beyond those defined above. Register addresses 16 through 31 (decimal) may be used to provide vendor-specific functions or abilities. Register addresses 8 through 15 (decimal) are reserved for assignment within future editions of this standard.

#### 22.2.4.4 Management frame structure

Frames transmitted on the MII Management Interface shall have the frame structure shown in table 22-9. The order of bit transmission shall be from left to right.

#### Table 9—Management frame format

| Management frame fields |     |    |    |       |       |    |                  |      |

|-------------------------|-----|----|----|-------|-------|----|------------------|------|

|                         | PRE | ST | OP | PHYAD | REGAD | ТА | DATA             | IDLE |

| READ                    | 11  | 01 | 10 | AAAAA | RRRRR | Z0 | DDDDDDDDDDDDDDDD | Z    |

| WRITE                   | 11  | 01 | 01 | AAAAA | RRRRR | 10 | DDDDDDDDDDDDDDDD | Z    |

#### 22.2.4.4.1 IDLE (IDLE condition)

The IDLE condition on MDIO is a high-impedance state. All three state drivers shall be disabled and the PHY's pull-up resistor will pull the MDIO line to a logic one.

#### 22.2.4.4.2 PRE (preamble)

At the beginning of each transaction, the station management entity shall send a sequence of 32 contiguous logic one bits on MDIO with 32 corresponding cycles on MDC to provide the PHY with a pattern that it can use to establish synchronization. A PHY shall observe a sequence of 32 contiguous one bits on MDIO with 32 corresponding cycles on MDC before it responds to any transaction.

If the STA determines that every PHY that is connected to the MDIO signal is able to accept management frames that are not preceded by the preamble pattern, then the STA may suppress the generation of the preamble pattern, and may initiate management frames with the ST (Start of Frame) pattern.

#### 22.2.4.4.3 ST (start of frame)

The start of frame is indicated by a <01> pattern. This pattern assures transitions from the default logic one line state to zero and back to one.

This is an Archive 1555 Standardser te has been superseded by a later version of this standard.

IEEE Std 802.3, 1998 Edition

#### 22.2.4.4.4 OP (operation code)

The operation code for a read transaction is <10>, while the operation code for a write transaction is <01>.

#### 22.2.4.4.5 PHYAD (PHY Address)

The PHY Address is five bits, allowing 32 unique PHY addresses. The first PHY address bit transmitted and received is the MSB of the address. A PHY that is connected to the station management entity via the mechanical interface defined in 22.6 shall always respond to transactions addressed to PHY Address zero <00000>. A station management entity that is attached to multiple PHYs must have a priori knowledge of the appropriate PHY Address for each PHY.

#### 22.2.4.4.6 REGAD (Register Address)

The Register Address is five bits, allowing 32 individual registers to be addressed within each PHY. The first Register Address bit transmitted and received is the MSB of the address. The register accessed at Register Address zero <00000> shall be the control register defined in 22.2.4.1, and the register accessed at Register Address one <00001> shall be the status register defined in 22.2.4.2.

#### 22.2.4.4.7 TA (turnaround)

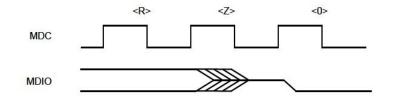

The turnaround time is a 2 bit time spacing between the Register Address field and the Data field of a management frame to avoid contention during a read transaction. For a read transaction, both the STA and the PHY shall remain in a high-impedance state for the first bit time of the turnaround. The PHY shall drive a zero bit during the second bit time of the turnaround of a read transaction. During a write transaction, the STA shall drive a one bit for the first bit time of the turnaround and a zero bit for the second bit time of the turnaround. Figure 22-13 shows the behavior of the MDIO signal during the turnaround field of a read transaction.

#### Figure 22-13—Behavior of MDIO during TA field of a read transaction

#### 22.2.4.4.8 DATA (data)

The data field is 16 bits. The first data bit transmitted and received shall be bit 15 of the register being addressed.

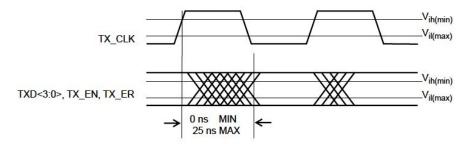

#### 22.3 Signal timing characteristics

All signal timing characteristics shall be measured using the techniques specified in annex 22C. The signal threshold potentials  $V_{ih(min)}$  and  $V_{il(max)}$  are defined in 22.4.4.1.

#### CSMA/CD

The HIGH time of an MII signal is defined as the length of time that the potential of the signal is greater than or equal to  $V_{ih(min)}$ . The LOW time of an MII signal is defined as the length of time that the potential of the signal is less than or equal to  $V_{il(max)}$ .

The setup time of an MII signal relative to an MII clock edge is defined as the length of time between when the signal exits and remains out of the switching region and when the clock enters the switching region. The hold time of an MII signal relative to an MII clock edge is defined as the length of time between when the clock exits the switching region and when the signal enters the switching region.

The propagation delay from an MII clock edge to a valid MII signal is defined as the length of time between when the clock exits the switching region and when the signal exits and remains out of the switching region.

#### 22.3.1 Signals that are synchronous to TX\_CLK

Figure 22-14 shows the timing relationship for the signals associated with the transmit data path at the MII connector. The clock to output delay shall be a minimum of 0 ns and a maximum of 25 ns.

Figure 22-14—Transmit signal timing relationships at the MII

#### 22.3.1.1 TX\_EN

TX\_EN is transitioned by the Reconciliation sublayer synchronously with respect to the TX\_CLK rising edge with the timing as shown in figure 22-14.

#### 22.3.1.2 TXD<3:0>

TXD<3:0> is transitioned by the Reconciliation sublayer synchronously with respect to the TX\_CLK rising edge with the timing as depicted in figure 22-14.

#### 22.3.1.3 TX\_ER

TX\_ER is transitioned synchronously with respect to the rising edge of TX\_CLK as shown in figure 22-14.

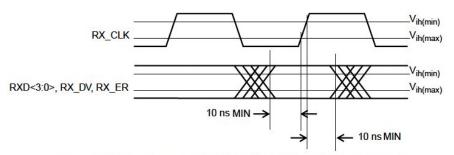

#### 22.3.2 Signals that are synchronous to RX\_CLK

Figure 22-15 shows the timing relationship for the signals associated with the receive data path at the MII connector. The timing is referenced to the rising edge of the RX\_CLK. The input setup time shall be a minimum of 10 ns and the input hold time shall be a minimum of 10 ns.

This is an christing the standard serve has been superseded by a later version of this standard.

Figure 22-15—Receive signal timing relationships at the MII

# 22.3.2.1 RX\_DV

RX\_DV is sampled by the Reconciliation sublayer synchronously with respect to the rising edge of RX\_CLK with the timing shown in figure 22-15.

## 22.3.2.2 RXD<3:0>

RXD<3:0> is sampled by the Reconciliation sublayer synchronously with respect to the rising edge of  $RX\_CLK$  as shown in figure 22-15. The RXD<3:0> timing requirements must be met at all rising edges of  $RX\_CLK$ .

## 22.3.2.3 RX\_ER

RX\_ER is sampled by the Reconciliation sublayer synchronously with respect to the rising edge of RX\_CLK as shown in figure 22-15. The RX\_ER timing requirements must be met at all rising edges of RX\_CLK.

## 22.3.3 Signals that have no required clock relationship

## 22.3.3.1 CRS

CRS is driven by the PHY. Transitions on CRS have no required relationship to either of the clock signals provided at the MII.

## 22.3.3.2 COL

COL is driven by the PHY. Transitions on COL have no required relationship to either of the clock signals provided at the MII.

## 22.3.4 MDIO timing relationship to MDC

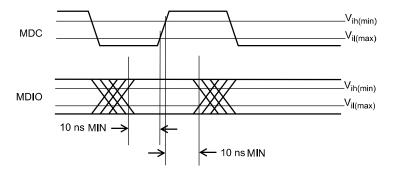

MDIO (Management Data Input/Output) is a bidirectional signal that can be sourced by the Station Management Entity (STA) or the PHY. When the STA sources the MDIO signal, the STA shall provide a minimum of 10 ns of setup time and a minimum of 10 ns of hold time referenced to the rising edge of MDC, as shown in figure 22-16, measured at the MII connector.

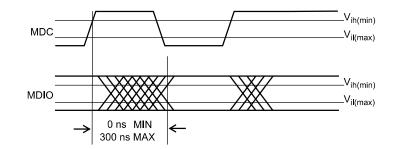

When the MDIO signal is sourced by the PHY, it is sampled by the STA synchronously with respect to the rising edge of MDC. The clock to output delay from the PHY, as measured at the MII connector, shall be a minimum of 0 ns, and a maximum of 300 ns, as shown in figure 22-17.

Figure 22-16—MDIO sourced by STA

Figure 22-17—MDIO sourced by PHY

## 22.4 Electrical characteristics

The electrical characteristics of the MII are specified such that the three application environments described in 22.1 are accommodated. The electrical specifications are optimized for the integrated circuit to integrated circuit application environment, but integrated circuit drivers and receivers that are implemented in compliance with the specification will also support the mother board to daughter board and short cable application environments, provided those environments are constrained to the limits specified in this clause.

NOTE—The specifications for the driver and receiver characteristics can be met with TTL compatible input and output buffers implemented in a digital CMOS ASIC process.

## 22.4.1 Signal levels

The MII uses TTL signal levels, which are compatible with devices operating at a nominal supply voltage of either 5.0 or 3.3 V.

NOTE—Care should be taken to ensure that all MII receivers can tolerate dc input potentials from 0.00 V to 5.50 V, referenced to the COMMON signal, and transient input potentials as high as 7.3 V, or as low as -1.8 V, referenced to the COMMON signal, which can occur when MII signals change state. The transient duration will not exceed 15 ns. The dc source impedance will be no less than  $R_{oh(min)}$ . The transient source impedance will be no less than  $(68 \times 0.85 =) 57.8 \Omega$ .

This is an Archive EEE Standardser te has been superseded by a later version of this standard.

Aerohive - Exhibit 1025 0079

# 22.4.2 Signal paths

MII signals can be divided into two groups: signals that go between the STA and the PHY, and signals that go between the Reconciliation sublayer and the PHY.

Signals between the STA and the PHY may connect to one or more PHYs. When a signal goes between the STA and a single PHY, the signal's path is a point-to-point transmission path. When a signal goes between the STA and multiple PHYs, the signal's transmission path has drivers and receivers attached in any order along the length of the path and is not considered a point-to-point transmission path.

Signals between the Reconciliation sublayer and the PHY may also connect to one or more PHYs. However, the transmission path of each of these signals shall be either a point-to-point transmission path or a sequence of point-to-point transmission paths connected in series.

All connections to a point-to-point transmission path are at the path ends. The simplest point-to-point transmission path has a driver at one end and a receiver at the other. Point-to-point transmission paths can also have more than one driver and more than one receiver if the drivers and receivers are lumped at the ends of the path, and if the maximum propagation delay between the drivers and receivers at a given end of the path is a very small fraction of the 10%–90% rise/fall time for signals driven onto the path.

The MII shall use unbalanced signal transmission paths. The characteristic impedance  $Z_0$  of transmission paths is not specified for electrically short paths where transmission line reflections can be safely ignored.

The characteristic impedance  $Z_0$  of electrically long transmission paths or path segments shall be 68  $\Omega \pm 15\%$ .

The output impedance of the driver shall be used to control transmission line reflections on all electrically long point-to-point signal paths.

NOTE—In the context of this clause, a transmission path whose round-trip propagation delay is less than half of the 10%–90% rise/fall time of signals driven onto the path is considered an electrically short transmission path.

## 22.4.3 Driver characteristics

The driver characteristics defined in this clause apply to all MII signal drivers. The driver characteristics are specified in terms of both their ac and dc characteristics.

NOTE—Rail-to-rail drivers that comply with the driver output V-I diagrams in annex 22B will meet the following ac and dc characteristics.

## 22.4.3.1 DC characteristics

The high (one) logic level output potential  $V_{oh}$  shall be no less than 2.40 V at an output current  $I_{oh}$  of -4.0 mA. The low (zero) logic level output potential  $V_{ol}$  shall not be greater than 0.40 V at an output current  $I_{ol}$  of 4.0 mA.

## 22.4.3.2 AC characteristics

Drivers must also meet certain ac specifications in order to ensure adequate signal quality for electrically long point-to-point transmission paths. The ac specifications shall guarantee the following performance requirements.

The initial incident potential change arriving at the receiving end of a point-to-point MII signal path plus its reflection from the receiving end of the path must switch the receiver input potential monotonically from a valid high (one) level to  $V_{il} \le V_{il(max)} - 200 \text{ mV}$ , or from a valid low (zero) level to  $V_{ih} \ge V_{ih(min)} + 200 \text{ mV}$ .

This is an Archive IEEE Standard. It has been superseded by a later of this standard.

Aerohive - Exhibit 1025 0080 Subsequent incident potential changes arriving at the receiving end of a point-to-point MII signal path plus their reflections from the receiving end of the path must not cause the receiver input potential to reenter the range  $V_{il(max)} - 200 \text{ mV} < V_i < V_{ih(min)} + 200 \text{ mV}$  except when switching from one valid logic level to the other. Such subsequent incident potential changes result from a mismatch between the characteristic impedance of the signal path and the driver output impedance.

## 22.4.4 Receiver characteristics

The receiver characteristics are specified in terms of the threshold levels for the logical high (one) and logical low (zero) states. In addition, receivers must meet the input current and capacitance limits.

## 22.4.4.1 Voltage thresholds

An input potential  $V_i$  of 2.00 V or greater shall be interpreted by the receiver as a logical high (one). Thus,  $V_{ih(min)} = 2.00$  V. An input potential  $V_i$  of 0.80 V or less shall be interpreted by the receiver as a logical low (zero). Thus,  $V_{il(max)} = 0.80$  V. The switching region is defined as signal potentials greater than  $V_{il(max)}$  and less than  $V_{ih(min)}$ . When the input signal potential is in the switching region, the receiver output is undefined.

# 22.4.4.2 Input current

The input current requirements shall be measured at the MII connector and shall be referenced to the +5 V supply and COMMON pins of the connector. The input current requirements shall be met across the full range of supply voltage specified in 22.5.1.

The bidirectional signal MDIO has two sets of input current requirements. The MDIO drivers must be disabled when the input current measurement is made.

The input current characteristics for all MII signals shall fall within the limits specified in table 22-10.

| Symbol          | Parameter          | Condition              | Signal(s)                                 | Min (µA) | Max (µA) |

|-----------------|--------------------|------------------------|-------------------------------------------|----------|----------|

| I <sub>ih</sub> | Input High Current | V <sub>i</sub> =5.25 V | All except COL,<br>MDC, MDIO <sup>*</sup> | _        | 200      |

|                 |                    |                        | COL <sup>†</sup>                          | _        | 20       |

|                 |                    |                        | MDC <sup>‡</sup>                          | _        | 20       |

|                 |                    |                        | MDIO <sup>§</sup>                         | _        | 3000     |

|                 |                    |                        | MDIO <sup>**</sup>                        | _        | 20       |

| I <sub>il</sub> | Input Low Current  | V <sub>i</sub> =0.00 V | All except COL,<br>MDC, MDIO <sup>a</sup> | -20      | _        |

|                 |                    |                        | COL <sup>b</sup>                          | -200     | _        |

|                 |                    |                        | MDC <sup>c</sup>                          | -20      | _        |

|                 |                    |                        | MDIO <sup>d</sup>                         | -180     | _        |

|                 |                    |                        | MDIO <sup>e</sup>                         | -3800    | _        |

## Table 10—Input current limits

| Symbol          | Parameter               | Condition             | Signal(s)         | Min (µA) | Max (µA) |

|-----------------|-------------------------|-----------------------|-------------------|----------|----------|

| I <sub>iq</sub> | Input Quiescent Current | V <sub>i</sub> =2.4 V | MDIO <sup>d</sup> |          | 1450     |

|                 |                         |                       | MDIO <sup>e</sup> | -1450    | _        |

#### Table 10—Input current limits (Continued)

\*Measured at input of Reconciliation sublayer for CRS, RXD<3:0>, RX CLK, RX DV, RX ER, and TX CLK. Measured at inputs of PHY for TXD<3:0>, TX EN, and TX ER.

<sup>†</sup>Measured at input of Reconciliation sublayer.

<sup>‡</sup>Measured at input of PHY.

<sup>§</sup>Measured at input of STA. \*\*Measured at input of PHY, which can be attached via the mechanical interface specified in 22.6.

NOTE—These limits for dc input current allow the use of weak resistive pull-ups or pull-downs on the input of each MII signal. They allow the use of weak resistive pull-downs on the signals other than COL, MDC, and MDIO. They allow the use of a weak resistive pull-up on the signal COL. They allow the use of a resistive pull-down of 2 k $\Omega \pm 5\%$  on the MDIO signal in the STA. They require a resistive pull-up of 1.5 k $\Omega$  ± 5% on the MDIO signal in a PHY that is attached to the MII via the mechanical interface specified in 22.6. The limits on MDC and MDIO allow the signals to be "bused" to several PHYs that are contained on the same printed circuit assembly, with a single PHY attached via the MII connector.

#### 22.4.4.3 Input capacitance

For all signals other than MDIO, the receiver input capacitance C<sub>i</sub> shall not exceed 8 pF.

For the MDIO signal, the transceiver input capacitance shall not exceed 10 pF.

#### 22.4.5 Cable characteristics

The MII cable consists of a bundle of individual twisted pairs of conductors with an overall shield covering this bundle. Each twisted pair shall be composed of a conductor for an individual signal and a return path dedicated to that signal.

NOTE-It is recommended that the signals RX\_CLK and TX\_CLK be connected to pairs that are located in the center of the cable bundle.

## 22.4.5.1 Conductor size

The specifications for dc resistance in 22.4.5.6 and characteristic impedance in 22.4.5.2 assume a conductor size of 0.32 mm (28 AWG).

## 22.4.5.2 Characteristic impedance

The single-ended characteristic impedance of each twisted pair shall be 68  $\Omega \pm 10\%$ . The characteristic impedance measurement shall be performed with the return conductor connected to the cable's overall shield at both ends of the cable.

## 22.4.5.3 Delay

The propagation delay for each twisted pair, measured from the MII connector to the PHY, shall not exceed 2.5 ns. The measurement shall be made with the return conductor of the pair connected to the cable's overall shield at both ends of the cable. The propagation delay shall be measured at a frequency of 25 MHz.

# 22.4.5.4 Delay variation

The variation in the propagation delay of the twisted pairs in a given cable bundle, measured from the MII connector to the PHY, shall not exceed 0.1 ns. The measurement shall be made with the return conductor of the pair connected to the cable's overall shield at both ends of the cable.

# 22.4.5.5 Shielding

The overall shield must provide sufficient shielding to meet the requirements of protection against electromagnetic interference.

The overall shield shall be terminated to the connector shell as defined in 22.6.2. A double shield, consisting of both braid and foil shielding, is strongly recommended.

This is an Archive 1555 Standardser te has been superseded by a later version of this standard.

# 22.4.5.6 DC resistance

The dc resistance of each conductor in the cable, including the contact resistance of the connector, shall not exceed 150 m $\Omega$  measured from the MII connector to the remote PHY.

## 22.4.6 Hot insertion and removal

The insertion or removal of a PHY from the MII with power applied (hot insertion or removal) shall not damage the devices on either side of the MII. In order to prevent contention between multiple output buffers driving the PHY output signals, a PHY that is attached to the MII via the mechanical interface defined in 22.6 shall ensure that its output buffers present a high impedance to the MII during the insertion process, and shall ensure that this condition persists until the output buffers are enabled via the Isolate control bit in the management interface basic register.

NOTE—The act of inserting or removing a PHY from an operational system may cause the loss of one or more packets or management frames that may be in transit across the MII or MDI.

# 22.5 Power supply

When the mechanical interface defined in 22.6 is used to interconnect printed circuit subassemblies, the Reconciliation sublayer shall provide a regulated power supply for use by the PHY.

The power supply shall use the following MII lines:

+5 V: The plus voltage output to the PHY.

COMMON: The return to the power supply.

#### 22.5.1 Supply voltage

The regulated supply voltage to the PHY shall be 5 Vdc  $\pm$  5% at the MII connector with respect to the COM-MON circuit at the MII over the range of load current from 0 to 750 mA. The method of over/under voltage protection is not specified; however, under no conditions of operation shall the source apply a voltage to the +5 V circuit of less than 0 V or greater than +5.25 Vdc.

Implementations that provide a conversion from the MII to the Attachment Unit Interface (AUI) to support connection to 10 Mb/s Medium Attachment Units (MAUs) will require a supplemental power source in order to meet the AUI power supply requirements specified in 7.5.2.5.

#### 22.5.2 Load current

The sum of the currents carried on the +5 V lines shall not exceed 750 mA, measured at the MII connector. The surge current drawn by the PHY shall not exceed 5 A peak for a period of 10 ms. The PHY shall be capable of powering up from 750 mA current limited sources.

## 22.5.3 Short-circuit protection

Adequate provisions shall be made to ensure protection of the power supply from overload conditions, including a short circuit between the +5 V lines and the COMMON lines.

# 22.6 Mechanical characteristics

When the MII is used to interconnect two printed circuit assemblies via a short length of cable, the cable shall be connected to the circuit assembly that implements the Reconciliation sublayer by means of the mechanical interface defined in this clause.

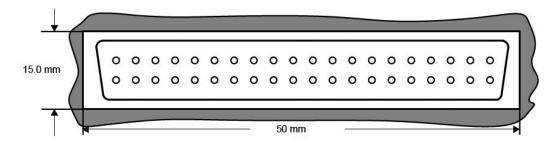

## 22.6.1 Definition of mechanical interface

A 40-pole connector having the mechanical mateability dimensions as specified in IEC 1076-3-101: 1995 shall be used for the MII connector. The circuit assembly that contains the MAC sublayer and Reconciliation sublayer shall have a female connector with screw locks, and the mating cable shall have a male connector with jack screws.

No requirements are imposed on the mechanical interface used to connect the MII cable to the PHY circuit assembly when the MII cable is permanently attached to the PHY circuit assembly, as shown in figure 22-2. If the cable is not permanently attached to the PHY circuit assembly, then a male connector with jack screws shall be used for the MII connector at the PHY circuit assembly.

NOTE—All MII conformance tests are performed at the mating surfaces of the MII connector at the Reconciliation sublayer end of the cable. If a PHY circuit assembly does not have a permanently attached cable, the vendor must ensure that all of the requirements of this clause are also met when a cable that meets the requirements of 22.4.5 is used to attach the PHY circuit assembly to the circuit assembly that contains the Reconciliation sublayer.

## 22.6.2 Shielding effectiveness and transfer impedance

The shells of these connectors shall be plated with conductive material to ensure the integrity of the current path from the cable shield to the chassis. The transfer impedance of this path shall not exceed the values listed in table 22-11, after a minimum of 500 cycles of mating and unmating. The shield transfer impedance values listed in the table are measured in accordance with the procedure defined in annex L of IEEE P1394 [A18].

| Frequenc | y Value                |

|----------|------------------------|

| 30 MHz   | $-26 \text{ dB}\Omega$ |

| 159 MHz  | -13 dBΩ                |

| 500 MHz  | $-5 \text{ dB}\Omega$  |

## Table 11—Transfer impedance performance requirements

All additions to provide for female shell to male shell conductivity shall be on the shell of the connector with male contacts. There should be multiple contact points around the sides of this shell to provide for shield continuity.

This is an Archive 155 E Standardse It has been superseded by a later version of this standard.

IEEE Std 802.3, 1998 Edition

#### 22.6.3 Connector pin numbering

Figure 22-18 depicts the MII connector pin numbering, as seen looking into the contacts of a female connector from the mating side.

$$\circ^{20} \circ^{19} \circ^{18} \circ^{17} \circ^{16} \circ^{15} \circ^{14} \circ^{13} \circ^{12} \circ^{11} \circ^{10} \circ^{9} \circ^{8} \circ^{7} \circ^{6} \circ^{5} \circ^{4} \circ^{3} \circ^{2} \circ^{1} \circ^{40} \circ^{39} \circ^{38} \circ^{37} \circ^{36} \circ^{35} \circ^{34} \circ^{33} \circ^{32} \circ^{31} \circ^{30} \circ^{29} \circ^{28} \circ^{27} \circ^{26} \circ^{25} \circ^{24} \circ^{23} \circ^{22} \circ^{21} \circ^$$

#### Figure 22-18—MII connector pin numbering

# 22.6.4 Clearance dimensions

The circuit assembly that contains the MAC sublayer and Reconciliation sublayer shall provide sufficient clearance around the MII connector to allow the attachment of cables that use die cast metal backshells and overmold assemblies. This requirement may be met by providing the clearance dimensions shown in figure 22-19.

Figure 22-19—MII connector clearance dimensions

## 22.6.5 Contact assignments

Table 22-12 shows the assignment of circuits to connector contacts.

| Contact | Signal name | Contact | Signal name |

|---------|-------------|---------|-------------|

| 1       | +5 V        | 21      | +5 V        |

| 2       | MDIO        | 22      | COMMON      |

| 3       | MDC         | 23      | COMMON      |

| 4       | RXD<3>      | 24      | COMMON      |

| 5       | RXD<2>      | 25      | COMMON      |

| 6       | RXD<1>      | 26      | COMMON      |

| 7       | RXD<0>      | 27      | COMMON      |

| 8       | RX_DV       | 28      | COMMON      |

| 9       | RX_CLK      | 29      | COMMON      |

| 10      | RX_ER       | 30      | COMMON      |

| 11      | TX_ER       | 31      | COMMON      |

| 12      | TX_CLK      | 32      | COMMON      |

| 13      | TX_EN       | 33      | COMMON      |

| 14      | TXD<0>      | 34      | COMMON      |

| 15      | TXD<1>      | 35      | COMMON      |

| 16      | TXD<2>      | 36      | COMMON      |

| 17      | TXD<3>      | 37      | COMMON      |

| 18      | COL         | 38      | COMMON      |

| 19      | CRS         | 39      | COMMON      |

| 20      | +5 V        | 40      | +5 V        |

#### Table 12—MII connector contact assignments

This is an Archive 1555 Standardser the has been superseded by a later version of this standard.

# 22.7 Protocol Implementation Conformance Statement (PICS) proforma for clause 22, Reconciliation Sublayer (RS) and Media Independent Interface (MII)<sup>29</sup>

## 22.7.1 Introduction

The supplier of a protocol implementation that is claimed to conform to IEEE Std 802.3u-1995, Reconciliation Sublayer (RS) and Media Independent Interface (MII), shall complete the following Protocol Implementation Conformance Statement (PICS) proforma.

A detailed description of the symbols used in the PICS proforma, along with instructions for completing the PICS proforma, can be found in clause 21.

# 22.7.2 Identification

## 22.7.2.1 Implementation identification

| Supplier                                                                                                                                                                      |                                                          |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| Contact point for enquiries about the PICS                                                                                                                                    |                                                          |  |  |

| Implementation Name(s) and Version(s)                                                                                                                                         |                                                          |  |  |

| Other information necessary for full identification—e.g., name(s) and version(s) for machines and/or operating systems; System Names(s)                                       |                                                          |  |  |

| NOTES                                                                                                                                                                         |                                                          |  |  |

| 1—Only the first three items are required for all implementations; other information may be completed as appropri-<br>ate in meeting the requirements for the identification. |                                                          |  |  |

| 2—The terms Name and Version should be interpreted a (e.g., Type, Series, Model).                                                                                             | ppropriately to correspond with a supplier's terminology |  |  |

# 22.7.2.2 Protocol summary

| Identification of protocol standard                                                                             | IEEE Std 802.3u-1995, Reconciliation Sublayer (RS) and Media Independent Interface (MII) |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Identification of amendments and corrigenda to this PICS proforma that have been completed as part of this PICS |                                                                                          |

| Have any Exception items been required?<br>(See clause 21; the answer Yes means that the implementa             | No [] Yes []<br>tion does not conform to the standard.)                                  |

| Date of Statement                                                                                               |                                                                                          |

<sup>&</sup>lt;sup>29</sup>Copyright release for PICS proformas Users of this standard may freely reproduce the PICS proforma in this annex so that it can be used for its intended purpose and may further publish the completed PICS.

# 22.7.3 PICS proforma tables for reconciliation sublayer and media independent interface

# 22.7.3.1 Mapping of PLS service primitives

| Item | Feature           | Subclause | Status | Support | Value/Comment                            |

|------|-------------------|-----------|--------|---------|------------------------------------------|

| PL1  | Response to RX_ER | 22.2.1.5  | М      |         | Must produce FrameCheckEr-<br>ror at MAC |

# 22.7.3.2 Mll signal functional specifications

| Item | Feature                                                                            | Subclause | Status | Support | Value/Comment                                            |

|------|------------------------------------------------------------------------------------|-----------|--------|---------|----------------------------------------------------------|

| SF1  | TX_CLK frequency                                                                   | 22.2.2.1  | М      |         | 25% of transmitted data rate<br>(25 MHz or 2.5 MHz)      |

| SF2  | TX_CLK duty cycle                                                                  | 22.2.2.1  | М      |         | 35% to 65%                                               |

| SF3  | RX_CLK min high/low time                                                           | 22.2.2.2  | М      |         | 35% of nominal period                                    |

| SF4  | RX_CLK synchronous to re-<br>covered data                                          | 22.2.2.2  | М      |         |                                                          |

| SF5  | RX_CLK frequency                                                                   | 22.2.2.2  | М      |         | 25% of received data rate<br>(25 MHz or 2.5 MHz)         |

| SF6  | RX_CLK duty cycle                                                                  | 22.2.2.2  | М      |         | 35% to 65%                                               |

| SF7  | RX_CLK source due to loss of signal                                                | 22.2.2.2  | М      |         | Nominal clock reference<br>(e.g., TX_CLK reference)      |

| SF8  | RX_CLK transitions only<br>while RX_DV de-asserted                                 | 22.2.2.2  | М      |         |                                                          |

| SF9  | RX_CLK max high/low time<br>following de-assertion of<br>RX_DV                     | 22.2.2.2  | М      |         | max 2 times the nominal period                           |

| SF10 | TX_EN assertion                                                                    | 22.2.2.3  | М      |         | On first nibble of preamble                              |

| SF11 | TX_EN remains asserted                                                             | 22.2.2.3  | М      |         | Stay asserted while all nibbles are transmitted over MII |

| SF12 | TX_EN transitions                                                                  | 22.2.2.3  | М      |         | Synchronous with TX_CLK                                  |

| SF13 | TX_EN negation                                                                     | 22.2.2.3  | М      |         | Before first TX_CLK after final nibble of frame          |

| SF14 | TXD<3:0> transitions                                                               | 22.2.2.4  | М      |         | Synchronous with TX_CLK                                  |

| SF15 | TXD<3:0> effect on PHY<br>while TX_EN is de-asserted                               | 22.2.2.4  | М      |         | No effect                                                |

| SF16 | TX_ER transitions                                                                  | 22.2.2.5  | М      |         | Synchronous with TX_CLK                                  |

| SF17 | TX_ER effect on PHY while<br>TX_EN is asserted                                     | 22.2.2.5  | М      |         | Cause PHY to emit invalid symbol                         |

| SF18 | TX_ER effect on PHY while<br>operating at 10 Mb/s, or when<br>TX_EN is de-asserted | 22.2.2.5  | М      |         | No effect on PHY                                         |

| Item | Feature                                                                       | Subclause | Status | Support | Value/Comment                                                            |

|------|-------------------------------------------------------------------------------|-----------|--------|---------|--------------------------------------------------------------------------|

| SF19 | TX_ER implementation                                                          | 22.2.2.5  | М      |         | At MII of a PHY                                                          |

| SF20 | TX_ER pulled down if not ac-<br>tively driven                                 | 22.2.2.5  | М      |         | At MII of a repeater or MAC/<br>RS only                                  |

| SF21 | RX_DV transitions                                                             | 22.2.2.6  | М      |         | Synchronous with RX_CLK                                                  |

| SF22 | RX_DV assertion                                                               | 22.2.2.6  | М      |         | From first recovered nibble to final nibble of a frame per figure 22-6   |

| SF23 | RX_DV negation                                                                | 22.2.2.6  | М      |         | Before the first RX_CLK fol-<br>lows the final nibble per<br>figure 22-6 |

| SF24 | RXD<3:0> effect on Reconcil-<br>iation sublayer while RX_DV<br>is de-asserted | 22.2.2.7  | М      |         | No effect                                                                |

| SF25 | RX_ER assertion                                                               | 22.2.2.8  | М      |         | By PHY to indicate error                                                 |

| SF26 | RX_ER transitions                                                             | 22.2.2.8  | М      |         | Synchronous with RX_CLK                                                  |

| SF27 | RX_ER effect on Reconcilia-<br>tion sublayer while RX_DV is<br>de-asserted    | 22.2.2.8  | М      |         | No effect                                                                |

| SF28 | CRS assertion                                                                 | 22.2.2.9  | М      |         | By PHY when either transmit<br>or receive is NON-IDLE                    |

| SF29 | CRS de-assertion                                                              | 22.2.2.9  | М      |         | By PHY when both transmit<br>and receive are IDLE                        |

| SF30 | CRS assertion during collision                                                | 22.2.2.9  | М      |         | Remain asserted throughout                                               |

| SF31 | COL assertion                                                                 | 22.2.2.10 | М      |         | By PHY upon detection of col-<br>lision on medium                        |

| SF32 | COL remains asserted while collision persists                                 | 22.2.2.10 | М      |         |                                                                          |

| SF33 | COL response to SQE                                                           | 22.2.2.10 | М      |         | Assertion by PHY                                                         |

| SF34 | MDC min high/low time                                                         | 22.2.2.11 | М      |         | 160 ns                                                                   |

| SF35 | MDC min period                                                                | 22.2.2.11 | М      |         | 400 ns                                                                   |

| SF36 | MDIO uses three-state drivers                                                 | 22.2.2.12 | М      |         |                                                                          |

| SF37 | PHY pullup on MDIO                                                            | 22.2.2.12 | М      |         | $1.5 \text{ k}\Omega \pm 5\% \text{ (to +5 V)}$                          |

| SF38 | STA pulldown on MDIO                                                          | 22.2.2.12 | М      |         | $2 \text{ k}\Omega \pm 5\%$ (to 0 V)                                     |

# 22.7.3.3 Frame structure

| Item | Feature                            | Subclause  | Status | Support | Value/Comment                                           |

|------|------------------------------------|------------|--------|---------|---------------------------------------------------------|

| FS1  | Format of transmitted frames       | 22.2.3     | М      |         | Per figure 22-10                                        |

| FS2  | Nibble transmission order          | 22.2.3     | М      |         | Per figure 22-11                                        |

| FS3  | Preamble 7 octets long             | 22.2.3.2.1 | М      |         | 10101010 10101010 10101010<br>10101010<br>10101010      |

| FS4  | Preamble and SFD transmis-<br>sion | 22.2.3.2.1 | М      |         | Per table 22-3                                          |

| FS5  | Preamble and SFD reception         | 22.2.3.2.2 | М      |         | Per table 22-4, table 22-5                              |

| FS6  | N octets transmitted as 2N nibbles | 22.2.3.3   | М      |         | Per figure 22-11                                        |

| FS7  | Indication of excess nibbles       | 22.2.3.5   | М      |         | Frame contains non-integer number of octets is received |

# 22.7.3.4 Management functions

| Item | Feature                                                  | Subclause  | Status | Support | Value/Comment                                                                                |

|------|----------------------------------------------------------|------------|--------|---------|----------------------------------------------------------------------------------------------|

| MF1  | Incorporate of basic register set                        | 22.2.4     | М      |         | Two 16-bit registers as Control<br>register (register 0) and Status<br>register (register 1) |

| MF2  | Action on reset                                          | 22.2.4.1.1 | М      |         | Reset the entire PHY including<br>Control and Status to default<br>value and $0.15 \le 1$    |

| MF3  | Return 1 until reset completed                           | 22.2.4.1.1 | М      |         | Yes (when reset is done, 0.15 is self clearing)                                              |

| MF4  | Reset completes within 0.5 s                             | 22.2.4.1.1 | М      |         |                                                                                              |

| MF5  | Loopback mode                                            | 22.2.4.1.2 | М      |         | Whenever 0.14 is 1                                                                           |

| MF6  | Receive circuitry isolated from network in loopback mode | 22.2.4.1.2 | М      |         |                                                                                              |

| MF7  | Effect of assertion of TX_EN in loopback mode            | 22.2.4.1.2 | М      |         | No transmission                                                                              |

| MF8  | Propagation of data in loop-<br>back mode                | 22.2.4.1.2 | М      |         | PHY accepts transmit data and return it as receive data                                      |

| MF9  | Delay from TX_EN to RX_DV<br>in loopback mode            | 22.2.4.1.2 | М      |         | Less than 512 BT                                                                             |

| MF10 | Behavior of COL in loopback mode                         | 22.2.4.1.2 | М      |         | De-asserted (for $0.7 = 0$ )                                                                 |

| MF11 | Behavior of COL in loopback mode                         | 22.2.4.1.2 | М      |         | If 0.7 = 1, see MF33 and MF34                                                                |

This is an Archive 1555 Standardser to has been superseded by a later version of this standard.