Approved for use through 01/31/2001. OMB 0651-0037

Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

### PROVISIONAL APPLICATION COVER SHEET

This is a request for filing a PROVISIONAL APPLICATION under 37 C.F.R. §1.53(c).

|                                                      |                                                            | Docket Number                                                                                               | 8011-7                                                     | Type a plus sign (+)<br>inside this box →                                                                                                                   | +             |               |

|------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|

| <del> </del>                                         |                                                            | INVE                                                                                                        | NTOR(s)/APPLIC                                             | ANT(s)                                                                                                                                                      |               |               |

| LAST NAME                                            | FIRST NAME                                                 | MIDDLE<br>INITIAL                                                                                           | RESIDENCE (C                                               | ITY AND EITHER STATE OR FORE                                                                                                                                | IGN COUNTRY)  | PTO           |

| Fallon<br>Buck<br>Pickel<br>McEerlain<br>Wolf-Sonkin | James<br>John<br>Paul<br>Stephen<br>Yury                   | J.<br>F.<br>J.                                                                                              | 362 Christop<br>225 Stewart /<br>325 East 17 <sup>th</sup> | ose, Armonk, New York 10504<br>her Street, Oceanside, New Yo<br>Avenue, Bethpage, New York 1<br>Street, New York, New York<br>int Road, Kings Point, New Yo | 1714<br>10003 | 60/18011      |

|                                                      |                                                            | TITLE OF THE                                                                                                | INVENTION (280                                             | characters max)                                                                                                                                             |               |               |

|                                                      |                                                            | DATA STORAG                                                                                                 | SE AND RETRIEVA                                            | L ACCELERATOR                                                                                                                                               |               |               |

|                                                      |                                                            | COR                                                                                                         | RESPONDENCE AD                                             | DRESS                                                                                                                                                       |               |               |

|                                                      |                                                            |                                                                                                             | HAU & ASSOCIATE<br>stead Turnpike                          |                                                                                                                                                             |               |               |

| STATE                                                | New York                                                   | ZIP CODE                                                                                                    | 11554                                                      | COUNTRY                                                                                                                                                     | USA           |               |

|                                                      |                                                            | ENCLOSED APPLICA                                                                                            | TION PARTS (che                                            | eck all that apply)                                                                                                                                         |               |               |

| ⊠ Specificat                                         | ion & Drawings                                             | Number of Pages                                                                                             | <u>108</u> §                                               | Small Entity Statement Other (specify)                                                                                                                      |               | <del></del> . |

|                                                      |                                                            | METHOD                                                                                                      | OF PAYMENT (ch                                             | eck one)                                                                                                                                                    |               |               |

| ☐ A check in is enclosed.                            | n the amount of \$                                         | <u>75.00</u> to cover the                                                                                   | e filing fee                                               | PROVISIONAL<br>FILING FEE<br>AMOUNT(S)                                                                                                                      |               |               |

| ☐ Charge fee<br>OF THIS SHEET                        |                                                            | nt Number 50-0679.                                                                                          | TWO COPIES                                                 | \$75.00                                                                                                                                                     |               |               |

| which may<br>at any tir<br>credit any                | become due under<br>me during the pend<br>overpayment of s | cy as well as any o<br>37 C.F.R. § 1.16<br>dency of this appli<br>such fee(s) to Depo<br>ES OF THIS SHEET A | and/or 1.17<br>cation, or<br>sit Account                   |                                                                                                                                                             |               |               |

CERTIFICATION UNDER 37 C.F.R. § 1.10

I hereby certify that this Provisional Application Cover Sheet and the documents referred to as enclosed therein are being deposited with the United States Postal Service on this date <u>February 3, 2000</u> in an envelope as "Express Mail Post Office to Addressee" Mail Label Number <u>EL433927955US</u> addressed to: Commissioner of Patents and Trademarks, Box Provisional Application, Washington, D.C. 20231.

Frank V. DeRosa

(Type or print name of person mailing paper)

(Signature of person mailing paper)

page 1 of 2

| The invention was made by an agency of the United States Government States Government. | ent or under a contract with an agency of the United |

|----------------------------------------------------------------------------------------|------------------------------------------------------|

| No.      □ Yes, the name of the U.S. Government agency and the Government              | nt contract number are:                              |

| Respectfully submitted,                                                                | •                                                    |

| SIGNATURE Trade                                                                        | Date 2/3/00                                          |

| TYPED or PRINTED NAME <u>Frank V. DeRosa</u>                                           | Registration No. 43,584 (if appropriate)             |

| Applicant or Palentee: Realtime Data, LLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Serial or Patent No.: 0 / Unassigned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Filed or Issued: Concurrently herewith                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| For: DATA STORAGE AND RETRIEVAL ACCELERATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VERIFIED STATEMENT CLAIMING SMALL ENTITY<br>STATUS (37 CFR 1.9(f) and 1.27(c)) - SMALL BUSINESS CONCERN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I hereby declare that I am                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ☐ the owner of the small business concern identified below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| an official of the small business concern empowered to act on behalf of the concern identified below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NAME OF SMALL BUSINESS CONCERN Realtime Data, LLC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ADDRESS OF SMALL BUSINESS CONCERN 206 East 63rd Street, New York, New York 10021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I hereby declare that the above identified small business concern qualifies as a small business concern as defined in 13 CFR 121.12, and reproduced in 37 CFR 1.9(d), for purposes of paying reduced fees to the United States Patent and Trademark Office under Section 41(a) and (b) of Title 35. United States Code, in that the number of employees of the concern, including those of its affiliates, does not exceed 500 persons. For purposes of this statement, (1) the number of employees of the business concern is the average over the previous fiscal year of the concern of the persons employed on a full-time, part-time or temporary basis during each of the pay periods of the fiscal year, and (2) concerns are affiliates of each other when either, directly or indirectly, one concern controls or has the power to control the other, or a third-party or parties controls or has the power to control both. |

| I hereby declare that rights under contract or law have been conveyed to, and remain with, the small business concern identified above, with regard to the invention described in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 🖾 the specification filed herewith.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| pplication serial no. 01, filed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| patent no, issued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| If the rights held by the above identified small business concern are not exclusive, each individual, concern or organization having rights in the invention is listed below* and no rights to the invention are held by any person, other than the inventor, who would not qualify as an independent inventor under 37 CPR 1.9(c) if that person made the invention, or by any concern which would not qualify as a small business concern under 37 CFR 1.9(d) or a nonprofit organization under 37 CFR 1.9(e).                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *NOTE: Separate verified statements are required from each named person, concern<br>or organization having rights to the invention averring to their status as small<br>entities, (37 CFR 1.27).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

(Small Entity-Small Business [7-4]-page 1 of 2)

|                                      | Each s                              | uch perso                           | n, concern or organization has                                    | ring any rights in the invention is listed below:                                                                                                                                                                        |                              |

|--------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                                      | 8                                   | No suci                             | i person, concern, or organiza                                    | tion exists.                                                                                                                                                                                                             | •                            |

|                                      | a                                   |                                     | ch person, concern or organiz                                     |                                                                                                                                                                                                                          |                              |

| PULL NA                              | AME.                                |                                     | <u> </u>                                                          |                                                                                                                                                                                                                          |                              |

|                                      |                                     |                                     |                                                                   |                                                                                                                                                                                                                          |                              |

| ADDRES                               | o ☐ Indi                            | viđusl                              | ☐ Small Business Concern                                          | □ Nouprofit Organization                                                                                                                                                                                                 |                              |

| FULL NA                              | AME                                 | ·                                   |                                                                   |                                                                                                                                                                                                                          |                              |

| ADDRES                               | S                                   |                                     |                                                                   |                                                                                                                                                                                                                          |                              |

| 1                                    | 🗆 Indivi                            | dual                                | ☐ Small Business Concern                                          | D Nonprofit Organization .                                                                                                                                                                                               |                              |

| information willful fall. Title 18 o | on and b<br>ise states<br>of the Us | elief are incres and<br>niced State | believed to be true; and further<br>the like so made are punishab | on knowledge are true and that all statements of that these statements were made with the knowle by fine or imprisonment, or both, under Sefalse statements may jeopardize the validity of rifled statement is directed. | wledge that<br>ction 1001 of |

| NAME O                               | F PERS                              | ON SIGI                             | NINO James J. 1                                                   | Fallon                                                                                                                                                                                                                   |                              |

| TITLEO                               | F PERS                              | on if $\sigma$                      | THER THAN OWNER                                                   | Chairman                                                                                                                                                                                                                 |                              |

| ADDRES                               | SS OF P                             | ERSON S                             | ·                                                                 | e. Annonk, New York 10504                                                                                                                                                                                                |                              |

|                                      |                                     |                                     | SIGNING 11 Wampus Clos                                            |                                                                                                                                                                                                                          |                              |

|                                      |                                     |                                     | ilGNING 11 Wamous Clos                                            |                                                                                                                                                                                                                          |                              |

# DATA STORAGE , AND RETRIEVAL ACCELERATOR

#### **PREFACE**

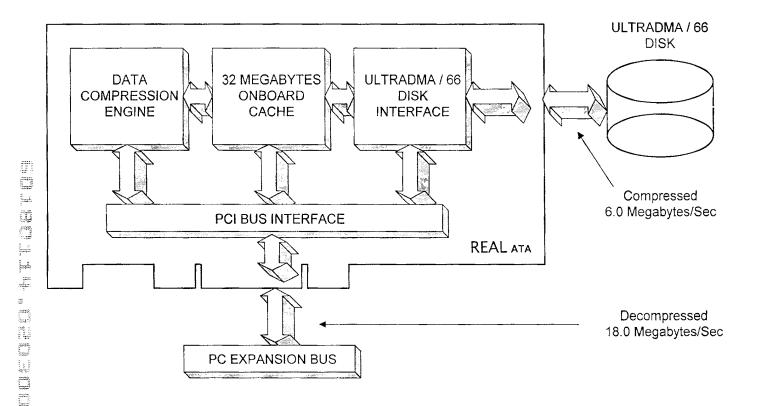

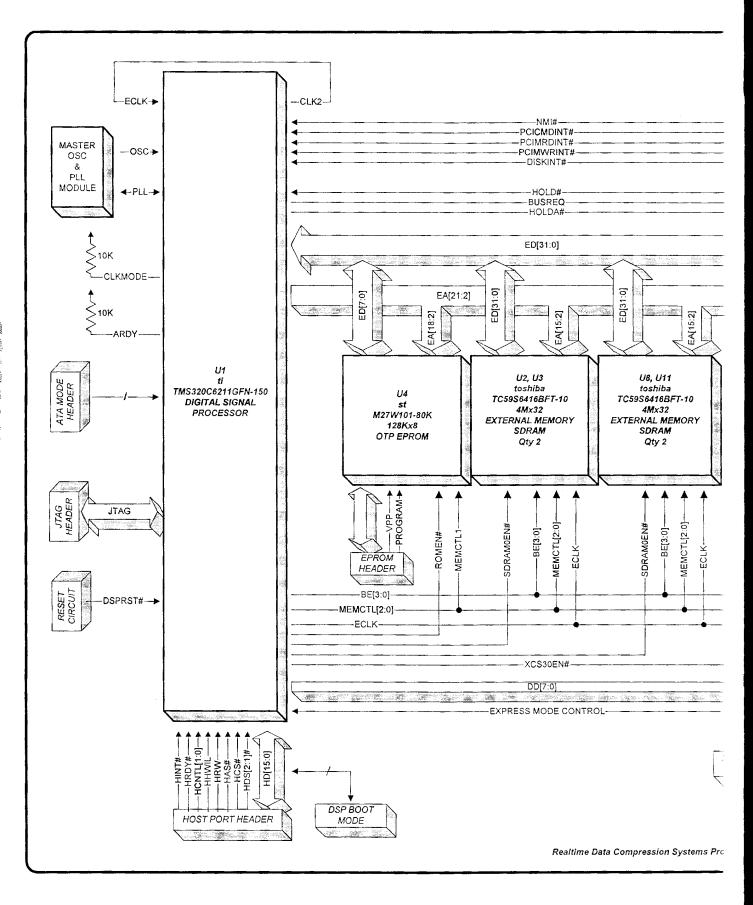

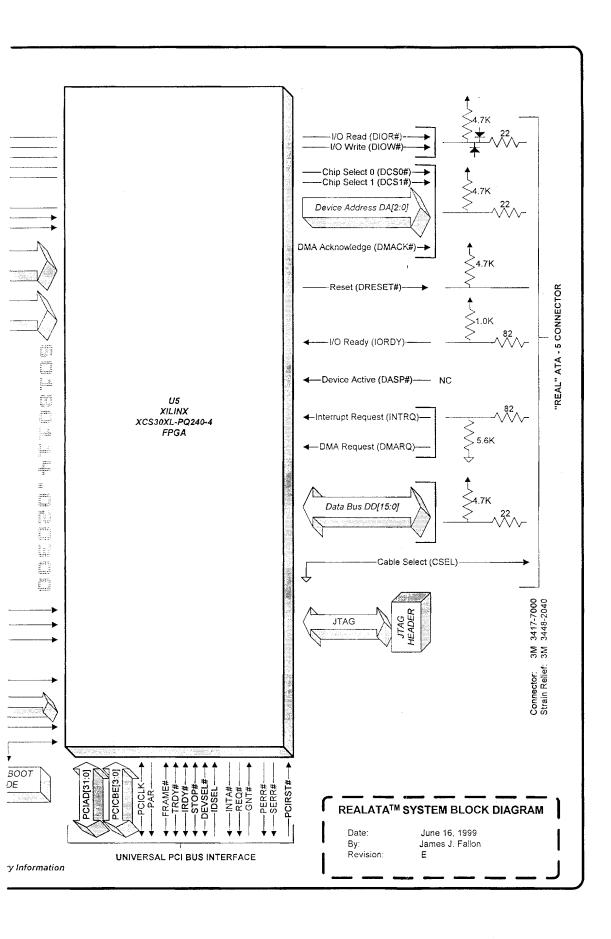

This manual describes the principles of operation, performance specifications, and detailed design of the Realtime Data, LLC UltraDMA Data Storage and Retrieval Accelerator (hereinafter affectionately referred to as the DSRA). This document begins with a brief introduction to fundamental performance limitations of current disk drives and the dramatic benefits provided by our DSRA. This is followed by a detailed DSRA performance specification. Next, a system overview is presented from a logical (not necessarily physical) functional partitioning with an emphasis on intrafunction dataflow and system level dynamic bandwidth allocation. A detailed block diagram is then presented and the function of each component is discussed in detail. Address maps are presented from the perspective of the onboard digital signal processor, disk controller, and PCI controller along with a view from the host PCI Bus. Available Interrupts and their allocation are discussed. Separate sections describe the internal architecture of the onboard field programmable gate array, programming the field programmable gate array, and the DSRA's reset and initialization methodology. Finally a software guide to the DSRA's command protocol is covered with a detailed specification of each DSRA command. Appendices list reference information including board component placement, a numerical listing of jumpers, external connectors for the UltraDMA disk interface and the PCI Bus, detailed schematics and a fully cross referenced parts list.

The DSRA is the represents Realtime's first product in our comprehensive family of data storage controllers, network data storage, and data centric secure networking. Our technology represents the next logical step in the evolution of high performance data storage and completely secure high bandwidth data transmission. Employing industry standard interfaces and protocols that seamlessly integrate with existing media devices, our product offers a many-fold increase in data storage density, access speed, and security. This approach overcomes the traditional bottlenecks associated with local and network disk data accesses. In order to achieve this level of performance our proprietary data compression and encryption engine reads one byte of data stored on disk and decodes this information into multiple bytes of information for the computer. By implementing this process in a combination of dedicated hardware and an ultra high speed digital signal processor the translation takes place in "real-time". Thus, rather than the traditional delays normally associated with software data compression, our hardware approach creates a many-fold performance improvement. Our technology is designed to be Scalable through each successive computer generation; Adaptable to serve multiple functions concurrently, increasing performance and enhancing value; *Insertable* to seamlessly integrate into existing marketplaces – modifications to existing standards are not required. Our Value Proposition is Product Excellence through Innovation. Our technology creates the state-of-the-art; is easy to install and use, and is flawlessly reliable.

#### **NOTATIONAL CONVENTIONS**

This manual utilizes the following conventions and nomenclature:

#### **Register Diagrams**

Register diagrams are presented as follows:

External Interrupt Polarity Register

| 31       | 4 | 3     | 2      | 1      | 0      |

|----------|---|-------|--------|--------|--------|

| Reserved |   | XIP7  | XIP6   | XIP5   | XIP4   |

| R, +0    |   | R, +0 | RW, +0 | RW, +0 | RW, +0 |

All register diagrams, unless otherwise noted, utilize the following notational conventions:

Each rectangle represents a logically related group of bits called a bit field.

Mnemonics for each field name is given within the rectangle.

Numbers directly above the bit field represent starting and ending bit locations (inclusive).

Properties are listed directly below each bit field.

R = Readable by the DSP's CPU

W = Writeable by the DSP's CPU

+x = Value undefined after DSP reset

+0 = Value is 0 after DSP reset

+1 = Value is 1 after DSP reset

C = Clearable by the DSP's CPU

#### **Software Notation**

Program Listings are in courier font

LDW .D1 \*A0,A1 ADD .L1 A1,A2,A3

All data is presented and utilized in little endian notation.

In syntax descriptions, the command is in **bold face**, and parameters are in italics. Portions of a syntax that are in **bold** should be entered as shown; portions of a syntax that are in italics describe the type of information that should be entered. Here is an example of a command syntax:

#### **READ DISK DATA**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                      | 16     | 15         | 8                | 7     | 0                          |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------|------------|------------------|-------|----------------------------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Command Packet Number<br>0000h to FFFFh | ••••   | Comr       | nand Type<br>00h | -     | ommand 001<br>neters (00h) | h  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Starting Block A                        | ddres. | s (Least L | Significant W    | Vord) | 041                        | h  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Starting Block A                        | ddres  | s (Most S  | Significant W    | ord)  | 081                        | h  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Number of Blo                           | ocks ( | Least Sig  | nificant Wor     | ·d)   | 0C                         | 'h |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Number of Blo                           | ocks ( | Most Sig   | nificant Wor     | ·d)   | 101                        | h  |

| The second secon | Destination Ad                          | dress  | (Least Si  | ignificant We    | ord)  | 14                         | h  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Destination Ad                          | dress  | (Most Si   | gnificant Wo     | ord)  | 181                        | h  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | [Checksum]                              |        |            | Res              | erved | 1C                         | 'h |

Square brackets ([and]) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets; you do not enter the brackets themselves. When there is a choice amongst multiple items they are separated by a |, for example a | b is a selection of either a or b, but not both.

#### **Hardware Notation**

DSRA busses and integrated circuit pins often are represented in groups. Device pin group notation consists of the pin name followed by brackets containing the range of pins included in the group. A colon separates the numbers in the range. For example, ED[31:0] represents the 32 bit DSP external data bus.

#### **Caution Statements**

A caution statement describes a situation that could potentially damage the DSRA, host computer, or software.

#### **Warning Statements**

A warning statement describes a situation that could potentially cause you injury or death.

Caution and Warning Statements are provided for your protection. Please read each caution and warning carefully.

# **REALTIME DATA, LLC**

UltraDMA/66 Data Storage & Retrieval Accelerator

### **TABLE OF CONTENTS**

| _                     | Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Title   | Page |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

|                       | 1.0 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | 8    |

|                       | 2.0 PERFORMANCE SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | 10   |

|                       | 3.0 SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | 11   |

| adan<br>nanii<br>adik | 4.0 DETAILED BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |      |

| esti.                 | 4.1 Master Oscinator 4.2 Digital Signal Processor 4.2 Digital Signal Processor 4.2 Digital Signal Processor 4.1 Master Oscinator 4.2 Digital Signal Processor 4.2 Digital Signa |         |      |

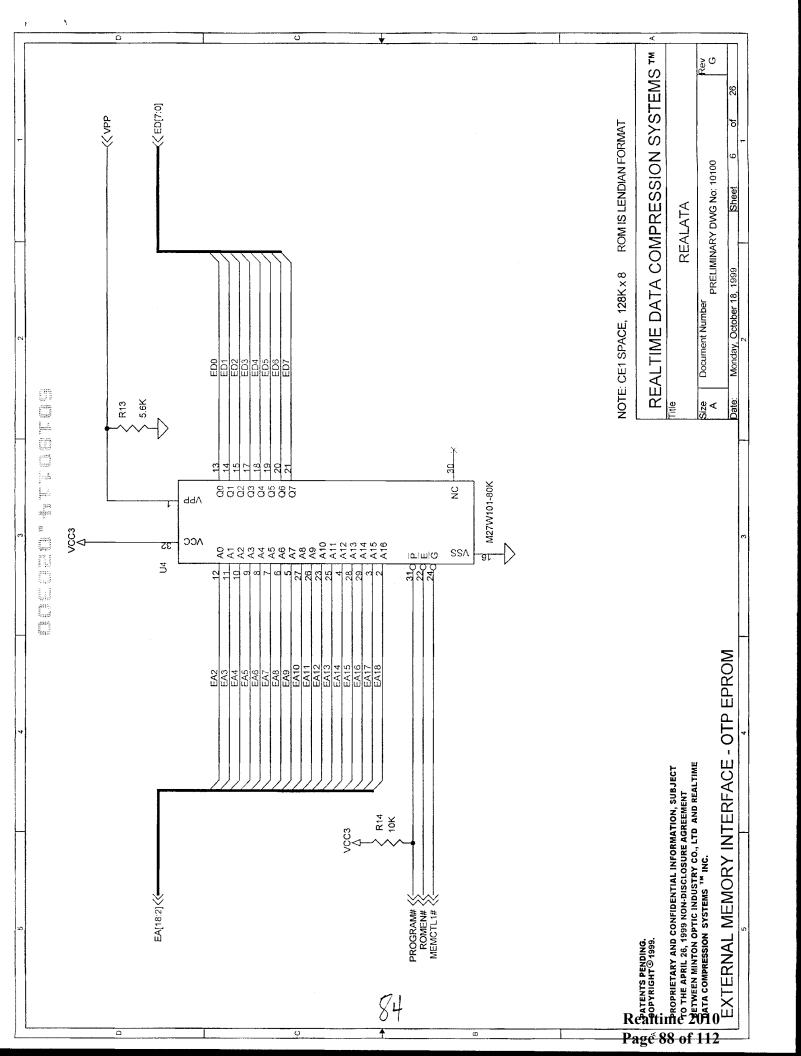

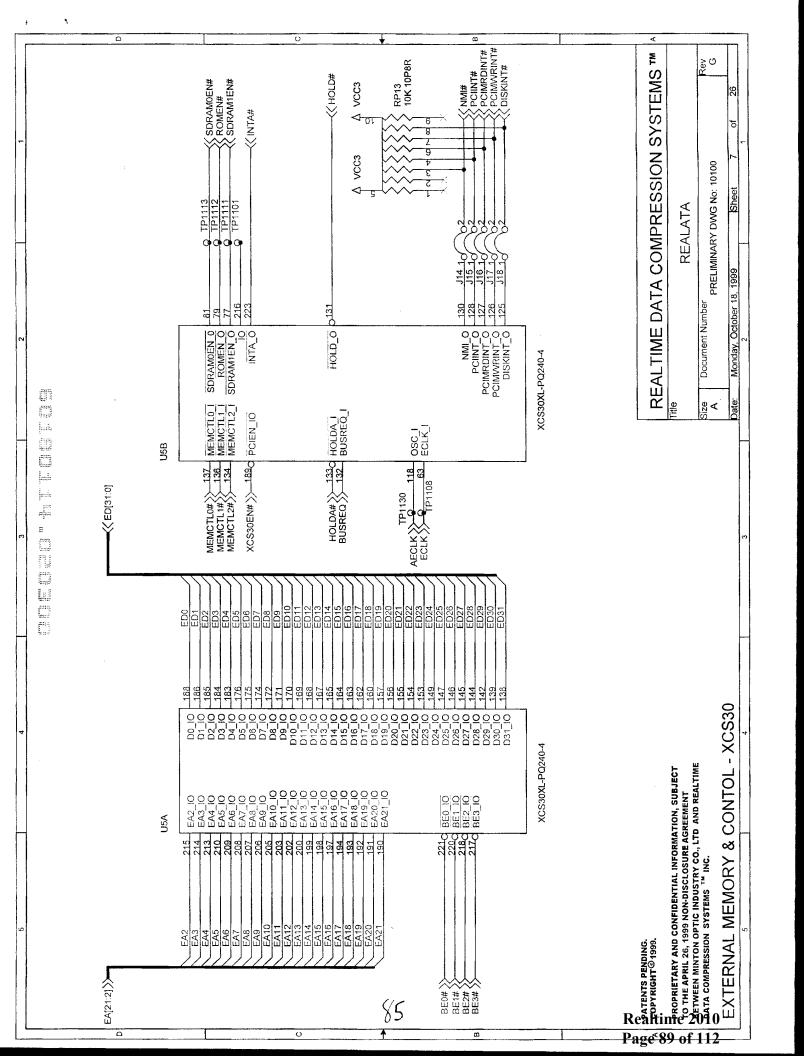

|                       | 4.3 OTP EPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |      |

| 5470,                 | 4.4 SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |      |

|                       | 5.0 MEMORY MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | 17   |