## United States Patent [19]

#### Horiguchi et al.

Patent Number: [11]

5,265,055

Date of Patent: [45]

Nov. 23, 1993

#### SEMICONDUCTOR MEMORY HAVING REDUNDANCY CIRCUIT

[75] Inventors: Masashi Horiguchi, Kawasaki; Jun

Etoh, Hachioji; Masakazu Aoki, Tokorozawa; Kiyoo Itoh,

Higashikurume, all of Japan

[73] Assignee: Hitachi, Ltd., Tokyo, Japan

[21] Appl. No.: 818,434

[22] Filed: Dec. 27, 1991

### Related U.S. Application Data

[63] Continuation of Ser. No. 419,399, Oct. 10, 1989, abandoned.

| [30] | Foreign Application Priority Data |

|------|-----------------------------------|

|      | ct. 7, 1988 [JP] Japan            |

|      | Int. Cl. <sup>5</sup>             |

| [58] | Field of Search                   |

| [56] | References Cited                  |

#### References Cited

#### U.S. PATENT DOCUMENTS

| 4,389,715 | 6/1983 | Eaton, Jr. et al<br>Segawa et al | 371/10.3 |

|-----------|--------|----------------------------------|----------|

| 4,675,895 | 6/1989 | Itoh et al                       | 365/51   |

|           |        | Yoshida et al                    |          |

| 4,837,747 | 6/1989 | Dosaka et al                     | 365/200  |

#### FOREIGN PATENT DOCUMENTS

130139 11/1985 Japan .

#### OTHER PUBLICATIONS

Edmond A. Reese et al., "A 4K×8 Dynamic RAM with Self-Refresh", IEEE Journal or Solid State Circuits, vol. SC-16, No. 5 Oct. 1981 pp. 479-487. Itoh et al., "High-Density One-Device Dynamic MOS

Memory Cells", IEE Proc., vol. 130, Pt. I, No. 3 Jun. 1983 pp. 127-135.

Itoh et al., "An Experimental 1 Mb DRAM with On-Chip Voltage Limiter", IEEE International Solid-State Circuits Conference, Digest of Technical papers, 1984 pp. 282-283.

Primary Examiner-Joseph L. Dixon Assistant Examiner-Jack A. Lane Attorney, Agent, or Firm-Antonelli, Terry Stout & Kraus

#### [57] ABSTRACT

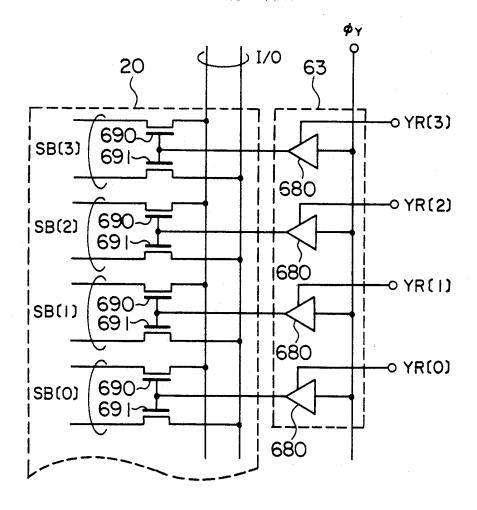

A redundancy technique is introduced for a semiconductor memory and, more particularly a redundancy technique for a dynamic random access memory (DRAM) having a storage capacity of 16 mega bits or more. In such a DRAM, the efficiency of the redundancy technique is reduced, since a memory array is divided into a large number of memory mats. According to the present redundancy technique, in a semiconductor memory including a memory array which has a plurality of word lines, a plurality of bit lines arranged so that two-level crossings are formed between the word lines and the bit lines, and memory cells disposed at desired ones of the two-level crossings, there is provided, furthermore, a plurality of spare word (or bit) lines, address comparing circuits for storing therein a defective address existing in the memory array, to compare an address to be accessed with the defective address, and selection circuitry for replacing a word or bit line including a defective memory cell by a spare word (or bit) line in accordance with the result of the comparison. The memory array of the semiconductor memory is divided into M memory mats (where  $M \ge 2$ ), the number m of word or bit lines which are simultaneously replaced by spare word (or bit) lines, is less than the number M and equal to a divisor thereof, and the number L of spare word (or bit) lines per one memory mat and the number R of address comparing circuits satisfy a relation  $L < R \le LM/m$  and, preferably, L < -R < LM/m.

#### 12 Claims, 34 Drawing Sheets

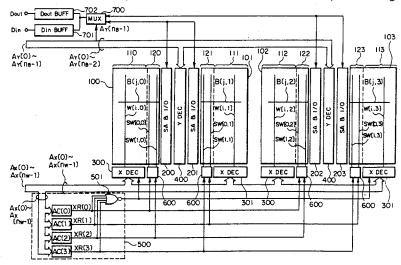

FIG. 1B PRIOR ART

Nov. 23, 1993

5,265,055

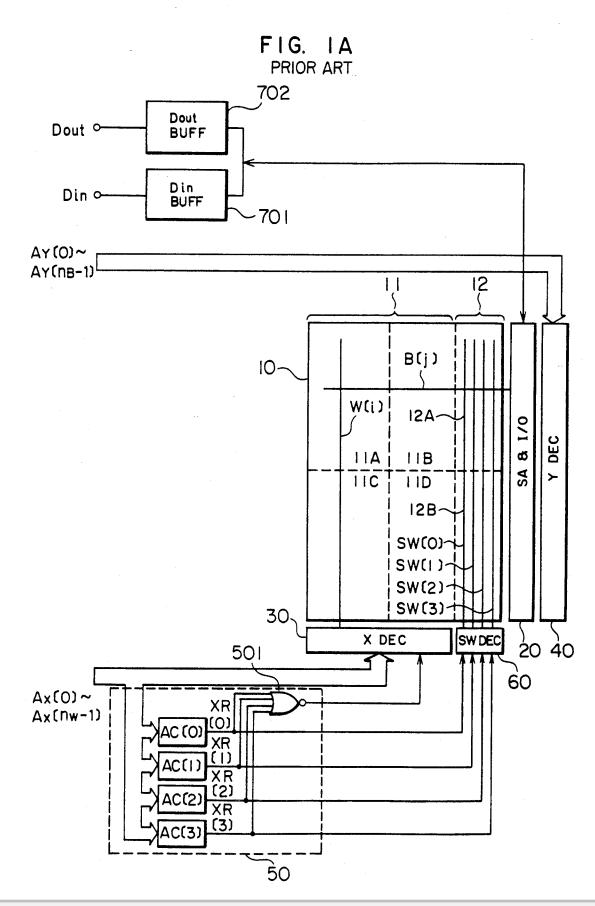

FIG. 2B PRIOR ART

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.