# Apple Inc. v. Realtime Data, LLC d/b/a/ IXO Cases IPR2016-01365, -01366

# Table of Contents

| "preloading the boot data into a cache memory"                                      |

|-------------------------------------------------------------------------------------|

| "preloadingprior to completion of initialization of<br>the central processing unit" |

| '963 Patent's Claim 1889                                                            |

| "preloading boot data, in compressed formfrom a boot device into a cache memory"    |

| "a plurality of encoders are utilized to provide the compressed boot data"          |

# "preloading the boot data into a cache memory"

# (12) United States Patent

## Fallon et al.

- (54) SYSTEMS AND METHODS FOR ACCELERATED LOADING OF OPERATING SYSTEMS AND APPLICATION PROGRAMS

- (75) Inventors: James J. Fallon, Armonk, NY (US); John Buck, Oceanside, NY (US): Paul F. Pickel, Bethpage, NY (US); Stephen J. McEerlain, New York, NY (US)

- (73) Assignce: Realtime Data LLC, New York, NY (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 223 days.

- (21) Appl. No.: 09/776,267

- (22) Filed: Feb. 2, 2001

- (65) Prior Publication Data

US 2002/0069354 A1 Jun. 6, 2002

#### Related U.S. Application Data

- (60) Provisional application No. 50/180,114, filed on Feb. 3, 2000.

- (51) Int. Cl. G06F 9/24 (2006.01) G06F 9/00 (2006.01)

|      | G06F 13/00 | (2006.01)             |

|------|------------|-----------------------|

| (52) | U.S. CL    | 713/2: 713/1: 711/113 |

(58) Field of Classification Search 713/2, 713/1, 100; 711/170, 118, 113

See application tile for complete search history

(56) References Cited

#### U.S. PATENT DOCUMENTS

4,127,518 A 11/1978 Coy et al.

# (10) Patent No.: US 7,181,608 B2 (45) Date of Patent: Feb. 20, 2007

4,302,775 A 11(1981 Widesgree et al. 4,394,774 A 7/1983 Widesgree et al. 4,574,351 A 3/1986 Dang et al.

(Continued)

#### FOREIGN PATENT DOCUMENTS

## 4127518 Al 2/1992 (Continued)

OTHER PUBLICATIONS

IBM, Fast Dos Soft Boot, Feb. 1, 1994, vol. 37, Isaue 2B, pp 185-186.\*

#### (Continued)

Primary Examiner—Thomas Lee Assistant Examiner—Suresh K Suryawanshi (74) Attorney, Agent. or Firm—Fish & Neave IP Group of Ropes & Gray LLP

(57) ABSTRACT

DE

Systems and methods are provided for accelerated loading of operating system and application programs upon system boot or application launch. In one aspect, a method for providing accelerated loading of an operating system includes maintaining a list of boot data used for booting a computer system, preloading the boot data upon initialization of the computer system, and servicing requests for boot data from the computer system using the preloaded boot data. The boot data may comprise program code associated with an operating system of the computer system, an application program, and a combination thereof. The boot data is retrieved from a boot device and stored in a cache memory device. The boot data is stored in a compressed format on the boot device and the preloaded boot data is decompressed prior to transmitting the preloaded boot data to the requesting system.

31 Claims, 13 Drawing Sheets

APPLE 1001

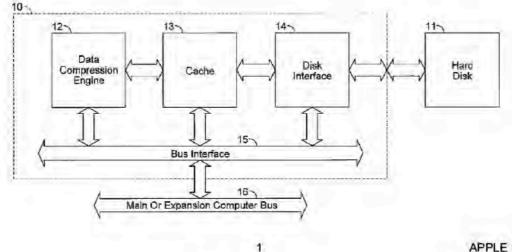

set of decoders, or a sequential set of decoders corresponding to the extracted compression type descriptor. The decoders D1 . . . Dn may include those lossless encoding techniques currently well known within the art, including: run length, Huffman, Lempel-Ziv Dictionary Compression, arithmetic coding, data compaction, and data null suppression. Decoding techniques are selected based upon their ability to effectively decode the various different types of encoded input data generated by the data compression systems described above or originating from any other 10 desired source.

27

As with the data compression systems discussed in U.S. Pat. No. 6,195,024, the decoder module 165 may include multiple decoders of the same type applied in parallel so as to reduce the data decoding time. An output data buffer or 15 cache 170 may be included for buffering the decoded data block output from the decoder module 165. The output buffer 70 then provides data to the output data stream. It is to be appreciated by those skilled in the art that the data compression system 180 may also include an input data 20 counter and output data counter operatively counled to the input and output, respectively, of the decoder module 165. In this manner, the compressed and corresponding decompressed data block may be counted to ensure that sufficient decompression is obtained for the input data block. 25

Again, it is to be understood that the embodiment of the data decompression system 180 of FIG. 10 is exemplary of a preferred decompression system and method which may be implemented in the present invention, and that other data decompression systems and methods known to those skilled in the art may be employed for providing accelerated data retrieval in accordance with the teachings herein.

Although illustrative embodiments have been described herein with reference to the accompanying drawings, it is to be understood that the present invention is not limited to 35 those precise embodiments, and that various other changes and modifications may be affected therein by one skilled in the art without departing from the scope or spirit of the invention. All such changes and modifications are intended to be included within the scope of the invention as defined 40 by the appended claims.

What is claimed is:

1. A method for providing accelerated loading of an operating system, comprising the steps of:

maintaining a list of boot data used for booting a computer 45 system;

initializing a central processing unit of the computer system:

preloading the boot data into a cache memory prior to completion of initialization of the central processing 50 unit of the computer system, wherein preloading the boot data comprises accessing compressed boot data from a boot device: and

servicing requests for boot data from the computer system using the preloaded boot data after completion of 55 initialization of the central processing unit of the computer system, wherein servicing requests comprises accessing compressed boot data from the cache and decompressing the compressed boot data at a rate that increases the effective access rate of the cache.

2. The method of claim 1, wherein the boot data comprises program code associated with one of an operating system of the computer system, an application program, and a combination thereof.

3. The method of claim 1, wherein the preloading is 65 performed by a data storage controller connected to the boot device.

#### 28

4. The method of claim 1, further comprising updating the list of boot data

5. The method of claim 4, wherein the step of updating comprises adding to the list any boot data requested by the computer system not previously stored in the list.

6. The method of claim 4, wherein the step of updating comprises removing from the list any boot data previously stored in the list and not requested by the computer system. 7. A system for providing accelerated loading of an

operating system of a host system comprising: a digital signal processor (DSP) or controller; a cache memory device; and

a non-volatile memory device, for storing logic code associated with the DSP or controller, wherein the logic code comprises instructions executable by the DSP or controller for maintaining a list of boot data used for booting the host system, for preloading the compressed boot data into the cache memory device prior to

completion of initialization of the central processing unit of the host system, and for decompressing the preloaded compressed boot data, at a rate that increases the effective access rate of the cache, to service requests for boot data from the host system after completion of initialization of the central processing unit of the host system.

8. The system of claim 7, wherein the logic code in the non-volatile memory device further comprises program instructions executable by the DSP or controller for maintaining a list of application data associated with an application program; preloading the application data upon launching the application program, and servicing requests for the application data from the host system using the preloaded application data.

9. The method of claim 1, further comprising:

maintaining a list of application data associated with an application program;

- preloading the application data into the cache memory prior to completion of initialization of the central processing unit of the computer system, wherein preloading the application data comprises accessing compressed application data from a boot device; and

- servicing requests for application data from the computer system using the preloaded application data after completion of initialization of the central processing unit of the computer system, wherein servicing requests comprises accessing compressed application data from the cache and decompressing the compressed application data

10. The method of claim 1, further comprising a data compression engine for compressing, wherein the compressing provides the compressed boot data and the data compression engine provides the compressed boot data to the boot device.

11. The method of claim 1, wherein the decompressing is provided by a data compression engine.

12. The method of claim 1, further comprising a data compression engine for compressing, wherein the compressing provides the compressed boot data, the data compression engine provides the compressed boot data to the boot device, 60 and the decompressing is provided by the data compression engine.

13. The method of claim 1, wherein the compressed boot data is accessed via direct memory access.

14. The method of claim 1, wherein Huffman encoding is utilized to provide the compressed boot data.

15. The method of claim 1, wherein Lempel-Ziv encoding is utilized to provide the compressed boot data.

by the appended claims.

What is claimed is:

1. A method for providing accelerated loading of an operating system, comprising the steps of:

- maintaining a list of boot data used for booting a computer 45 system;

- initializing a central processing unit of the computer system;

- preloading the boot data into a cache memory prior to completion of initialization of the central processing 50 unit of the computer system, wherein preloading the boot data comprises accessing compressed boot data from a boot device; and

- servicing requests for boot data from the computer system using the preloaded boot data after completion of 55 j initialization of the central processing unit of the computer system, wherein servicing requests comprises

| pression          | 7. A system for providing accelerated loading of an         |

|-------------------|-------------------------------------------------------------|

| y other 10        | operating system of a host system comprising:               |

|                   | a digital signal processor (DSP) or controller;             |

| in U.S.           | a cache memory device; and                                  |

| include           | a non-volatile memory device, for storing logic code        |

| lel so as         | associated with the DSP or controller, wherein the logic    |

| uffer or 15       | code comprises instructions executable by the DSP or        |

| led data          | controller for maintaining a list of boot data used for     |

| output            | booting the host system, for preloading the compressed      |

| am. It is         | boot data into the cache memory device prior to             |

| the data          | completion of initialization of the central processing      |

| out data 20       | unit of the host system, and for decompressing the          |

| d to the          | preloaded compressed boot data, at a rate that increases    |

| : <b>165</b> . In | the effective access rate of the cache, to service requests |

| decom-            | for boot data from the host system after completion of      |

| ufficient         | initialization of the central processing unit of the host   |

| . 25              | system.                                                     |

| ut of the         | 8. The system of claim 7, wherein the logic code in the     |

|                   | 7                                                           |

# (12) United States Patent Fallon et al. (54) SYSTEMS AND METHODS FOR ACCELERATED LOADING OF OPERATING SYSTEMS AND APPLICATION PROGRAMS

- (75) Inventors: James J. Fallon, Armonk, NY (US); John Buck, Oceanside, NY (US); Paul F. Pickel, Bethpage, NY (US); Stephen J. McErlain, New York, NY (US)

- (73) Assignee: Realtime Data, LLC, Armonk, NY (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 286 days.

This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 11/551,204

- (22) Filed: Oct. 19, 2006

- (65) Prior Publication Data

US 2007/0083746 A1 Apr. 12, 2007

#### **Related U.S. Application Data**

- (63) Continuation of application No. 09/776,267, filed on Feb. 2, 2001, now Pat. No. 7,181,608.

- (60) Provisional application No. 60/180,114, filed on Feb. 3, 2000.

- (51) Int. Cl. *G06F 9/00* (2006.01) *G06F 9/24* (2006.01) *G06F 13/28* (2006.01)

- U.S. Cl. 713/2; 713/1; 711/113

Field of Classification Search 713/2 See application file for complete search history.

- (56) References Cited

# U.S. PATENT DOCUMENTS

3,394,352 A 7/1968 Wernikoll et al.

# US008090936B2

# (10) Patent No.: US 8,090,936 B2 (45) Date of Patent: \*Jan. 3, 2012

| 3.490.690 A | 1/1970  | Apple et al.     |

|-------------|---------|------------------|

| 4.021.782 A |         | Hoerning         |

| 4.032.893 A | 6/1977  |                  |

| 4.054.951 A | 10/1977 | Jackson et al.   |

| 4.127.518 A | 11/1978 | Coy et al.       |

| 4,302,775 A |         | Widergren et al. |

|             | (Con    | tinued)          |

DE

(57)

#### FOREIGN PATENT DOCUMENTS 4127518 2/1992 (Continued)

#### OTHER PUBLICATIONS

Millman, Howard, "Image and video compression", Computerworld, vol. 33, Issue No. 3, Jan. 18, 1999, pp. 78.

(Continued)

Primary Examiner — Suresh K Suryawanshi (74) Attorney, Agent, or Firm — Sterne, Kessler, Goldstein & Fox P.L.L.C.

#### ABSTRACT

Systems and methods are disclosed for providing accelerated loading of operating system and application programs. In one aspect, a method for providing accelerated loading of an operating system comprises the steps of: maintaining a list of boot data; preloading the boot data upon initialization of the computer system; and servicing requests for boot data from the computer system using the preloaded boot data. In a preferred embodiment, the boot data is retrieved from a boot device and stored in a cache memory device. In another aspect, a method for accelerated loading of an operating system comprises updating the list of boot data during the boot process, wherein updating comprises adding to the list any boot data requested by the computer system not previously stored in the list and/or removing from the list any boot data previously stored in the list and not requested by the computer system.

24 Claims, 13 Drawing Sheets

APPLE 1001

5

such changes and modifications are intended to be included within the scope of the invention as defined by the appended claims.

27

What is claimed is:

1. A method comprising:

maintaining a list of boot data used for booting a computer system, wherein at least a portion of said boot data is compressed by a data compression engine to provide said at least a portion of said boot data in compressed 10 form, and stored in compressed form on a boot device;

initializing a central processing unit of said computer system; preloading said at least a portion of said boot data in com-

pressed form from said boot device to a memory;

accessing and decompressing said at least a portion of said boot data in said compressed form from said memory; and

utilizing said decompressed at least a portion of said boot data to boot said computer system, wherein said at least 20 a portion of said boot data is decompressed by said data compression engine.

**2**. The method of claim **1**, wherein said decompressed at least a portion of said boot data comprises program code associated with an operating system of said computer system. <sup>25</sup>

**3**. The method of claim **1**, wherein said decompressed at least a portion of said boot data comprises program code associated with an application program of said computer system.

4. The method of claim 1, wherein said decompressed at 30 least a portion of said boot data comprises program code associated with an application program and an operating system of said computer system.

**5**. The method of claim **1**, wherein said preloading is performed by a data storage controller connected to said boot 35 device.

6. The method of claim 1, further comprising updating the list of boot data.

**7**. The method of claim **1**, wherein Huffman encoding is utilized to provide said at least a portion of said boot data in 40 said compressed form.

8. The method of claim 1, wherein Lempel-Ziv encoding is utilized to provide said at least a portion of said boot data in said compressed form.

**9**. The method of claim **1**, wherein a plurality of encoders 45 are utilized to provide said at least a portion of compressed data in compressed form.

**10**. The method of claim **1**, wherein a plurality of encoders in a parallel configuration are utilized to provide said at least a portion of said data in compressed form. 50

a portion of said data in compressed form. 11. A system comprising:

a processor:

a memory; and

nemory, and

a non-volatile memory device for storing logic code associated with the processor, wherein said logic code comprises instructions executable by the processor for maintaining a list of boot data used for booting the host system, at least a portion of said boot data is stored in compressed form in said non-volatile memory device, said at least a portion of said boot data in compressed form is preloaded into said memory, and said preloaded at least a portion of boot data in compressed form is decompressed and utilized to boot said computer system; and a data compression engine for providing said at least a portion of said boot data in compressed form by compressing said at least a portion of said boot data and decompressing said at least a portion of said boot data in compressed form to provide said decompressed at least a portion of boot data.

12. The system of claim 11, wherein said logic code further comprises program instructions executable by said processor for maintaining a list of application data associated with an application program.

13. The system of claim 11, wherein said logic code further comprises program instructions executable by said processor for maintaining a list of application data associated with an application program, and wherein said application data is preloaded upon launching the application program and utilized by said computer system.

14. The system of claim 11, wherein Huffman encoding is utilized to provide said at least a portion of said boot data in compressed form.

15. The system of claim 11, wherein Lempel-Ziv encoding is utilized to provide said at least a portion of said boot data in compressed form.

16. The system of claim 11, wherein a plurality of encoders are utilized to provide said at least a portion of said boot data in compressed form.

17. The system of claim 11, wherein a plurality of encoders in a parallel configuration are utilized to provide said at least a portion of said boot data in compressed form.

18. A method of preloading an operating system for booting a computer system comprising:

storing substantially all of the operating system in compressed form on a boot device;

preloading a first portion of the substantially all of the

operating system from said boot device to a memory; accessing and decompressing the first portion from the memory using a data compression engine;

utilizing the decompressed first portion to partially boot said computer system;

responsive to a request, locating a second portion of the substantially all of the operating system using a boot data list and preloading the second portion from the boot device to the memory;

accessing and decompressing the second portion from the memory using the data compression engine; and

utilizing the decompressed second portion to further partially boot said computer system.

**19**. The method of claim **18**, wherein the preloading is performed by a data storage controller connected to the boot device.

**20**. The method of claim **18**, further comprising updating the boot data list.

**21**. The method of claim **18**, wherein Huffman encoding is utilized to obtain the substantially all of the operating system in compressed form.

22. The method of claim 18, wherein Lempel-Ziv encoding is utilized to obtain the substantially all of the operating system in compressed form.

23. The method of claim 18, wherein a plurality of encoders are utilized to obtain the substantially all of the operating system in compressed form.

**24**. The method of claim **18**, wherein a plurality of encoders in a parallel configuration are utilized to obtain the substantially all of the operating system in compressed form.

\* \* \* \* \*

rogram code iid computer

ompressed at 30 rogram code perating sys-

bading is perto said boot 35

updating the

1 encoding is 1 boot data in 40

v encoding is 1 boot data in

y of encoders 45 f compressed a portion of said boot data in compressed form.

**18**. A method of preloading an operating system for booting a computer system comprising:

storing substantially all of the operating system in compressed form on a boot device;

preloading a first portion of the substantially all of the operating system from said boot device to a memory;

accessing and decompressing the first portion from the memory using a data compression engine;

utilizing the decompressed first portion to partially boot said computer system;

responsive to a request, locating a second portion of the substantially all of the operating system using a boot data list and preloading the second portion from the boot device to the memory;

accessing and decompressing the second portion from the memory using the data compression engine; and

utilizing the decompressed second portion to further partially boot said computer system.

19. The method of claim 18, wherein the preloading is

norformed by a data storage controller connected to the best

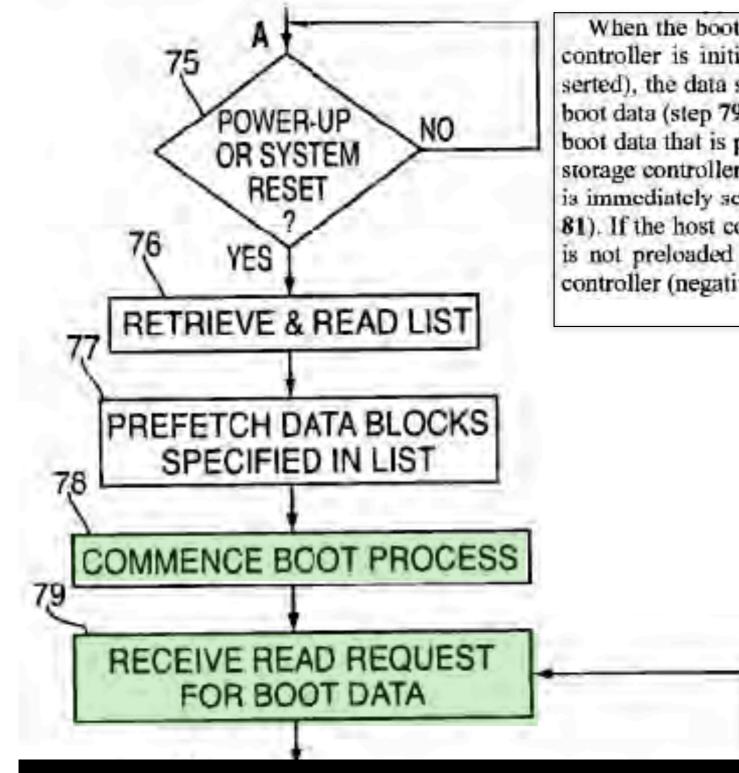

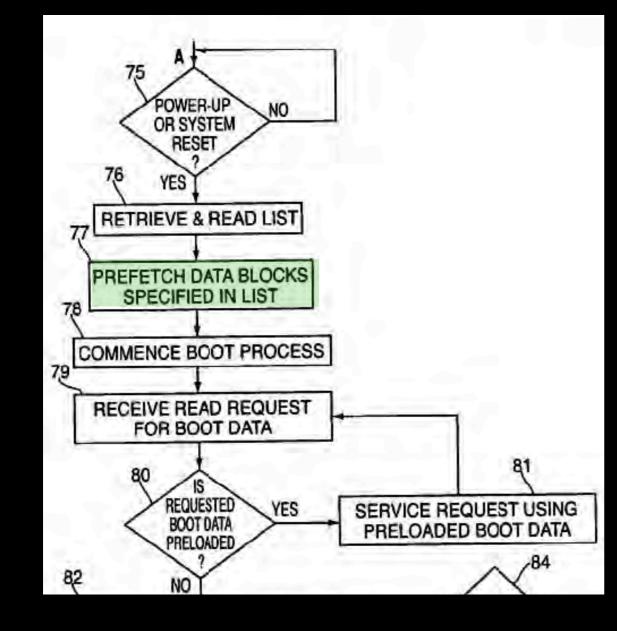

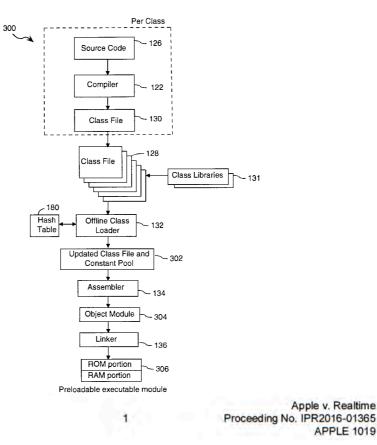

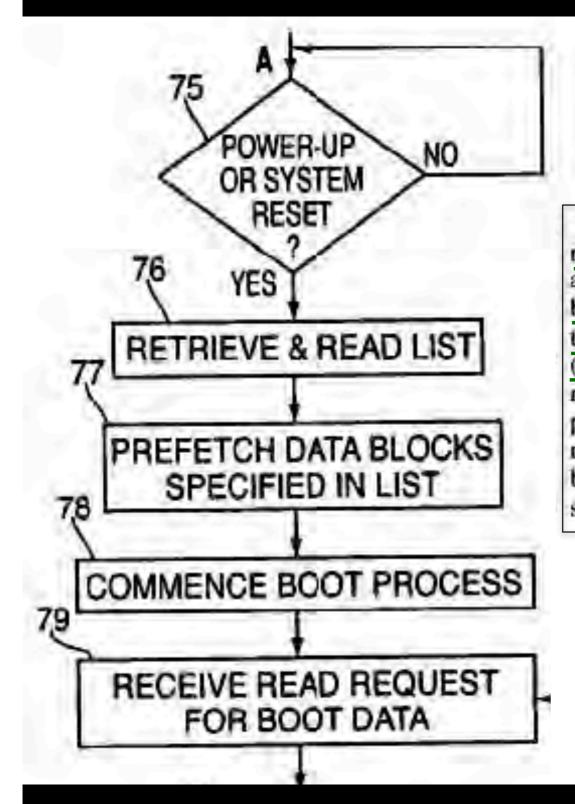

FIG. 7a

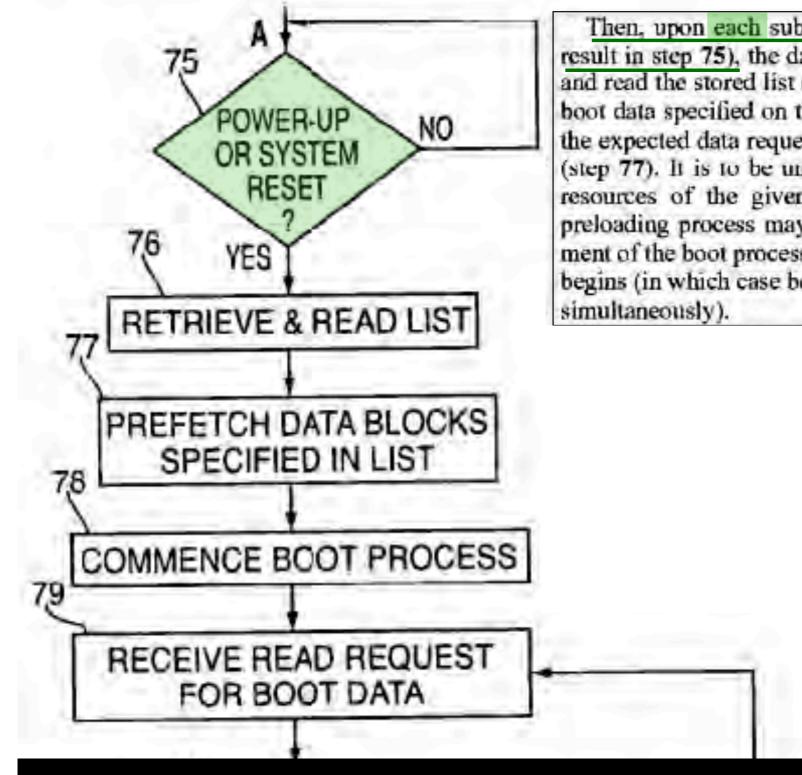

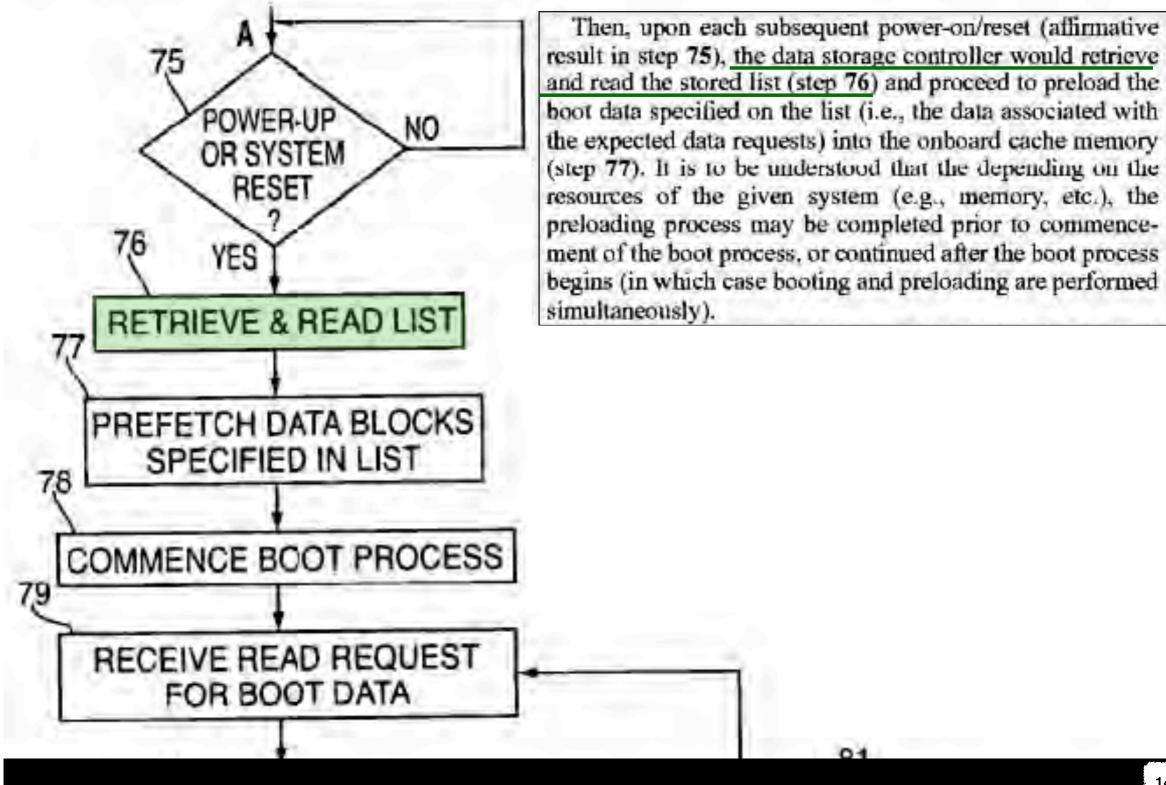

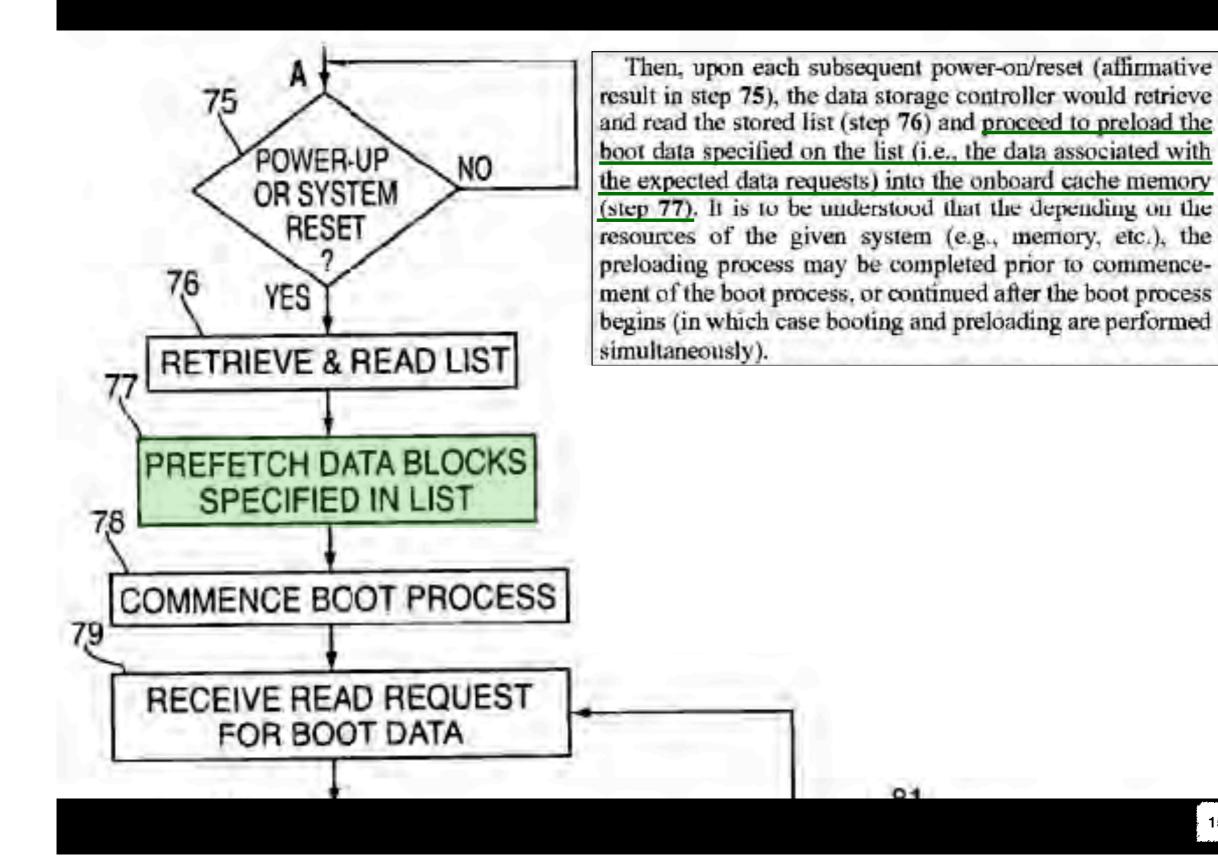

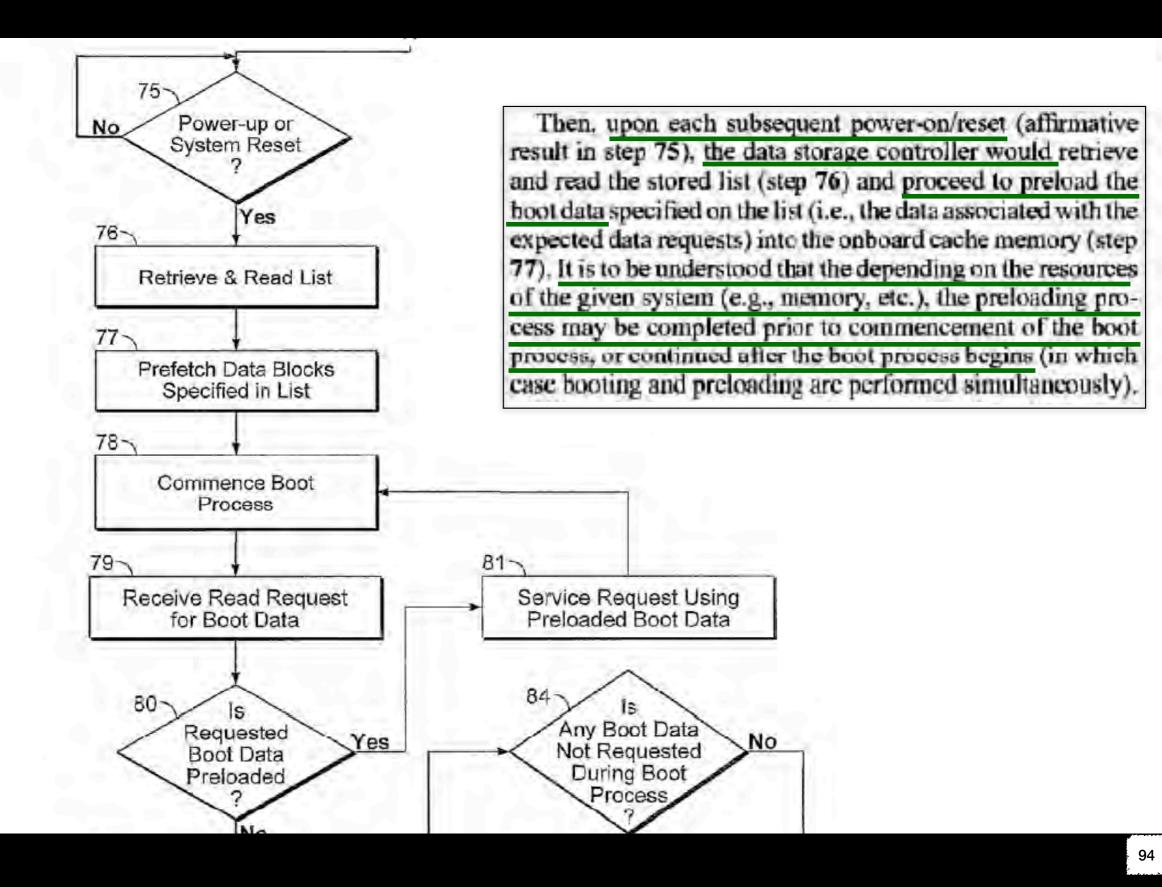

Then, upon each subsequent power-on/reset (affirmative result in step 75), the data storage controller would retrieve and read the stored list (step 76) and proceed to preload the boot data specified on the list (i.e., the data associated with the expected data requests) into the onboard cache memory (step 77). It is to be understood that the depending on the resources of the given system (e.g., memory, etc.), the preloading process may be completed prior to commencement of the boot process, or continued after the boot process begins (in which case booting and preloading are performed simultaneously).

01

result in step 75), the data storage controller would retrieve and read the stored list (step 76) and proceed to preload the boot data specified on the list (i.e., the data associated with the expected data requests) into the onboard cache memory (step 77). It is to be understood that the depending on the resources of the given system (e.g., memory, etc.), the preloading process may be completed prior to commencement of the boot process, or continued after the boot process begins (in which case booting and preloading are performed

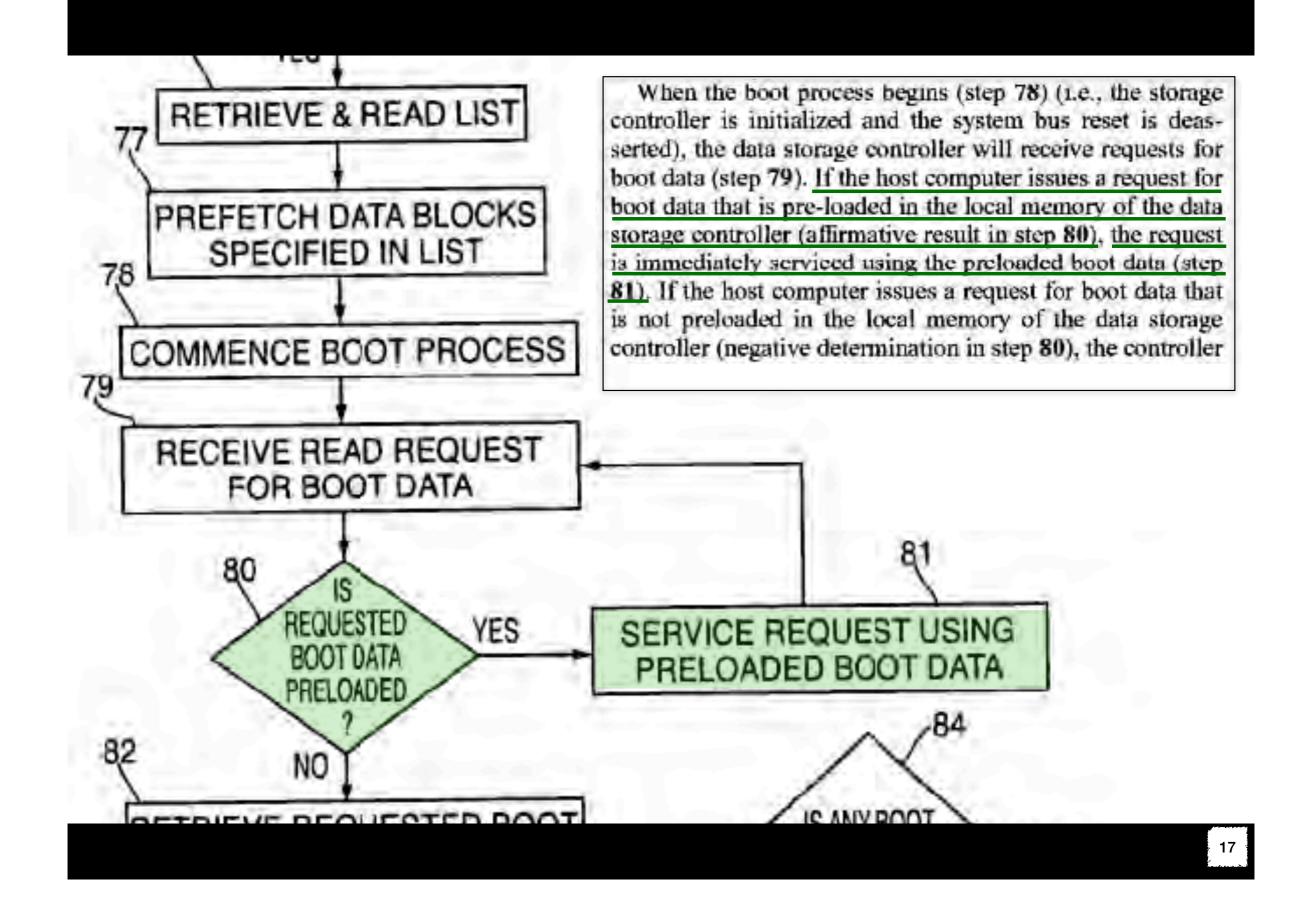

When the boot process begins (step 78) (i.e., the storage controller is initialized and the system bus reset is deasserted), the data storage controller will receive requests for boot data (step 79). If the host computer issues a request for boot data that is pre-loaded in the local memory of the data storage controller (affirmative result in step 80), the request is immediately serviced using the preloaded boot data (step 81). If the host computer issues a request for boot data that is not preloaded in the local memory of the data storage controller (negative determination in step 80), the controller

01

UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

APPLE INC., Petitioner,

**v**.

REALTIME DATA LLC, Patent Owner.

Case IPR2016-01365 Patent 7,181,608

PETITIONER'S REPLY TO PATENT OWNER'S RESPONSE

Ex. 2013 Page 18 of 145

# Proceeding No.: IPR2016-01365 Attorney Docket: 39521-0023IP1

anticipation" of anything, let alone "immediate or near-in-time use." Because the '608 Patent does not even use these terms to describe preloading, it would be improper to import them into the term preloading under BRI.

# 2) Realtime's Preloading Construction is Inconsistent with Examples of Preloading in the '608 Patent

Contrary to BRI, Realtime's construction improperly excludes examples of preloading in the '608 Patent. POR, 3-7, 12-16, 16-26. Specifically, the claims require preloading boot data prior to completion of initialization of the central processing unit. The '608 Patent describes several examples where preloading occurs prior to completion of initialization because the preloading occurs prior to system reset or boot. In these examples, the '608 Patent simply states that preloading occurs prior to system reset or boot; it does not qualify how far in advance of reset or boot the preloading occurs. Thus, these examples align with the claim language, but are not limited to preloading "in anticipation of immediate or near-in-time use," as advocated by Realtime.

For example, the '608 Patent explains that "*prior to host system reset*, the data storage controller can proceed to *pre-load* the portions of the computer operating system from the boot device (e.g., hard disk) into the on-board cache memory." '608, 21:45-65. In this example, "[s]ince the same portions of the operating system must be loaded *upon each boot process*, it is advantageous for the boot device

occurs prior to completion of initialization because the preloading occurs prior to system reset or boot. In these examples, the '608 Patent simply states that preloading occurs prior to system reset or boot; it does not qualify how far in advance of reset or boot the preloading occurs. Thus, these examples align with the claim language, but are not limited to preloading "in anticipation of immediate or near-in-time use," as advocated by Realtime.

For example, the '608 Patent explains that "*prior to host system reset*, the data storage controller can proceed to *pre-load* the portions of the computer operating system from the boot device (e.g., hard disk) into the on-board cache memory."

'608, 21:45-65. In this example, "[s]ince the same portions of the operating system

must be loaded upon each boot process, it is advantageous for the boot device

21

If only the PCI Bus and DSP require SDRAM:

| PCI Bus Interface<br>DSP Accesses | (A+B)/K<br>(A+B)/K |  |

|-----------------------------------|--------------------|--|

If only the DSP and Disk require SDRAM:

| PCI Bus Interface       | 2A/K |

|-------------------------|------|

| UltraDMA Disk Interface | 2B/K |

|                         |      |

It should be noted that the resultant ratios may all be scaled by a constant in order to most effectively utilize the bandwidths of the internal busses and external interfaces. In based upon the time required to complete individual cycles. For example if PCI Bus interface takes 20% longer than all other cycles, the PCI time slice should be adjusted longer accordingly.

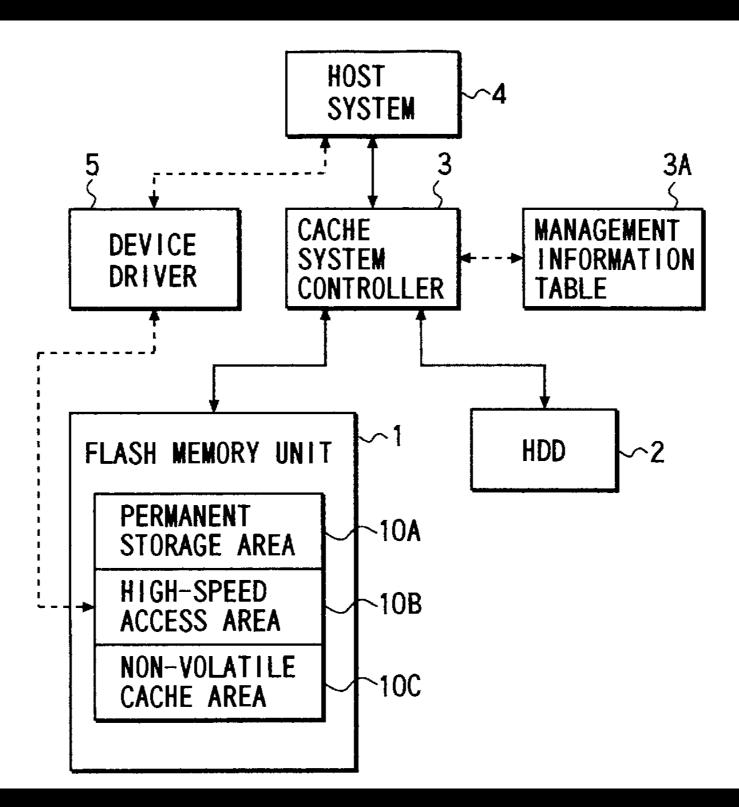

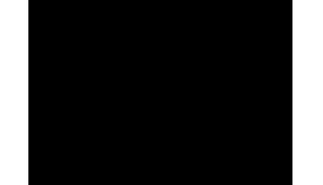

V. Instant Boot Device for Operating System, Application Program and Loading

Typically, with conventional boot device controllers, after reset, the boot device controller will wait for a command controller will typically be reset prior to bus reset and before the computer bus starts sending commands, this wait period is unproductive time. The initial bus commands inevitably instruct the boot device controller to retrieve data from the boot device (such as a disk) for the operating system. Since 40 most boot devices are relatively slow compared to the speed of most computer busses, a long delay is seen by the computer user. This is evident in the time it takes for a typical computer to boot.

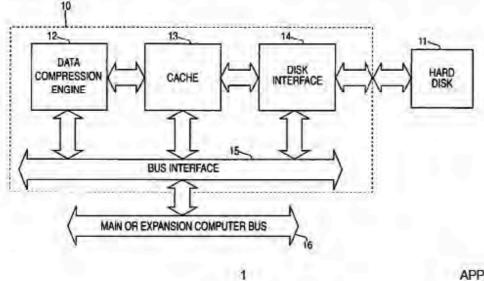

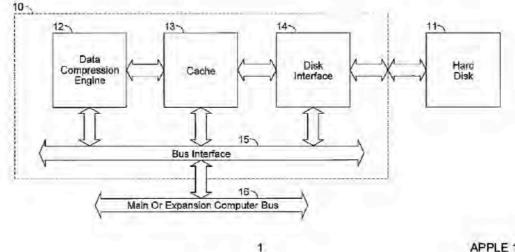

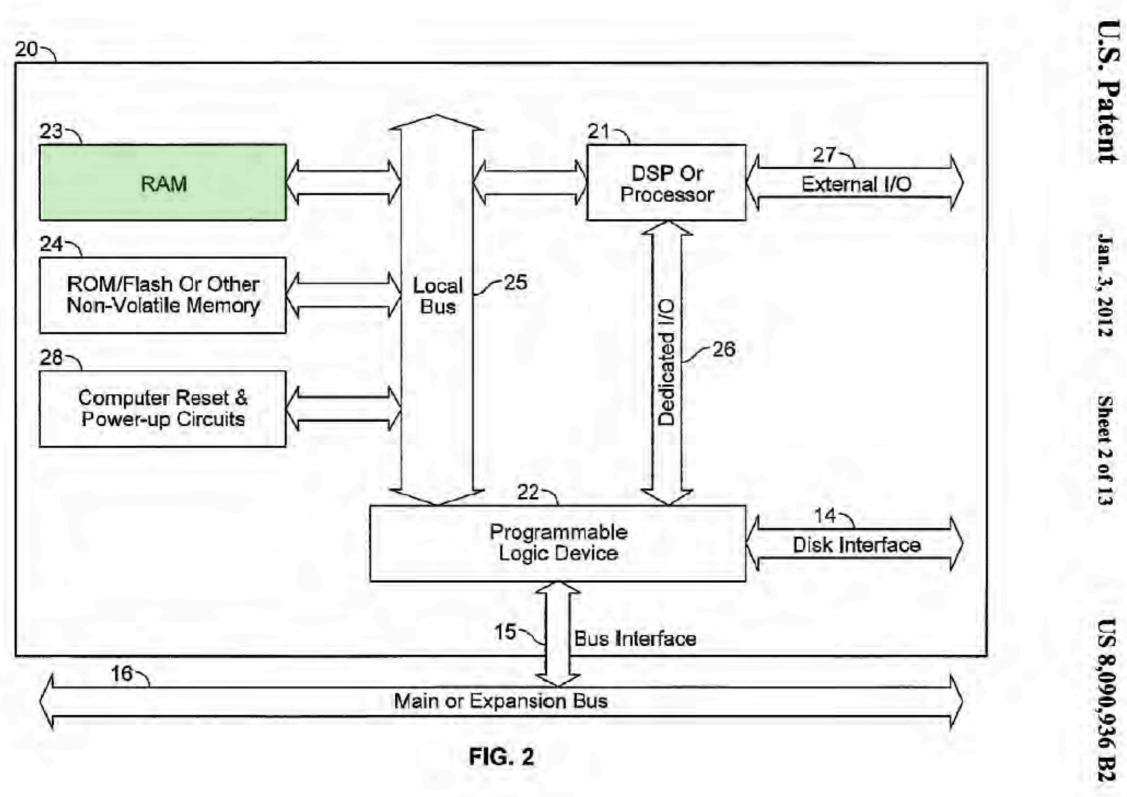

(having an architecture as described herein) may employ a technique of data preloading to decrease the computer system boot time. Upon host system power-up or reset, the data storage controller will perform a self-diagnostic and program the programmable logic device (as discussed 50 above) prior to completion of the host system reset (e.g., PCI bus reset) so that the logic device can accept PCI Bus commands after system reset. Further, prior to host system reset, the data storage controller can proceed to pre-load the portions of the computer operating system from the boot 55 device (e.g., hard disk) into the on-board cache memory. The data storage controller preloads the needed sectors of data in the order in which they will be needed. Since the same portions of the operating system must be loaded upon each ler to preload such portions and not wait until it is commanded to load the operating system. Preferably, the data storage controller employs a dedicated IO channel of the DSP (with or without data compression) to pre-load computer operating systems and applications.

Once the data is preloaded, when the computer system bus issues its first read commands to the data storage controller 22

seeking operating system data, the data will already be available in the cache memory of the data storage controller. The data storage controller will then be able to instantly start transmitting the data to the system bus. Before transmission 5 to the bus, if the data was stored in compressed format on the boot device, the data will be decompressed. The process of preloading required (compressed) portions of the operating system significantly reduces the computer boot process time. In addition to preloading operating system data, the data 10 storage controller could also preload other data that the user would likely want to use at startup. An example of this would be a frequently used application such as a word

processor and any number of document files. There are several techniques that may be employed in 15 accordance with the present invention that would allow the data storage controller to know what data to preload from the boot device. One technique utilizes a custom utility program that would allow the user to specify what applications/data should be preloaded.

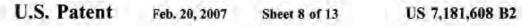

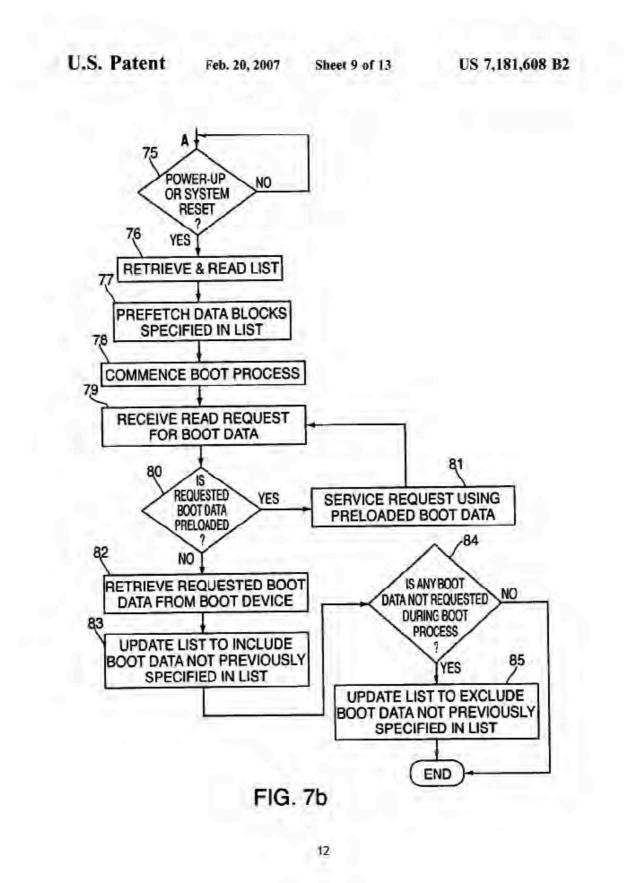

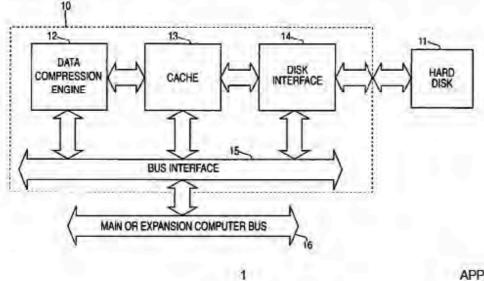

Another technique (illustrated by the flow diagram of 20 FIGS. 7a and 7b) that may be employed comprises an automatic process that requires no input from the user. With this technique, the data storage controller maintain a list comprising the data associated with the first series of data addition each ratio can be scale by an adjustment factor 25 requests received by the data storage controller by the host system after a power-on/reset. In particular, referring to FIG. 7a, during the computer boot process, the data storage controller will receive requests for the boot data (step 70). In response, the data storage controller will retrieve the 30 requested boot data from the boot device (e.g., hard disk) in the local cache memory (step 71). For each requested data block, the data storage controller will record the requested data block number in a list (step 72). The data storage controller will record the data block number of each data over the computer bus (such as PCI). Since the boot device 35 block requested by the host computer during the boot process (repeat steps 70-72). When the boot process is complete (affirmative determination in step 73), the data storage controller will store the data list on the boot device (or other storage device) (step 74).

Then, upon each subsequent power-on/reset (affirmative result in step 75), the data storage controller would retrieve and read the stored list (step 76) and proceed to preload the boot data specified on the list (i.e., the data associated with the expected data requests) into the onboard cache memory It is to be appreciated that a data storage controller 45 (step 77). It is to be understood that the depending on the resources of the given system (e.g., memory, etc.), the preloading process may be completed prior to commencement of the boot process, or continued after the boot process begins (in which case booting and preloading are performed simultaneously).

When the boot process begins (step 78) (i.e., the storage controller is initialized and the system bus reset is deasserted), the data storage controller will receive requests for boot data (step 79). If the host computer issues a request for boot data that is pre-loaded in the local memory of the data storage controller (affirmative result in step 80), the request is immediately serviced using the preloaded boot data (step 81). If the host computer issues a request for boot data that is not preloaded in the local memory of the data storage boot process, it is advantageous for the boot device control- 60 controller (negative determination in step 80), the controller will retrieve the requested data from the boot device, store the data in the local memory, and then deliver the requested boot data to the computer bus (step 82). In addition, the data storage controller would update the boot data list by record-65 ing any changes in the actual data requests as compared to the expected data requests already stored in the list (step 83). Then, upon the next boot sequence, the boot device con-

It is to be appreciated that a data storage controller 45 (ste (having an architecture as described herein) may employ a resc technique of data preloading to decrease the computer pre system boot time. Upon host system power-up or reset, the me data storage controller will perform a self-diagnostic and beg program the programmable logic device (as discussed 50 sim above) prior to completion of the host system reset (e.g., PCI bus reset) so that the logic device can accept PCI Bus con commands after system reset. Further, prior to host system ser reset, the data storage controller can proceed to pre-load the boc portions of the computer operating system from the boot 55 boc device (e.g., hard disk) into the on-board cache memory. The stoi data storage controller preloads the needed sectors of data in is i the order in which they will be needed. Since the same **81**) portions of the operating system must be loaded upon each is t boot process, it is advantageous for the boot device control- 60 con ler to preload such portions and not wait until it is comwil

storage controller employs a dedicated IO channel of the DSP (with or without data compression) to pre-load computer operating systems and applications.

Once the data is preloaded, when the computer system bus issues its first read commands to the data storage controller

# 22

- seeking operating system data, the data will already be available in the cache memory of the data storage controller. The data storage controller will then be able to instantly start transmitting the data to the system bus. Before transmission

- 5 to the bus, if the data was stored in compressed format on the boot device, the data will be decompressed. The process of preloading required (compressed) portions of the operating system significantly reduces the computer boot process time. In addition to preloading operating system data, the data

23

u

b

S1

11

tł

Т

UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

APPLE INC., Petitioner,

v.

REALTIME DATA LLC, Patent Owner.

Case IPR2016-01365 Patent 7,181,608

PETITIONER'S REPLY TO PATENT OWNER'S RESPONSE

Ex. 2013 Page 24 of 145

Proceeding No.: IPR2016-01365 Attorney Docket: 39521-0023IP1 controller to *preload* such portions and not wait until it is commanded to load the operating system." *Id*.

This example makes explicit that, contrary to Realtime's arguments, preloading occurs "prior to host system reset" (i.e., prior to boot<sup>1</sup>). Indeed, the '608 Patent deems such an approach "advantageous." '608, 21:45-65.

The '608 Patent provides further confirmation that preloading may occur prior to a subsequent boot process through discussion of two alternative examples. In a first example, preloading is completed prior to boot and, in a second, alternative example, booting and preloading are performed simultaneously. '608, 22:20-50. Specifically, the '608 Patent explains that:

It is to be understood that the depending on the resources of the given system (e.g., memory, etc.), the *preloading* process may be completed *prior to commencement of the boot process*, or continued after the boot process begins (in which case booting and preloading are performed simultaneously).

# '608, 22:40-50.

This passage demonstrates that, in a system equipped with appropriate resources (e.g., non-volatile cache memory), preloading in the '608 Patent is

<sup>&</sup>lt;sup>1</sup> The '608 Patent explains, at 11:26-30, that "the boot process begins when the CPU of the host system is released from external reset ...."

to a subsequent boot process through discussion of two alternative examples. In a first example, preloading is completed prior to boot and, in a second, alternative example, booting and preloading are performed simultaneously. '608, 22:20-50. Specifically, the '608 Patent explains that:

It is to be understood that the depending on the resources of the given system (e.g., memory, etc.), the *preloading* process may be completed *prior to commencement of the boot process*, or continued after the boot process begins (in which case booting and preloading are performed simultaneously).

'608, 22:40-50.

This passage demonstrates that, in a system equipped with appropriate resources (e.g., non-volatile cache memory), preloading in the '608 Patent is

## US 7,181,608 B2

#### If only the PCI Bus and DSP require SDRAM:

21

| PCI Bus Interface | (A+B)/K |

|-------------------|---------|

| DSP Accesses      | (A+B)/K |

| DSP Accesses<br>UltraDMA Disk Interface | 2A/K |  |

|-----------------------------------------|------|--|

| UltraDMA Disk Interface                 | 2B/K |  |

If only the PCI Bus and Disk require SDRAM:

| PCI Bus Interface<br>UltraDMA Disk Interface | 2A/K<br>2B/K |  |

|----------------------------------------------|--------------|--|

|                                              | ET UTK       |  |

It should be noted that the resultant ratios may all be scaled by a constant in order to most effectively utilize the bandwidths of the internal busses and external interfaces. In addition each ratio can be scale by an adjustment factor <sup>25</sup> based upon the time required to complete individual cycles. For example if PCI Bus interface takes 20% longer than all other cycles, the PCI time slice should be adjusted longer accordingly.

V. Instant Boot Device for Operating System, Application Program and Loading

Typically, with conventional boot device controllers, after reset, the boot device controller will wait for a command over the computer bus (such as PCI). Since the boot device 35 controller will typically be reset prior to bus reset and before the computer bus starts sending commands, this wait period is unproductive time. The initial bus commands inevitably instruct the boot device controller to retrieve data from the boot device (such as a disk) for the operating system. Since 40 most boot devices are relatively slow compared to the speed of most computer busses, a long delay is seen by the computer user. This is evident in the time it takes for a typical computer to boot.

(having an architecture as described herein) may employ a technique of data preloading to decrease the computer system boot time. Upon host system power-up or reset, the data storage controller will perform a self-diagnostic and program the programmable logic device (as discussed above) prior to completion of the host system reset (e.g., PCI bus reset) so that the logic device can accept PCI Bus commands after system reset. Further, prior to host system reset, the data storage controller can proceed to pre-load the portions of the computer operating system from the boot 55 device (e.g., hard disk) into the on-board cache memory. The data storage controller preloads the needed sectors of data in the order in which they will be needed. Since the same portions of the operating system must be loaded upon each boot process, it is advantageous for the boot device control- 60 ler to preload such portions and not wait until it is commanded to load the operating system. Preferably, the data storage controller employs a dedicated IO channel of the DSP (with or without data compression) to pre-load computer operating systems and applications. 65

Once the data is preloaded, when the computer system bus issues its first read commands to the data storage controller

## 22

seeking operating system data, the data will already be available in the cache memory of the data storage controller. The data storage controller will then be able to instantly start transmitting the data to the system bus. Before transmission

to the bus, if the data was stored in compressed format on the boot device, the data will be decompressed. The process of preloading required (compressed) portions of the operating system significantly reduces the computer boot process time. In addition to preloading operating system data, the data to storage controller could also preload other data that the user

would likely want to use at startup. An example of this would be a frequently used application such as a word processor and any number of document files.

There are several techniques that may be employed in accordance with the present invention that would allow the data storage controller to know what data to preload from the boot device. One technique utilizes a custom utility program that would allow the user to specify what applications/data should be preloaded.

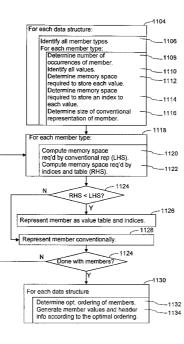

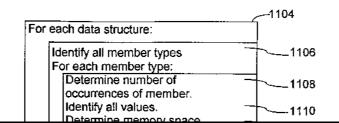

Another technique (illustrated by the flow diagram of FIGS. 7a and 7b) that may be employed comprises an automatic process that requires no input from the user. With this technique, the data storage controller maintain a list comprising the data associated with the first series of data requests received by the data storage controller by the host system after a power-on/reset. In particular, referring to FIG. 7a, during the computer boot process, the data storage controller will receive requests for the boot data (step 70). In response, the data storage controller will retrieve the requested boot data from the boot device (e.g., hard disk) in the local cache memory (step 71). For each requested data block, the data storage controller will record the requested data block number in a list (step 72). The data storage controller will record the data block number of each data block requested by the host computer during the boot process (repeat steps 70-72). When the boot process is complete (affirmative determination in step 73), the data storage controller will store the data list on the boot device (or other storage device) (step 74).

the spected data requests) into the onboard cache memory data storage controller will perform a self-diagnostic and rogram the programmable logic device (as discussed 50 spectra data storage controller will perform a self-diagnostic and solve and the spectra data storage controller will perform a self-diagnostic and solve and the spectra data storage controller will perform a self-diagnostic and solve and the spectra data storage controller will perform a self-diagnostic and solve and the spectra data storage controller will perform a self-diagnostic and solve and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data storage controller will perform a self-diagnostic and the spectra data specified on the list (i.e., the data associated with the expected data requests) into the onboard cache memory (step 77). It is to be understood that the depending on the resources of the given system (e.g., memory, etc.), the periodical period spectra data specified on the boot process of the given system (step 76) and proceed to process and the spectra data specified on the spectra data specified on the spectra data specified on the spectra data specified o

When the boot process begins (step 78) (i.e., the storage controller is initialized and the system bus reset is deasserted), the data storage controller will receive requests for boot data (step 79). If the host computer issues a request for boot data that is pre-loaded in the local memory of the data storage controller (affirmative result in step 80), the request is immediately serviced using the preloaded boot data (step 81). If the host computer issues a request for boot data that is not preloaded in the local memory of the data storage controller (negative determination in step 80), the controller will retrieve the requested data from the boot device, store the data in the local memory, and then deliver the requested boot data to the computer bus (step 82). In addition, the data storage controller would update the boot data list by recording any changes in the actual data requests as compared to the expected data requests already stored in the list (step 83). Then, upon the next boot sequence, the boot device con-

| ıe |    | (or other storage device) (step 74).                            |

|----|----|-----------------------------------------------------------------|

|    | 40 | Then, upon each subsequent power-on/reset (affirmative          |

| b  |    | result in step 75), the data storage controller would retrieve  |

| ıe |    | and read the stored list (step 76) and proceed to preload the   |

| а  |    | boot data specified on the list (i.e., the data associated with |

|    |    | the expected data requests) into the onboard cache memory       |

| er | 45 | (step 77). It is to be understood that the depending on the     |

| а  |    | resources of the given system (e.g., memory, etc.), the         |

| er |    | preloading process may be completed prior to commence-          |

| ıe |    | ment of the boot process, or continued after the boot process   |

| ıd |    | begins (in which case booting and preloading are performed      |

| ŀd | 50 | simultaneously).                                                |

| CI |    | When the boot process begins (step 78) (i.e., the storage       |

| 15 |    | controller is initialized and the system bus reset is deas-     |

| m  |    | serted), the data storage controller will receive requests for  |

| ıe |    | boot data (step 79). If the host computer issues a request for  |

|    |    |                                                                 |

| - Office Action Summary | Application No.       | Applicant(s) |

|-------------------------|-----------------------|--------------|

|                         | 09/776,267            | FALLON ET AL |

|                         | Examiner              | Art Unit     |

|                         | Suresh K. Suryawanshi | 2115         |

-- The MAILING DATE of this communication appears on the cover sheet with the correspondence address --Period for Reply

- A SHORTENED STATUTORY PERIOD FOR REPLY IS SET TO EXPIRE 3 MONTH(S) FROM

- THE MAILING DATE OF THIS COMMUNICATION.

- Extensions of time may be available under the provisions of 37 CFR 1.136(a). In no event, however, may a reply be timely filed after SIX (5) MONTHS from the mailing date of this communication.

- after SX (5) MON FIS from the mailing date of this communication. If the period for reply is specified above is lass than thirty (30) days, a reply within the statutory minimum of thirty (30) days will be considered timely. MO period for reply is specified above, the maximum statutory period will apply and will expire SIX (5) MONTHS from the mailing date of this communication. Failure to reply within the set or extended period for reply will, by statute, causa the application to become ABANDONED (35 U.S.C. § 133). Any reply received by the Office lake than three months after the mailing date of this communication, even if timely filed, may reduce any earned patent term adjustment. See 37 CFR 1.704(b).

Status

- 1) Responsive to communication(s) filed on 02 May 2005.

- 2a) This action is FINAL. 2b) This action is non-final.

- 3) Since this application is in condition for allowance except for formal matters, prosecution as to the merits is closed in accordance with the practice under Ex parte Quayle, 1935 C.D. 11, 453 O.G. 213.

#### **Disposition of Claims**

- 4) Claim(s) 1,2,4-7,9,10,12,13,15 and 17 is/are pending in the application.

- 4a) Of the above claim(s) \_\_\_\_\_ is/are withdrawn from consideration.

- 5) Claim(s) \_\_\_\_\_ is/are allowed.

- 6) Claim(s) 1,2,4-7,9,10,12,13,15 and 17 is/are rejected.

- Claim(s) \_\_\_\_\_ is/are objected to.

- 8) Claim(s) \_\_\_\_\_ are subject to restriction and/or election requirement.

#### **Application Papers**

- 9) The specification is objected to by the Examiner.

- 10) The drawing(s) filed on 02 February 2001 is/are: a) accepted or b) objected to by the Examiner. Applicant may not request that any objection to the drawing(s) be held in abeyance. See 37 CFR 1.85(a). Replacement drawing sheet(s) including the correction is required if the drawing(s) is objected to. See 37 CFR 1.121(d),

- 11) The oath or declaration is objected to by the Examiner. Note the attached Office Action or form PTO-152.

#### Priority under 35 U.S.C. § 119

- 12) Acknowledgment is made of a claim for foreign priority under 35 U.S.C. § 119(a)-(d) or (f).

- a) All b) Some \* c) None of:

- 1. Certified copies of the priority documents have been received.

- 2. Certified copies of the priority documents have been received in Application No.

- 3. Copies of the certified copies of the priority documents have been received in this National Stage application from the International Bureau (PCT Rule 17.2(a)).

- \* See the attached detailed Office action for a list of the certified copies not received.

#### Attachment(s)

1) X Notice of References Cited (PTO-892) 2) Notice of Draftsperson's Palent Drawing Review (PTO-948)

- 3) Information Disclosure Statement(s) (PTO-1449 or PTO/SB/08)

- Paper No(s)/Mall Date

- U.S. Patent and Trademark Office PTOL-326 (Rev. 1-04)

6) Other: Office Action Summary

4) Interview Summary (PTO-413) Paper No(s)/Mall Date.

5) Notice of Informal Patent Application (PTO-152)

Part of Paper No./Mail Date 3

01

Application/Control Number: 09/776,267 Art Unit: 2115

#### Claim Rejections - 35 USC § 103

Page 3

4 The following is a quotation of 35 U.S.C. 103(a) which forms the basis for all

obviousness rejections set forth in this Office action:

(a) A patent may not be obtained though the invention is not identically disclosed or described as set forth in section 102 of this title, if the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains. Patentability shall not be negatived by the manner in which the invention was made.

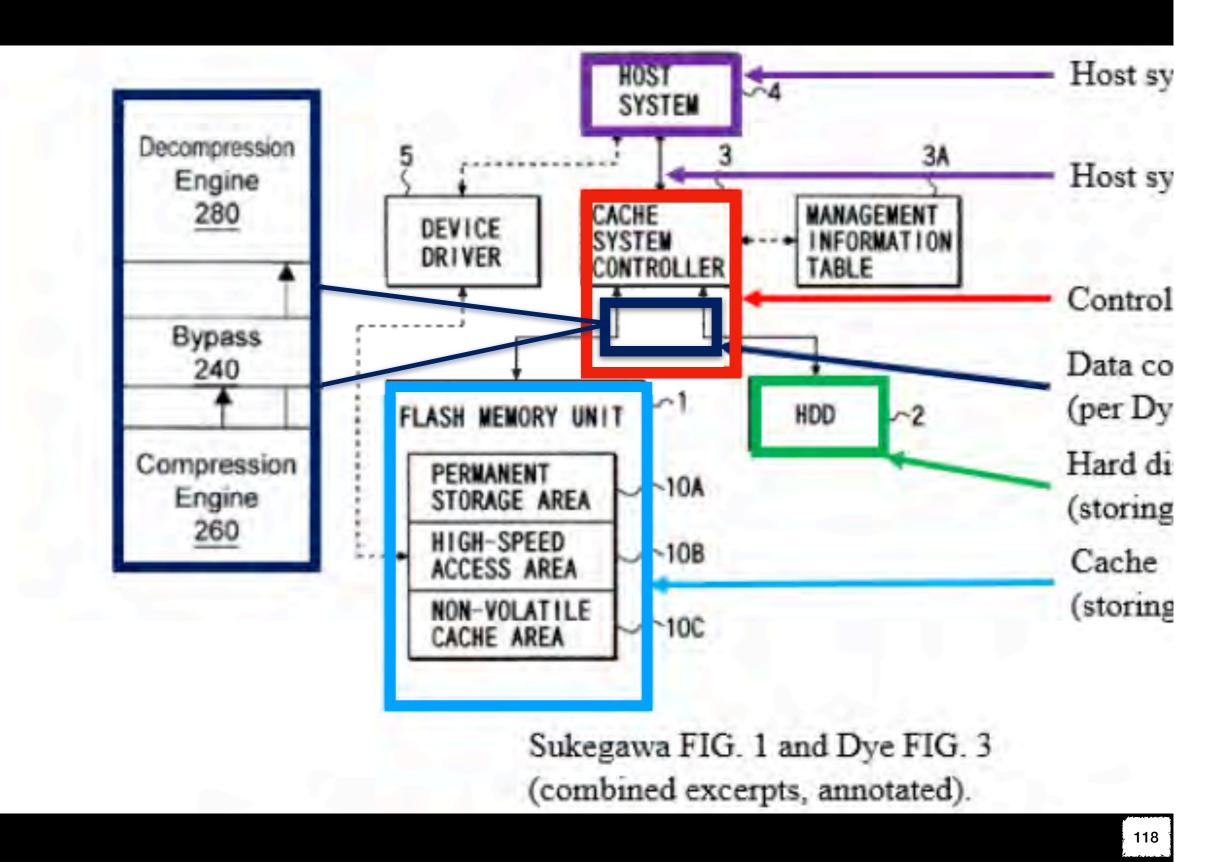

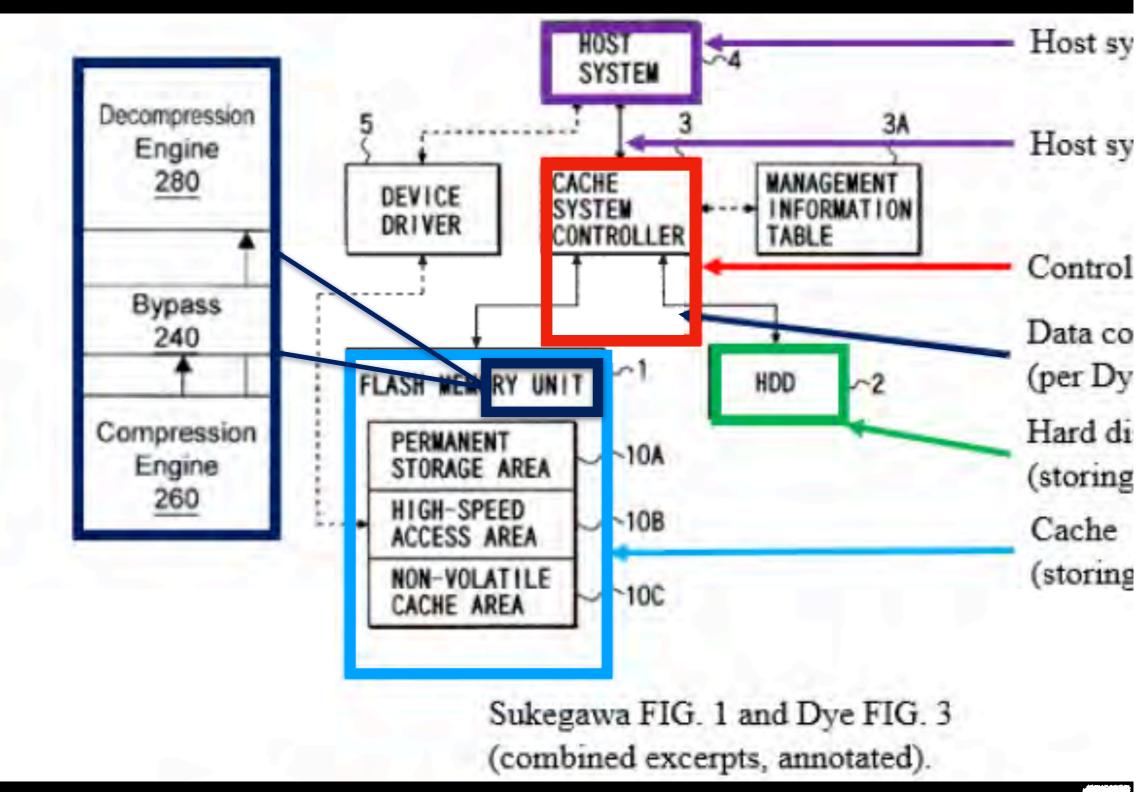

5. Claims 1-2, 4-7, 9-10, 12-13 and 15 are rejected under 35 U.S.C. 103(a) as being

unpatentable over Krocker et al (US Patent no 6,073,232) in view of Esfahani et al (US Patent no 6,434,695 B1).

6. As per claim 1, Krocker et al teach

maintaining a list of boot data used for booting a computer system [col. 2, lines 30-47; col. 5, lines 1-7; a prefetch table containing a listing of the disk locations and length of data records that were requested by the host computer in the immediately previous power-on/reset];

preloading the boot data upon initialization of the computer system [col. 2, lines 36-41; col. 3, lines 30-39; col. 5, lines 17-21; data is preloaded into the RAM cache according to the prefetch table]; and

servicing requests for boot data from the computer system using the preloaded boot data [col. 2, lines 41-47; col. 3, lines 30-39; data is communicated from the cache to the host computer].

5. Claims 1-2, 4-7, 9-10, 12-13 and 15 are rejected under 35 U.S.C. 103(a) as being unpatentable over <u>Krocker et al (US Patent no 6,073,232) in view of Esfahani et al (US Patent no</u> 6,434,695 B1).

6. As per claim 1, Krocker et al teach

maintaining a list of boot data used for booting a computer system [col. 2, lines 30-47; col. 5, lines 1-7; a prefetch table containing a listing of the disk locations and length of data records that were requested by the host computer in the immediately previous power-on/reset];

preloading the boot data upon initialization of the computer system [col. 2, lines 36-41; col. 3, lines 30-39; col. 5, lines 17-21; data is preloaded into the RAM cache according to the prefetch table]; and

# UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

APPLE, INC., Petitioner

v.

REALTIME DATA LLC, Patent Owner

Case IPR2016-01365 Patent 7,181,608

# EXPERT DECLARATION OF DR. GODMAR BACK IN SUPPORT OF THE PATENT OWNER'S RESPONSE

Ex. 2003 Page 1 of 52

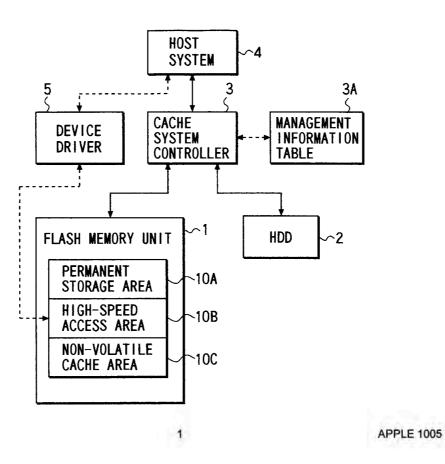

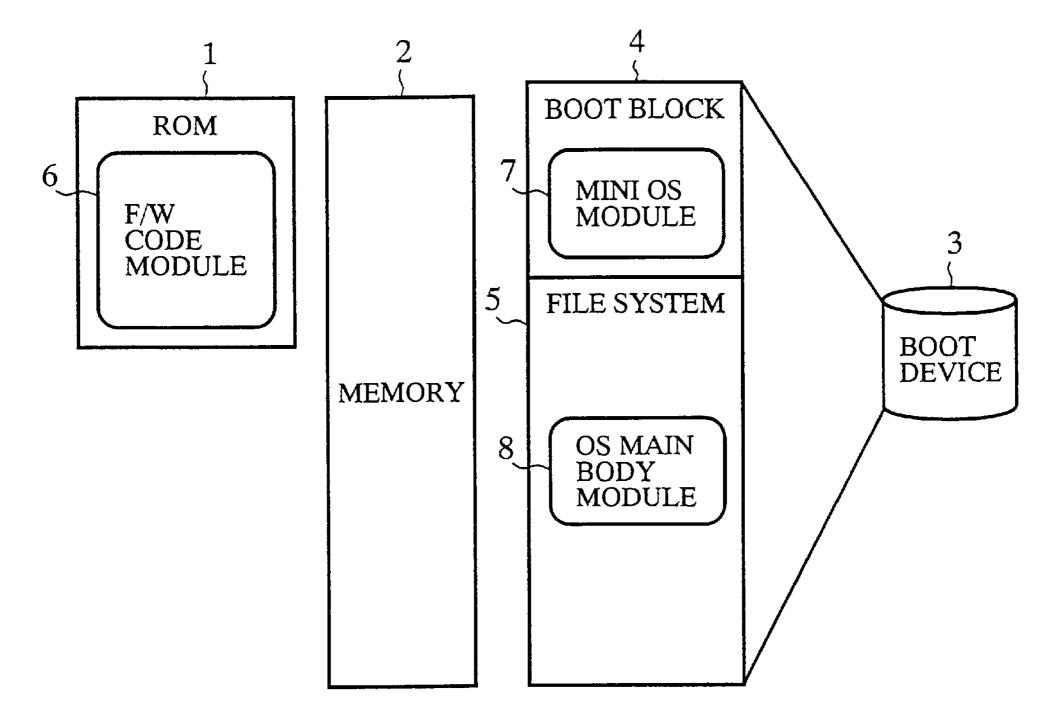

boot device.<sup>24</sup> And specification also explains that the data is preloaded from a boot device into the onboard cache memory of an exemplary data storage controller.<sup>25</sup>

51. Based on the disclosures of the '608 Patent, a POSITA would have understood that this movement of data from storage into memory is performed in anticipation of immediate or near-in-time use. Again, this is the manner in which the '608 Patent uses "preloading." For example, the '608 Patent discloses that the invention is designed to "provide[] accelerated loading of operating system and application programs upon system boot or application launch."<sup>26</sup> To this end, certain claims recite that boot or application data is preloaded to service requests for that data.<sup>27</sup> And in certain embodiments of the '608 Patent, the specification describes "preloading" as loading data because it will be needed, or is likely to be needed, for use by the system.<sup>28</sup>

52. In addition, the '608 Patent indicates that "preloading" is similar to "prefetching," which refers to the process of retrieving data before it is needed.  $\overline{^{24} \text{ Ex. 1001, '608 Patent at 3:60-61.}}$

Ex. 1001, 000 I atent at 5.00-01.

<sup>25</sup> Ex. 1001, '608 Patent at 21:50-54, 22:41-45.

<sup>26</sup> Ex. 1001, '608 Patent at 1:15-21; *see also* '608 Patent at Abs., 3:34-40.

<sup>27</sup> Ex. 1001, '608 Patent at claims 1, 7-9, 22, 27.

<sup>28</sup> Ex. 1001, '608 Patent at Abs., 21:56-62, 22:9-19, 23:13-38; Figs. 7b, 8b.

Ex. 2003 Page 23 of 52

Based on the disclosures of the '608 Patent, a POSITA would have 51. understood that this movement of data from storage into memory is performed in anticipation of immediate or near-in-time use. Again, this is the manner in which the '608 Patent uses "preloading." For example, the '608 Patent discloses that the invention is designed to "provide[] accelerated loading of operating system and application programs upon system boot or application launch."26 To this end, certain claims recite that boot or application data is preloaded to service requests for that data.<sup>27</sup> And in certain embodiments of the '608 Patent, the specification describes "preloading" as loading data because it will be needed, or is likely to be needed, for use by the system.<sup>28</sup>

52. In addition, the '608 Patent indicates that "preloading" is similar to "prefetching," which refers to the process of retrieving data before it is needed.

Page 34 of 145

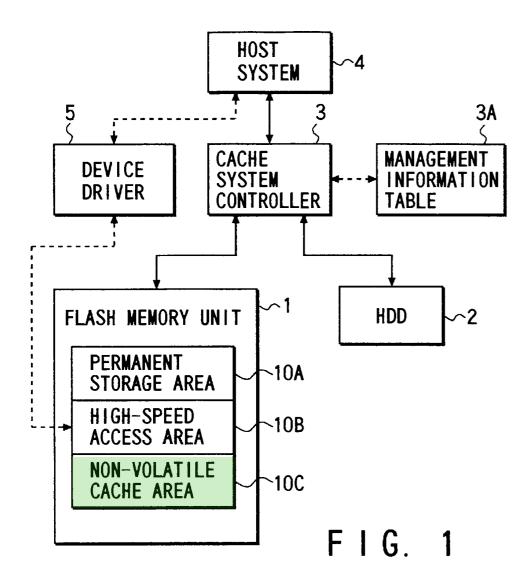

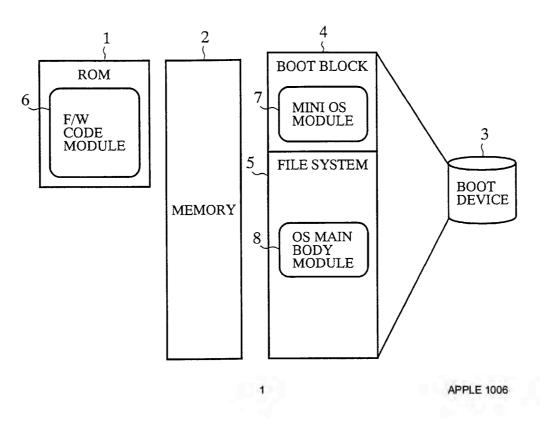

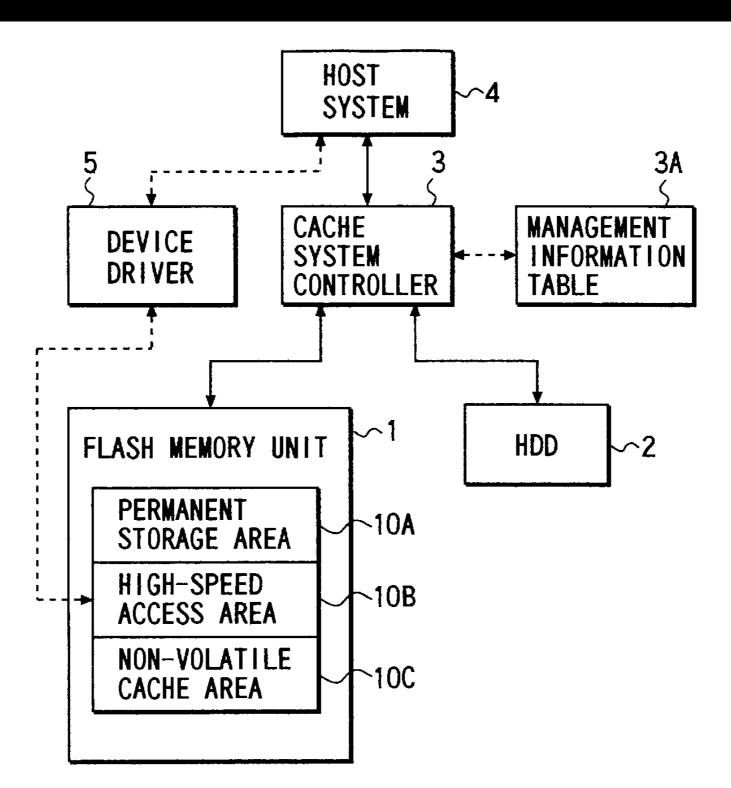

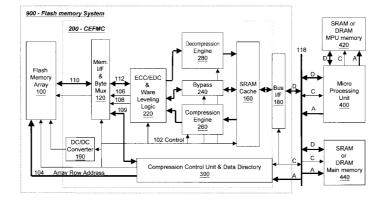

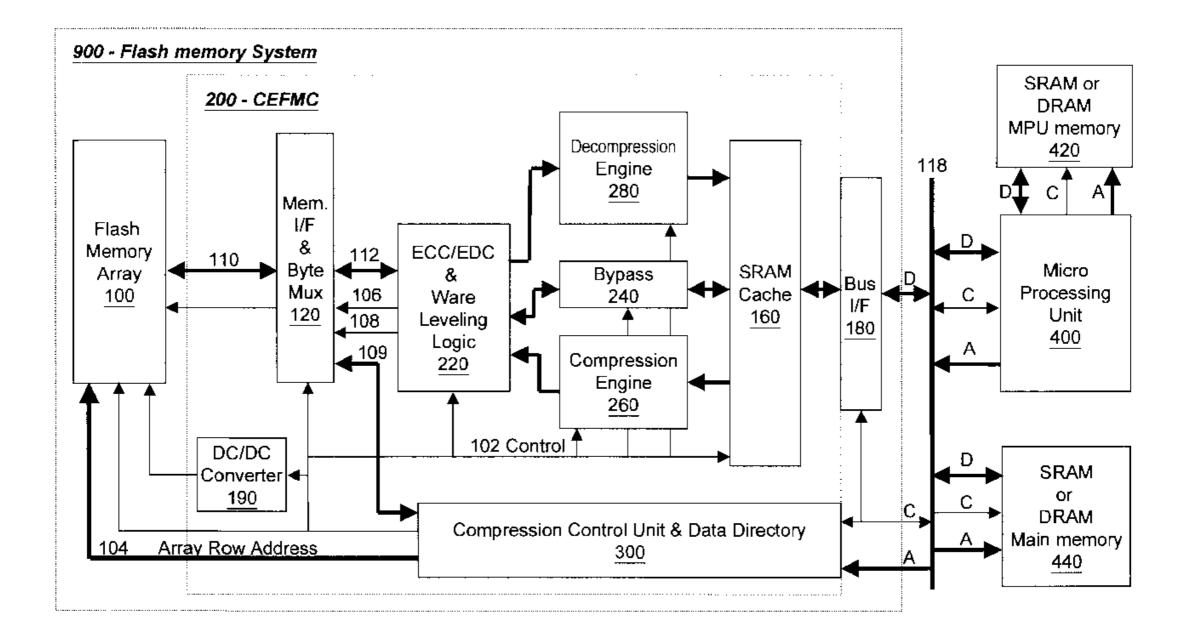

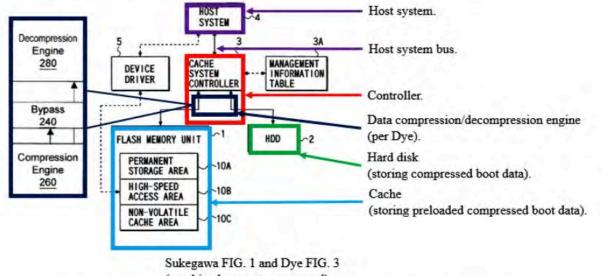

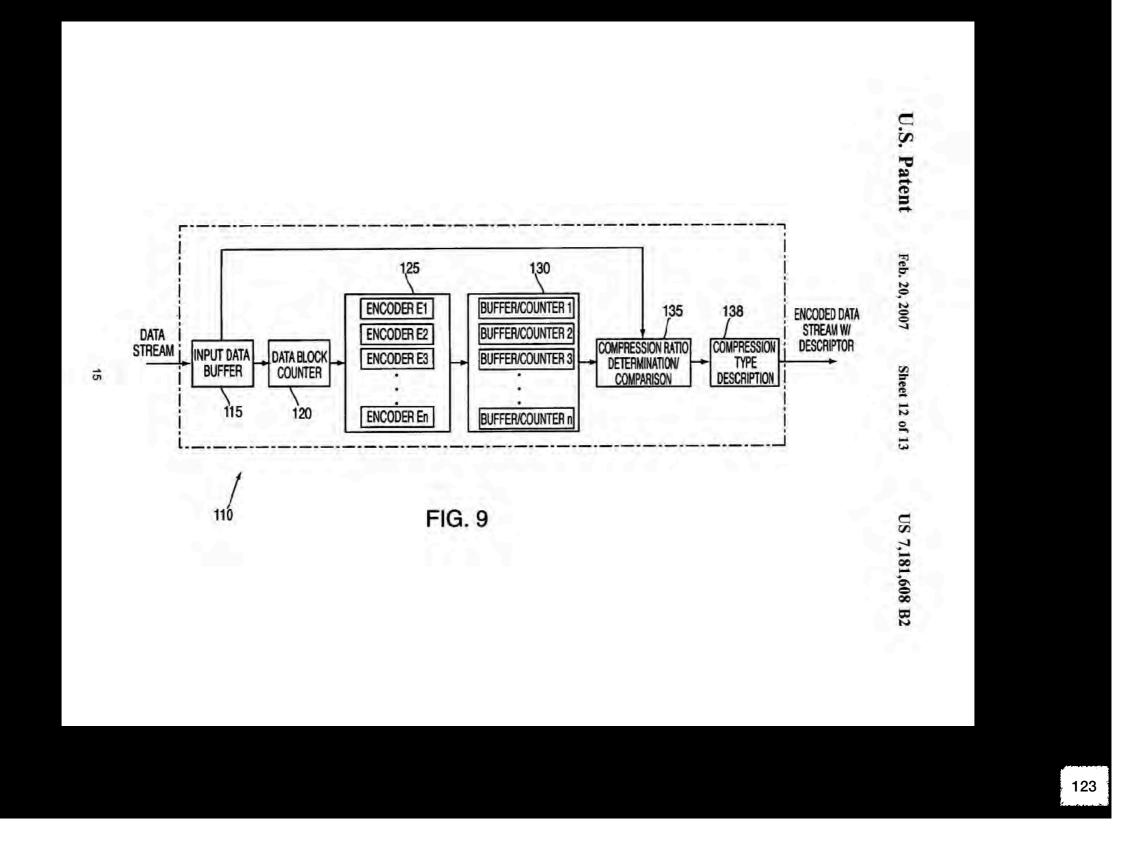

Specifically, in one embodiment, boot data is preloaded into the onboard cache memory of an exemplary data storage controller in step 77 of Figure 7b.<sup>29</sup> As shown below, Figure 7b describes step 77 as "Prefetch Data Blocks Specified in List":<sup>30</sup>

53. Figure 7b therefore indicates that "preloading" has a meaning similar to "prefetching." And "prefetching" refers to the process of retrieving data before it

Ex. 2003 Page 24 of 52

<sup>&</sup>lt;sup>29</sup> Ex. 1001, '608 Patent at 22:40-45; see also '608 Patent at 22:20-39.

<sup>&</sup>lt;sup>30</sup> Ex. 1001, '608 Patent at Fig. 7b.

53. Figure 7b therefore indicates that "preloading" has a meaning similar to "prefetching." And "prefetching" refers to the process of retrieving data before it is needed,<sup>31</sup> which further supports my interpretation of how a POSITA would have understood "preloading" at the time of invention.

54. This interpretation is also consistent with the file history of the '608 Patent. For example, during prosecution, the Patent Examiner initially rejected the <sup>31</sup> Ex. 2011, The Design and Implementation of the 4.4BSD Operating System at 535 (defining "prefetching" as "[t]he retrieval of data before they are needed. Many machines prefetch machine instructions so they can overlap the time spent

fetching instructions from memory with the time spent decoding instructions.");

UNITED STATES PATENT AND TRADEMARK OFFICE

BEFORE THE PATENT TRIAL AND APPEAL BOARD

APPLE INC., Petitioner,

v.

REALTIME DATA LLC, Patent Owner.

Case IPR2016-01365 Patent 7,181,608

PETITIONER'S REPLY TO PATENT OWNER'S RESPONSE

Ex. 2013 Page 37 of 145

### Proceeding No.: IPR2016-01365 Attorney Docket: 39521-0023IP1

completed before a boot process commences. Indeed, and as the passage makes clear by its alternative example, preloading during the boot process is only necessary in systems lacking appropriate resources.

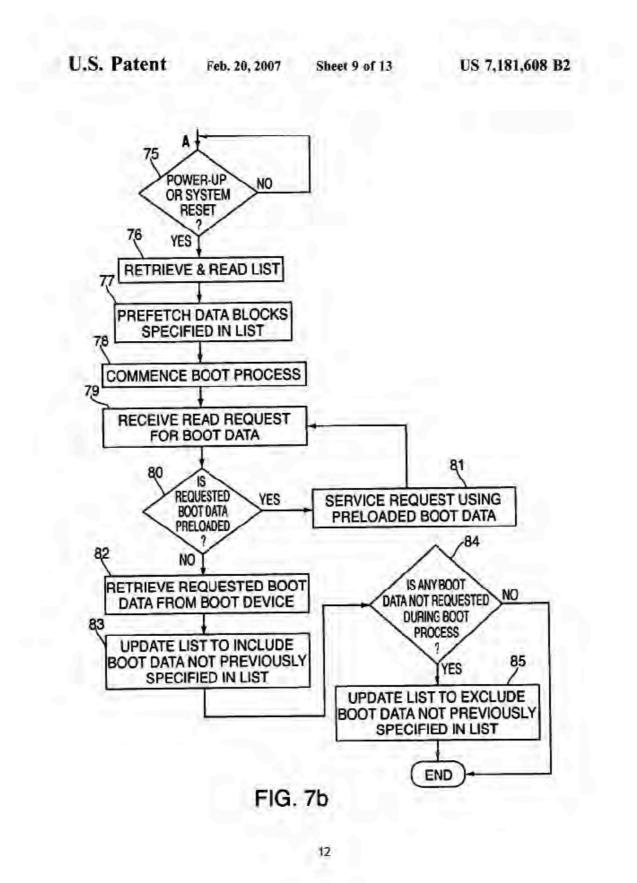

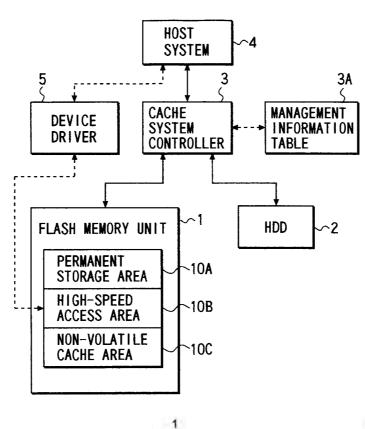

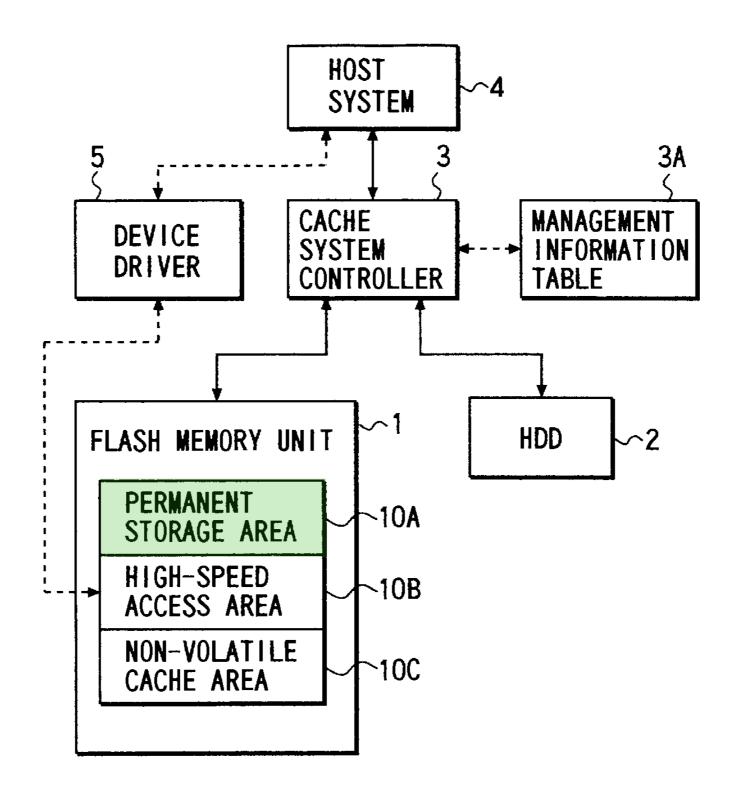

Along these lines, the '608 Patent explains, and Dr. Back confirms<sup>2</sup>, that the cache memory device in which preloaded boot data is stored "may comprise...*non-volatile memory*" in which data is persistently stored across boot cycles. '608, 6:60-63. Indeed, Dr. Back explained that, "if boot data were stored in the cache memory and if a form of non-volatile memory were used, then this data stored in the cache *would be available after subsequent power on*." APPLE-1017 42, 76. Dr. Back added, "[t]hat's what non-volatile means." *Id.*, 76.

By describing examples of preloading prior to boot, including examples of preloading into non-volatile memory, the intrinsic record of the '608 Patent runs contrary to Realtime's attempt to narrow the term preloading. Indeed, Realtime's "preloading" construction is improper because it excludes examples within the '608 Patent specification and is inconsistent with the testimony of Realtime's own expert, Dr. Back.

<sup>2</sup> In his deposition on June 20, 2017, Dr. Back was asked whether the claimed cache memory "could be either volatile or non-volatile," and he concluded that yes, "it could be either way." APPLE-1017, 29-30.

in systems lacking appropriate resources.

Along these lines, the '608 Patent explains, and <u>Dr. Back confirms<sup>2</sup></u>, that the cache memory device in which <u>preloaded boot data is stored "may comprise...non-</u> <u>volatile memory" in which data is persistently stored across boot cycles.</u> '608, 6:60-63. Indeed, Dr. Back explained that, "if boot data were stored in the cache memory and if a form of non-volatile memory were used, then this data stored in the cache *would be available after subsequent power on*." APPLE-1017 42, 76. Dr. Back added, "[t]hat's what non-volatile means." *Id.*, 76.

By describing examples of preloading prior to boot, including examples of preloading into non-volatile memory, the intrinsic record of the '608 Patent runs

"preloading" construction is improper because it excludes examples within the '608 Patent specification and is inconsistent with the testimony of Realtime's own expert, Dr. Back.

<sup>2</sup> In his deposition on June 20, 2017, Dr. Back was asked whether the claimed cache memory "could be either volatile or non-volatile," and he concluded that yes, "it could be either way." APPLE-1017, 29-30.

|        | UNITED STATES PATENT AND                                                                   | TRADEMARK OFFICE                               |

|--------|--------------------------------------------------------------------------------------------|------------------------------------------------|

|        | BEFORE THE PATENT TRIAL                                                                    |                                                |

|        |                                                                                            |                                                |

| APPLE, | INC.,                                                                                      |                                                |

|        | Petitioners,                                                                               |                                                |

|        | -vs-                                                                                       | Case IPR2016-0136                              |

|        |                                                                                            | Patent 7,181,608B                              |

| REALTI | ME DATA LLC,                                                                               |                                                |

|        | Patent Owner.                                                                              |                                                |

| 1000   | 5. T. I.                                                                                   |                                                |

| APPLE, | INC.,                                                                                      |                                                |

|        | Detitionara                                                                                |                                                |

|        | Petitioners,                                                                               |                                                |

|        | -vs-                                                                                       | Case IPR2016-0136                              |

|        |                                                                                            | Patent 8,090,936B                              |

| REALTT | ME DATA LLC,                                                                               |                                                |

|        |                                                                                            |                                                |

|        |                                                                                            |                                                |

|        | Patent Owner.                                                                              |                                                |

|        |                                                                                            |                                                |

|        |                                                                                            |                                                |

|        |                                                                                            | F DR. GODMAR BACK                              |

|        | Patent Owner.                                                                              |                                                |

|        | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2                  | :28 p.m.<br>017                                |

|        | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2                                | :28 p.m.<br>017                                |

|        | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2                  | :28 p.m.<br>017                                |

|        | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2                  | :28 p.m.<br>017                                |

|        | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2                  | :28 p.m.<br>017                                |

|        | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2<br>Blacksburg, V | :28 p.m.<br>017                                |

| Job No | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2<br>Blacksburg, V | :28 p.m.<br>017<br>Tirginia                    |

| Job No | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2<br>Blacksburg, V | :28 p.m.<br>017<br>Tirginia                    |

| Job No | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2<br>Blacksburg, V | :28 p.m.<br>017<br>Tirginia                    |

| Job No | Patent Owner.<br>VIDEOTAPED DEPOSITION O<br>11:18 a.m. to 2<br>June 20, 2<br>Blacksburg, V | :28 p.m.<br>017<br>irginia<br>R, CRR<br>Page 1 |

Apple v. Realtime Proceeding No. IPR2016-01365 APPLE 1017

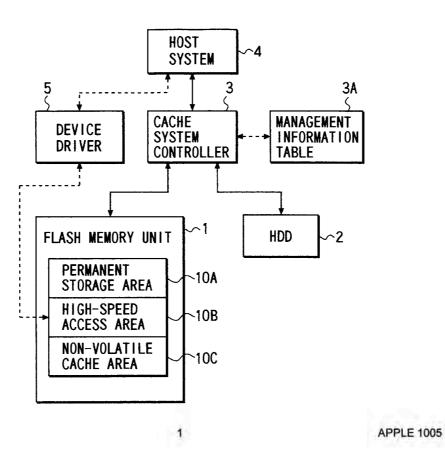

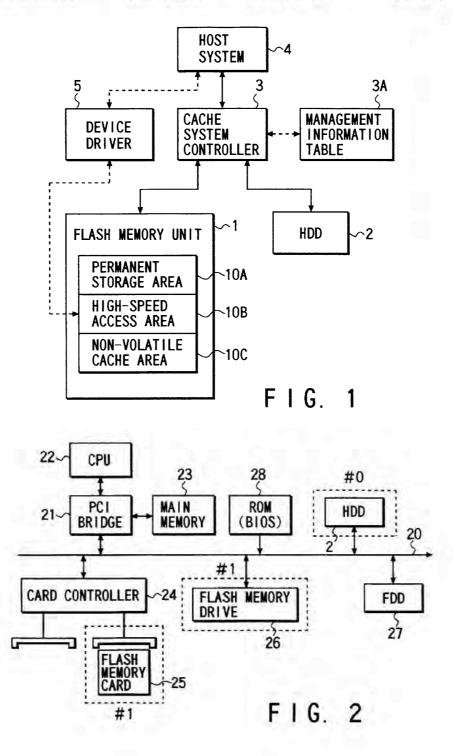

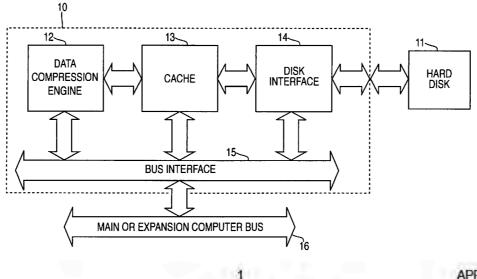

#### GODMAR BACK 1 device in the context of the specification. In your opinion, can the Data Controller 2 0. 3 10 which is shown in Figure 1 and described 4 elsewhere in the patent, can that function as 5 described in the '936 Patent if Cache 13 is a 6 nonvolatile memory? 7 MR. EDELL: Objection. Form. 8 THE WITNESS: I would say no. No. The 9 -- well, let me qualify this. 10 The -- most of the, if not all, of the 11 specification of both the '608 and the '936 12 Patents focus on how this particular controller 13 would operate if the cache memory is a volatile 14 memory. But if it weren't a volatile memory, 15 then the cache controller could -- would operate 16 in a way that actually does not benefit from the 17 nonvolatility of the memory. 18 BY MS. VIDAL: 19 0. So nonvolatility of the memory would just 20 be an added feature? 21 MR. EDELL: Objection to form. 22 THE WITNESS: In this hypothetical setup 23 that you are proposing, the nonvolatility of the 24 memory would be superfluous, and it would not be 25 needed. Page 27

Veritext Legal Solutions 866 299-5127 27

| 2  | Q. In your opinion, can the Data Controller      |

|----|--------------------------------------------------|

| 3  | 10 which is shown in Figure 1 and described      |

| 4  | elsewhere in the patent, can that function as    |

| 5  | described in the '936 Patent if Cache 13 is a    |

| 6  | nonvolatile memory?                              |

| 7  | MR. EDELL: Objection. Form.                      |

| 8  | THE WITNESS: I would say no. No. The             |

| 9  | well, let me qualify this.                       |

| 10 | The most of the, if not all, of the              |

| 11 | specification of both the '608 and the '936      |

| 12 | Patents focus on how this particular controller  |

| 13 | would operate if the cache memory is a volatile  |

| 14 | memory. But if it weren't a volatile memory,     |

| 15 | then the cache controller could would operate    |

| 16 | in a way that actually does not benefit from the |

| 17 | nonvolatility of the memory.                     |

|    |                                                  |

| 14 | memory. But if it weren't a volatile memory,     |

|----|--------------------------------------------------|

| 15 | then the cache controller could would operate    |

| 16 | in a way that actually does not benefit from the |

| 17 | nonvolatility of the memory.                     |

| 18 | BY MS. VIDAL:                                    |

| 19 | Q. So nonvolatility of the memory would just     |

| 20 | be an added feature?                             |

| 21 | MR. EDELL: Objection to form.                    |

| 22 | THE WITNESS: In this hypothetical setup          |

| 23 | that you are proposing, the nonvolatility of the |

| 24 | memory would be superfluous, and it would not be |

| 25 | needed.                                          |

|    | Page 27                                          |

|    | Veritext Legal Solutions<br>866 299-5127         |

|    | 27                                               |

Ex. 2013 Page 44 of 145

#### GODMAR BACK THE WITNESS: The earlier question, my 1 2 understanding is that you asked whether Disk 11 3 is an example of the boot device that is 4 referenced in Claim 1 of the '936 Patent. 5 BY MS. VIDAL: Correct. Would it be the same for the 6 0. 7 '608? 8 Α. Let us double check if the '608 refers to 9 the boot device. 10 Q. Thank you. 11 Α. It does and, it would be the same. 0. 12 Thank you. In your opinion, can the 13 claimed cache memory of both the '608 and the '936 14 Patents be nonvolatile memory? 15 MR. EDELL: Objection to form. 16 THE WITNESS: The Cache Memory 13 in both 17 the '608 and the '936 Patent could be either 18 volatile or nonvolatile memory. As I explained, 19 if it were nonvolatile memory, there would not be any benefit derived from the fact that it is 20 21 nonvolatile. 22 BY MS. VIDAL: 23 And the same is true for the claimed 0. 24 cache memory? That could be either volatile or 25 nonvolatile? Page 29

Veritext Legal Solutions 866 299-5127 29

| 11 | A. It does and, it would be the same.              |

|----|----------------------------------------------------|

| 12 | Q. Thank you. In your opinion, can the             |

| 13 | claimed cache memory of both the '608 and the '936 |

| 14 | Patents be nonvolatile memory?                     |

| 15 | MR. EDELL: Objection to form.                      |

| 16 | THE WITNESS: The Cache Memory 13 in both           |

| 17 | the '608 and the '936 Patent could be either       |

| 18 | volatile or nonvolatile memory. As I explained,    |

| 19 | if it were nonvolatile memory, there would not     |

| 20 | be any benefit derived from the fact that it is    |

| 21 | nonvolatile.                                       |

| 22 | BY MS. VIDAL:                                      |

| 23 | Q. And the same is true for the claimed            |

| Ē  | GODMAR BACK                                          |

|----|------------------------------------------------------|

| 1  | MR. EDELL: Objection to form.                        |

| 2  | THE WITNESS: By "the claimed," you mean              |

| 3  | the claimed cache memory in the claim of the         |

| 4  | patent?                                              |

| 5  | BY MS. VIDAL:                                        |

| 6  | Q. That's correct.                                   |

| 7  | A. For claims, we apply a broader                    |

| 8  | interpretation than for the specification.           |

| 9  | Q. So then your answer would be yes to that?         |

| 10 | A. The answer would be yes to whether it             |

| 11 | could be either volatile or nonvolatile memory? I    |

| 12 | think it could be either way.                        |

| 13 | Q. I'd like to turn to Paragraph 46 of the           |

| 14 | '936 declaration. That would be Exhibit 3.           |

| 15 | A. Yes. Page 17?                                     |

| 16 | Q. That's correct. In this paragraph, you            |

| 17 | state that "the term 'preloading' as used in Claims  |

| 18 | 1, 18 and 19 of the '936 Patent, means transferring  |

| 19 | data from storage to memory in anticipation of       |

| 20 | immediate or near-in-time use." Do you see that?     |

| 21 | A. I do not see that. I don't state that.            |

| 22 | No. The paragraph reads that it is my opinion that   |

| 23 | a person of ordinary skill would have understood the |

| 24 | term "preloading" as used in Claims 1, 18 and 19 to  |

| 25 | mean transferring data from storage to memory in     |

|    | Page 30                                              |

Veritext Legal Solutions 866 299-5127 30

| 0  | Q. mat s correct.                                   |

|----|-----------------------------------------------------|

| 7  | A. For claims, we apply a broader                   |

| 8  | interpretation than for the specification.          |

| 9  | Q. So then your answer would be yes to that?        |

| 10 | A. The answer would be yes to whether it            |

| 11 | could be either volatile or nonvolatile memory? I   |

| 12 | think it could be either way.                       |

| 13 | Q. I'd like to turn to Paragraph 46 of the          |

| 14 | '936 declaration. That would be Exhibit 3.          |

| 15 | A. Yes. Page 17?                                    |

| 16 | Q. That's correct. In this paragraph, you           |

| 17 | state that "the term 'preloading' as used in Claims |

| 18 | 1, 18 and 19 of the '936 Patent, means transferring |

Ex. 2013 Page 48 of 145

#### Glossary

s into main memory mory when they are I to reside in virtual reside in main memr needed.

the kernel. 4.4BSD chine, repairing any on. See also crash

process as a result of

h an optional slash ated by slashes, and as with a slash, it is ins at the root direc*chname*, and the path process. A slash by the current working

low on a connection. but the send window tstanding. If no winv probe is sent. the system maps a

to as the *pmap* strucon and access tables y-management hardccess rights, in addi-

ts the unidirectional stream-oriented, reliwith the "1" symbol. im a to the standard (1b". tput of one process is

ystem to place pages

#### Glossary

**polling I/O** The normal mode for a descriptor whereby the system will block if a read request has no data available or a write request has no buffering available. A process can determine whether an I/O operation will block by polling the kernel using the *select* system call. The *select* system call can be requested to return immediately with the information or to block until at least one of the requested I/O operations can be completed. See also *nonblocking I/O*; *signal-driven I/O*.

- POSIX The standards group for P1003, the portable operating-system interfaces established by the IEEE. Its first established standard was the kernel interface, 1003.1, which was ratified in 1988.

- prefetching The retrieval of data before they are needed. Many machines prefetch machine instructions so that they can overlap the time spent fetching instructions from memory with the time spent decoding instructions.

- prepaging The prefetching of pages of memory. Prepaging is a technique used by virtual-memory systems to reduce the number of page faults.

- probing The operation of checking to see whether a hardware device is present on a machine. Each different type of hardware device usually requires its own technique for probing.

- process In operating systems, a task or thread of execution. In UNIX, user processes are created with the *fork* system call.

- process control block (PCB) A data structure used to hold process context. The hardware-defined PCB contains the hardware portion of this context. The software PCB contains the software portion, and is located in memory immediately after the hardware PCB.

- process group A collection of processes on a single machine that all have the same process-group identifier. The kernel uses this grouping to arbitrate among multiple jobs contending for the same terminal.