EXHIBIT 1102

# UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

# QUALCOMM INCORPORATED, GLOBALFOUNDRIES INC., GLOBALFOUNDRIES U.S. INC., GLOBALFOUNDRIES DRESDEN MODULE ONE LLC & CO. KG, GLOBALFOUNDRIES DRESDEN MODULE TWO LLC & CO. KG Petitioner

v.

DSS Technology Management, Inc. Patent Owner

> U.S. Patent No. 5,965,924 Claims 7-12, 15 and 17

# DECLARATION OF RICHARD BLANCHARD, PH.D. ON BEHALF OF PETITIONER

Exhibit 1102 Page 1 of 77

# **TABLE OF CONTENTS**

| I.                                              | Relev                              | Relevant Law7                                                                                                                                       |  |

|-------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                 | A.                                 | Claim Construction7                                                                                                                                 |  |

|                                                 | B.                                 | Anticipation                                                                                                                                        |  |

|                                                 | C.                                 | Obviousness                                                                                                                                         |  |

| II.                                             | Summary of Opinions10              |                                                                                                                                                     |  |

| III.                                            | Introduction to the '924 Patent11  |                                                                                                                                                     |  |

| IV.                                             | Brief                              | Brief Description of the Technology14                                                                                                               |  |

|                                                 | A.                                 | Overview of Transistor Fabrication14                                                                                                                |  |

|                                                 | 1.                                 | Basic Structure of Transistors14                                                                                                                    |  |

|                                                 | 2.                                 | Formation of Transistor Components16                                                                                                                |  |

|                                                 | 3.                                 | Local Interconnects17                                                                                                                               |  |

|                                                 | B.                                 | Overview of the '924 Patent18                                                                                                                       |  |

|                                                 | 1.                                 | Problem Disclosed in the '924 Patent                                                                                                                |  |

|                                                 | 2.                                 | Summary of Invention of the '924 Patent                                                                                                             |  |

|                                                 | 3.                                 | Prosecution History                                                                                                                                 |  |

| V. Overview of the Primary Prior Art References |                                    | view of the Primary Prior Art References                                                                                                            |  |

|                                                 | A.                                 | Overview of Sakamoto (Ex. 1103)25                                                                                                                   |  |

|                                                 | В.                                 | Overview of Cederbaum (Ex. 1104)27                                                                                                                  |  |

| VI.                                             | Claim Construction                 |                                                                                                                                                     |  |

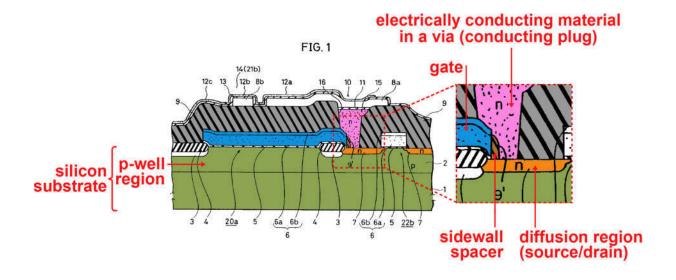

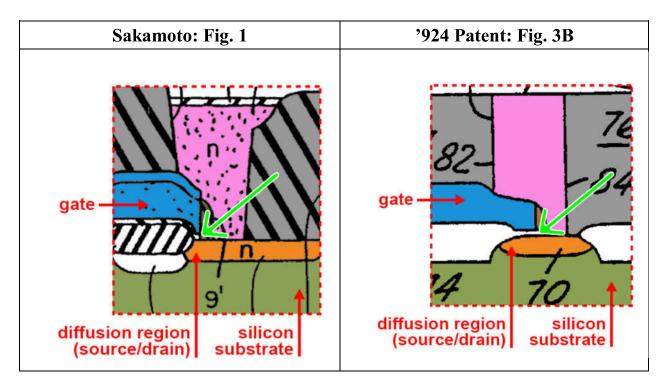

| VII.                                            | Level of Ordinary Skill In The Art |                                                                                                                                                     |  |

| VIII.                                           | Spec                               | Specific Grounds for Petition                                                                                                                       |  |

|                                                 | A.                                 | Ground I: Claims 7-9, 15 and 17 are anticipated by Sakamoto33                                                                                       |  |

|                                                 | 1.                                 | Independent Claim 7                                                                                                                                 |  |

|                                                 |                                    | Claim 8: "A method according to claim 7, wherein said diffusion gion is an N+ or a P+ region."                                                      |  |

|                                                 | m                                  | Claim 9: "A method according to claim 7, wherein said insulating aterial is selected from the group consisting of silicon oxide and silicon tride." |  |

U.S. Patent No. 5,965,924 Claims 7-12, 15 and 17

| 4. Claim 15: "A method according to claim 7, wherein said gate is a polysilicon gate." / Claim 17: "The method according to claim 7, wherein said gate comprises polysilicon."                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B. Ground II: Claims 10-12 are obvious in view of the combination of Sakamoto and Cederbaum                                                                                                                                                                                                                                                                                                                                           |

| 2. Claim 10: "a method according to claim 7, wherein said electrically conducting plug is a metal plug" / Claim 11: "a method according to claim 7, wherein said electrically conducting plug is preferably a refractory metal plug" / Claim 12: "a method according to claim 7, wherein said electrically conducting plug is formed of a material selected from the group consisting of titanium, tantalum, molybdenum and tungsten" |

| Availability for Cross-Examination                                                                                                                                                                                                                                                                                                                                                                                                    |

| Right to Supplement                                                                                                                                                                                                                                                                                                                                                                                                                   |

IX.

Х.

I, Richard Blanchard, declare as follows:

1. My name is Richard Blanchard.

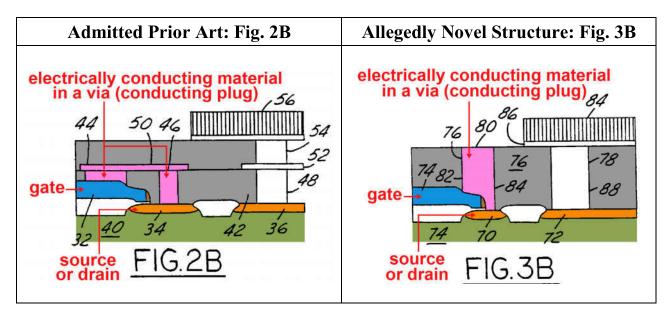

2. My academic credentials include both a Bachelor of Science Degree in Electrical Engineering (BSEE) and a Master of Science Degree in Electrical Engineering (MSEE) from the Massachusetts Institute of Technology in 1968 and 1970, respectively. I subsequently obtained a Ph.D. in Electrical Engineering in 1982 from Stanford University

3. I have worked or consulted for more than 40 years as an Electrical Engineer. My primary focus has been on the development, manufacture, operation, and use of devices and integrated circuits, the assembly of these devices and integrated circuits, products that use them, and their failures. My employment history following my graduation from MIT began at Fairchild Semiconductor in 1970. At Fairchild, my responsibilities included circuit and device design, process development, and product engineering in the Linear Integrated Circuits Department.

4. In 1974, I joined Foothill College as an Associate Professor in the Engineering & Technology Division. My responsibilities included developing a program in Semiconductor Technology as well as teaching other courses in the division. While at Foothill College, I co-founded two companies, Cognition and Supertex, and later joined Supertex as a Vice

President in 1978. At Supertex, I designed and developed discrete DMOS (double-diffused metal oxide semiconductor) transistors, as well as integrated circuits that contained DMOS transistors. At Supertex, I also supervised the in-house assembly area, which included responsibility for the associated manufacturing processes. I left Suptertex to join Siliconix in 1982, where I soon became Vice President of Engineering, with the responsibility for directing all of the company's product design and development. At Siliconix, I directed and contributed to the development of both discrete transistors and integrated circuits, including aspects of their assembly.

5. In 1987, I joined IXYS Corporation as a Senior Vice President with the responsibility for organizing an integrated circuit department. At IXYS, I developed integrated circuits that contained DMOS devices or that interfaced to DMOS devices. My responsibilities included the design, assembly, and testing of these integrated circuits.

6. These duties continued until 1991, when I left IXYS to set up Blanchard Associates, a consulting firm specializing in semiconductor technology, including intellectual property. Soon thereafter, I was invited to join Failure Analysis Associates, which I did in late 1991. At Failure

Analysis Associates, I investigated failures in electrical and electronic systems in addition to performing design and development consulting.

7. I left Failure Analysis in 1998 to join IP Managers, which later merged with Silicon Valley Expert Witness Group, now known as Thomson Reuters Expert Witness Services ("Thomson Reuters"). At Thomson Reuters, I work with companies on patent and trade secret matters. I also consult for a number of semiconductor companies, working with them to develop products and intellectual property, or assisting them in other technical areas through Blanchard Associates. Design and development projects that I have worked on range from the design and evaluation of specific components, to the selection of the technology appropriate for the fabrication of different subsystems of a system.

8. I am a member of a number of professional societies, including the Institute of Electrical and Electronic Engineers, the International Microelectronics and Packaging Society, the American Vacuum Society, the Electronic Device Failure Analysis Society, and the Electrostatic Discharge Society. A copy of my curriculum vitae (including a list of all publications authored in the previous 10 years) is attached as Appendix A.

9. I have reviewed the specification, claims and file history of U.S.Patent No. 5,965,924, as well as the petition for inter partes review of this patent:

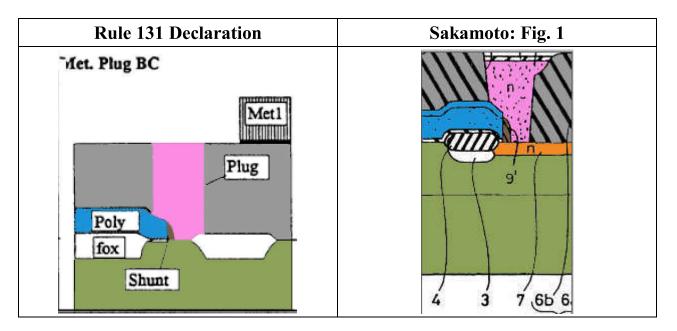

IPR2016-00290, including the Declaration of Dr. John C. Bravman. I understand that the '924 patent was filed on July 24, 1997, issued from a "continued prosecution application" ("CPA") of U.S. App. No. 08/561,951 and claims priority to an application filed on November 22, 1995. I understand that, for purposes of determining whether a publication will qualify as prior art, the earliest date that the '924 patent could be entitled to is November 22, 1995. However, I further understand that the prior assignee claimed a conception date of May 17, 1995 during prosecution of the '924 application. Amendment and Rule 131 Declaration dated Jan. 5, 1998 (Ex. 1106). Even under that conception date, the cited references are prior art and invalidate the '924 patent.

10. I have reviewed the following patents in preparing this declaration:

- U.S. Patent No. 5,475,240 ("Sakamoto") (Ex. 1103).

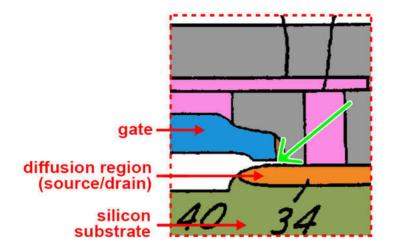

- U.S. Patent No. 5,100,817 ("Cederbaum") (Ex. 1104).

11. I have reviewed the above patents and any other publication cited in this declaration.

12. I have considered certain issues from the perspective of a person of ordinary skill in the art as described below at the time the '924 patent application was filed. In my opinion, a person of ordinary skill in the art for the '924 patent would have found the '924 patent invalid.

13. I have been retained by the Petitioner as an expert in the field of semiconductor device fabrication and design. I am working as an independent consultant in this matter and am being compensated at my normal consulting rate of \$375 per hour for my time. My compensation is not dependent on and in no way affects the substance of my statements in this Declaration.

14. I have no financial interest in the Petitioner. I similarly have no financial interest in the '924 patent, and have had no contact with the named inventor of the '924 patent.

#### I. RELEVANT LAW

15. I am not an attorney. For the purposes of this declaration, I have been informed about certain aspects of the law that are relevant to my opinions. My understanding of the law is as follows:

#### **A. Claim Construction**

16. I have been informed that claim construction is a matter of law and that the final claim construction will ultimately be determined by the Board. For the purposes of my analysis in this proceeding and with respect to the prior art, I have been informed that I should apply what is known as "the *Phillips* standard," rather than the broadest reasonable interpretation standard.

17. Specifically, I have been informed and understand that since the '924 patent expired on November 22, 2015, the *Phillips* standard applies for the

purposes of claim construction. I further understand that the *Phillips* standard means that claim terms are given their plain and ordinary meaning as understood by a person of ordinary skill in the art at the time of the invention in light of the claim language and the patent specification.

18. I have also been informed and understand that any claim term that lacks a definition in the specification is therefore given its plain and ordinary meaning as understood by one of ordinary skill in the art.

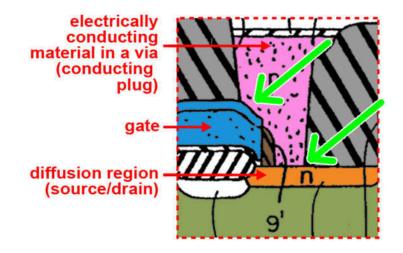

#### **B.** Anticipation

19. I have been informed and understand that a patent claim may be "anticipated" if each element of that claim is present either explicitly, implicitly, or inherently in a single prior art reference. I have also been informed that, to be an inherent disclosure, the prior art reference must necessarily disclose the limitation, and the fact that the reference might possibly practice or contain a claimed limitation is insufficient to establish that the reference inherently teaches the limitation.

# C. Obviousness

20. I have been informed and understand that a patent claim can be considered to have been obvious to a person of ordinary skill in the art at the time the application was filed. This means that, even if all of the requirements of a claim are not found in a single prior art reference, the claim is not patentable if the

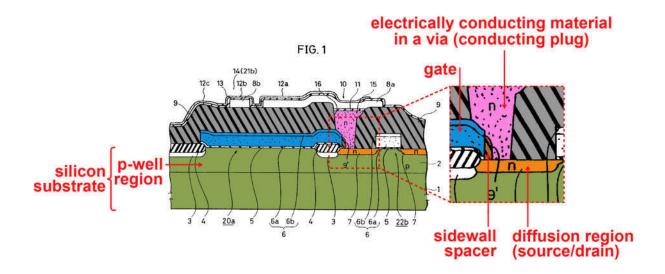

differences between the subject matter in the prior art and the subject matter in the claim would have been obvious to a person of ordinary skill in the art at the time the application was filed.

21. I have been informed and understand that a determination of whether a claim would have been obvious should be based upon several factors, including, among others:

- the level of ordinary skill in the art at the time the application was filed;

- the scope and content of the prior art; and

- what differences, if any, existed between the claimed invention and the prior art.

22. I have been informed and understand that the teachings of two or more references may be combined in the same way as disclosed in the claims, if such a combination would have been obvious to one having ordinary skill in the art. In determining whether a combination based on either a single reference or multiple references would have been obvious, it is appropriate to consider, among other factors:

whether the teachings of the prior art references disclose known concepts combined in familiar ways, which, when combined, would yield predictable results;

- whether a person of ordinary skill in the art could implement a predictable variation, and would see the benefit of doing so;

- whether the claimed elements represent one of a limited number of known design choices, and would have a reasonable expectation of success by those skilled in the art;

- whether a person of ordinary skill would have recognized a reason to combine known elements in the manner described in the claim;

- whether there is some teaching or suggestion in the prior art to make the modification or combination of elements claimed in the patent; and

- whether the innovation applies a known technique that had been used to improve a similar device or method in a similar way.

23. I understand that one of ordinary skill in the art has ordinary creativity, and is not an automaton.

24. I understand that in considering obviousness, it is important not to determine obviousness using the benefit of hindsight derived from the patent being considered.

# **II. SUMMARY OF OPINIONS**

25. It is my opinion that every limitation of the structures described in claims 7-12, 15 and 17 of the '924 patent are disclosed by the prior art, and are anticipated and/or rendered obvious by the prior art.

The following discussion and analysis is substantially the same as that of Dr. John C. Bravman in IPR2016-00290, supplemented with additional analysis and comments provided throughout this declaration.

#### **III. INTRODUCTION TO THE '924 PATENT**

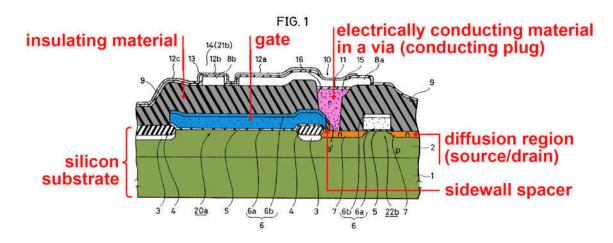

26. The '924 patent is directed to certain aspects of the structure and fabrication of transistors used in semiconductor and integrated circuit products such as microprocessors and memory. Transistors act as microscopic switches that turn on and off at extraordinarily high rates to enable aggregations of transistors (and other components) to process data. Transistors are made up of various structures including "contacts" that provide electrically conductive pathways into and out of certain structures within a transistor, and which thereby are used to connect transistors together.

27. The '924 patent is concerned with electrically connecting different transistor parts to each other in a particular way. Transistors typically have three terminals through which electrical signals may pass: a "source," a "drain," and a "gate." The '924 patent is concerned with connecting the gate of one transistor to, for example, the source or drain of a neighboring transistor.

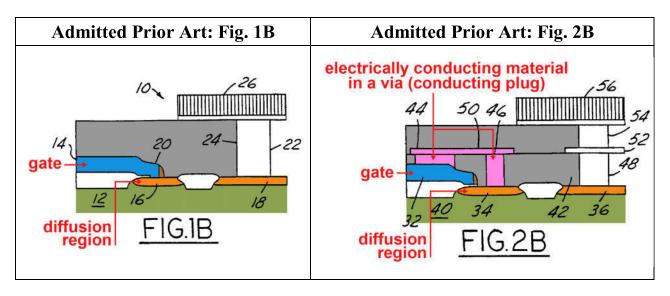

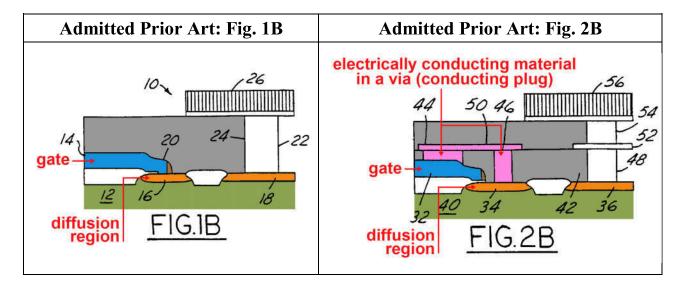

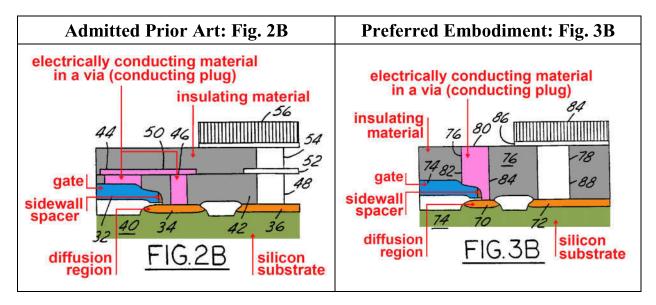

28. According to the specification of the '924 patent, there were many well-known ways of making electrical connections between different transistor parts. As shown in Figure 2B (below), for instance, one of the prior art ways of

connecting the components of two transistors was by using two electrical connections called "plugs"—one connected to the gate of one transistor, and the other connected to the source or drain of the other—and then connecting those plugs together. As shown in Figure 3B (below), the purported invention of the '924 patent was to replace the two plugs with one plug.<sup>1</sup>

29. In both the prior art (Figure 2B) and the allegedly novel structure of the '924 patent (Figure 3B), the gate is connected to a diffusion region (*i.e.*, a source or drain) by either two connected plugs, or a single plug. The patent does not claim that the one-plug structure provides any performance benefits over the two-plug structure. Instead, the benefit was that the one-plug structure was easier

<sup>&</sup>lt;sup>1</sup> All emphasis and annotations are added unless otherwise indicated.

to manufacture than the admitted prior art. '924 patent at 1:57-2:63, 4:18-5:12 (Ex. 1101).

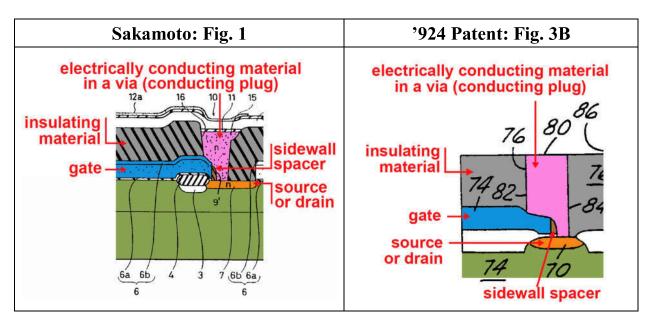

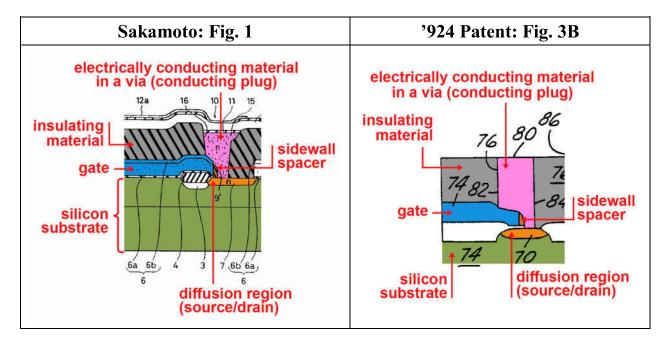

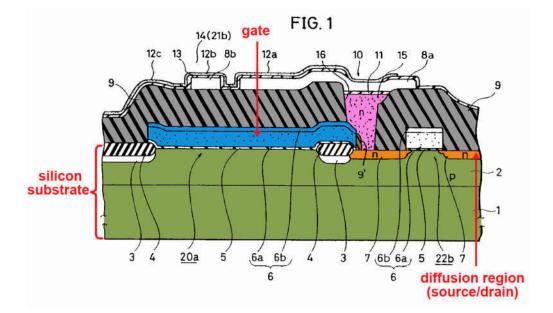

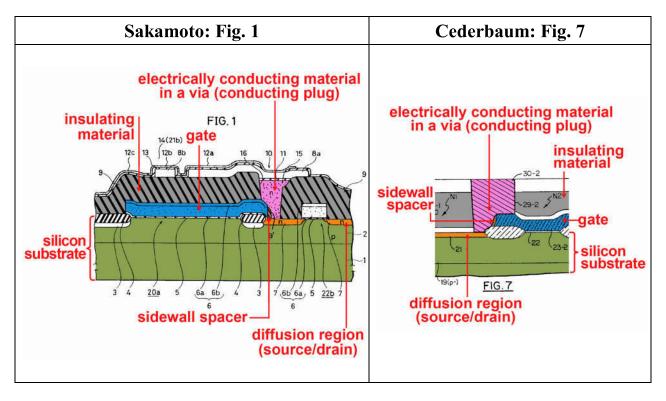

30. Long before the '924 patent's November 22, 1995 priority date, many others had already developed and used the exact same one-plug structure. U.S. Patent No. 5,475,240 ("Sakamoto"), for instance, which has an effective filing date of March 4, 1992, discloses the same one-plug structure that the '924 patent contends is novel. Specifically, as shown in the patents' respective figures, the one-plug structure of Sakamoto (Figure 1) is in all relevant aspects identical to the one-plug structure of the '924 patent (Figure 3B).

31. As shown, both structures include a gate connected to a source or drain through a single plug.

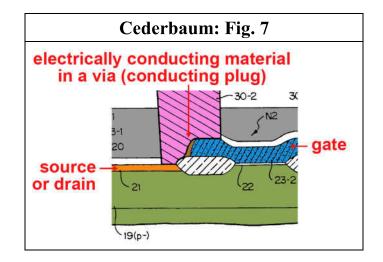

U.S. Patent No. 5,965,924 Claims 7-12, 15 and 17

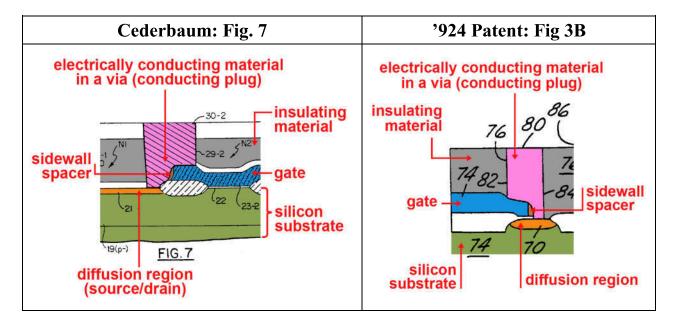

32. U.S. Patent No. 5,100,817 ("Cederbaum") issued on March 31, 1992,

and, just like the '924 one-plug structure, discloses a single conducting plug connecting a gate to a source or drain.

33. Sakamoto and Cederbaum were not at issue during prosecution of the '924 patent. These references anticipate and/or render obvious claims 7-12, 15 and 17 of the '924 patent.

# IV. BRIEF DESCRIPTION OF THE TECHNOLOGY

34. The '924 patent generally relates to the field of semiconductor integrated circuit manufacturing and claims particular structures for transistors in semiconductors, as well as a related method for manufacturing those structures.

# A. Overview of Transistor Fabrication

1. Basic Structure of Transistors

35. Semiconductor integrated circuits, such as microprocessors and computer memory, are typically made up of hundreds of millions (and in some

cases billions) of microscopic structures called transistors. Transistors act as microscopic switches that turn on and off at extraordinarily high rates to enable aggregations of transistors (and other components) to process data.

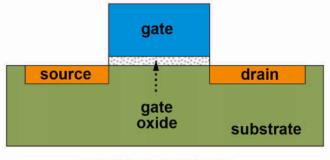

36. As shown in the figure below, transistors typically include three primary "electrodes" or "terminals"—a "gate," a "source," and a "drain":

**BASIC TRANSISTOR**

37. The source and drain regions (also referred to as "diffusion regions") are transistor components that emit (source) and receive (drain) current/carriers when the transistor is "on." The gate typically sits between the source and drain and is a terminal that can have a voltage applied to it that in turn causes a current to flow between the source and drain. As of the time of the invention of the '924 patent, the source and drain of a transistor were typically formed in the surface of a semiconductor "substrate," while the gate typically sat above the substrate and separated from it by a thin layer of insulator ("gate oxide").

#### 2. Formation of Transistor Components

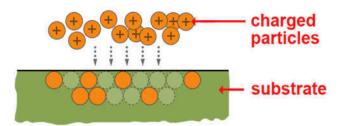

38. Transistor fabrication typically starts with a silicon substrate. In typical planar transistors, the source and drain regions ("diffusion regions") are created by implanting regions of the substrate with ions (charged atomic particles) of different materials—called "dopants" or "impurities". (Once implanted the ions become neutral atoms). This process—referred to as "doping" because it dopes the silicon substrate with atomic particles that have additional charge carriers—is shown below:

A mask can be used for directing the charged particles to specific locations in the substrate.

39. Structures can then be formed above the substrate by depositing layers of other materials onto the substrate. A gate electrode, for example, is formed by first growing or depositing a "gate oxide" (an insulator) on the substrate followed by depositing a conductive material (metal or polysilicon) on top of the gate oxide. The conductive material acts as the gate, and the gate oxide creates a layer of isolation between the gate and the source/drain regions ("S/D regions" or "diffusion regions").

U.S. Patent No. 5,965,924 Claims 7-12, 15 and 17

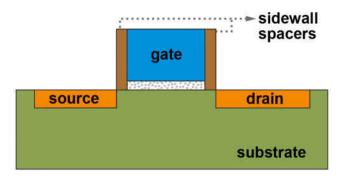

40. Insulating materials may then be deposited around and over the gate and the S/D regions to maintain electrical isolation where desired. Sidewall spacers, for instance, can be formed on each side of the gate electrode as shown below:

As was known as of the time of the '924 invention, such sidewall spacers help to prevent direct electrical contact between the gate electrode and nearby components and thus help to prevent short-circuits.

#### 3. Local Interconnects

41. Many transistors can be connected together to form electronic circuits. For certain types of circuits, it is sometimes useful to connect the gate of one transistor to a diffusion region (the source or drain) of a nearby transistor. This type of connection is called a "local interconnect," because connections are made locally between nearby transistors.

42. According to the specification of the '924 patent, a variety of different types of local interconnects were well-known prior to the purported invention. For example, as shown in Figure 1B of the '924 patent, one well-known way to form a

U.S. Patent No. 5,965,924 Claims 7-12, 15 and 17

local interconnect was to position the gate in a location where it physically touches the diffusion region on one side, creating an electrical connection. As shown in Figure 2B of the '924 patent, another well-known way to make a local interconnect was to place one electrically conductive "plug" above the gate and another "plug" above the diffusion (e.g., source or drain) region, and then electrically connect the two plugs together.

43. The '924 patent acknowledges that both examples were known prior art. *See* '924 patent at Figs. 1A, 1B, 2A, 2B, 1:25-2:45, 3:30-35 (Ex. 1101).

#### B. Overview of the '924 Patent

44. The '924 patent issued from U.S. App. No. 08/900,047, which was filed on July 24, 1997, and claims priority to an application filed on November 22, 1995. '924 patent at cover page (Ex. 1101). The invention of the '924 patent is a single plug to connect different transistor parts. '924 patent at 2:32-67, 4:18-5:12 (Ex. 1101).

# 1. Problem Disclosed in the '924 Patent

45. The '924 patent addresses manufacturing inefficiencies in forming local interconnects. Figures 1 and 2 of the '924 patent are prior art and show examples of two well-known types of local interconnects that (according to the '924 patent) are inefficient to manufacture.

46. Figure 1B shows a "buried contact" local interconnect structure in which the gate directly touches—*i.e.*, is in direct electrical connection with—a diffusion region. According to the '924 patent, the problem with this structure is that the gate has to be implanted with the same type of impurities as those implanted in the diffusion region. *See* '924 patent at 1:57-2:11 (Ex. 1101). But most manufacturers use a variety of different types of impurities in different transistors. To use the "buried contact" approach, a manufacturer would have to ensure that any two transistors connected using this approach use the same impurities, which complicates the manufacturing process. *See id*.

47. Figure 2B shows another prior art local interconnect structure, using what is called a "strapping" technique. To form this "strapping" local interconnect structure, a manufacturer creates two electrically conductive plugs (numbers 44 and 46)—one above the gate and one above a diffusion region. The manufacturer then places an electrically conductive "local strap" (number 50) on top of the plugs, electrically connecting the two plugs together. This local strap is also sometimes called a "shunt" or a "shunt layer." In combination, the two plugs and the local strap electrically connect the gate to a diffusion region. *See* '924 patent at 2:12-32 (Ex. 1101). According to the '924 patent, the problem with the strapping technique is that it requires a large number of manufacturing process steps, as well as significant space to accommodate the two plugs and the local strap. *See* '924 patent at 2:33-41 (Ex. 1101).

# 2. Summary of Invention of the '924 Patent

48. The '924 patent's claimed structure includes nearly identical

components as the prior art described in the specification. Specifically, both the claimed structure and the prior art include a substrate, a gate, a diffusion region, a sidewall spacer adjacent to the gate, and an insulating material.

49. As shown in Figures 2B and 3B, in both the prior art of the '924 patent and the structure of the disclosed embodiment, the gate is connected to the diffusion region (source or drain), by either two connected plugs, or a single plug. The diffusion region is located in a substrate and is not directly connected to the gate. The gate is substantially covered by an insulating material.

50. The only feature that the patent describes as novel, which is shown in Figure 3B, is the use of a single metal plug to connect the gate and the diffusion region, rather than connecting the two components directly (as in the prior art

"buried contact" technique (Figure 1B)) or using two plugs (as in the prior art "strapping" technique (Figure 2B)). '924 patent at 2:64-67, 3:35-36 (describing Figure 3B as "a cross-sectional view of a preferred embodiment of the present invention."), 4:18-5:12, claims 1, 7 (Ex. 1101); *see also id.* at 2:42-63.

#### 3. Prosecution History

51. The '924 patent issued from a "continued prosecution application" ("CPA") of U.S. App. No. 08/561,951. CPA Request dated Feb. 10, 1999 (Ex. 1105). During prosecution of the '924 patent, the Applicant tried to antedate a prior art reference, based on a lab notebook dated May 17, 1995. Amendment and Rule 131 Declaration dated Jan. 5, 1998 (Ex. 1106). For purposes of this Petition, I understand that the references relied upon by Petitioner all qualify as prior art even if the Patent Owner could ultimately prove a conception date as early as May 17, 1995.

52. According to this lab notebook, the novelty of the '924 invention arises from the use of a single plug—which is what allegedly leads to fewer processing steps as compared to known prior art techniques. *See* Rule 131 Declaration dated January 5, 1998, Exhibit A ("By *placing a metallic plugged contact* where poly is required to shunt to diffusion, contacts to [different types of] diffusion can be achieved .... [T]his will require no more layout area than the traditional buried contact. This method has potential [manufacturing] process step

savings of 8-11 steps over Trad. BC [traditional buried contact local interconnect (as shown in Figure 1B of the '924 patent)] and 6-8 steps over strapping [local interconnect (as shown in Figure 2B of the '924 patent)].") (Ex. 1106).

53. However, during prosecution, rather than relying on this "single plug" structure, the Applicant relied on other alleged differences to overcome the prior art applied by the Examiner. The present petition relies on prior art that was not before the Examiner. This prior art teaches not only the "single plug" aspect of the claims, but also all of the additional minor differences that the Applicant used to try to distinguish the Examiner's prior art.

#### a. The "sidewall spacer" limitations

54. The Examiner rejected the original claims under 35 U.S.C. § 102(e) based on U.S. Patent No. 5,451,434 to Nicholls ("Nicholls"). Office Action dated Nov. 7, 1996 at p. 3 (Ex. 1107). Nicholls taught a single metal plug that connects a diffusion region and a gate. In order to overcome the rejection, the Applicant added a limitation to the claims requiring a sidewall spacer adjacent to the gate. Amendment dated June 9, 1997 at pp. 2-3 (Ex. 1109). Nicholls expressly teaches the placement of a sidewall during manufacture, but also teaches that the sidewall can be completely or "partially removed" in a later manufacturing step. Nicholls at 4:25-32 (Ex. 1108). The Applicant overcame the rejection by arguing that the removal of the sidewall during manufacturing taught away from retaining a

sidewall spacer adjacent to the gate. Amendment dated June 9, 1997 at pp. 3-4 (Ex. 1109). The prior art relied upon in this petition teaches the "sidewall spacer" limitation.

#### b. Direct electrical connection

55. The Examiner also rejected the claims under 35 U.S.C. § 102(e) based on U.S. Patent No. 5,541,427 to Chappell ("Chappell"). Office Action dated February 24, 1998 (Ex. 1110). Chappell taught a single metal plug that connects to both a diffusion region and a gate region. Chappell at 4:38-48 (Ex. 1111). The Applicant overcame the rejection by arguing that the metal plug of Chappell purportedly contacts a portion of the gate region that is not conductive, rather than the conductive portion of the gate itself. *See* Amendment dated April 23, 1998 at p. 4 ("when the opening 42 is filled with an electrically conductive material, there is **no contact** to the electrically conductive portion of the gate stack"") (emphasis in original) (quoting Chappell at 4:38-48) (Ex. 1112). The prior art references relied upon in this petition teach a direct electrical connection between the diffusion region and the electrically conductive portion of the gate.

# **V. OVERVIEW OF THE PRIMARY PRIOR ART REFERENCES**

56. The claimed invention of the '924 patent—using a single plug to electrically connect the gate to the diffusion region—was well-known as of the May 17, 1995 purported conception date.

#### A. Overview of Sakamoto (Ex. 1103)

57. Sakamoto was filed on August 19, 1994, as a continuation of an earlier application filed on March 4, 1992, and issued on December 12, 1995. I understand that Sakamoto is prior art to the '924 patent under 35 U.S.C. § 102(e).

58. Sakamoto is directed to precisely the same problem as the '924 patent —how to effectively and efficiently connect different transistor portions together and discloses precisely the same solution claimed in the '924 patent—using a single plug. Sakamoto at 4:45-49 ("The first interconnection structure comprises a silicon plug layer embedded within an opening formed in the interlevel insulating layer and connected to both gate electrode of the first MOS drive transistor and source/drain region of the second MOS transfer transistor...") (Ex. 1103); *see also id.* at 1:13-14. Figure 1 of Sakamoto shows a structure with the same components arranged in the same way as shown in Figure 3B of the '924 patent. *Id.* at Fig. 1; '924 patent at Fig. 3B (Ex. 1101).

59. Both Figure 1 of Sakamoto and Figure 3B of the '924 patent show a cross-sectional structure with a single plug. The plug fills an opening (labeled 16 in Sakamoto) containing a sidewall spacer and directly electrically connects a diffusion region to a gate. The diffusion region is located in a substrate and is not directly connected to the gate. The gate is also substantially covered by an insulating material. *See* Sakamoto at 6:52-58 ("An opening 16 is formed in an interlevel insulating layer 9. An n+ source/drain region 7 of an n channel MOS transfer transistor 22b and a gate electrode 6 of an n channel MOS drive transistor 20a are exposed at the bottom of opening 16. A plug layer 15 of polycrystalline silicon directly connected to the n+ source/drain region 7 and gate electrode 6 is embedded within opening 16."), 7:47-51 ("An opening 16 for direct contact is formed in interlevel insulating layer 9 ... formation of the opening 16 leaving a

sidewall spacer 9' from the interlevel insulating layer 9 ..."), 7:26-27 ("Oxide films 5 form gate oxide films 5,5 of MOS transistors 20a, 22b.") (Ex. 1103); *see also* '924 patent at 3:46-4:17 (Ex. 1101). Thus, Sakamoto and the '924 patent both solve the same problem of connecting different transistor portions (e.g., source/drain to gate) by using a single plug interconnect. Sakamoto at 6:49-7:13 (Ex. 1103).

#### **B.** Overview of Cederbaum (Ex. 1104)

60. Cederbaum issued on March 31, 1992, and I understand that it is prior art under 35 U.S.C. § 102(b). Figure 7 of Cederbaum also discloses a structure that includes components arranged in a way that is identical in all relevant aspects as the structure in Figure 3B of the '924 patent. Cederbaum at Fig. 7 (Ex. 1104); '924 patent at Fig. 3B (Ex. 1101).

61. Both Figure 7 of Cederbaum and Figure 3B of the '924 patent show a single plug (which Cederbaum calls a "contact stud"). The plug fills an opening (labeled 28-2 (Figure 6) in Cederbaum) containing a sidewall spacer and directly connects the source/drain region to the gate. *See* Cederbaum at Figs. 4-7, 7:33-49 (Figs. 4-7 show "active regions 21... to constitute the source and drain regions" and "[n]umeral[] ... 23-2 designate[s] ... the gate electrodes ... ."), 7:49-57 ("Oxide sidewalls or spacers 24 have been formed on the lateral sides of the polysilicon gate electrodes for a better definition of the channel length of NFETs.") (Ex. 1104). The diffusion region is located in a substrate, and not directly connected to the gate, which is substantially covered by the insulating material. Cederbaum at 7:33-40 ("The starting material consists of a conventional P<sup>+</sup> silicon substrate 18 having a P<sup>-</sup> epitaxial layer 19.... N<sup>+</sup> implanted active regions 21 have

been formed in the epitaxial layer 19 to constitute the source and drain regions...."), 8:26-50 (explaining the formation of the insulating phosphosilicate glass (PSG) layer 26 over the gate and substrate) (Ex. 1104). The contact stud is created by filling the opening with a "highly conductive material" that is "typically a metal." *Id.* at 9:32-34, 9:35-43 ("Prior to tungsten (W) filling, a titanium (Ti) layer is deposited" followed by "a thin titanium nitride (TiN).").

#### VI. CLAIM CONSTRUCTION

62. The '924 patent expired on November 22, 2015. Accordingly, as noted above, I understand that I should apply the claim construction based on the *Phillips* standard rather than the broadest reasonable interpretation standard applicable to non-expired patents.

63. The term "diffusion region in a silicon substrate" is an element of all challenged claims. I conclude that the term should be construed to mean a "conductive terminal region, such as a source or drain, that contains dopants implanted in the silicon substrate." In pending litigation with a Petitioner, I understand that the Patent Owner has proposed to construe the term as a "conductive terminal region such as a source or drain in a silicon substrate." The Patent Owner thus agrees with me that the term requires a conductive terminal region, such as a source or drain in a silicon substrate. As a result, the only dispute between the Patent Owner and myself is whether the diffusion region

"contains dopants implanted in the silicon substrate." The patent makes clear that it does.

64. The plain language of the claims requires the diffusion region to be formed in the silicon substrate. Claim 1, for example, requires a "diffusion region formed in said [silicon] substrate." '924 patent at claim 1 (Ex. 1101). Similarly, claim 7 requires a "diffusion region in a silicon substrate." *Id.* at claim 7. The specification then explains, in a section describing "[t]he present invention," that the diffusion region is formed in the substrate by implanting dopants in the substrate:

The present invention provides a semiconductor structure that has a metal plug local interconnect (or shunt) for connecting a polysilicon gate to a diffusion region in a structure and a method of forming such a semiconductor structure.

Referring initially to FIGS. 3A and 3B wherein an enlarged top view and a cross-sectional view of the *present invention* metal plug local interconnect is shown, respectively. Diffusion regions 70 and 72 of either *N*+ *or P*+ *doping* are first formed by an *ion implantation* process in the *surface of the silicon substrate* 74.

'924 patent at 3:40-51 (Ex. 1101); *see also id*. at 1:36-38 (explaining that the "ion implantation process ... increase[s] the surface dopant concentration" in substrate),

1:21-22 (describing "region doped by impurity ions in a semiconductor substrate"). The '924 patent does not describe any way of forming diffusion regions in a silicon substrate other than by implanting dopants in the substrate. Accordingly, the '924 patent makes clear that the claimed diffusion regions contain dopants implanted in the substrate.

Moreover, at the time of the alleged invention of the '924 patent, one 65. skilled in the art would have readily understood that a diffusion region is a conductive terminal region, such as a source or drain, that contains dopants implanted in the substrate. In order to form a diffusion region in a substrate, the dopants need to be inserted into the substrate. As the '924 patent explains, at the time of the alleged invention, this was done by implanting dopants into the substrate. This is confirmed by contemporaneous prior art references. Sakamoto and Nicholls, for example, teach the use of ion implantation to form a diffusion region. Sakamoto at 7:32-38 ("N type impurity *ion* ... is *implanted* ... by an ion implantation method.... Thus, *n*+ *source/drain regions* ... are formed.") (Ex. 1103); Nicholls at 2:64-66 ("As shown in FIG. 1b, a *dopant* is then *implanted* into the silicon substrate so as to form active silicon implant regions 8, 10"), 3:55-4:13 (Ex. 1108).

66. Accordingly, the term "diffusion region in a silicon substrate" should be construed to mean a "conductive terminal region, such as a source or drain, that contains dopants implanted in the silicon substrate."<sup>2</sup>

#### VII. LEVEL OF ORDINARY SKILL IN THE ART

67. In my opinion, a person of ordinary skill in the art at the time of the alleged invention would have had at least a B.S. degree in electrical engineering or materials science (or equivalent experience), and would have at least two or three years of experience with semiconductor device fabrication and design. I met and/or exceeded these requirements for one of ordinary skill in the art at the time of the filing of the '924 patent.

<sup>&</sup>lt;sup>2</sup> I am informed and understand that in pending litigation between the Patent Owner and a Petitioner, the parties have proposed competing constructions for one additional limitation. I have reviewed these competing constructions and determined that the prior art meets these limitations under either party's construction, so I have not attempted to construe them for the purposes of this petition. The prior art also discloses the required "diffusion region in a silicon substrate" limitation under either party's construction.

# **VIII. SPECIFIC GROUNDS FOR PETITION**

68. The sections below demonstrate in detail how the prior art discloses the limitations of the challenged claims of the '924 patent, and how those claims are anticipated and/or rendered obvious by the prior art.

# A. Ground I: Claims 7-9, 15 and 17 are anticipated by Sakamoto

# 1. Independent Claim 7

69. Sakamoto discloses each and every element of claim 7 and thus, anticipates the claim under 35 U.S.C. § 102(e).

# a. "A method of forming a local interconnect in a semiconductor structure, comprising the step of:"

70. Sakamoto expressly discloses a method of forming a local interconnect by describing a series of "[s]teps of manufacturing the memory cell of the SRAM shown in FIG. 1." Sakamoto at 7:14-15 (Ex. 1103); *see also id.* at 7:16-8:52. One skilled in the art would understand that the SRAM memory cell of Sakamoto discloses "a semiconductor structure." Sakamoto at Fig. 1, 6:39-8:52 (describing Figure 1), Title ("Contact structure of an interconnection layer for a *semiconductor device* and a multilayer interconnection SRAM"), 1:13-16 ("The present invention relates to improvement of a contact structure of an interconnection in a region having steps in *a semiconductor device* having a multilayer interconnection structure.") (Ex. 1103); *see also id.* at claims 1-9, Abstract, Title, 1:18-3:35, 3:60-4:2, 5:1-18, 5:33-50, 13:13-25.

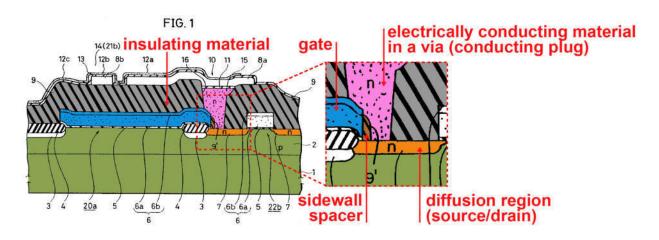

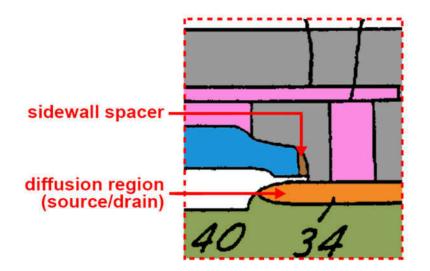

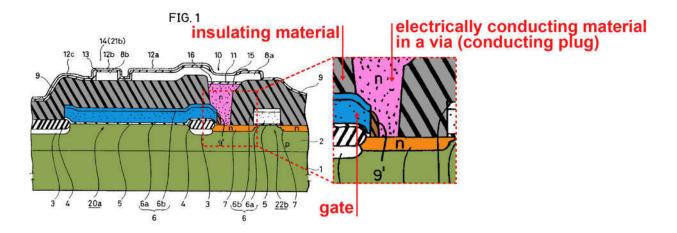

71. Figure 1 of Sakamoto (shown below) discloses a local interconnect structure:

Sakamoto at Fig. 1, 6:39-8:52 (describing Figure 1), claims 1-9, 3:55-57 (an "object of the present invention is to provide a method of manufacturing an interconnection having an interconnection structure...."), Title, Abstract, 1:13-16, 3:38-59 (Ex. 1103).

- b. [a]: "depositing an electrically conducting material in a via exposing at least a portion of a gate, a sidewall spacer adjacent to said gate and a portion of a diffusion region such that said electrically conducting material contacts and provides electrical communication between said gate and said diffusion region"

- 72. Sakamoto discloses the claimed electrically conducting material.

Figure 1 (which is the structure formed by the manufacturing method disclosed in Sakamoto) shows (and Sakamoto explains) depositing an electrically conducting

material (plug layer 15) in a via (opening 16):

Sakamoto at Fig. 1 (Ex. 1103); *see also id.* at Figs. 2-5, claims 1, 4, and 7, 6:49-7:14 ("An opening 16 is formed in an interlevel insulating layer 9 .... A plug layer 15... directly connected to the n+ source/drain region 7 and gate electrode 6 is embedded within opening 16."), 7:15-8:12 (plug layer 15 is formed when "[p]olycrystalline silicon layer 15a is deposited ... to fill opening 16 [and] is etched, leaving a portion of the ... layer only within opening 16....").

73. As shown in the figure above, absent the conducting material 15, the via exposes at least a portion of the gate (gate electrode 6), a sidewall spacer (sidewall spacer 9') that is adjacent to the gate (gate electrode 6) and a portion of a diffusion region (n+ source/drain region 7). *Compare* Sakamoto at Fig. 2 (showing portion of gate electrode 6, sidewall spacer 9' and portion of n+ source/drain region 7 exposed in opening 16 during manufacturing process before plug 15 is

formed) *with* Fig. 4 (showing plug 15 covering portion of gate electrode 6, sidewall spacer 9' and portion of n+ source/drain region 7 later in the process) (Ex. 1103). *See also id.* at Fig. 1, 6:52-55 ("[a]n n+ source/drain region 7 ... and a gate electrode 6 ... *are exposed* at the bottom of opening 16."), 7:46-50 ("a sidewall spacer 9" is located in the opening 16), 2:49-52, claims 4, 6, 7 and 9. Because Sakamoto teaches the source/drain 7 region and gate electrode 6 are "exposed" by opening 16, the sidewall spacer 9' is also exposed by the opening 16.

74. Figure 1 also shows (and Sakamoto explains) that the electrically conducting material (plug layer 15) contacts and provides direct electrical communication between the gate and the diffusion region:

Sakamoto at Fig. 1, 6:49-7:14 ("An opening 16 is formed.... A plug layer 15 of polycrystalline silicon *directly connected* to the n+ source/drain region 7 and gate electrode 6 is embedded within opening 16. N type impurity ... is introduced into

polycrystalline silicon plug layer 15 *in order to provide conductivity*."), 1:47-57 (Ex. 1103). As Figure 1 shows, the plug layer 15 directly touches both of those elements and is "electrically conducting material." *Id.* at Fig. 1, 6:56-61; *see also id.* at 6:66-7:13, 7:47-50, 7:53-61, claims 1-4, 6, 7 and 9.

## c. [b]: "said semiconductor structure comprising said diffusion region in a silicon substrate"

75. As discussed above in the Claim Construction section, the term "diffusion region in a silicon substrate" should be construed as a "conductive terminal region, such as a source or drain, that contains dopants implanted in the silicon substrate." Sakamoto discloses the claimed diffusion region.<sup>3</sup>

76. Figure 1 of Sakamoto discloses a semiconductor structure comprising the diffusion region (n+ source/drain region 7) in a silicon substrate (silicon substrate 1 with p-well region 2).

<sup>3</sup> Even the '924 patent notes that a diffusion region in a silicon substrate was known to a person of ordinary skill in the art at the time of the '924 patent. *See* '924 patent at prior art Fig. 2B, 2:15-20 ("a polysilicon gate 32 is first formed without direct contact with the diffusion region 34 and 36 in a silicon substrate 40.") (Ex. 1101).

Sakamoto at Fig. 1 (Ex. 1103).

77. As shown in Figure 1 above, the p-well region 2 is formed below the top surface of the silicon substrate 1, and the source/drain region 7 is formed below the top surface of the p-well region 2 (and thus below the top surface of the substrate). *See* Sakamoto at Fig. 1 (Ex. 1103); *see also id.* at 2:23-29 ("[a]n n channel MOS drive transistor 20a and an n channel MOS transfer transistor 22b each comprises n+ source/drain regions 7, 7, a gate oxide film 5 and gate electrode 6."), claim 1 ("...said first MOS transfer transistor and said second MOS transfer transfer transistor being formed *on the main surface of the silicon substrate ... a source/drain region* of said second MOS transfer transistor...*"*), Title, Abstract, 1:13-16, 2:23-29, 3:60-4:2, 4:20-67, 5:1-18, 5:33-50, 6:39-61, 7:14-39, 12:57-58, 13:13-25.

38

Sakamoto teaches that the diffusion region is a "conductive terminal 78. region, such as a source or drain," because it constitutes a source/drain region 7 of a transistor and electrically connects the transistor to other components in the semiconductor structure. Sakamoto at 6:51-61 ("An n+ source/drain region 7 of an n channel MOS transfer transistor 22b and a gate electrode 6 of an n channel MOS drive transistor 20a are exposed at the bottom of opening 16. A plug layer 15 of polycrystalline silicon directly connected to the n+ source/drain region 7 and gate electrode 6 is embedded within opening 16. N type impurity... is introduced into polycrystalline silicon plug layer 15 in order to provide conductivity."), claim 1 ("...said first MOS transfer transistor and said second MOS transfer transistor being formed on the main surface of the silicon substrate ... a source/drain region of said second MOS transfer transistor... a source/drain region of said first MOS transfer transistor...") (Ex. 1103).

79. Sakamoto further teaches that the diffusion region contains dopants implanted in the silicon substrate. Sakamoto at 7:17-21 ("p type impurity *is implanted in a main surface of a silicon substrate 1*… Subsequently, implanted p type impurity is *diffused to the depth* of about 2-3 μm *from the main surface of substrate 1* by heat treatment to *form a p well 2*."), 7:32-38 ("N type impurity ion

39

... *is implanted into p well 2* by an ion implantation method... Thus, n+ source/drain regions 7 ... are formed.") (Ex. 1103).<sup>4</sup>

80. Finally, one skilled in the art would understand that Sakamoto teaches that the silicon substrate is the silicon substrate 1 with p-well region 2 for several reasons. Sakamoto at Fig. 1 (Ex. 1103).

81. First, although Figure 1 shows a line delineating the p-well region 2, the text of Sakamoto makes clear to one skilled in the art that the p-well region 2 is a part of the silicon substrate 1 because the "p well 2" is formed in the "surface of substrate 1." *Id.* at 7:17-21 ("p type impurity *is implanted in a main surface of a silicon substrate 1*… Subsequently, implanted p type impurity is *diffused to the depth* of about 2-3 µm *from the main surface* of substrate 1 by heat treatment to

<sup>&</sup>lt;sup>4</sup> I am informed and understand that in pending litigation, the Patent Owner has proposed to construe "diffusion region a silicon substrate" as "conductive terminal region such as a source or drain in a silicon substrate." Sakamoto teaches the Patent Owner's construction as well because, as I explained above, it teaches a diffusion region that is a conductive terminal region such as a source or drain (Sakamoto at 6:51-61 (Ex. 1103)) and that is in the silicon substrate (*id.* at Fig. 1, 7:17-38). Accordingly, even under the Patent Owner's construction, Sakamoto discloses this claim limitation.

*form a p well 2*."), 2:22-26; *see also id*. at 1:19-24, 4:14-19, 4:20-67, 6:39-48 (explaining the similarity between Figure 1 and background Figure 28), 7:40-43, 8:13-17, and claims 1, 4 and 7.

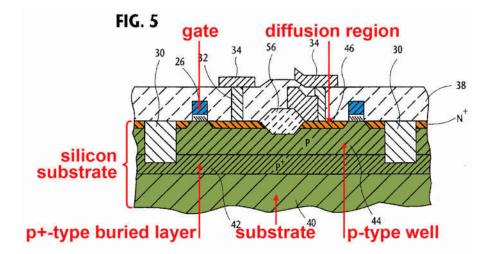

82. Second, during prosecution of the parent application for the '924 patent, the Examiner similarly considered a p-type well formed in a silicon substrate to be part of the substrate, even though the relevant prior art figure shows them delineated with different labels. Specifically, as shown below in Figure 5 of U.S. Patent No. 5,453,640 ("Kinoshita") (Ex. 1113), the prior art disclosed a diffusion region 46 that is formed within the p-type well 44 and shows the gate electrode 26 formed on a top surface of the p-type well 44:

Kinoshita at Fig. 5 (Ex. 1113); *id.* at 4:20-35 (identifying gate electrode 26, substrate 40, buried layer 42, p-type well 44, and diffusion region 46 in Figure 5), 3:34-35. Confirming that the Examiner considered the p-type well to be part of the substrate, the Examiner concluded that Figure 5 discloses "a semiconductor device

comprising: a silicon substrate (40), a diffusion region (46) *formed within* said substrate, [and] a polysilicon gate electrode (26) *formed on a top surface of* said substrate ....." April 17, 1996 Office Action at 3 (Ex. 1117). In my opinion this is consistent with what a person of ordinary skill in the art would understand.

83. In responding to the Examiner's rejection, the Applicant did not dispute the Examiner's assertion that the p-type well 44 was part of the substrate 40. In fact, the Applicant expressly acknowledged that another separately delineated layer in Figure 5—the buried layer 42—is also part of the substrate 40. *See* Amendment dated August 14, 1996 at 4 ("Kinoshita further teaches a block of static memory cells using CMOS transistors, wherein metal interconnections, e.g., ground lines for the CMOS transistors, are simplified by *using buried layers in the substrate*....") (Ex. 1114).

84. Third, the line delineating the p-well region 2 part of silicon substrate 1 is not present in all figures of Sakamoto, and Sakamoto elsewhere explicitly shows that regions, such as well regions, are formed in silicon substrate 1 (making clear that p-well region 2 is a part of the silicon substrate). *See* Sakamoto at Fig. 25, 12:57-58 ("On a surface of a silicon substrate 1, for example, an n type impurity region 30 is formed."), claim 1 ("…said first MOS transfer transistor and said second MOS transfer transistor being formed *on the main surface of the silicon substrate* … a source/drain region of said second MOS transfer transistor...

42

a source/drain region of said first MOS transfer transistor...") (Ex. 1103). Thus, one skilled in the art would understand that the p-well region 2 is part of silicon substrate 1 in the semiconductor structure disclosed in Sakamoto.

# d. [c]: "said gate being on said substrate juxtaposed to but not contacting said diffusion region"

85. Sakamoto discloses a gate (gate electrode 6) being on the substrate (silicon substrate 1 with p-well region 2).<sup>5</sup>

<sup>5</sup> Sakamoto shows the gate on top of a "field oxide film 4." Sakamoto at 7:17-29 (Ex. 1103). Applicant's purported conception documents also show the gate over the same field oxide (labeled "fox"). Accordingly, Sakamoto's gate is on the substrate, just like the '924 patent's gate is on the substrate.

Rule 131 Declaration, Exhibit A (Ex. 1106); Sakamoto at Fig. 1 (Ex. 1103).

Sakamoto at Fig. 1, 6:52-58 ("A plug layer 15 of polycrystalline silicon directly connected to the n+ source/drain region 7 and gate electrode 6 is embedded within opening 16."), 7:17-32 ("a silicon substrate 1 … form gate electrodes 6, 6 of MOS transistors 20a, 22b…") (Ex. 1103); *see also id.* at claim 1, 2:23-32, 4:20-67, 6:39-7:7, 7:17-52, 12:57-58.

86. As shown in Figure 1, Sakamoto also discloses that the gate is juxtaposed to but not contacting the diffusion region (n+ source/drain region 7), as shown by the white space identified by the green arrow separating the gate from the diffusion region:

87. The white region is an oxide film 5 that separates the gate from the diffusion region. Sakamoto at Fig. 1, 7:24-27 ("Oxide films 5 of 12 nm-15 nm thickness are formed on the surface of the p well 2.... Oxide films 5 form gate oxide films 5,5 of MOS transistors 20a, 20b.") (Ex. 1103); *see also id.* at 2:23-31, 6:42-45, 6:52-58, 6:66-7:7, 7:17-52, 12:57-58. This is identical to the structure shown above in Figure 3B of the '924 patent. '924 patent at Fig. 3B (Ex. 1101). Indeed, there would be no need for a plug to connect the gate and diffusion region if they were directly connected. *See, e.g., id.* at Figs. 1A, 1B, 1:24-2:10

(describing the prior art buried contact approach where gate and diffusion region are directly connected and there is no plug).  $^{6}$

# e. [d]: "said sidewall spacer being disposed above said diffusion region"

88. Figure 1 of Sakamoto discloses a sidewall spacer (sidewall spacer 9') disposed above the diffusion region (source/drain region 7):

<sup>&</sup>lt;sup>6</sup> As is shown in Figure 2B of the prior art, even the '924 patent notes that a gate being on said substrate juxtaposed to but not contacting said diffusion region, was known to a person of ordinary skill in the art at the time of the '924 patent:

'924 patent at prior art Fig. 2B, 2:15-20 ("a polysilicon gate 32 is first formed without direct contact with the diffusion regions 34 and 36 in a silicon substrate 40.") (Ex. 1101).

Sakamoto at Fig. 1, 7:44-52 ("a sidewall spacer 9" is located in the "opening 16"), claims 6 and 9 (Ex. 1103).<sup>7</sup>

<sup>7</sup> As is shown in Figure 2B of the prior art, even the '924 patent notes that a sidewall spacer being disposed above the diffusion region was known to a person of ordinary skill in the art at the time of the '924 patent:

'924 patent at prior art Fig. 2B (Ex. 1101).

# f. [e]: "said via being in an insulating material on said gate."

89. Figure 1 of Sakamoto discloses a via (opening 16) in an insulating material (insulating layer 9) on the gate (gate electrode).

Sakamoto at Fig. 1, 7:40-47 ("Subsequently, a BPSG (BoroPhospho Silicate Glass) film is deposited on the whole surface of silicon substrate 1.... In this step, an interlevel insulating layer 9 having a planarized surface is formed."), 2:47-53 ("[a]n opening 16 is formed in interlevel insulating layer 9. Inside opening 16, gate electrode 6 of n channel MOS drive transistor 20a and one of n+ source/drain regions 7 of n channel MOS transfer transistor 22b is exposed.") (Ex. 1103); *see also id.* at Fig. 2, Abstract, claims 1, 4, and 7, 2:33-34, 3:60-63, 4:20-67, 5:3-6, 5:20-23, 5:35-38, 6:39-7:14, 7:47-52.

- 2. <u>Claim 8: "A method according to claim 7, wherein said diffusion region</u> <u>is an N+ or a P+ region."</u>

- 90. Sakamoto discloses that the diffusion region (n+ source/drain region

7) is "an N+ or a P+ region" (*i.e.*, an n+ region).<sup>8</sup> Specifically, Sakamoto discloses that the diffusion region is an "N+ ... region," because it expressly refers to the diffusion region as an "n+ source/drain region 7." Sakamoto at 6:52-58 ("An n+ source/drain region 7 [is] exposed at the bottom of opening 16."), 7:32-38 ("Thus, n+ source/drain regions 7 of four MOS transistors 20a, 20b, 22a, 22b are formed.") (Ex. 1103); *see also id.* at 2:22-29.

3. <u>Claim 9: "A method according to claim 7, wherein said insulating</u> <u>material is selected from the group consisting of silicon oxide and silicon</u> <u>nitride."</u>

91. Sakamoto discloses forming the insulating layer 9 from a BPSG

(BoroPhospho Silicate Glass) film. Sakamoto at 7:39-47 ("a BPSG (BoroPhospho Silicate Glass) film ... is softened and reflowed by heat treatment, so that a surface of the BPSG film is planarized. In this step, an interlevel insulating layer 9 ... is

<sup>&</sup>lt;sup>8</sup> Even the '924 patent notes that N+ and P+ diffusion regions were known to a person of ordinary skill in the art at the time of the '924 patent. *See* '924 patent at 1:15-2:11 ("In the semiconductor fabrication process, it is frequently required to make local interconnect between a gate polysilicon layer to N+ and P+ diffusion regions.") (Ex. 1101).

formed.") (Ex. 1103). A person of skill in the art would readily recognize that BPSG is a type of silicon oxide. *See* Hiatt (1994) at p. 185 ("Doped silicon oxides such as phosphosilicate glass (PSG) and borophosphosilicate glass (BPSG)...") (Ex. 1115); '924 patent at 3:61-63 ("an insulating layer 76 of *silicon oxide*"), 4:39 ("#13-Nit/*BPSG*"), 4:52 ("#13-Nit/*BPSG*") (Ex. 1101).

92. A person of ordinary skill would further recognize that silicon oxide and silicon nitride are commonly used interchangeably in semiconductor structures. For example, even the '924 patent itself, in discussing the "prior art interconnect" structures at column 1:15-2:45, discloses the interchangeability of the silicon oxide ("BPSG") with silicon nitride ("Nit"). '924 patent at 4:39 ("#13-*Nit/BPSG*"), 4:52 ("#13-*Nit/BPSG*") (Ex. 1101).

93. Thus, one skilled in the art would understand that Sakamoto discloses an insulating material selected from the group consisting of silicon oxide and silicon nitride, *i.e.*, formed of either silicon oxide or silicon nitride.

- 4. <u>Claim 15: "A method according to claim 7, wherein said gate is a</u> polysilicon gate." / <u>Claim 17: "The method according to claim 7, wherein</u> said gate comprises polysilicon."

- 94. Sakamoto discloses that the gate electrode 6 comprises polysilicon and is, in fact, a polysilicon gate. <sup>9</sup> Polysilicon is also known as "polycrystalline silicon." *See* Cederbaum at 1:17 ("polycrystalline silicon (polysilicon)") (Ex. 1104); Seto (1975) at Introduction (Ex. 1116) ("polycrystalline silicon (polysilicon)"). Sakamoto discloses that the gate electrode 6 is "formed of polycrystalline silicon" (*i.e.* polysilicon). Sakamoto at 2:28-32, 2:49-52, 7:27-32 ("A polycide film formed of polycrystalline silicon 6a and refractory metal silicide 6b ... is patterned ... to form gate electrodes 6, 6 ....") (Ex. 1103).

# **B.** Ground II: Claims 10-12 are obvious in view of the combination of Sakamoto and Cederbaum

95. Dependent claims 10-12 add limitations specifying particular (and obvious design) choices for the material used in the conducting plug. Sakamoto,

<sup>9</sup> Even the '924 patent notes that a polysilicon gate was known to a person of ordinary skill in the art at the time of the '924 patent. *See* '924 patent at 2:11-32 ("a polysilicon gate 32 is first formed without direct contact with the diffusion regions 34 and 36 in a silicon substrate."), 1:15-1:24 ("In the semiconductor fabrication process, it is frequently required to make local interconnect between a gate polysilicon layer to N+ and P+ diffusion regions."), 1:25-2:11 (Ex. 1101).

when combined with Cederbaum renders obvious these claims under 35 U.S.C. § 103(a). Each of these claims depends from claim 7. Therefore the analysis with respect to claim 7 as set forth above in Ground I is incorporated by reference.

2. <u>Claim 10: "a method according to claim 7, wherein said electrically conducting plug is a metal plug" / Claim 11: "a method according to claim 7, wherein said electrically conducting plug is preferably a refractory metal plug" / Claim 12: "a method according to claim 7, wherein said electrically conducting plug is formed of a material selected from the group consisting of titanium, tantalum, molybdenum and tungsten"</u>

96. Sakamoto discloses an electrically conducting plug made of polycrystalline silicon. Sakamoto at 6:56-58 ("plug layer 15 of *polycrystalline silicon* directly connected to the n+ source/drain region 7 and gate electrode 6 is embedded within opening 16.") (Ex. 1103); *see also id.* at 6:66-7:13, 7:53-62, 8:7-21, 9:67-10:23.

97. <u>Claim 10</u>: Cederbaum discloses an electrically conducting plug (contact stud 30-2) which is a metal plug formed of tungsten, thereby disclosing the limitations of claim 10. Cederbaum at 9:31-65 ("[Prior to *tungsten (W) filling*, a titanium (Ti) layer is deposited [in] the first stud openings 28-1, 28-2 and 28-3.... Next, a thin titanium nitride (TiN) layer is formed over the titanium layer.... A *tungsten layer* is then deposited ... to entirely fill the first stud openings.... Planarization of the Ti-TiN and *W* [*i.e., tungsten*] composite layer produces first contact pads 29 and *first contact studs 30* in first stud openings 28."), claim 14 (Ex. 1104).

98. <u>Claim 11</u>: Cederbaum's tungsten metal plug (contact stud 30-2) is also a refractory metal plug, which meets the requirement of claim 11. *See, e.g.*, Cederbaum at 9:31-65, claim 14 (Ex. 1104); '924 patent at 1:53-54 ("A *refractory metal plug such as a tungsten plug* is then deposited...") (Ex. 1101); Nicholls at 6:41-60 ("refractory metal such as tungsten" and "[e]xamples of such selectively depositable refractory metals are tungsten, copper, molybdenum and tantalum.") (Ex. 1108).

99. <u>Claim 12</u>: Finally, as already stated above, Cederbaum discloses an electrically conducting plug (contact stud 30) formed of tungsten, which is a material selected from the group consisting of titanium, tantalum, molybdenum and *tungsten*, as required by claim 12. Cederbaum at 9:31-65, claim 14 (Ex. 1104).

100. It would have been obvious for one skilled in the art to replace the polycrystalline plug 15 of Sakamoto with the refractory metal tungsten plug (contact stud 30) of Cederbaum for multiple reasons.<sup>10</sup>

101. First, both Sakamoto and Cederbaum describe the same type of devices directed to the same problem: improving the structure of transistors used in semiconductor devices—in particular, the problem of stacking transistors in a particular type of memory circuit called a Static Random Access Memory ("SRAM") cell. *See* Sakamoto at 1:29-32 ("a semiconductor device having a structure in which semiconductor elements are *stacked* on a substrate, a structure of an *SRAM (Static Random Access Memory)* will be described."), 1:13-16 (Ex. 1103); Cederbaum at 1:7-14 ("The present invention relates to … a method of forming *stacked*, self-aligned polysilicon gate PFET devices…. In particular, the method has applicability in the forming of *stacked* self-aligned polysilicon gate

<sup>&</sup>lt;sup>10</sup> Even the '924 patent notes that a tungsten refractory metal conducting plug was known to a person of ordinary skill in the art at the time of the '924 patent. *See* '924 patent at 1:50-56 ("A refractory metal plug such as a tungsten plug is then deposited into hole 24."), 2:23-32 ("After the deposition of a glue layer (not shown), metal plugs 44, 46 and 48 are deposited into the vias. After a tungsten plug etch back and a local interconnect masking/etching process…") (Ex. 1101).

PFETs ... in six device (6D) *SRAM cells*.") (Ex. 1104); *see also* '924 patent at 2:32-63, 4:10-15 (Ex. 1101).

102. In fact, Sakamoto and Cederbaum (and the '924 patent) disclose nearly identical structures with nearly identical components.

103. Like Figure 1 of Sakamoto, Figure 7 of Cederbaum shows an electrically conducting plug (contact stud 30-2) within an opening 28-2 (Figure 6) which contains a sidewall spacer 24 (Figure 4). The contact stud 30-2 directly connects a diffusion region (source/drain 21) to a gate (gate electrode 23-2). The source/drain 21 is formed in a substrate and is not directly connected to the gate electrode 23-2, which is substantially covered by an insulating material 26. Cederbaum at Figs. 4-7, 7:31-40, 7:37-52 ("N+ implanted active regions 21...

constitute the source and drain regions of the NFETs," "[n]umeral[]...23-2 designate[s]...the gate electrode[] of NFETs...," and "[o]xide sidewalls or spacers 24 have been formed on the lateral sides of the polysilicon gate electrodes"), 8:26-39, 9:28-68, 13:31-37 (Ex. 1104).

104. Second, the particular material to be used for electrical conductivity would have been a simple design choice to one of ordinary skill in the art. It was known that there were multiple materials that could be used to make an electrical connection between different parts of a transistor. *See, e.g.*, Nicholls at 6:41-54 (explaining "an advantage of using a refractory metal such as tungsten over aluminium" as a plug), 6:55-60 ("The present invention is not limited to the use of tungsten [as a plug] but can be carried out utilising any refractory metal ... which preferably can be selectively deposited into a contact hole. Examples of such selectively depositable refractory metals are tungsten, copper, molybdenum and tantalum.") (Ex. 1108). The use of a refractory metal is thus a mere implementation detail which one skilled in the art would have known about and been motivated to use.

105. Third, as both Sakamoto and Cederbaum explain, there are advantages to using an electrically conducting plug formed of a refractory metal, such as tungsten (as in Cederbaum) instead of a polycide film formed from polycrystalline silicon and a metal (as in Sakamoto). Sakamoto describes the benefits of increased

56

conductivity of the plug and increased conductivity and ohmic contact between the plug and other components, such as the source/drain region 7. See Sakamoto at 8:5-12 ("Impurity ion is ion-implanted into polycrystalline silicon plug layer 15 ... in order to provide conductivity."), 2:28-32, 2:62-64, 6:58-63, 7:3-7 ("ohmic contact of interconnection layer 8a, polycrystalline silicon plug layer 15, and source/drain region 7 can be obtained by having titanium silicide layer 11 interposed between interconnection layer 8a and polycrystalline silicon plug layer 15."), 7:26-28, 10:5-8 ("Fine ohmic contact can be also provided between the silicon plug layer and the upper interconnection layer of p type conductivity by interposing a refractory metal silicide layer etc.") (Ex. 1103). Cederbaum then describes a tungsten conducting plug (contact stud 30-2) that has the better conductivity and lower resistivity as compared to a polycide/polycrystalline silicon plug (like Sakamoto's plug). Cederbaum at 4:39-41 ("[p]olycide is a quite good conductive material, however it is known to exhibit higher resistivities than metal."), 9:32-34 ("filling the first stud openings with a highly conductive material (typically a metal, such as tungsten)"), 6:47-48 ("[t]he [conventional] N+/P+ diode contact structure is replaced by a tungsten contact stud forming an ohmic contact.") (Ex. 1104).

### IX. AVAILABILITY FOR CROSS-EXAMINATION

106. In signing this declaration, I recognize that the declaration will be filed as evidence in a case before the Patent Trial and Appeal Board of the United States Patent and Trademark Office. I also recognize that I may be subject to cross examination in the case and that cross examination will take place within the United States. If cross examination is required of me, I will appear for cross examination within the United States during the time allotted for cross examination.

### X. RIGHT TO SUPPLEMENT

107. I reserve the right to supplement my opinions in the future to respond to any arguments that Patent Owner raises and to take into account new information as it becomes available to me.

U.S. Patent No. 5,965,924 Claims 7-12, 15 and 17

#### Jurat

108. I declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1101 of Title 18 of the United States Code.

Dated: June II, 2016

ichard Blanchard

Dr. Richard Blanchard

U.S. Patent No. 5,965,924 Claims 7-12, 15 and 17

# APPENDIX A

### Richard A. Blanchard, Ph.D.

#### **Professional Profile**

Dr. Blanchard has over 40 years of combined industry, research, academic, and consulting experience. His research covers semiconductor device and electronics design, semiconductor device physics, semiconductor manufacturing processes and equipment, failure analysis, and reverse engineering of semiconductor devices and electronic circuits. Dr. Blanchard is a named inventor on more than 200 issued U.S. patents. As a result, he has been involved in numerous patent and trade secret litigation matters including a number of ITC proceedings. He has also authored or co-authored books and articles dealing with semiconductor design, process development, and failure analysis.

Dr. Blanchard has worked at Blanchard Associates, Los Altos, Silicon Valley Expert Witness Group, Mountain View, Exponent Failure Analysis Associates, Inc., Menlo Park, CA, IXYS Corporation, San Jose, Siliconix, Inc. Santa Clara, Supertex, Inc. Sunnyvale, Cognition, Inc. Mountain View, Foothill College, Los Altos Hills, and at Fairchild Semiconductor, Mountain View, CA.

#### **Credentials and Professional Affiliations**

| 1982 | Stanford University | Ph.D., Electrical Engineering |

|------|---------------------|-------------------------------|

| 1970 | M.I.T.              | MSEE                          |

| 1968 | M.I.T.              | BSEE                          |

- Senior Member, Institute of Electrical and Electronics Engineers

- Member, Electronic Device Failure Analysis Society

- Member, International Microelectronics & Packaging Society

- Member, American Vacuum Society

- Member, National Fire Protection Association

- Court Appointed Special Master

### Patents

| Patent Number | Date Issued | <u>Title</u>                                                                                                                                                                                                                                |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9,362,348     | 6/7/2016    | Method of manufacturing a light emitting, power generating,<br>Or other electronic apparatus                                                                                                                                                |

| 9,356,595     | 5/31/2016   | Bidirectional two-base bipolar junction transistor devices,<br>operation, circuits, and systems with collector-side base driven,<br>diode-mode turn-on, double base short at initial turn-off, and two<br>base junctions clamped by default |

| 9,355,853     | 5/31/2016   | Systems and methods for bidirectional device fabrication                                                                                                                                                                                    |

| 9,349,928     | 5/24/2016   | Method of manufacturing a printable composition of a liquid or gel suspension of diodes                                                                                                                                                     |

| 9,343,593     | 5/17/2016   | Printable composition of a liquid or gel suspension of diodes                                                                                                                                                                               |

| 9,337,262     | 5/10/2016   | Structures and methods with reduced sensitivity to surface charge                                                                                                                                                                           |

| 9,316,362     | 4/19/2016   | LED lighting apparatus formed by a printable composition of a liquid or gel suspension of diodes and methods of using same                                                                                                                  |

| 9,306,048     | 4/05/2016   | Dual depth trench-gated MOS controlled thyristor with well-<br>defined turn-on characteristics                                                                                                                                              |