### MULTILING CORPORATION

180 NORTH UNIVERSITY AVE. Suite 600 PROVO, UT 84601-4474 VOICE (801) 377-2000 FAX (801) 377-7085

### TRANSLATOR'S CERTIFICATE OF TRANSLATION

Translation from Japanese to English

MultiLing Project Number: GBPLC1710001HQ-S

Client: Greenblum & Bernstein, P.L.C.

MultiLing Corporation, a Delaware corporation, which has its principal office at 180 North University Avenue, Suite 600, Provo, UT 84601-4474, USA, certifies that

- (a) it is a professional translation company of multiple languages including Japanese and English;

- (b) it has translated from the original document to the translated document identified below, and to the best of its knowledge, information, and belief the translation of that document is accurate as a publication quality translation; and further,

- (c) these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Original Document Identifier: Awaya (1998) (03005811); JPH08250596A (03005939); JPH09293690A (03002312); JPH10125627A (03005938); JPH10256256A (03002313). Translated Document Identifier: Awaya (1998) (03005811)\_en-US; JPH08250596A (03005939)\_en-US; JPH09293690A (03002312)\_en-US; JPH10125627A (03005938)\_en-US; JPH10256256A (03002313)\_en-US.

Signed this 10th day of February 2017.

Michael Degn, VP Sales/Marketing

ACKNOWLEDGMENT BEFORE NOTARY

State of Utah

}ss.

(JP)

## (19) Japan Patent Office (12) Japanese Unexamined **Patent Application** Publication (A)

(11) Patent Application Publication No.

### **Japanese Unexamined Patent Application Publication No.** H09-293690

(43) Date of Disclosure: November 11, 1997 (Heisei 9)

| ( <b>51</b> ) Int. Cl. <sup>6</sup> |        | Ident. Code | Inter. Ref. No. | FI   |        | Location of Tech. Indication |

|-------------------------------------|--------|-------------|-----------------|------|--------|------------------------------|

| H01L                                | 21/28  | 301         |                 | H01L | 21/28  | 301R                         |

|                                     | 21/203 |             |                 |      | 21/203 | S                            |

|                                     | 21/768 |             |                 |      | 21/903 | C                            |

Examination Request Status: Yes No. of Claims: 4 OL(6 pages total)

(21) Filing Number: Patent Application No.

H08-106539

(22) Date of Application: April 26, 1996 (Heisei 8)

(71) Applicant: 000004237

NEC (Nippon Electric Company)

5-7-1 Shiba, Minato-ku, Tokyo

(72) Inventor: Yoshinao MIURA

C/o NEC (Nippon Electric Company),

5-7-1 Shiba, Minato-ku, Tokyo

(74) Agent: Akio SUZUKI, attorney

### (54) [Name of Invention] METHOD FOR MANUFACTURING SEMICONDUCTOR DEVICE

#### (57) Abstract

[Problem] Use of an amorphous film as a barrier film between a silicon (Si) substrate and a contact metal has been proposed, however, an amorphous film is difficult to form only in a contact hole area because said film must be formed using a sputtering method.

[Resolution Means] Forming an insulating film 12 of silicon oxide, and the like, on a surface of a silicon substrate, opening a contact hole 13 in the insulating film locally, uniformly depositing a thin Ti film 14 on a front surface that includes the contact hole to a thickness of 10 nm, then, heating a base to 450 to 550°C to form an amorphous TiSi<sub>x</sub> film 15 only on an exposed Si part inside the contact hole, which thus becomes a thin barrier film. Forming an Al film 16 thereupon to create a pad.

### Specification

Title of the Invention: METHOD FOR MANUFACTURING SEMICONDUCTOR DEVICE

# [DETAILED DESCRIPTION OF THE INVENTION] [0001]

[Technical Field of the Invention] The present invention relates to an improvement in a method for forming contact structures using metal nitride barrier layers in a method for manufacturing semiconductor devices.

[0002]

[Conventional Technology] The importance of wiring techniques for making connections between elements has become more and more important as devices have become more integrated in recent years. It is especially critical to reduce resistance in wiring contacts while maintaining reliability. While it is common for Al, W, and the like, to be used as main constituent metals in conventional contact structures, when these metals and silicon substrates are brought into close contact and joined, heat treatments cause interfacial interdiffusion and silicide reactions, and form a high resistance layer at the interface, while current leaks are generated due to the piercing of the shallow junction of the reaction layer. Barrier layers with high reaction suppressing force and low resistance are needed to prevent this, and thus barrier layers made of high melting point metals such as Ti, W, or the like, or compounds thereof, have been used.

In particular, a variety of techniques have been proposed that use a metal nitride film accompanied by a thin silicidation layer near the interface as a barrier by thermally nitriding a high melting point metal on Si. Examples include Japanese Unexamined Patent Application Publication No. H02-235372 and Japanese Unexamined Patent Application Publication No. H04-112529. FIG. 4 is a cross sectional view illustrating one of these examples, where an  $SiO_2$  film 42 is formed on an Si substrate 41 as an insulating film, a barrier film 45 made of a metal nitride of a high melting point metal such as Ti, W, or the like, is formed in a contact hole 43 opened in the insulating film 42, and a metal 45 of mainly Al, W, or the like, is formed on the insulating film. [0004]

However, barrier properties are insufficient because these constituent barrier films are generally polycrystalline structures, and because there are grain boundaries that become high speed diffusion paths. Thus, film thickness that is sufficiently thicker than grain crystal size is required to achieve adequate barrier properties, which increases contact resistance. Furthermore, when barrier properties are enhanced by filling these grain boundaries using oxidation (Applied Physics Letters Vol. 47, p. 471 (September 1985), Japanese Unexamined Patent Application Publication No. H05-267211), the specific resistance of the material itself increases through the introduction of impurities such as oxygen, and the like, which also increases contact resistance. Moreover, to prevent damage to Si substrate surfaces in conjunction with the formation of barrier films in polycrystalline barrier films, barrier films cannot be formed directly onto Si substrates, and thus good electrical properties cannot be achieved.

From this point of view, techniques have been proposed where it is preferable to make the crystal grains small and that use amorphous films or microcrystalline films obtained through sputtering in nitrogen atmospheres as barrier films (Applied Surface Science, Vol. 41 and 42, p. 207 (1989)). [0006]

[Problem to be Solved by the Invention] However, when such amorphous films and microcrystal granular films are formed using sputtering methods, there is a problem in that it is impossible to employ a self aligning process to selectively form barrier films on contact openings, or, in particular, to form barrier films in contact holes, and thus that it is difficult to apply such films to fine, highly integrated semiconductor devices.

[0007]

An object of the present invention is to provide a manufacturing process that makes it possible to use a self aligning process to selectively deposit an amorphous film in a contact hole, realizes a contact structure having low contact resistance and high barrier properties, and manufactures a semiconductor device having high speed operating characteristics and a simple structure.

[0008]

[Means for Solving the Problem] The manufacturing method according to the present invention is characterized in that the method exposes a barrier film formed between a silicon substrate and a contact metal to a reactive gas containing nitrogen after evenly depositing a thin high melting point metal film on the silicon substrate while keeping a substrate temperature at 450 to 550°C to form the barrier film as a thin amorphous or microcrystalline barrier film made of a high melting point metal, silicon, and nitrogen. For example, a preferred embodiment of the present invention forms an insulating film of silicon oxide, and the like, on a surface of a silicon substrate; opens a contact hole locally in the insulating film, uniformly deposits a thin high melting point metal film on an entire surface that includes the contact hole, heats the substrate to 450 to 550°C to thus form an amorphous layer made of the high melting point metal and silicon only on an exposed silicon part inside the contact hole, removes unreacted metal on the insulating film by chemical etching, and then exposes the film to a reactive gas containing nitrogen to form a thin amorphous or microcrystalline barrier layer.

Here, it is preferable that the thin high melting point metal film is made of Ti, Zr, and Hf and is formed to a thickness of 10 nm or less. Furthermore, the process for exposing to a reactive gas containing nitrogen is radical nitrogen beam irradiation, or highly reactive nitrogen compound gas irradiation using hydrazine, ammonia, or the like. [0010]

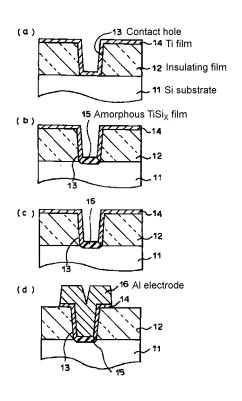

[Description of the Preferred Embodiments] A first embodiment of the present invention will be described next with reference to FIG. 1. First, as illustrated in FIG. 1 (a), an insulating film 12 made of SiO<sub>2</sub> is formed on a surface of a (100) surface Si substrate 11, and then, the insulating film 12 is selectively etched to open a contact hole 13 in a required location. Furthermore, an electron beam gun is used in a high vacuum to deposit a 4 nm thick polycrystalline Ti film 14. [0011]

Next, as illustrated in FIG. 1 (b), the deposited polycrystalline Ti film 14 is heated for five minutes at  $500^{\circ}$ C to reform the area of the polycrystalline Ti film 14 touching the Si substrate 11 into a Ti amorphous film 15. It can be confirmed, from the fact that the Reflection High Energy Electron Diffraction (RHEED) pattern is hollow and the Si peak strength according to X-ray Photoelectron Spectroscopy (XPS) has increased significantly, that a surface layer of this film has become a TiSi<sub>x</sub> amorphous layer. It was discovered that a heating temperature in the range of 450 to  $550^{\circ}$ C is preferable because, at  $600^{\circ}$ C or above, silicide begins to crystallize rapidly making it impossible to obtain an amorphous film, and because, at  $400^{\circ}$ C or below, it takes too much time to mutually diffuse metal and silicon.

Next, as illustrated in FIG. 1 (c), a radical nitrogen beam with a flux of approximately 1 X 10<sup>-5</sup> Torr was supplied to the substrate surface for five minutes using a radical nitrogen source while the temperature of the Si substrate was maintained. Based on an XPS surface analysis of the Ti amorphous film 15, this resulted in the surface being reformed into an even film containing approximately equal amounts of Ti, Si, and N, and thus being configured as a barrier film. This barrier film 15, observed using cross sectional Transmission Electron Microscope (TEM), was found to be a film with a uniform thickness of 5 nm having an extremely steep interface with an amorphous structure made of extremely fine grains with diameters of 1 nm or less. Furthermore, because the RHEED pattern is still hollow even after the substrate temperature is raised to 800°C, the amorphous structure of this film is very stable, which is in stark contrast to the fact that

amorphous  $TiSi_x$  readily undergoes a phase transition to a polycrystalline structure at around 650°C. [0013]

Therefore, as illustrated in FIG. 1 (d), a 50 nm thick Al film 16 is deposited on the Ti amorphous film 15, and this Al film 16 is etched along with the crystalline Ti film 14 to form a contact wire. With this wire structure, the barrier film 15 maintains flatness despite undergoing a slight decrease in film thickness even when heat treated (550°C for 60 minutes) in a nitrogen atmosphere, and is thus suppressed to a level of thickness equal to or less than that of an interface interdiffusion barrier film.

In this way, a metastable amorphous silicide state is achieved at a temperature lower than a crystallization temperature when the Ti reacts with the silicon. If nitriding is carried out at this stage, the amorphous state stabilizes, which thus enables the formation of a precisely uniform barrier film. This film enhances barrier properties, and is able to reduce film thickness and decrease contact resistance significantly when compared to conventional methods. Furthermore, because a damage layer caused by sputtering, and the like, is not left behind, good bonding can be realized.

[0015]

A second embodiment according to the present invention will be described with reference to FIG. 2. First, as illustrated in FIG. 2 (a), an insulating film 22 made of  $SiO_2$  is formed on a surface of a (100) surface n-Si substrate 21, and then, a 10  $\mu$ m diameter contact hole 23 is opened in a portion of the film. Furthermore, a polycrystalline Ti film 24 10 nm thick is deposited over an entire surface using a sputtering method, and then, only the Ti film 24 in the contact hole 23 is heated to  $500^{\circ}$ C for five minutes, and is thus reformed into an amorphous TiSi<sub>x</sub> 25. [0016]

Next, as illustrated in FIG. 2 (b), the substrate is taken out of a high vacuum tank and immersed in an etching solution containing hydrochloric acid as a main component for 1 minute to remove the unreacted Ti film 24. The substrate is re-introduced into the high vacuum and irradiated with a radical nitrogen beam. Line analysis of this sample surface using Auger Electron Spectroscopy (AES) revealed that while the elements Ti, Si, N, and O were observed in the bottom of the contact hole 23, only Si, N, and O were observed on the surface of the insulating film 22, and thus it was successfully confirmed that, as is illustrated in FIG. 2 (c), a conductive amorphous TiSiN film 26 was formed only in the bottom of the contact hole 23, while an SiN film 27 was formed on the surface of the insulating film 22. Therefore, as illustrated in FIG. 2 (d), a 200 nm thick Al film 28 is formed to form an Al pad inside the contact hole using a lithography process. [0017]

Using an I-V method to evaluate the diode properties of a Schottky junction produced in this way revealed that a nearly ideal curve having a barrier wall height of 0.55 eV was achieved. This indicates that a substrate surface damage layer, introduced by the sputtering process, was consumed by silicidation, and that an interface with few defects was obtained. Thus, it is expected that the barrier wall height will be half an Si band gap (1.1 eV), and that, in terms of ohmic contact, contact resistance that is sufficiently low with respect to both n and p- substrates was obtained, which is probably also effective for forming C-MOS (Complementary-MOS) elements. [0018]

An amorphous TiSi<sub>x</sub> 25 was formed only on an exposed part of the substrate by the deposition and subsequent heating of the Ti film 24 according to the present embodiment, and an unreacted Ti film 24 was left behind because an interface reaction with Ti in a coated part of the insulating film 22 was slow. Because the unreacted metal Ti dissolves at a much faster rate than amorphous TiSi<sub>x</sub> when an etching solution having hydrochloric acid as a major component is used, performing the nitriding process after chemically removing only the unreacted Ti film 24 makes it possible to selectively form a barrier film 26 of TiSiN only on an exposed part of the Si substrate 21, which thus makes it possible to form a barrier film only inside the contact hole.

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.