VERIFICATION OF TRANSLATION

I, Yukiko T. Buntin

of 1950 Roland Clarke Place

Reston, VA 20191

declare that I am well acquainted with both the Japanese and English languages, and that the attached is an accurate translation, to the best of my knowledge and ability, of Japanese Unexamined Patent Application Publication No. H09-64044, published March 7, 1997.

I further declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code and that such willful false statements may jeopardize the validity of the above-captioned application or any patent issued thereon.

Signature

Yukiko T. Buntin

Date 3 - 2 - 2017

| (19) Japan Patent Office (JP) | (12) Patent Publication (A) |

|-------------------------------|-----------------------------|

|-------------------------------|-----------------------------|

(11) Patent Publication No.

### JP H09-64044

(43) Publication Date: March 7, 1997

| (51) Intl. Cl. <sup>6</sup> ID N      |              | ID No.       | PTO Ref. No.                       | F1                         | Technolo                         | Technology Indication Area |  |

|---------------------------------------|--------------|--------------|------------------------------------|----------------------------|----------------------------------|----------------------------|--|

| H01L                                  | 21/3205      |              |                                    |                            |                                  |                            |  |

|                                       | 21/28        | 301          |                                    |                            |                                  |                            |  |

|                                       |              |              |                                    | H01L 21/88                 | R                                |                            |  |

|                                       |              |              |                                    | 21/28                      | 301T                             |                            |  |

|                                       |              |              |                                    | 21/88                      | M                                |                            |  |

|                                       |              | Reque        | est for Examination N              | Not Requested              | No. of Claims: 2                 | FD (9 pages total)         |  |

| (21) App                              | lication No. | Applicati    | ion H07-238972                     | (71) Applica               | nt 0000030                       | 78                         |  |

|                                       |              |              | Т                                  | Toshiba Corporation        |                                  |                            |  |

| (22) Application Date August 25, 1995 |              | 7            | 72 Horikawa-cho, Saiwai-ku,        |                            |                                  |                            |  |

|                                       |              | ŀ            | Kawasaki-shi, Kanagawa-ken         |                            |                                  |                            |  |

|                                       |              | (72) Invento | r Tadashi                          | IIJIMA                     |                                  |                            |  |

|                                       |              | c            | c/o Toshiba Corporation R&D Center |                            |                                  |                            |  |

|                                       |              | 1            | 1 Komukai Toshiba-cho, Saiwai-ku,  |                            |                                  |                            |  |

|                                       |              |              |                                    | Kawasaki-shi, Kanagawa-ken |                                  |                            |  |

|                                       |              | (72) Inve    |                                    | r Kyoichi                  | SUGURO                           |                            |  |

|                                       |              |              |                                    | c                          | c/o Toshiba Corporation R&D Cent |                            |  |

|                                       |              | 1            | 1 Komukai Toshiba-cho, Saiwai-ku,  |                            |                                  |                            |  |

|                                       |              |              | F                                  | Kawasaki-shi, Kanagawa-ken |                                  |                            |  |

|                                       |              |              |                                    | (72) Invento               | r Yoshiak                        | i SHIMOOKA                 |  |

|                                       |              |              | c/o Toshiba Corporation R&D Center |                            |                                  |                            |  |

|                                       |              | 1            | 1 Komukai Toshiba-cho, Saiwai-ku,  |                            |                                  |                            |  |

|                                       |              | F            | Kawasaki-shi, Kanagawa-ken         |                            |                                  |                            |  |

|                                       |              | (74) Represe | entative Patent A                  | gent Takehiko SUZUE        |                                  |                            |  |

|                                       |              |              |                                    |                            |                                  |                            |  |

# (54) [Title of Invention] SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD THEREOF

(57) [Abstract] (Revised)

PURPOSE: Improving barrier

properties of a barrier metal layer, and

which is aimed at improving

characteristics of an element, improving

reliability of wiring, and the like.

#### [Solution]

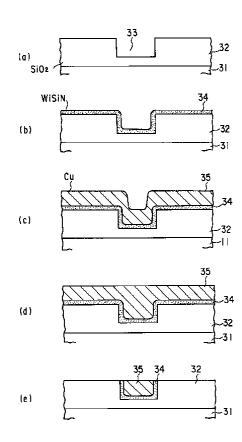

In a semiconductor device in which a wiring is formed on a semiconductor substrate through a barrier metal, a groove 33 is formed on a surface of a semiconductor substrate 31, and, on bottom and side surfaces of the groove 33, an amorphous alloy layer 34 of W-Si-N is formed, the alloy layer internally including micro crystallites of W. A Cu film 35 is embedded as the wiring within the groove 33 through the alloy layer 34.

#### [Scope of the Claims]

[Claim 1] A semiconductor device comprising an amorphous alloy layer of W-Si-N formed on at least a bottom surface of an electrode or wiring layer, and the alloy layer internally has a structure including micro crystallites each having a diameter smaller than a film thickness of the alloy layer.

[Claim 2] A manufacturing method of the semiconductor device comprising a step of forming, on an area where an electrode or wiring layer is to be formed over a semiconductor substrate, an amorphous alloy layer of W-Si-N that internally includes micro crystallites, and a step of forming a conductive film to be used as an electrode or wiring layer over the alloy layer.

[0001]

[Field of the invention] The present invention relates to a semiconductor device, and more particularly to a semiconductor device which has an improved barrier metal layer incorporated in an electrode or a wiring, and a manufacturing method of the same.

[0002]

[Conventional technology] Conventionally, a barrier metal layer has been interposed between one wiring layer and another wiring layer or an element when electrical contact is made. This intends to prevent reaction/diffusion between the wiring layers or between the wiring layer and the element, and to obtain favorable and reliable contact. Further, the barrier metal layer is used, not only for contacting portions, but also for forming a wiring or electrode on an insulating film.

[0003]

At present, TiN, TiW, and the like are used as a barrier metal material. Such materials are formed into a film by a sputtering process or the like, and the film produced is a polycrystal and is a columnar crystal in which a grain boundary is at right angles to a ground film. Therefore, the film has a grain boundary which is likely to produce diffusion in a direction in which diffusion is to be prevented, and the film has an unsuitable structure for ensuring barrier properties.

[0004]

It is also desired that the wiring layer has low resistance in order to enable the element to work with high efficiency. In order to do this, a future barrier metal layer must achieve lowered resistance by still further reduction in film thickness. The barrier properties of a reduced thickness barrier metal layer deteriorate more than those of a thick film. Therefore, it

is expected that barrier properties are insufficient in the barrier metal layer formation method currently in use. Moreover, in order to obtain perfect barrier properties, a thin film of a monocrystalline body must be used. However, creating a thin film of a monocrystalline body without any defects is extremely difficult and cannot be achieved with present technology. [0005]

In addition, polysilicon is conventionally used for gate electrodes. Since polysilicon has high electric resistance, an element has an increased parasitic resistance, thereby deteriorating the characteristics of the element. Therefore, use of a metal or a silicide as a low resistance material has been tried. However, when a metal film is formed on a gate insulating film by an ordinary sputtering technique and the like, it becomes polycrystalline and the crystal faces are not uniform, thereby creating differences in work functions between different crystal faces. Therefore, unstable difference is created in work functions in the semiconductor beneath the gate insulating film, causing the threshold voltage to become unstable and the element cannot be practically used.

[0006]

In addition, with the conventional barrier metal manufacturing method, when forming a film to a contact, a groove, and the like with a high aspect ratio, step coverage is poor, and the film thickness on a bottom or a side surface is reduced, thereby posing a problem that the performance of a barrier metal is deteriorated.

[0007]

[Problems to be solved by the invention] Thus, in the conventional semiconductor device, one could not say that the barrier property of the barrier metal layer used for an electrode or wiring was sufficient, and this had become a factor which causes degradation of an element characteristic, the reliability deterioration of wiring, and the like. Since control of the work function of the metal electrode on gate insulating film could not be performed, there was a problem that it was difficult to use a metal film as a gate electrode.

[8000]

With film-forming methods such as sputtering, when forming a film to a contact, a slot, and the like with a high aspect ratio, due to poor step coverage, the film thickness in a bottom or a side surface is reduced, thereby posing a problem that the performance of a barrier metal is deteriorated.

[0009]

The present invention was made in consideration of the above-mentioned situation, and it intends to improve the barrier property of a barrier metal layer, and to provide a

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.