ASME proceedings (IEEE/SEMI Advanced Semiconductor manufacturing Conference and workshop

IEEE/SEMI®

1998

IEEE/SEMI

Advanced

Semiconductor

Manufacturing

Conference

And Workshop

Theme - Semiconductor Manufacturing: Meeting the Challenges of the Global Marketplace

# **ASMC 98 PROCEEDINGS**

The IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop is an annual forum that provides a venue for the presentation of methodologies, approaches and techniques required to achieve world class semiconductor manufacturing. A key role this conference plays is in promoting interaction among semiconductor professionals at all levels. The goal and objective of the conference are to assist in making the participating companies more knowledgeable of semiconductor production methods, encourage open communication between participants, and develop the strategic relationship between users and suppliers needed to achieve manufacturing excellence and improve global competitiveness.

September 23 – 25, 1998 Boston, Massachusetts, USA

# 1998 PROCEEDINGS IEEE/SEMI ADVANCED SEMICONDUCTOR MANUFACTURING CONFERENCE AND WORKSHOP (ASMC)

· I 25a

PERMISSION TO REPRINT OR COPY: 1998

Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 09123 USA. Instructors are permitted to photocopy isolated articles for non-commercial classroom use without fee. For other copying, reprint or re-publication permission, write to IEEE Copyright Manager, IEEE Service Center, 445 Hoes Lane, Piscataway, NJ 08855 USA; or SEMI, 805 East Middlefield Road, Mountain View, CA 94043 USA. All rights reserved.

Copyright © 1998 by Institute of Electrical & Electronics Engineering, Inc. (IEEE) and Semiconductor Equipment and Materials International, Inc. (SEMI)

## PRINTED AND BOUND IN THE UNITED STATES OF AMERICA

Additional copies of these Proceedings may be purchased from:

SEMI

805 East Middlefield Road Mountain View, CA 94043 USA

Phone: (650) 940-6971 http://www.semi.org IEEE Service Center

445 Hoes Lane

Piscataway, NJ 08855-0060 USA

Phone: (732) 981-0060 In the US 1-800-678-IEEE

http://www.ieee.org

Refer to the IEEE Catalog Number, printed below:

IEEE Catalog Number; 98CH36168

ISBN Number: 0-7803-4380.

0-7803-4380-8 Softbound Edition 0-7803-4381-6 Casebound Edition 0-7803-4382-4 Microfiche Edition

ISSN: 1078-8743

Layout, composition and compilation by Semiconductor Equipment and Materials International (SEMI)

# TABLE OF CONTENTS

Overview of SEMI and the IEEE

| Keynote Address: Semiconductor Manufacturing: Transition from a Technology Driven to an Economic Driv<br>Infrastructure, James Hines, Dataquest, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Yield Modeling & Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| Predictive Yield Modeling for Reconfigurable Memory Circuits  Dennis Ciplickas and Xiaolei Li, Rakesh Vallishayee, PDF Solutions, Inc.; Andrzej Strojwas, Carnegie Mellon University;  Randy Williams and Michael Renfro, Intel Corp.; Raman Nurani, KLA-Tencor Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | aragetsesi Exercinesi<br>May and Jacy DeVint<br>la Memerare and Alla |

| Analysis and Modeling of Systematic and Defect Related Yield Issues During Early Development of a New Technology R. Guldi, J. Watts, S. PapaRao, D. Catlett, J. Montgomery and T. Saeki, <i>Texas Instruments Inc.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | eff, Joseph-emailie<br>7<br>A vend ythe en Denho                     |

| How to Simultaneously Reduce a and B Error with SPC? A Multi-Variate Process Control Approach R. Nasongkhla, J. George Shanthikumar, U.C. Berkeley; R. Nurani, KLA-Tencor; M. McIntyre, Advanced Micro Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13<br>Fund remark of only                                            |

| Yield Analysis and Data Management Using Yield Manager™ F. Lee, Motorola; S. Smith, Knights Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                                   |

| A Comparison of Critical Area Analysis Tools Sean Fitzpatrick, Geoffrey O'Donoghue and Gary Cheek, Analog Devices, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | one gridere 31 m. I done<br>typilderik VIIIR. 19940                  |

| opinion in a real femology real and real femology real fem | 34 / 134                                                             |

| Overall Equipment Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| The Advantages of Using Short Cycle Time Manufacturing (SCM) Instead of Continuous Flow Manufacturing (CFM) Donald Martin, IBM Microelectronics Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| Improvement of AME 8110 Oxide Etcher Daily Clean Kevin Welp, Paul Fisher, Joan Holden, Ping Wang, Mynetta Gunn and Jennie Franco, Motorola Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                   |

| Semiconductor Metrics: Conflicting Goals or Increasing Opportunities?  Linda Sattler, National Microelectronics Research Centere; Robert Schlueter, Texas Instruments Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55                                                                   |

| Towards Real-Time Fault Identification in Plasma Etching Using Neural Networks Benyong Zhang and Gary May, Georgia Institute of Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61                                                                   |

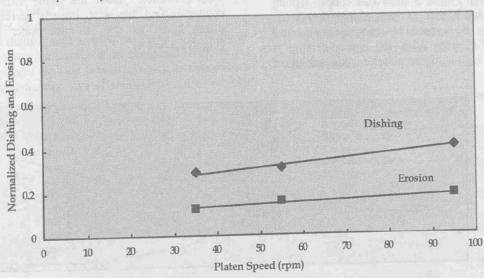

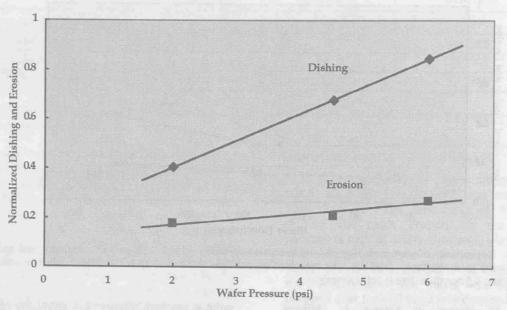

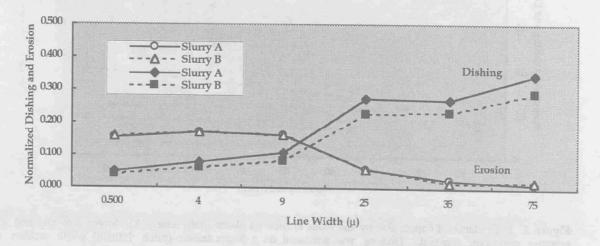

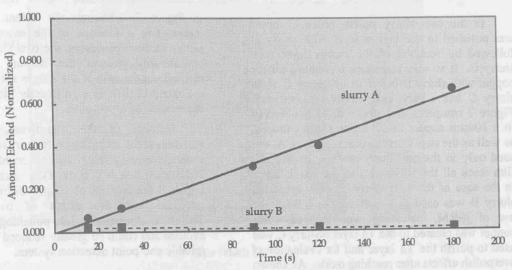

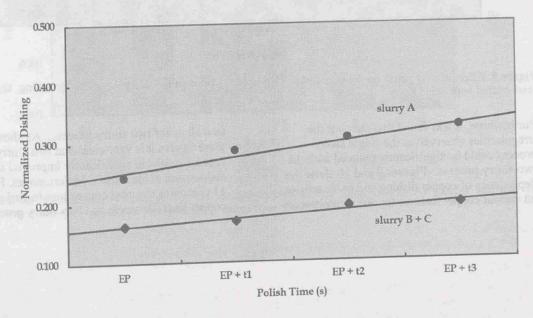

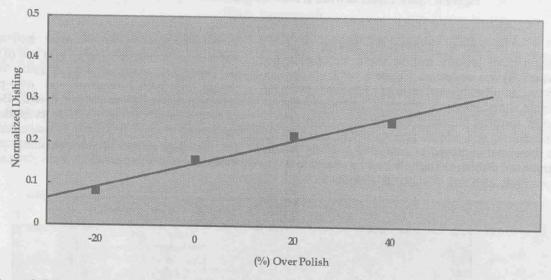

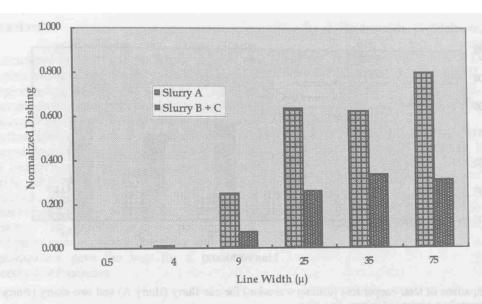

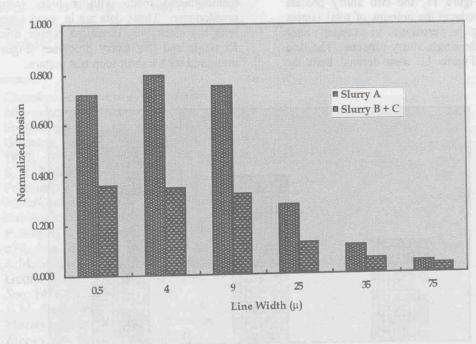

| Control Methods for the Chemical-Mechanical Polishing Process in Shallow Trench Isolation Yutong Wu, Jim Gilhooly and Brett Philips, IBM Microelectronics Division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                                                   |

| A80 – A New Perspective on Predictable Factory Performance Calum Cunningham and Richard Babikian, Intel Ireland                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71                                                                   |

| Yield Enhancement Strategies & Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| Statistical Methodology for Yield Enhancement via Baseline Reduction K. Fridgeirsdottir and R. Akella, Stanford University; M. Li, P. McNally and S. Mittal, Intel Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77                                                                   |

| Development of New Methodology and Technique to Accelerate Region Yield Improvement K. Wong, P. Mitchell, J. Nulty, M. Carpenter, L. Kavan, B. Jin, G. McMahon, C. Seams, J. Fewkes, A. Gordon and C. Sandstrom, Cypress Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82                                                                   |

| Correlation of Digital Image Metrics to Production ADC Matching Performance  Jennifer Blais, IBM Microelectronics, Verlyn Fischer, Yoel Moalem, Matthew Saunders, KLA-Tencor Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86                                                                   |

| Intelligent Line Monitor: Maximum Productivity Through an Integrated and Automated Line Monitoring Strategy Tom Pilon, IBM Micoelectronics Division; Mark Burns, Verlyn Fischer and Matthew Saunders, KLA-Tencor Corp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93                                                                   |

| Defect Inspection Sampling Plans: Which One Is Right For Me?  Brian Scanlan, Analog Devices B.V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103                                                                  |

| Sampling Methodology for SEM-based Defect Classification: Risk, Cost and Benefit Analysis Ram Akella and Chih-Hung Lin, Stanford University; Prasanna Chitturi, Applied Materials, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109                                                                  |

| † Not available at time of printing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

| IEEE/SEMI Advanced Semiconductor Manufacturing Conference & Workshop 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Boston, MA                                                           |

# Harnessing & Developing Workforce Potential

| The Effect of Perfomance Based Incentive Plans Tim Ingersoll, Texas Instruments, Inc.                                                                                                                                                               | 115 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Enhancing Fab Performance Under Team Council Methodology Ronald N. Dupuis, Jr., John Gervais and Stevan Park, Fairchild Semiconductor                                                                                                               | 119 |

| Risk Management Exercise in a Wafer Fab Utilizing Dynamic Simulation Todd McCay and Gary DePinto, Motorola, Inc.                                                                                                                                    | 122 |

| Rewards, Structure and Alignment Affect Goal Attainment Janet Gentleman-Ingersoll, Texas Instruments, Inc.                                                                                                                                          | 128 |

| Quantifying Capacity Loss Associated With Staffing in a Semiconductor Manufacturing Line C. Pollitt, IBM Microelectronics Division; John Matthews, TEFEN USA                                                                                        | 133 |

| Filling the Technology Gap Through Balanced Joint Development Projects and Contracted Independent Research Providers Scott Runnels, Southwest Research Institute; Frank Miceli and Bill Easter, Lucent Technologies; Inki Kim, SpeedFam Corporation | 138 |

| Poster Session                                                                                                                                                                                                                                      |     |

| Automated Lot Tracking and Identification System Ulrich Rohrer, SMST Böblingen                                                                                                                                                                      | 142 |

| A Cost Benefit Analysis of Photolithography and Metrology Dedication in a Metrology Constrained Multi-Part Number Fabricator Roger H. Woods, IBM Microelectronics Division                                                                          | 145 |

| Dynamic Capacity Modeling  James R. Mercier, IBM Microelectronics Division                                                                                                                                                                          | 148 |

| Effect of 300mm Wafer and Small Lot Size on Final Test Process Efficiency and Cost of LSI Manufacturing System Koji Nakamae, Akihisa Chikamura and Hiromu Fujioka, Osaka University                                                                 | 151 |

| Fab Implementation of a System for Cleaning Wafers Which Survive Wafer-Breakage Events David F. Hilscher, MiCRUS                                                                                                                                    | 156 |

| A Framework for Real-time Process Control – Part 1: Data Sampling and Processing Graham Rong, Ph.D., GenRad, Inc.                                                                                                                                   | 159 |

| Human Based Knowledge for the Probe Failure Pattern Classification with the Use of a Back Propagation Neural Network.  Application on Submicron Linear Technologies  Carlos Ortega, J. Ignacio, Alonso Montull, Eliseo Sobrino, Lucent Technologies | 165 |

| In-line Defect Density Targets for New Technology from Development to Manufacturing Ed Shamble, Mira Ben-Tzur and Shahin Sharifzadeh, Cypress Semiconductor                                                                                         | 171 |

| In-Situ Gate Oxide/Electrode Deposition for a 0.5µm BiCMOS Process Flow Tom Carbone, Fairchild Semiconductor; Gary Solomon, Semitherm Incorporated                                                                                                  | 174 |

| Manufacturing and Reliability Improvements in Metal-Oxide-Metal Capacitors – MOMCAPs  Larry Lowell, Analog Devices, Inc.                                                                                                                            | 181 |

| Manufacturing for Design: Putting Process Control in the Language of the Designer David C. Potts, Fairchild Semiconductor                                                                                                                           | 187 |

| New Business Models for Standard and ASIC Products in the Semiconductor Industry - Competing on Cost and Time-to-Market R. Akella, J. Kleinknecht, J. Gillespie and B. Kim, Stanford University; A. Frederick, LSI Logic, Inc.                      | 190 |

| Novel Methodology to Include all Measured Extension Values per Defect to Improve Defect Size Distributions Christopher Hess and Larg Weiland, University of Karlsruhe                                                                               | 197 |

| Reducing Perfluorinated Compound Emissions  Cynthia Hines, James Pinto, Raymond Izor, Thomas Tamayo and William Miller, IBM Microelectronics Division                                                                                               | 203 |

| Keynote Address: Foundry Industry Update, Don Brooks, UMC                                                                                                                                                                                                                            | tit to ma |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| International Session                                                                                                                                                                                                                                                                |           |

| Yield Management for Development and Manufacture of Integrated Circuits  Hiroshi Koyama and Masayuki Inokuchi, JEOL Ltd.                                                                                                                                                             |           |

| Statistical Methods for Measurement Reduction in Semiconductor Manufacturing Richard Babikian, Intel Ireland Limited; Curt Engelhard, Intel Corp.                                                                                                                                    | 212       |

| America, Japan and Europe – Which Areas Have the Edge in Customer Satisfaction and Why Christine D. Burgeson, VLSI Research Inc.                                                                                                                                                     | 216       |

| Contamination Free Manufacturing                                                                                                                                                                                                                                                     |           |

| Effects of Process Parameters on Particle Formation in SiH <sub>4</sub> /N <sub>2</sub> 0 PECVD and WF <sub>6</sub> CVD Processes  Z. Wu, S. Nijhawan, S. A. Campbell, N. Rao and P.H. McMurry, University of Minnesota                                                              |           |

| Overcoming the Barriers to Cleaning with Bubble-Free Ozonated De-Ionized Water Timothy Bush, Steven Hardwick and Michael Wikol, W.L. Gore and Associates, Inc.                                                                                                                       |           |

| In-Situ Particle Monitoring in a Vertical Poly Furnace Peter Glass and Joe Kudlacik, IBM Microelectronics Division; Ray Burghard, Pacific Scientific Instruments Group                                                                                                               |           |

| Advanced Aqueous Wafer Cleaning in Power Semiconductor Device Manufacturing R.S. Ridley, Sr., T. Grebs, J. Trost, R. Webb, M. Schuler, R.F. Longenberger, T. Fenstemacher and M. Caravaggio, Harris Semiconductor                                                                    | 235       |

| Residual Gasses Investigation for Elimnating Contamination In LPCVD Si <sub>3</sub> N <sub>4</sub> Process  N. Zhang, G. Magloczki, S. Aumick, G. Chiusano, S. Beckett, G. Nicholls and L. Stearns, MiCRUS                                                                           |           |

| Advantages to Point of Use Filtration of Photoresists in Reducing Contamination on the Wafer Surface Dennis Capitanio, Ph.D., Pall Corp.                                                                                                                                             |           |

| Advanced Metrology                                                                                                                                                                                                                                                                   |           |

| Matching Automated CD SEMs in Multiple Manufacturing Environments  John Allgair and Dustin Ruehle, Motorola, Inc.; John Miller and Richard Elliott, KLA-Tencor Corp.                                                                                                                 | 252       |

| Sidewall Angle Measurements Using CD SEM Bo Su, Tony Pan, Ping Li, Jeff Chinn, Applied Materials Inc.; Xuelong Shi and Mircea Dusa, National Semiconductor Corp.                                                                                                                     | 259       |

| Uses of Corona Oxide Silicon (COS) Measurements for Diffusion Process Monitoring and Troublshooting Richard G. Cosway, Kelvin B. Catmull, Janie Shray, Robert Naujokaitis, Meagan Peters and Don Grant, Motorola, Inc.; Gregory Horner and Brian Letherer, Keithley Instruments Inc. | 262       |

| Effective Defect Detection and Classification Methodology Based on Integrated Laser Scanning Inspection and                                                                                                                                                                          | 266       |

| Automatic Defect Classification Yong-Hui Fan, Ph.D. and Yoel Moalem, KLA-Tencor Corp.                                                                                                                                                                                                | 200       |

| The Quantitation of Surface Modifications in 200 and 300 mm Wafer Processing with an Automated Contact Angle System Ronald Carpio, SEMATECH; David Hudson, AST Products, Inc.                                                                                                        |           |

| Correlation of Ellipsonometric Modeling Results To Observed Grain Structure for OPO Film Stacks Tod E. Robinson, KLA-Tencor Corp.                                                                                                                                                    | 278       |

| Cost Reduction                                                                                                                                                                                                                                                                       |           |

| Beyond Cost-of-Ownership: A Casual Methodology for Costing Wafer Processing Stephanic Miraglia, Peter Miller, Thomas Richardson, Gregory Blunt and Cathy Blouin, IBM Microelectronics Division                                                                                       | 289       |

| A Study in the Continuous Improvement Process: Implementation of an Optimized Scrubber to Replace TEOS Backside  Etch Post SOG Etchback                                                                                                                                              |           |

| W. Au, D. Parks and P. Esquivel, VLSI Technology, Inc.                                                                                                                                                                                                                               | 208       |

| Simulation of Test Wafer Consumption in a Semiconductor Facility Bryce Foster, Doron Meyersdorf, José Padillo and Rafi Brenner, TEFEN Ltd.                                                                                                                                           | 298       |

| † Not available at time of printing                                                                                                                                                                                                                                                  |           |

| Improvement of Silicon Wafer Minority Carrier Lifetime Through the Implementation of a Pre-Thermal Donor Anneal                                                                                                                                                                                                                                       |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Cleaning Process Larry Martines, Charley Wang and Tom Hardenburger, UniSil Corporation; Nancie Barker and Brian Sohmers, Siliconix Corporation                                                                                                                                                                                                        | 303 |

| Design for Manufacturability: A Key to Semiconductor Manufacturing Excellence  R. Wilcox, T. Forhan, G. Starkey and D. Turner, IBM Microelectronics Division                                                                                                                                                                                          | 308 |

| Advanced Processing/Photo & Etch                                                                                                                                                                                                                                                                                                                      |     |

| Highly Selective Oxide to Nitride Etch Processes on BPSG/Nitride/Oxide Structures in a MERIE Etcher W. Graf and G. Skinner, SIEMENS, D. Basso, J.M. Martin and E. Sabouret, IBM France; F. Gautier, Applied Materials                                                                                                                                 | 314 |

| Overview of Plasma Induced Damage After Dry Etch Processing Yuri Karzhavin and Wei Wu, Motorola, Inc.                                                                                                                                                                                                                                                 | 320 |

| Wet Chemical Cleaning for Damaaged Layer Removal Inside the Deep Sub-Micron Contact Hole Mitsuo Miyamoto, Morita Chemical Industries Co., Ltd.; Hideto Gotoh, Texas Instruments, Japan                                                                                                                                                                | 327 |

| Effects of Photoresist Foreshortening on an Advanced Ti/AICu/Ti Metallurgy and W Interconnect Technology (Abstract) C. Whiteside, M. Rutten, H. Trombley, H. Landis and M. Boltz, IBM Microelectronics Division                                                                                                                                       | 332 |

| FC2: Off-Axis Focus Control For Critical Level I-Line Photolithography Christopher H. Putnam, Jacek K. Tyminski, Sean J. McNamara, Nikon Precision Inc.                                                                                                                                                                                               | 333 |

| Keynote Address: Sub-0.25 micron Interconnection Scaling: Damascene Copper versus Subtractive Aluminum  Anthony K. Stamper, Sr. T.L. McDevitt and S. L. Luce, IBM Microelectronics Division                                                                                                                                                           | 337 |

| Advanced Processing/A New Era of Interconnect Technology                                                                                                                                                                                                                                                                                              |     |

| Copper Interconnect - Technology New Paradigms for BEOL Manufacturing Kenneth Rose and Ramon Mangaser, Rensselaer Polytechnic Institute                                                                                                                                                                                                               | 347 |

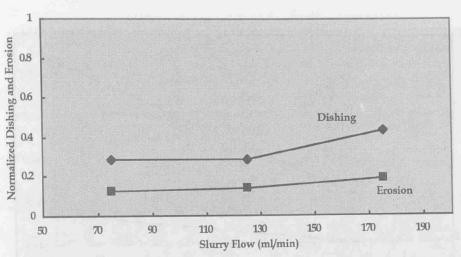

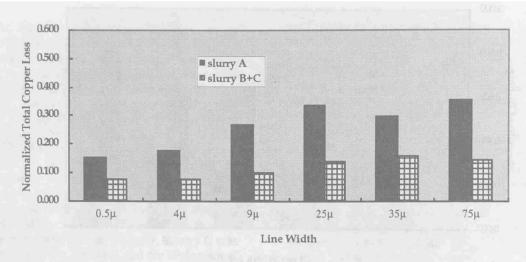

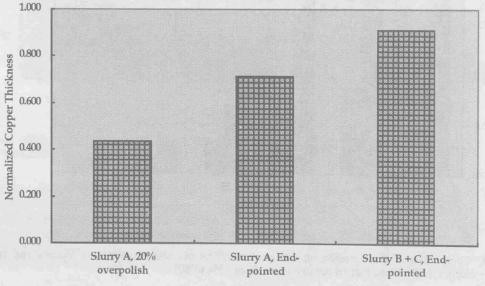

| Development of a Production Worthy Copper CMP Process  K. Wijckoon, S. Mishra, S. Tsai, K. Puntambekar, M. Chandrachood, F. Redeker, R. Tolles, B. Sun, L. Chen, T. Pan, P. Li, S. Nanjangud, G.Amico, Applied Materials, Inc.; J. Hawkins, T. Myers, R. Kistler, V. Brusic, S. Wang, I. Cherian, L. Knowles, C. Schmidt, C. Baker, Cabot Corporation | 354 |

| Cu CMP with Orbital Technology. Summary of the Experience Y. Gotkis, D. Schey, S. Alamgir, J. Yang, K. Holland, Integrated Process Equipment Corporation (IPEC)                                                                                                                                                                                       | 364 |

| A Study of Post-Chemical-Mechanical Polish Cleaning Strategies C. Huynh, M. Rutten, R. Cheek and H. Linde, IBM Microelectronics Division                                                                                                                                                                                                              | 372 |

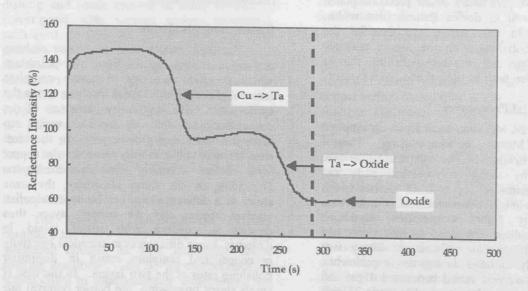

| Process Control and Monitoring with Laser Interferometry Based Endpoint Detection in Chemical Mechanical Planarization David Chan, Bogdan Swedek, Andreas Wiswesser, Manush Birang, Applied Materials, Inc.                                                                                                                                           | 377 |

| Factory Automation – WIP Management                                                                                                                                                                                                                                                                                                                   |     |

| A Layer Based Layout Approach for Semiconductor Fabrication Facilities  Chao-Fan Chang and Shao-Kung Chang, Industrial Technology Research Institute                                                                                                                                                                                                  |     |

| Quantifying Impact of WIP Delivery on Operator Schedule in Semiconductor Manufacturing Line Allen L. Findley, IBM Microelectronics Division                                                                                                                                                                                                           | 391 |

| Better Dispatch Application – A Success Story Anke Giegandt and Gary Nicholson, SIEMENS Microelectronics                                                                                                                                                                                                                                              | 396 |

| Development and Implementation of an Automated Wafer Transport System  Joe Sikich, Hewlett Packard                                                                                                                                                                                                                                                    | 400 |

| A Focus on Cycle Time vs. Tool Utilization "Paradox" with Material Handling Methodology  George W. Horn and William A. Podgurski, Middlesex General Industries, Inc.                                                                                                                                                                                  | 405 |

## Advanced Processing - Isolation and Dielectric Issue at $0.18 \mu m$

| A Manufacturable Shallow Trench Isolation Process for 0.18µm and Beyond-Optimization, Stress Reduction                                                                                                                                                                                          |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| and Electrical Performance F. Nouri, O. Laparra, H. Sur, G.C. Tai, D. Pramanik and M. Manley, VLSI Technology, Inc.                                                                                                                                                                             | 413 |

| Performance and Productivity Improvements in an Advanced Dielectric Etch Reactor for sub 0.3μm Applications M. Srinivasan, R. Caple, G. Hills, G. Mueller, T. Nguyen, and E. Wagganer, Lam Research Corp.                                                                                       | 419 |

| A Study of Boron Doping Profile Control for a Low Vt Device Used in the Advanced Low Power, High Speed Mixed Signal IC Alec Chen, Kyle Flessner and Farris Malone, Peyman Sana, Robert Dixon, Peter Ying and Lou Hutter, Texas Instruments, Inc.                                                | 423 |

| Silicon Nanoelectronics: 100nm Barriers and Potential Solutions Vijay Parihar, R. Singh, K.F. Poole, Clemson University                                                                                                                                                                         | 427 |

| On the Integration of Ta <sub>2</sub> O <sub>5</sub> as a Gate Dielectric in sub-0.18μm, CMOS Processes  T. Devoivre and C. Papadas, ST Microelectronics; M. Setton, LAM Research; N. Sandler, Formerly with LAM Research;  L. Vallier, CNET Grenoble; I. Bouras, Integrated System Development | 434 |

| Factory Modeling/Simulation                                                                                                                                                                                                                                                                     |     |

| Batch Size Optimization of a Furnace and Pre-Clean Area By Using Dynamic Simulations H.J.A. Rulkens, E.J.J. van Campen and J. van Herk, <i>Philips Semiconductor</i> ; J.E. Rooda, <i>Eindhoven University of Technology</i>                                                                    | 439 |

| Simulation Analysis of 300mm Intrabay Automation Vehicle Capacity Alternatives Gerald T. Mackulak, Ph.D., Arizona State University; Frederick P. Lawrence and John Rayter, PRI Automation, Inc.                                                                                                 | 445 |

| Management of Multiple-Pass Constraints J. Bonal, A. Sadai, C. Ortega, S. Aparicio, M. Fernandez, R. Oliva, L. Rodriguez, M. Rosendo, A. Sanchez, E. Paule and D. Ojeda, <i>Lucent Technologies</i>                                                                                             | 451 |

| MOSAIC I Product Transfer Using Virtual Flow Concept Ping Wang, Steve Spivey, Edward Warda, Mark Bowser, Bridgette Cosentino, Ed Zabasajja, Piyush Shah, Salma Imam, John Keller and Joe Fulton, Motorola, Inc.                                                                                 | 455 |