### MULTILING CORPORATION

180 NORTH UNIVERSITY AVE. Suite 600 PROVO, UT 84601-4474 VOICE (801) 377-2000 FAX (801) 377-7085

### TRANSLATOR'S CERTIFICATE OF TRANSLATION

Translation from Japanese to English

MultiLing Project Number: GBPLC1710001HQ-S

Client: Greenblum & Bernstein, P.L.C.

MultiLing Corporation, a Delaware corporation, which has its principal office at 180 North University Avenue, Suite 600, Provo, UT 84601-4474, USA, certifies that

- (a) it is a professional translation company of multiple languages including Japanese and English;

- (b) it has translated from the original document to the translated document identified below, and to the best of its knowledge, information, and belief the translation of that document is accurate as a publication quality translation; and further,

- (c) these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Original Document Identifier: Awaya (1998) (03005811); JPH08250596A (03005939); JPH09293690A (03002312); JPH10125627A (03005938); JPH10256256A (03002313). Translated Document Identifier: Awaya (1998) (03005811)\_en-US; JPH08250596A (03005939)\_en-US; JPH09293690A (03002312)\_en-US; JPH10125627A (03005938)\_en-US; JPH10256256A (03002313)\_en-US.

Signed this 10th day of February 2017.

Michael Degn, VP Sales/Marketing

ACKNOWLEDGMENT BEFORE NOTARY

State of Utah

}ss.

(19) Japan Patent Office (J P)

# (12) Japanese Unexamined Patent Application Publication (A)

(11) Patent Application Publication Number.

## H10-256256

|                      |         |        | (43) Publication Date: |        | e: Septemb | September 25, 1998 |  |

|----------------------|---------|--------|------------------------|--------|------------|--------------------|--|

| ( <b>51</b> ) Int. C | 1.6     | ID No. | FI                     |        |            |                    |  |

| H01L                 | 21/3205 |        | H01L                   | 21/88  | R          |                    |  |

|                      | 21/265  |        |                        | 21/28  | 301R       |                    |  |

|                      | 21/28   | 301    |                        | 21/265 | Q          |                    |  |

|                      |         |        |                        | 21/88  | M          |                    |  |

| Examination requ                                                            | No. of Claims: 18 OL (total 6 pages)   |                                                                                                                        |                                                                                             |  |                      |

|-----------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|----------------------|

| (21) Application No. Application H10-8037                                   |                                        | (71) Applicant: 390019839 Samsung Electronics Co., Ltd. Uehondado-dong 416, Hachijo-gu, Suwon City, Gyeonggi-do, Korea |                                                                                             |  | ng 416,<br>won City, |

| (22) Publication date:                                                      | January 19, 1998                       | (72) Inventor:                                                                                                         | Gwon ▲ Tetsu ▼ Sun<br>1028-1 3-dong, Seocho-si,<br>Seoul, Korea<br>Kyongnam Apartment 7-707 |  |                      |

| (31) Priority Claim Number<br>(32) Priority date:<br>Priority Claim Country | 97P7271<br>March 5, 1997<br>Korea (KR) | (74) Agent:                                                                                                            |                                                                                             |  | Mikoto Hata          |

# (54) [Title of Invention] COPPER METAL WIRE FORMING METHOD FOR SEMICONDUCTOR DEVICE

#### (57) Abstract

[Purpose] To provide a copper metal wire forming method for a semiconductor device having a noncrystalline diffusion preventing film that can prevent diffusion between the semiconductor substrate and the copper metal film.

[Resolution means] A copper metal wire forming method for a semiconductor device has an interlayer insulating film 15a and a diffusion preventing film formed in order on a semiconductor substrate. The diffusion preventing film is formed by a chemical vapor deposition method using any one of Mo, W, Ti, Ta, WN TiW, TiN, or combinations thereof. Furthermore, a noncrystalline diffusion preventing film 17a is formed by ion injection of impurities into the diffusion preventing film, and then a copper film 19a is formed on the noncrystalline diffusion preventing film. The impurities can be one type selected from boron (B), nitrogen (N), and silicon (Si). Therefore, the diffusion of copper through the noncrystalline diffusion preventing film can be prevented.

Specification

Title of the Invention: COPPER METAL WIRE FORMING METHOD FOR SEMICONDUCTOR DEVICE

# [DETAILED DESCRIPTION OF THE INVENTION] [0001]

[Technical Field of the Invention] The present invention relates to a method of manufacturing the semiconductor device, particularly a method of forming a copper metal wire of a semiconductor device.

[0002]

[Background Technology] Generally, a metal wire forming method of a semiconductor device occupies a very important position in the semiconductor manufacturing process because this is a factor for determining the operation speed, yield, and reliability of the semiconductor device. In a conventional semiconductor device with low integration density, a metal wire layer was formed using pure aluminum, but an aluminum layer experiences contact spiking due to absorption of silicon atoms from the silicon substrate due to the increased temperature during a sintering step, and therefore Al-1% Si where aluminum is saturated with silicon is widely used as a material for the metal wire layer.

[0003]

However, if a wire layer of a semiconductor device is formed by using this Al-1% Si, silicon residue is formed by depositing silicon from the wire layer during heat treatment at a temperature of approximately 450°C or higher, silicon nodules are formed by phase epitaxial growth of silicon atoms at contact holes, and there is increased resistance of the metal wire layer and increased contact resistance. Forming a diffusion preventing film such as a TiN thin film between the metal wire layer and the silicon substrate or the insulating layer is commonly known in order to prevent the formation of aluminum spiking, silicon residue, and silicon nodules caused by the aforementioned reactions between the metal wire layer and the silicon substrate. [0004]

On the other hand, copper with a lower relative resistance than conventional alumina metal because of a continuous reduction of the area of the semiconductor element is focused on as a next-generation metal wire material.

[0005]

However, the diffusion rate of copper in the diffusion preventing film is much larger than aluminum, and the diffusion preventing ability is lost in existing TiN films at temperatures of 600°C or higher. The cause is that a TiN thin film has a crystalline particle structure with a columnar structure, and therefore copper that primarily diffuses along the grain boundary cannot be effectively blocked. Furthermore, the TiN thin film is formed by a sputtering method, so there are disadvantages that not only is the occurrence of defects in the thin film due to radiation loss higher, but the step coverage is poor. [0006]

[Problem to Be Resolved by the Invention] A technical problem of the present invention is to provide a copper metal wire forming method for a semiconductor device having a noncrystalline diffusion preventing film with excellent step coverage and that can block diffusion of copper through a grain boundary.

[0007]

[Means for Resolving the Problem] In order to resolve the aforementioned technical problems, the copper metal wire forming method for a semiconductor device according to one aspect of the present invention successively forms an interlayer insulating film (interlevel dielectric layer) and a diffusion preventing film (diffusion barrier film). The diffusion preventing film is formed using any one of Mo, W, Ti, Ta, WN TiW, TiN, or combinations thereof. Furthermore, a noncrystalline diffusion preventing film is formed by ion injection of impurities into the diffusion preventing film, and then a copper film is formed on the noncrystalline diffusion preventing film. The impurities can be one type selected from boron (B), nitrogen (N), and silicon (Si). Therefore, the copper of the copper film will not diffuse into the interlayer insulating film because of the noncrystalline diffusion preventing film.

Furthermore, the copper metal wire forming method for a semiconductor device according to another aspect of the present invention forms an interlayer insulating film on the semiconductor substrate, and then forms contact holes that expose the semiconductor substrate by etching. Next, a diffusion preventing film is formed on the interlayer insulating film and the exposed semiconductor substrate. The diffusion preventing film is formed using any one of Mo, W, Ti, Ta, WN TiW, TiN, or combinations thereof. Next, a noncrystalline diffusion preventing film is formed by ion injection of impurities into the diffusion preventing film. The impurities can be one type selected from boron (B), nitrogen (N), and silicon (Si). Next, a copper film is formed on the noncrystalline diffusion preventing film. Therefore, the copper of the copper film will not diffuse into the semiconductor substrate because of the noncrystalline diffusion preventing film. [0009]

Furthermore, the copper metal wire forming method for a semiconductor device according to another aspect of the present invention has an interlayer insulating film and a first copper film formed in order on a semiconductor substrate. Next, a via hole that exposes the first copper film is formed by etching the interlayer insulating film, and then a diffusion preventing film is formed on the exposed first copper film and the interlayer insulating film. The diffusion preventing film is formed using any one of Mo, W, Ti, Ta, WN TiW, TiN, or combinations thereof. Next, a noncrystalline diffusion preventing film is formed by ion injection of impurities into the diffusion preventing film, and then a second copper film is formed on the noncrystalline diffusion preventing film. The impurities can be one type selected from boron (B), nitrogen (N), and silicon (Si).

Furthermore, the copper metal wire forming method for a semiconductor device according to yet another aspect of the present invention forms a first interlayer insulating film on the semiconductor substrate, and then forms contact holes that expose the semiconductor substrate by etching. Next, a first diffusion preventing film is formed on the exposed semiconductor substrate and the first interlayer insulating film, and then the first noncrystalline diffusion preventing film is formed by ion injection of impurities into the first diffusion preventing film.

Next, a first copper film and a second diffusion preventing film are formed in order on the first noncrystalline diffusion preventing film. Next, a second noncrystalline

diffusion preventing film is formed by ion injection of impurities into the second diffusion preventing film. Next, a second interlayer insulating film is formed on the entire surface of the second noncrystalline diffusion preventing film, and then a via hole that exposes the first copper film is formed by etching the second interlayer insulating film and the second noncrystalline diffusion preventing film. A third diffusion preventing layer is formed on the entire surface of the substrate in which the via holes are formed, and then a third noncrystalline diffusion preventing film is formed by ion injection of impurities into the third diffusion preventing film. Next, a second copper film is formed such that the via holes can be embedded on the third noncrystalline diffusion preventing film.

With the copper metal wire forming method for a semiconductor device of the present invention, a diffusion preventing film is formed and then impurities are ion injected into the diffusion preventing film, so the diffusion of copper through the grain boundary can be prevented by making the crystal structure to be noncrystalline.

[0013]

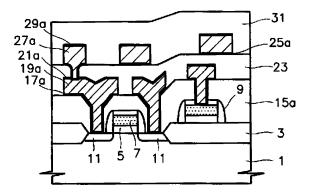

[Description of the Preferred Embodiments] An embodiment of the present invention is described below in detail by referring to the attached drawings. As illustrated in Fig. 1, a transistor is formed with a gate oxide film 5, a gate electrode 7, a spacer 9, a source/drain region 11, and a capping insulating film 13 on an active region of a semiconductor substrate 1 limited by a field oxide film 3. At this time, the gate electrode 7 and the capping insulating film 13 are also formed on the field insulating film 3. Next, a first interlayer insulating film 15 is formed on the entire surface of the resulting product where the transistor was formed.

[0014]

As illustrated in Fig. 2, a first interlayer insulating film pattern 15a with a contact hole 16 that exposes the surface of the source/drain region 11 of the semiconductor substrate is formed by etching the first interlayer insulating film 15 using a photoetching process. At this time, the capping insulating film 13 formed on the field insulating film 3 is also etched, and a contact hole 16 is formed to expose the gate electrode 7. [0015]

As illustrated in Fig. 3, the first diffusion preventing film is formed on the entire surface of the semiconductor substrate 1 that is exposed by the contact hole 16, using any one of Mo, W, Ti, Ta, WN TiW, TiN, or combinations thereof, at a thickness of 100 to 1000 Å. The diffusion preventing film is formed by a chemical vapor deposition method with excellent step coverage and minimal occurrence of defects, such as low-pressure chemical vapor deposition (LPCVD) or plasma enhanced chemical vapor deposition (PECVD) at a temperature of 300 to 600°C. Next, the first noncrystalline diffusion preventing film 17 is formed by ion injection of impurities such as boron (B), nitrogen (N) or silicon into the first diffusion preventing film at an acceleration voltage of 20 to 140 KeV and a dose of  $10^{16}$  -  $10^{17}$  ions/cm<sup>2</sup>. This time, the ion injected impurity is positioned at the interface between the semiconductor substrate 1 and the first noncrystalline diffusion preventing film 17. Therefore, the first noncrystalline diffusion preventing film 17 has a crystalline structure that is noncrystalline because of ion injection, and therefore diffusion of copper through the grain boundary and into the source/drain region 11 and the gate electrode 7 is prevented up to 800°C. Furthermore, the first noncrystalline diffusion preventing film 17 prevents reaction between the first interlayer insulating film pattern 15a

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.